#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I²C, SCI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 47                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-BQFP                                                                     |

| Supplier Device Package    | 64-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36074ghv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.4 **Pin Assignment**

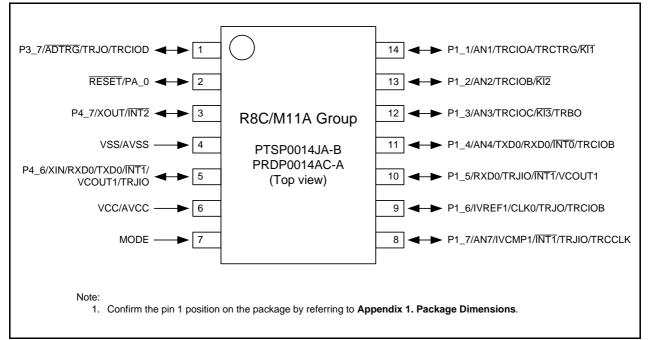

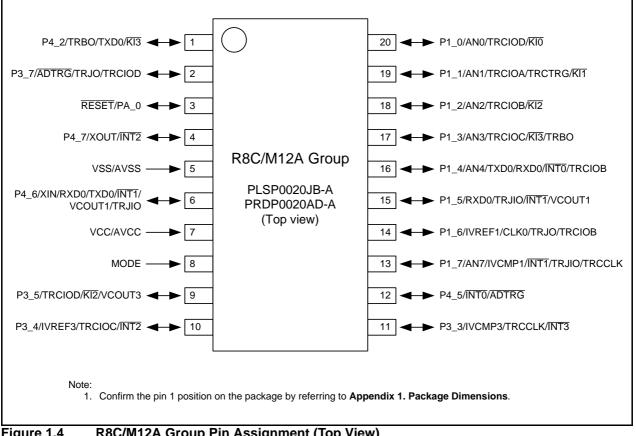

Figures 1.3 and 1.4 show Pin Assignment (Top View). Table 1.6 lists the Pin Name Information by Pin Number.

Figure 1.3 R8C/M11A Group Pin Assignment (Top View)

R8C/M12A Group Pin Assignment (Top View) Figure 1.4

# WDR Bit (Watchdog timer reset detect flag)

This flag indicates that a reset has been generated by the watchdog timer.

[Condition for setting to 0]

- When a software reset, hardware reset, power-on reset, or voltage monitor 0 reset occurs.

- [Condition for setting to 1]

- When a watchdog timer reset occurs.

# 8. Watchdog Timer

The watchdog timer is a function for detecting program malfunctions. Using this function is recommended, since it can improve system reliability.

The watchdog timer also has a function that can be used as a periodic timer.

## 8.1 Overview

The watchdog timer has a 14-bit down counter, and count source protection mode can be enabled or disabled. Table 8.1 lists the Watchdog Timer Specifications.

For details on the watchdog timer reset, see 6.3.5 Watchdog Timer Reset.

For details on the periodic timer, see **8.3.4 Periodic Timer Function**.

Figure 8.1 shows the Watchdog Timer Block Diagram.

| Item                                        | Count Source Protection Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Count Source Protection Mode Enabled                                                                                                                                                                   |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count source                                | CPU clock or low-speed on-chip oscillator clock (1/16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Low-speed on-chip oscillator clock                                                                                                                                                                     |

| Count operation                             | Decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |

| Count start condition                       | Either of the following can be selected:<br>• The count is automatically started after a res<br>• The count is started by writing to the WDTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                        |

| Count stop conditions                       | When wait mode or stop mode is entered while the count source is the CPU clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | None                                                                                                                                                                                                   |

| Watchdog timer<br>initialization conditions | <ul> <li>Reset</li> <li>00h and then FFh are written to the WDTR r<br/>(when a refresh acceptance period is set)</li> <li>Underflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | register during the refresh acceptance period                                                                                                                                                          |

| Operation at underflow                      | Watchdog timer interrupt or watchdog timer reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Watchdog timer reset                                                                                                                                                                                   |

| Selectable functions                        | <ul> <li>Selection of the count source<br/>Selected by bits WDTC6 to WDTC7 in the N</li> <li>Count source protection mode <ul> <li>Whether count source protection mode is<br/>selected by the CSPROINI bit in the OFS</li> <li>If count source protection mode is disable<br/>enabled or disabled is selected by the CS</li> </ul> </li> <li>Start or stop of the watchdog timer after a re<br/>Selected by the WDTON bit in the OFS reg</li> <li>Initial value of the watchdog timer (underflow<br/>Selected by bits WDTUFS0 to WDTUFS1 in<br/>Refresh acceptance period for the watchdog<br/>Selected by bits WDTRCS0 to WDTRCS1 in</li> </ul> | enabled or disabled after a reset can be<br>register.<br>d, whether count source protection mode is<br>PRO bit in the CSPR register.<br>eset<br>ister.<br>v period)<br>n the OFS2 register.<br>g timer |

Table 8.1 Watchdog Timer Specifications

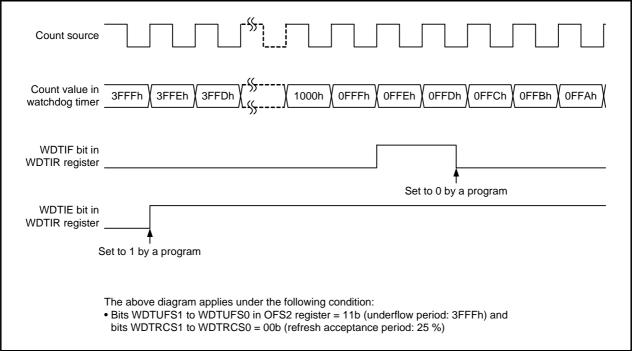

#### 8.3.4 Periodic Timer Function

The count range is determined by the underflow period setting (bits WDTUFS0 to WDTUFS1 in the OFS2 register) and the refresh acceptance period setting (bits WDTRCS0 to WDTRCS1 in the OFS2 register). The periodic timer cannot be used in stop mode.

Table 8.5 lists the Periodic Timer Settings. Figure 8.3 shows the Timing of Periodic Timer Function.

When the periodic timer runs beyond the count range in Table 8.5, the WDTIF bit in the WDTIR register is set to 1 (periodic timer interrupt requested).

| Table 8.5 | Periodic Timer Settings |

|-----------|-------------------------|

|-----------|-------------------------|

| Initial Value Set by Bits WDTUFS1<br>to WDTUFS0 in OFS2 Register | Refresh Range Set by Bits WDTRCS1 to<br>WDTRCS0 in OFS2 Register <sup>(1)</sup> | Range Counted by Periodic Timer |

|------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------|

|                                                                  | 10b                                                                             | $3FFFh \rightarrow 2FFFh$       |

| 11b                                                              | 01b                                                                             | $3FFFh \rightarrow 1FFFh$       |

|                                                                  | 00b                                                                             | $3FFFh \rightarrow 0FFFh$       |

|                                                                  | 10b                                                                             | $1FFFh \rightarrow 17FFh$       |

| 10b                                                              | 01b                                                                             | $1FFFh \rightarrow 0FFFh$       |

|                                                                  | 00b                                                                             | $1FFFh \rightarrow 07FFh$       |

|                                                                  | 10b                                                                             | $0FFFh \rightarrow 0BFFh$       |

| 01b                                                              | 01b                                                                             | $0FFFh \rightarrow 07FFh$       |

|                                                                  | 00b                                                                             | $0FFFh \rightarrow 03FFh$       |

|                                                                  | 10b                                                                             | $03FFh \rightarrow 02FFh$       |

| 00b                                                              | 01b                                                                             | $03FFh \rightarrow 01FFh$       |

|                                                                  | 00b                                                                             | $03FFh \rightarrow 00FFh$       |

Note:

1. When bits WDTRCS1 to WDTRCS0 in the OFS2 register is 11b (100 %), set the WDTIE bit to 0 (periodic timer interrupt disabled).

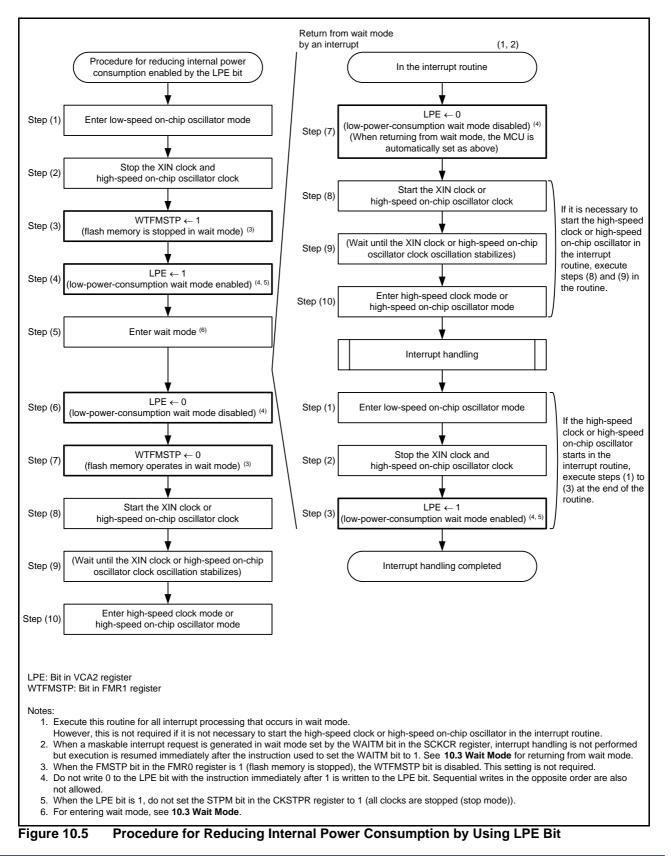

#### 10.5.9 Reducing Internal Power Consumption

When entering wait mode using low-speed on-chip clock mode or low-speed on-chip oscillator mode, internal power consumption can be reduced using the LPE bit in the VCA2 register. To enable low internal power consumption using the LPE bit, follow **Figure 10.5 Procedure for Reducing Internal Power Consumption by Using LPE Bit**.

RENESAS

| Interrupt                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Undefined instruction interrupt      | An unidentified instruction interrupt is generated when the UND instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Overflow interrupt                   | An overflow interrupt is generated when the O flag is 1 (arithmetic operation overflow) and the INTO instruction is executed. Instructions that change the O flag are as follows:<br>ABS, ADC, ADCF, ADD, CMP, DIV, DIVU, DIVX, NEG, RMPA, SBB, SHA, and SUB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BRK instruction interrupt            | A BRK interrupt is generated when the BRK instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INT instruction interrupt            | An INT instruction interrupt is generated when the INT instruction is executed.<br>Software interrupt numbers the INT instruction can specify are 0 to 63. The<br>number is assigned to each peripheral function interrupt. When the INT<br>instruction is executed specifying the number, the peripheral function interrupt<br>with the same number can be executed.<br>For software interrupt numbers 0 to 31, the U flag is saved on the stack during<br>instruction execution, and the U flag is set to 0 (ISP) before the interrupt<br>sequence is executed. The U flag is restored from the stack when the MCU<br>returns from the interrupt numbers 32 to 63, the U flag does not change state during<br>instruction execution, and the selected SP is used. |

| Watchdog timer interrupt             | This interrupt is generated by the watchdog timer. For details, see <b>8. Watchdog Timer</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Oscillation stop detection interrupt | This interrupt is generated by the oscillation stop detection function. For details on the oscillation stop detection function, see <b>9. Clock Generation Circuit</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Voltage monitor 1 interrupt          | This interrupt is generated by the voltage detection circuit. For details on the voltage detection circuit, see <b>7. Voltage Detection Circuit</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Single-step interrupt                | Do not use this interrupt. It is provided exclusively for use in development tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Address match interrupt              | When one of the AIENi0 bit (i = 0 or 1) in the AIENi register is 1 (enabled), an address match interrupt is generated immediately before executing the instruction that is stored at an address indicated by the corresponding AIADRi register (i = 0 or 1). For details on the address match interrupt, see <b>11.7 Address Match Interrupt</b> .                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Peripheral function interrupt        | A peripheral function interrupt is generated by a peripheral function in the MCU.<br>For the interrupt sources for the corresponding peripheral function interrupt, see<br>the interrupts and the vector table addresses as listed in <b>Table 11.6 Relocatable</b><br><b>Vector Table</b> . For details on the peripheral functions, see the descriptions of<br>individual peripheral functions.                                                                                                                                                                                                                                                                                                                                                                   |

Table 11.2

Descriptions of Interrupts

# 11.2.4 Key Input Enable Register (KIEN)

| Address 0003Eh |       |       |       |       |       |       |       |       |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Bit            | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |  |

| Symbol         | KI3PL | KI3EN | KI2PL | KI2EN | KI1PL | KI1EN | KI0PL | KI0EN |  |

| After Reset    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| Bit | Symbol | Bit Name                                 | Function                          | R/W |

|-----|--------|------------------------------------------|-----------------------------------|-----|

| b0  | KI0EN  | KI0 input enable bit                     | 0: Disabled<br>1: Enabled         | R/W |

| b1  | KI0PL  | KIO input edge select bit <sup>(1)</sup> | 0: Falling edge<br>1: Rising edge | R/W |

| b2  | KI1EN  | KI1 input enable bit                     | 0: Disabled<br>1: Enabled         | R/W |

| b3  | KI1PL  | KI1 input edge select bit <sup>(1)</sup> | 0: Falling edge<br>1: Rising edge | R/W |

| b4  | KI2EN  | KI2 input enable bit                     | 0: Disabled<br>1: Enabled         | R/W |

| b5  | KI2PL  | KI2 input edge select bit <sup>(1)</sup> | 0: Falling edge<br>1: Rising edge | R/W |

| b6  | KI3EN  | KI3 input enable bit                     | 0: Disabled<br>1: Enabled         | R/W |

| b7  | KI3PL  | KI3 input edge select bit <sup>(1)</sup> | 0: Falling edge<br>1: Rising edge | R/W |

Note:

1. Changing the bits KliPL or KliEN (i = 0 to 3) may set the IRKI bit in the IRR3 register to 1 (interrupt requested). See 11.9.4 Rewriting Registers PMLi, PMHi (i = 1, 3, or 4), ISCR0, INTEN, and KIEN.

#### Interrupt Monitor Flag Register 2 (IRR2) 11.2.8

| Ado     | dress 00 | 052h        |                                                                      |              |           |             |                      |          |      |     |

|---------|----------|-------------|----------------------------------------------------------------------|--------------|-----------|-------------|----------------------|----------|------|-----|

|         | Bit      | b7          | b6                                                                   | b5           | b4        | b3          | b2                   | b1       | b0   |     |

| Sy      | /mbol    | _           |                                                                      |              | —         | IRCMP3      | 3 IRCMP1             |          |      |     |

| After F | Reset    | 0           | 0                                                                    | 0            | 0         | 0           | 0                    | 0        | 0    |     |

|         | <u> </u> | <del></del> |                                                                      |              |           |             |                      |          |      |     |

| Bit     | Symbo    | l.          |                                                                      | Bit Nam      | е         |             |                      | Func     | tion | R/W |

| b0      | —        | Res         | erved                                                                |              |           |             | The read value is 0. |          |      | R   |

| b1      | —        |             |                                                                      |              |           |             |                      |          |      |     |

| b2      | IRCMP    | 1 Con       | nparator B1                                                          | interrupt re | equest mo | •           | 0: No interru        |          | ed   | R   |

| b3      | IRCMP:   | 3 Con       | nparator B3                                                          | interrupt re | equest mo | onitor flag | 1: Interrupt r       | equested |      | R   |

| b4      | —        | Noth        | Nothing is assigned. The write value must be 0. The read value is 0. |              |           |             |                      |          |      | —   |

| b5      | —        |             |                                                                      |              |           |             |                      |          |      |     |

| b6      | —        |             |                                                                      |              |           |             |                      |          |      |     |

| b7      | —        |             |                                                                      |              |           |             |                      |          |      |     |

The IRR2 register is the monitor flag register for comparator B1 and comparator B3 interrupt requests. See 11.4.2.1 Registers IRR0 to IRR2 for the relation between interrupt monitor flag bits and peripheral function interrupts.

# 13.3.4 Timer RJ Mode Register (TRJMR)

| Address     | Address 000DCh |      |      |      |        |       |       |       |  |  |

|-------------|----------------|------|------|------|--------|-------|-------|-------|--|--|

| Bit         | b7             | b6   | b5   | b4   | b3     | b2    | b1    | b0    |  |  |

| Symbol      | TCKCUT         | TCK2 | TCK1 | TCK0 | TEDGPL | TMOD2 | TMOD1 | TMOD0 |  |  |

| After Reset | 0              | 0    | 0    | 0    | 0      | 0     | 0     | 0     |  |  |

| Bit | Symbol | Bit Name                                        | Function                                                                                                                                      | R/W |

|-----|--------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | TMOD0  | Timer RJ operating mode select bits             | b2 b1 b0                                                                                                                                      | R/W |

| b1  | TMOD1  |                                                 | 0 0 0: Timer mode<br>0 0 1: Pulse output mode                                                                                                 | R/W |

| b2  | TMOD2  |                                                 | 0 1 0: Event counter mode<br>0 1 1: Pulse width measurement mode<br>1 0 0: Pulse period measurement mode<br>Other than the above: Do not set. | R/W |

| b3  | TEDGPL | TRJIO edge polarity select bit                  | 0: One-way edge<br>1: Two-way edge                                                                                                            | R/W |

| b4  | TCK0   | Timer RJ count source select bits (1, 2)        | b6 b5 b4<br>0 0 0; f1                                                                                                                         | R/W |

| b5  | TCK1   |                                                 | 0.0.1; f8                                                                                                                                     | R/W |

| b6  | TCK2   |                                                 | 0 1 0: fHOCO<br>0 1 1: f2<br>Other than the above: Do not set.                                                                                | R/W |

| b7  | TCKCUT | Timer RJ count source cutoff bit <sup>(2)</sup> | 0: Count source is supplied<br>1: Count source is cut off                                                                                     | R/W |

Notes:

1. When event counter mode is selected, the external input (TRJIO) is selected as the count source regardless of the setting of bits TCK0 to TCK2.

2. Do not switch or cut off the count source during count operation. When switching or cutting off the count source, set the TSTART bit in the TRJCR register to 0 (count is stopped) and the TCSTF bit to 0 (count is stopped) to stop the timer count.

Select the operating mode when the count is stopped (the TSTART bit is 0 and the TCSTF bit is 0). When a value is written to the TRJMR register, the toggle flip-flop is initialized.

## 13.3.5 Timer RJ Event Select Register (TRJISR)

| Address 000DDh |    |    |    |    |    |          |          |          |

|----------------|----|----|----|----|----|----------|----------|----------|

| Bit            | b7 | b6 | b5 | b4 | b3 | b2       | b1       | b0       |

| Symbol         |    |    |    |    | —  | RCCPSEL2 | RCCPSEL1 | RCCPSEL0 |

| After Reset    | 0  | 0  | 0  | 0  | 0  | 0        | 0        | 0        |

| Bit | Symbol   | Bit Name                             | Function                                                                                                                                                             | R/W |

|-----|----------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | RCCPSEL0 | Timer RC output signal select        | 0 0: TRCIOD                                                                                                                                                          | R/W |

| b1  | RCCPSEL1 | bits                                 | 0 1: TRCIOC<br>1 0: TRCIOB                                                                                                                                           | R/W |

| b2  | RCCPSEL2 | Timer RC output signal inversion bit | <ol> <li>1 1: TRCIOA</li> <li>0: Low-level period of timer RC output signal is counted</li> <li>1: High-level period of timer RC output signal is counted</li> </ol> | R/W |

| b3  |          |                                      | value must be 0. The read value is 0.                                                                                                                                |     |

| 03  |          | Nothing is assigned. The write       | value must be 0. The feat value is 0.                                                                                                                                | _   |

| b4  | —        |                                      |                                                                                                                                                                      |     |

| b5  | —        |                                      |                                                                                                                                                                      |     |

| b6  | —        |                                      |                                                                                                                                                                      |     |

| b7  | _        |                                      |                                                                                                                                                                      |     |

| ,                                                                                                      | Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                                                                      |              |                          |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------|

| Count source                                                                                           | After the value is written, it is written to the reload register<br>by the third count source                                                                                                                                                                                                                                                                                                                                               |              |                          |

| TRBPRE ·<br>reload register                                                                            | Previous value (01h)                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                          |

| ······································                                                                 | Reloaded by the next count source                                                                                                                                                                                                                                                                                                                                                                                                           |              |                          |

| Prescaler                                                                                              | ( 07h ) 06h ) 05h ) 04h ) 01h ) 00h ) 0                                                                                                                                                                                                                                                                                                                                         | 01h 00h      | (01h                     |

| Prescaler<br>underflow                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | 1                        |

|                                                                                                        | After the value is written, it is written to the read at the first underflow                                                                                                                                                                                                                                                                                                                                                                | reload regis | ter                      |

| TRBPR<br>reload register                                                                               | Previous value New value (25h)                                                                                                                                                                                                                                                                                                                                                                                                              |              |                          |

|                                                                                                        | Reloaded at the second under                                                                                                                                                                                                                                                                                                                                                                                                                | erflow       |                          |

| Counter                                                                                                | 03h 02h 25h 24h                                                                                                                                                                                                                                                                                                                                                                                                                             |              | <b>√</b>                 |

|                                                                                                        | RBMR register is 1 (write to reload register only)<br>Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                | 23h          | <u>х</u>                 |

|                                                                                                        | RBMR register is 1 (write to reload register only)                                                                                                                                                                                                                                                                                                                                                                                          |              | )<br>                    |

| ,                                                                                                      | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                   |              | )                        |

| Count source                                                                                           | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                   |              | )<br>                    |

| Count source                                                                                           | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                   | 23h          | )(<br>)()<br>)(01h)      |

| Count source<br>TRBPRE<br>reload register                                                              | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                   |              | )<br><br>(01h)           |

| Count source<br>TRBPRE<br>reload register                                                              | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register                                                                                                                                                                                                                                                                                                                                   |              | )<br><br>)<br>01h )      |

| Count source<br>TRBPRE<br>reload register<br>Prescaler                                                 | RBMR register is 1 (write to reload register only)<br>Write 01h to TRBPRE register and 25h to TRBPR register<br>After the value is written, it is written to the reload register<br>by the third count source<br>Previous value<br>New value (01h)<br>Reloaded at underflow<br>(07h) 06h 05h 04h 03h 02h 01h 00h 01h 00h 01h 00h 0<br>After the value is written, it is v                                                                   | 01h ( 00h    | )<br><br>)<br><br>]      |

| Count source<br>TRBPRE <sup>-</sup><br>reload register<br>Prescaler<br>underflow<br>TRBPR <sup>-</sup> | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register After the value is written, it is written to the reload register by the third count source Previous value New value (01h) Reloaded at underflow (07h 06h 05h 04h 03h 02h 01h 00h 01h 00h 01h 00h 0                                                                                                                                | 01h ( 00h    | )()<br>()(01h)<br>()(1h) |

| Count source<br>TRBPRE<br>reload register<br>Prescaler<br>underflow                                    | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register After the value is written, it is written to the reload register by the third count source Previous value New value (01h) Reloaded at underflow O7h 06h 05h 04h 03h 02h 01h 00h 01h 00h 01h 00h 0 After the value is written, it is written to the reload register the reload register the reload register at the first underflow | 01h ( 00h    |                          |

| Count source<br>TRBPRE <sup>-</sup><br>reload register<br>Prescaler<br>underflow<br>TRBPR <sup>-</sup> | RBMR register is 1 (write to reload register only) Write 01h to TRBPRE register and 25h to TRBPR register After the value is written, it is written to the reload register by the third count source Previous value New value (01h) Reloaded at underflow O7h 06h 05h 04h 03h 02h 01h 00h 01h 00h 01h 00h 0 After the value is written, it is written to the reload register the reload register the reload register at the first underflow | 01h ( 00h    |                          |

(Timer Mode or Programmable One-Shot Generation Mode)

RENESAS

# 15. Timer RC

Timer RC is a 16-bit timer that provides output compare and input capture functions and can count external events. It can be used as a multifunction timer with various applications such as generation of pulse output with an arbitrary duty cycle using the compare match between the timer RC counter and four general registers.

#### 15.1 Overview

Table 15.1 lists the Timer RC Specifications. Table 15.2 lists the Timer RC Functions. Figure 15.1 shows the Timer RC Block Diagram. Table 15.3 lists Timer RC Pin Configuration.

|                                         | Item                              |                                             | Description                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------|-----------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Count sources<br>(counter input clocks) | Operating Internal clock<br>clock |                                             | <ul> <li>f1, f2, f4, f8, or f32:<br/>Selected when bits CKS2 to CKS0 in the TRCCR1<br/>register are 000b to 100b.</li> <li>fHOCO:<br/>Selected when bits CKS2 to CKS0 in the TRCCR1<br/>register are 110b.</li> </ul>                                                         |  |  |

|                                         |                                   | External clock<br>(external event<br>count) | TRCCLK input:<br>Selected when bits CKS2 to CKS0 in the TRCCR1<br>register are 101b.                                                                                                                                                                                          |  |  |

| Pulse I/O pins                          |                                   |                                             | 4                                                                                                                                                                                                                                                                             |  |  |

| General registers                       |                                   |                                             | <ul> <li>4</li> <li>Can be set as output compare or input capture registers individually.</li> <li>Can be used as buffer registers for output compare or input capture.</li> </ul>                                                                                            |  |  |

| Operating modes Timer mode              |                                   |                                             | <ul> <li>Output compare function:<br/>Low-level, high-level, or toggle output can be performed.</li> <li>Input capture function:<br/>A rising edge, falling edge, or two-way edge can be<br/>detected.</li> <li>Counter clear function: A count period can be set.</li> </ul> |  |  |

|                                         | PWM mode                          |                                             | PWM output with up to three phases.                                                                                                                                                                                                                                           |  |  |

|                                         | PWM2 mode                         |                                             | Pulse output with an arbitrary period and duty.                                                                                                                                                                                                                               |  |  |

| Interrupt sources                       |                                   |                                             | <ul> <li>Compare match/input capture multiplexed interrupt × 4<br/>sources</li> <li>Overflow interrupt</li> </ul>                                                                                                                                                             |  |  |

| Others                                  |                                   |                                             | <ul> <li>The initial value of the timer RC output can be set<br/>arbitrarily.</li> <li>A/D conversions triggered by compare matches in<br/>registers TRCGRA, TRCGRB, TRCGRC, and TRCGRD<br/>can be set.</li> </ul>                                                            |  |  |

Table 15.1 Timer RC Specifications

Table 15.2 Timer RC Functions

| Item                      |                    | Counter        | I/O Pin        |                |                 |                 |  |  |

|---------------------------|--------------------|----------------|----------------|----------------|-----------------|-----------------|--|--|

|                           |                    | Counter        | TRCIOA         | TRCIOB         | TRCIOC          | TRCIOD          |  |  |

| General registers (output |                    | Period setting | TRCGRA         | TRCGRB         | TRCGRC          | TRCGRD          |  |  |

|                           | nput capture       | with the       | register       | register       | register        | register        |  |  |

| multiplexe                | d registers)       | TRCGRA         |                |                | In buffer       | In buffer       |  |  |

|                           |                    | register       |                |                | operation       | operation       |  |  |

|                           |                    |                |                |                | Buffer register | Buffer register |  |  |

|                           |                    |                |                |                | for the TRCGRA  | for the TRCGRB  |  |  |

|                           |                    |                |                |                | register        | register        |  |  |

| Counter c                 | ear function       | Input capture/ | Input capture/ | —              | —               | —               |  |  |

|                           |                    | compare match  | compare match  |                |                 |                 |  |  |

|                           |                    | for the TRCGRA | for the TRCGRA |                |                 |                 |  |  |

|                           |                    | register       | register       |                |                 |                 |  |  |

|                           |                    | TRCTRG input   | —              | _              | _               | —               |  |  |

| -                         | nction for initial | —              | Available      | Available      | Available       | Available       |  |  |

| output leve               | əl                 |                |                |                |                 |                 |  |  |

| Buffer ope                | ration             | _              | Available      | Available      | _               | —               |  |  |

| Compare Low-level         |                    | —              | Available      | Available      | Available       | Available       |  |  |

| match                     | output             |                |                |                |                 |                 |  |  |

| High-level                |                    | —              | Available      | Available      | Available       | Available       |  |  |

|                           | output             |                |                |                |                 |                 |  |  |

| Toggle output             |                    | —              | Available      | Available      | Available       | Available       |  |  |

| Input capture function    |                    | —              | Available      | Available      | Available       | Available       |  |  |

| PWM mode                  |                    | —              | —              | Available      | Available       | Available       |  |  |

| PWM2 mc                   | de                 | —              | —              | Available      | _               | —               |  |  |

| Interrupt s               | ources             | Overflow       | Compare match/ | Compare match/ | Compare match/  | Compare match/  |  |  |

|                           |                    |                | input capture  | input capture  | input capture   | input capture   |  |  |

#### 16.3.1.4 Continuous Receive Mode

Continuous receive mode is selected by setting the U0RRM bit in the U0C1 register to 1 (continuous receive mode enabled). In this mode, reading the U0RB register sets the TI bit in the U0C1 register to 0 (data present in the U0TB register). When the U0RRM bit is 1, do not write dummy data to the U0TB register by a program.

## 16.3.1.5 Dealing with Communication Errors

If communication is aborted or a communication error occurs while transmitting or receiving in clock synchronous serial I/O mode, follow the procedure below:

- (1) Set the TE bit in the U0C1 register to 0 (transmission disabled) and the RE bit to 0 (reception disabled).

- (2) Set bits SMD2 to SMD0 in the U0MR register to 000b (serial interface disabled).

- (3) Set bits SMD2 to SMD0 in the U0MR register to 001b (clock synchronous serial I/O mode).

- (4) Set the TE bit in the U0C1 register to 1 (transmission enabled) and the RE bit to 1 (reception enabled).

# 17.2.4 A/D Control Register 0 (ADCON0)

| Ade     | dress 000 | 9Eh   |              |             |             |            |           |             |      |     |

|---------|-----------|-------|--------------|-------------|-------------|------------|-----------|-------------|------|-----|

|         | Bit       | b7    | b6           | b5          | b4          | b3         | b2        | b1          | b0   |     |

| Sy      | /mbol     | _     | —            | —           | —           | —          | —         | _           | ADST |     |

| After F | Reset     | 0     | 0            | 0           | 0           | 0          | 0         | 0           | 0    |     |

|         |           | -     |              |             |             |            |           |             |      |     |

| Bit     | Symbol    |       | В            | lit Name    |             |            |           | Functior    | 1    | R/W |

| b0      | ADST      | A/D o | conversion   | start bit   |             | 0: A/D co  | onversion | stops       |      | R/W |

|         |           |       |              |             |             | 1: A/D co  | onversion | starts      |      |     |

| b1      | -         | Noth  | ing is assig | gned. The v | write value | must be 0. | The read  | value is 0. |      | _   |

| b2      | —         |       |              |             |             |            |           |             |      |     |

| b3      | —         |       |              |             |             |            |           |             |      |     |

| b4      | —         |       |              |             |             |            |           |             |      |     |

| b5      | —         |       |              |             |             |            |           |             |      |     |

| b6      | —         |       |              |             |             |            |           |             |      |     |

| b7      | —         |       |              |             |             |            |           |             |      |     |

The ADCON0 register is used to control A/D conversion operation.

## ADST Bit (A/D conversion start bit)

The ADST bit is used to start or stop A/D conversion.

[Conditions for setting to 0]

- When A/D conversion is completed in one-shot mode or single sweep mode.

- When 0 is written to this bit by software. (A/D conversion stops)

- [Conditions for setting to 1]

- When 1 is written to this bit by software. (A/D conversion starts)

- When the A/D conversion start trigger enabled by the TRCADCR register is input.

- When an external trigger ( $\overline{\text{ADTRG}}$ ) is input.

| Table 17.6 | A/D Conversion Tim | е |

|------------|--------------------|---|

|            |                    | • |

|                                                |        |                      | A/                      | D Conversion Clo | ock        |          |

|------------------------------------------------|--------|----------------------|-------------------------|------------------|------------|----------|

|                                                | Symbol | f1                   | f2                      | f4               | f8         | fAD      |

| Item                                           |        | CKS0 = 1             | CKS0 = 0                | CKS0 = 1         | CKS0 = 0   | CKS0 = 0 |

|                                                |        | CKS                  | 1 = 1                   | CKS              | CKS1 = 0   |          |

|                                                |        |                      | CKS2 = 1 <sup>(2)</sup> |                  |            |          |

| A/D conversion start delay time <sup>(3)</sup> | tD     | 3                    | 3 to 4                  | 3 to 6           | 3 to 10    | 3        |

| Input sampling time                            | tSPL   | 16                   | 31                      | 61               | 121        | 16       |

| A/D comparison time                            | tCMP   | 25                   | 50                      | 100              | 200        | 25       |

| A/D conversion time                            | tCONV  | 44                   | 84 to 85                | 164 to 167       | 324 to 331 | 44       |

| End processing time                            | tEND   | 2 to 3 cycles of fAD |                         |                  |            |          |

CKS0, CKS1, CKS2: Bits in ADMOD register

Notes:

1. The numerical values in the table indicate the number of system clock (f) cycles.

2. The numerical values in the table indicate the number of fAD cycles.

3. In repeat mode, single sweep mode, and repeat sweep mode, there is no delay time during the A/D conversion time (tCONV) for the second and subsequent rounds.

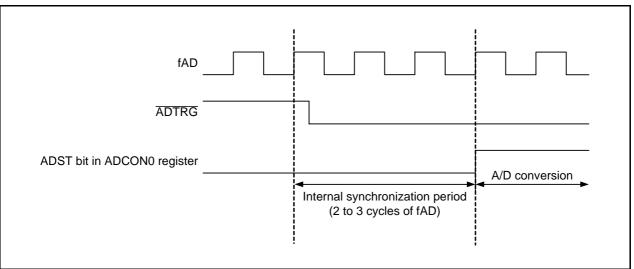

# 17.3.1.2 External Trigger Input Timing

A/D conversion can also be started by an external trigger input. When bits ADCAP1 to ADCAP0 in the ADMOD register are 11b (A/D conversion is started by external trigger ( $\overline{ADTRG}$ )), an external trigger can be input to the  $\overline{ADTRG}$  pin. The ADST bit in the ADCON0 register is set to 1 (A/D conversion starts) on the rising edge of the  $\overline{ADTRG}$  input pin and A/D conversion is started. Other operations are the same as when the ADST bit in the ADCON0 register set to 1 by software.

Figure 17.3 shows the External Trigger Input Timing.

#### FST2 Bit (LBDATA monitor flag)

This is a read-only bit indicating the lock bit status. To confirm the lock bit status, execute the read lock bit status command and then read the FST2 bit after the FST7 bit is set to 1 (ready).

This bit is updated when the program, erase, and read lock bit status commands are generated. When the read lock bit status command is input, the FST7 bit is set to 0 (busy). When the FST7 bit is set to 1 (ready), the lock bit status is stored in the FST2 bit. The data in the FST2 bit is retained until the next command is input.

## FST3 Bit (Program-suspend status flag)

This is a read-only bit indicating the suspend status. This bit is set to 1 when a program-suspend request is acknowledged and a program-suspend status is entered; otherwise it is set to 0.

#### FST4 Bit (Program error status flag)

This is a read-only bit indicating the auto-programming status. The bit is set to 1 if a program error occurs; otherwise it is set to 0. For details, see the description in **19.6.7 Full Status Check**.

#### FST5 Bit (Erase error/blank check error status flag)

This is a read-only bit indicating the status of auto-erase or block blank check command. The bit is set to 1 if an erase error or blank check error occurs; otherwise it is set to 0. For details, see the description in **19.6.7 Full Status Check**.

#### FST6 Bit (Erase-suspend status flag)

This is a read-only bit indicating the suspend status. This bit is set to 1 when an erase-suspend request is acknowledged and an erase-suspend status is entered; otherwise it is set to 0.

## FST7 Bit (Ready/busy status flag)

When the FST7 bit is set to 0 (busy), the flash memory is in one of the following states:

- During programming

- During erasure

- During the lock bit program

- During the read lock bit status

- During the block blank check

- During forced stop operation

- The flash memory is being stopped

- The flash memory is being activated

Otherwise, the FST7 bit is set to 1 (ready).

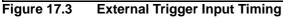

Suspend Enabled)

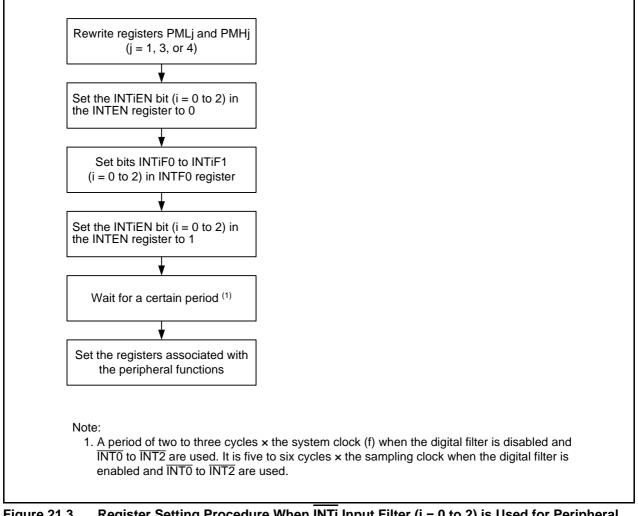

# 21.5.6 Setting Procedure When INTi Input Filter (i = 0 to 2) is Used for Peripheral Functions

Figure 21.3 shows the Register Setting Procedure When  $\overline{INTi}$  Input Filter (i = 0 to 2) is Used for Peripheral Functions (Timer RJ2, Timer RB2, and Timer RC).

Figure 21.3 Register Setting Procedure When INTi Input Filter (i = 0 to 2) is Used for Peripheral Functions (Timer RJ2, Timer RB2, and Timer RC)

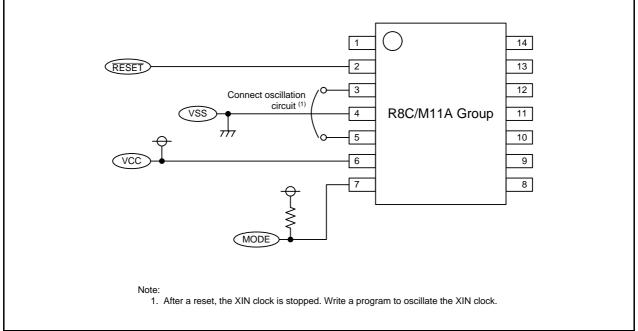

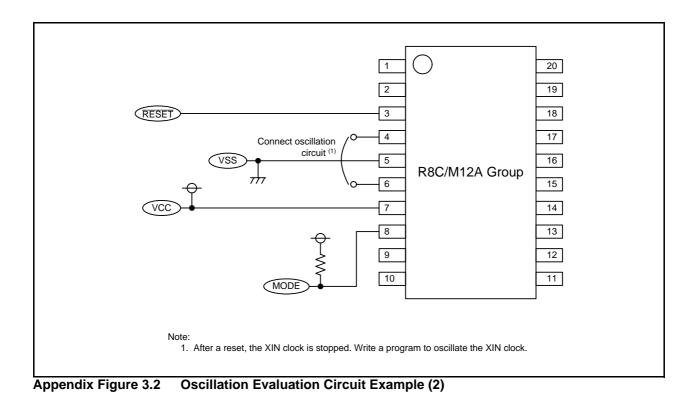

# Appendix 3. Oscillation Evaluation Circuit Example

Appendix Figures 3.1 and 3.2 show Oscillation Evaluation Circuit Examples.

Appendix Figure 3.1 Oscillation Evaluation Circuit Example (1)

#### SALES OFFICES

**Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renessas.com/" for the latest and detailed information.

Renesas Electronics America Inc.

2880 Scott Bouloward Samta Clara, CA 95050-2554, U.S.A.

Tel: +1408-588-6000, Fax: +1408-588-6130

Renesas Electronics Canada Limited

1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada

Tel: +1905-898-5441, Fax: +11-905-898-3220

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +44-182-585-100, Fax: +44-1028-585-900

Renesas Electronics Europe Limited

Trel: +44-182-585-100, Fax: +44-1028-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany

Tel: +49-11-65030, Fax: +44-1028-503-1327

Renesas Electronics (China) Co., Ltd.

Th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China

Tel: +49-11-55030, Fax: +48-21-18650-3127

Renesas Electronics (Shanghai) Co., Ltd.

Unit 204, 205, A2IA Center, No.1233 Lujazul Ring Rd., Pudong District, Shanghai 200120, China

Tel: +49-11-85030, Fax: +452-2886-7898

Renesas Electronics (Shanghai) Co., Ltd.

Unit 204, 205, AZIA Center, No.1233 Lujazul Ring Rd., Pudong District, Shanghai 200120, China

Tel: +482-1-5877-1818, Fax: +486-21-6867-78387

Renesas Electronics Taiwan Co., Ltd.

Unit 204, 205, AZIA Center, No.1233 Lujazul Ring Rd., Pudong District, Shanghai 200120, China

Tel: +482-1869-9318, Fax: +485-2386-0229044

Renesas Electronics Taiwan Co., Ltd.

Unit 104, 1051, 16/F, Tower 2, Grand Century Place, 139 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2486-9318, Fax: +485-2486-921994

Renesas Electronics Singapore Pte. Ltd.

In AntowirFord Areau, #65-078-980

Renesas Electronics Singapore Pte. Ltd.

In AntowirFord Areau, #66-078-8901

Renesas Electronics Singapore Pte. Ltd.

In AntowirFord Areaus, #66-078-9805

Renesas Electronics Singapore Pte. Ltd.

In AntowirFord Areaus, #66-078-9805

Renesas Electronics Korea Co., Ltd.

In Genesas Electronics Korea Co., Ltd.

In Genesa Electronics Korea Co., Ltd.

In Genesas Electronics Korea Co., Ltd.

In Genesa Electro

© 2012 Renesas Electronics Corporation. All rights reserved. Colophon 1.1