#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 16MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SCI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 47                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-BQFP                                                                     |

| Supplier Device Package    | 64-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36074lhv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3. Register Notation

The symbols and terms used in register diagrams are described below.

| Address XXXXh<br><u>Bit</u> <u>b7</u> <u>b6</u> <u>b5</u> <u>b4</u> <u>b3</u> <u>b2</u> <u>b1</u> <u>b0</u><br><u>After Reset</u> <u>0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | x.x.x                                                                                                                                              | XXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Regi | ster (Sy | mbol)            |            |                               |                    |               |               |           |     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------------------|------------|-------------------------------|--------------------|---------------|---------------|-----------|-----|--|--|

| Symbol       XXX7       XXX6       XXS5       -       -       -       XXX1       XXX0       *1         After Reset       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                             | Address XXXXXh                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |          |                  |            |                               |                    |               |               |           |     |  |  |

| After Reset       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <th< td=""><td></td><td></td><td></td><td>b6</td><td>b5</td><td>b4</td><td>b3</td><td>b2</td><td>b1</td><td>b0</td><td></td><td></td></th<>                                                                                                                                                                        |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | b6       | b5               | b4         | b3                            | b2                 | b1            | b0            |           |     |  |  |

| Bit       Symbol       Bit Name       Function       R/W         bit       0 0: XXX       0 0: XXX       R/W         b1       XX1       0 1: XXX       R/W         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b4       -       .       W       W         b6       XXX6       XXX bits       Function varies depending on the operating mode.       R/W         b7       XXX7       XXX bit       0: XXX       R       R/W         b7       XXX7       XXX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         r       R/W       R       0: XXX       R       R/W         r       R                                                                                                                                                                                                                                                 | Sy                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |          |                  |            |                               |                    |               |               |           |     |  |  |

| b0       XXX0       XXX bit       b1 to       0: XXX       RWW         b1       XXX1       VX bit       0: XXX       0: XXX       RWW         b1       XXX1       VX bit       0: XXX       0: XXX       RWW         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -       -         b3       -       Reserved       Set to 0.       W       W         b4       -       -       Set to 0.       W         b6       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       IV       0: XXX       R       R/W         b7       XX7       XXX bit       0: XXX       R       R/W         b7       XX7       XXX bit       0: XXX       R/W       R/W         k7/W: Read and write.       R:       R:       R:       R       R/W         k7/W: Sead and write. </td <td>After F</td> <td colspan="13"></td>                                                                                                                                                                    | After F                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |          |                  |            |                               |                    |               |               |           |     |  |  |

| b1       XXX1       0 0: XXX       RW         b1       XXX1       0 1: XXX       0 1: XXX         0 D: XXX       0 1: XXX       0 1: XXX         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b6       XXX6       Function varies depending on the operating mode.       RW         b7       XXX7       XXX bits       Function varies depending on the operating mode.       RW         b7       XXX7       XX bit       0: XXX       R         *1       R/W: Read and write.       R:       Read only.       *2       *3         *1       R/W: Read and write.       R:       Read only.       *2       *3         *2       *3       *3       *1       *2       *3         *3       •Nothing is assigned.       Nothing is assigned.       Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         •Do not set.       Operation is not guaranteed when a value is set.       •The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                                                                                     | Bit Symbol Bit Name Function R                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |          |                  |            |                               |                    |               |               |           | R/W |  |  |

| b1       XXX1       01: XXX       RW         10: Do not set.       11: XXX       10: Do not set.       11: XXX         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b6       XXX5       XXX bits       Function varies depending on the operating mode.       RW         b6       XXX6       XXX bits       0: XXX       R         b7       XXX7       XXX bit       0: XXX       R         *1       R/W: Read and write.       R: Read only.       *         *2       *3       *       *       *         *1       Nothing is assigned.       *       *         *2       *3       *       *       *         *2       *3       *       *       *         *3       •       Nothing is assigned.       *       •         Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.       •       •         •       Do not set.       •       •       •       •         •       Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.       • <td>b0</td> <td>XXX0</td> <td>XXX</td> <td>bit</td> <td></td> <td></td> <td></td> <td>v</td> <td></td> <td></td> <td></td> <td>R/W</td> | b0                                                                                                                                                 | XXX0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | XXX  | bit      |                  |            |                               | v                  |               |               |           | R/W |  |  |

| b3       —       Reserved       Set to 0.       W         b4       —       Set to 0.       W         b5       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       W       R/W       R/W         b7       XXX7       XXX bit       0: XXX       R         b7       XX7       XXX bit       0: XXX       R         *2       *3       *3       *1       R/W Read and write.         *2       *3       *3       *1       *3         • Nothing is assigned.       *3       *1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                    | XXX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |          |                  |            | 0 1: XX<br>1 0: Do<br>1 1: XX | X<br>not set.<br>X |               |               |           | R/W |  |  |

| b4       -         b5       XXX5         b6       XXX6         b7       XXX7         b7       XXX7         xxx       bit         b7       XXX7         xxx       0: XXX         b7       XXX7         xxx       0: XXX         b7       XXx7         xxx bit       0: XXX         1: XXX       R         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       Reserved         Reserved       Reserved         Reserved       Reserved         Reserved       Set to the specified value.         *3       Nothing is assigned.         Nothing is assigned.       Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         *Do not set.       Operation is not guaranteed when a value is set.         *Function varies depending on the operating mode.       For information on the individual modes, see the                                                                                                                                                                                                                                                                         | b2                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |          | ned. The w       | rite value |                               |                    | value is un   | defined.      |           | —   |  |  |

| b5       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       R       R         b7       XXX7       XXX bit       0: XXX       R         b7       XXX7       XXX bit       0: XXX       R         *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *1       *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *3       *1       *3       *1         *3       *10 thing is assigned.       Nothing is assigned.       Nothing is assigned.       *0 on to set.         Operation is not guaranteed when a value is set.       *1       *1       *1       *1         • Function or aries depending on the operating mode.       *1       *1       *1       *1         *1       R       *2       *3       *3       *2       *3       *3         • Nothing is assigned.       Nothing is assigned.                                                                                                                                                                                          |                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Rese | rved     |                  |            | Set to 0.                     |                    |               |               |           | W   |  |  |

| b6       XXX6       R/W         b7       XXX7       XXX bit       0: XXX         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *3       *1         *3       *1         *3       *3         *3       *3         *10       Nothing is assigned.         Nothing is assigned.       Nothing is assigned.         Nothing is assigned.       Nothing is assigned.         *4       *3         • Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         • Do not set.       Operation is not guaranteed when a value is set.         • Function varies depending on the operating mode.       The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | <u> </u> |                  |            |                               |                    |               |               |           |     |  |  |

| b7       XXX7       XXX bit       0: XXX<br>1: XXX       R         *2       *3         *1       R/W: Read and write.         R: Read only.       *2       *3         *1       R/W: Read and write.       R: Read only.         W: Write only.       -: Nothing is assigned.       *3         *2       *3       *1         *3       • Nothing is assigned.       *3         Nothing is assigned.       Nothing is assigned.         *0 portation is not guaranteed when a value is set.       *1         • Function varies depending on the operating mode.       The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | bits     |                  |            | Function                      | i varies de        | pending on    | the operation | ing mode. |     |  |  |

| <ul> <li>1: XXX</li> <li>*2</li> <li>*3</li> <li>*1 R/W: Read and write. R: Read only. W: Write only. —: Nothing is assigned. </li> <li>*2</li> <li>• Reserved Reserved Reserved Reserved to the specified value. </li> <li>*3 • Nothing is assigned. Nothing is assigned. Nothing is assigned. Do not set. Operation is not guaranteed when a value is set. • Function varies depending on the operating mode. The function of the bit varies with the peripheral function mode. For information on the individual modes, see the</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VVV  | L :4     | $ \rightarrow -$ |            | 0. VVV                        |                    | $\setminus$ — |               |           |     |  |  |

| <ul> <li>*2 *3</li> <li>*1 R/W: Read and write. R: Read only. W: Write only. —: Nothing is assigned. </li> <li>*2 </li> <li>*2 </li> <li>*2 </li> <li>*3 Nothing is assigned. Nothing is assigned. Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0. *3 • Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0. • Do not set. Operation is not guaranteed when a value is set. • Function varies depending on the operating mode. The function of the bit varies with the peripheral function mode. For information on the individual modes, see the</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 07                                                                                                                                                 | ~~~/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ~~~  | DIT      |                  |            |                               |                    | $\backslash$  |               |           | ĸ   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W: RG<br>R: Read<br>W: Writ<br>—: Noth<br>*2<br>• Reserve<br>Reserve<br>*3<br>• Nothing<br>Nothin<br>• Do not s<br>Opera<br>• Function<br>The fu | <ul> <li>*1 <ul> <li>R/W: Read and write.</li> <li>R: Read only.</li> <li>W: Write only.</li> <li>: Nothing is assigned.</li> </ul> </li> <li>*2 <ul> <li>Reserved</li> <li>Reserved bits. Set to the specified value.</li> </ul> </li> <li>*3 <ul> <li>Nothing is assigned.</li> <li>Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.</li> </ul> </li> <li>Do not set. <ul> <li>Operation is not guaranteed when a value is set.</li> </ul> </li> <li>Function varies depending on the operating mode. <ul> <li>The function of the bit varies with the peripheral function mode. For information on the individual modes, see the</li> </ul> </li> </ul> |      |          |                  |            |                               |                    |               |               |           |     |  |  |

| 10.4    | Stop Mode                                                                  |     |

|---------|----------------------------------------------------------------------------|-----|

| 10.4.1  | Entering Stop Mode                                                         |     |

| 10.4.2  | Pin States in Stop Mode                                                    |     |

| 10.4.3  | Returning from Stop Mode                                                   | 102 |

| 10.5    | Reducing Power Consumption                                                 |     |

| 10.5.1  | Voltage Detection Circuit                                                  |     |

| 10.5.2  | Ports                                                                      |     |

| 10.5.3  | Clocks                                                                     |     |

| 10.5.4  | Wait Mode and Stop Mode                                                    |     |

| 10.5.5  | Stopping Peripheral Function Clocks                                        |     |

| 10.5.6  | Timers                                                                     |     |

| 10.5.7  | A/D Converter                                                              | 104 |

| 10.5.8  | Serial Interface (UART0)                                                   | 104 |

| 10.5.9  | Reducing Internal Power Consumption                                        | 105 |

| 10.5.10 | O Stopping Flash Memory                                                    | 106 |

| 10.5.11 | Low-Current-Consumption Read Mode                                          | 107 |

| 10.6    | Notes on Power Control                                                     | 108 |

| 10.6.1  | Program Restrictions When Entering Wait Mode                               | 108 |

| 10.6.2  | Program Restrictions When Entering Stop Mode                               | 108 |

|         |                                                                            |     |

|         | rrupts                                                                     |     |

|         | Overview                                                                   |     |

|         | Registers                                                                  |     |

| 11.2.1  | External Input Enable Register (INTEN)                                     |     |

| 11.2.2  | INT Input Filter Select Register 0 (INTF0)                                 |     |

| 11.2.3  | INT Input Edge Select Register 0 (ISCR0)                                   |     |

| 11.2.4  | Key Input Enable Register (KIEN)                                           |     |

| 11.2.5  | Interrupt Priority Level Register i (ILVLi) (i = 0, or 2 to E)             |     |

| 11.2.6  | Interrupt Monitor Flag Register 0 (IRR0)                                   |     |

| 11.2.7  | Interrupt Monitor Flag Register 1 (IRR1)                                   |     |

| 11.2.8  | Interrupt Monitor Flag Register 2 (IRR2)                                   |     |

| 11.2.9  | External Interrupt Flag Register (IRR3)                                    |     |

| 11.2.10 |                                                                            |     |

| 11.2.11 |                                                                            |     |

|         | Interrupts and Interrupt Vectors                                           |     |

| 11.3.1  | Fixed Vector Table                                                         |     |

| 11.3.2  | Relocatable Vector Table                                                   |     |

|         | Interrupt Control                                                          |     |

| 11.4.1  | I Flag                                                                     |     |

| 11.4.2  | Registers IRR0 to IRR3                                                     |     |

| 11.4.3  | Interrupt Priority Levels in ILVLi Register ( $i = 0$ , or 2 to E) and IPL |     |

| 11.4.4  | Interrupt Sequence                                                         |     |

| 11.4.5  | Interrupt Response Time                                                    |     |

| 11.4.6  | IPL Change When Interrupt Request is Acknowledged                          |     |

| 11.4.7  | Saving Registers                                                           |     |

| 11.4.8  | Returning from Interrupt Routine                                           |     |

| 11.4.9  | Interrupt Priority                                                         |     |

| 11.4.10 |                                                                            |     |

| 11.5    | INT Interrupt                                                              | 130 |

## 9.2.6 Clock Control Register When Returning from Modes (CKRSCR)

| Address 00025h |        |        |        |    |       |       |       |       |  |  |  |  |

|----------------|--------|--------|--------|----|-------|-------|-------|-------|--|--|--|--|

| Bit            | b7     | b6     | b5     | b4 | b3    | b2    | b1    | b0    |  |  |  |  |

| Symbol         | STOPRS | WAITRS | PHISRS | _  | CKST3 | CKST2 | CKST1 | CKST0 |  |  |  |  |

| After Reset    | 0      | 0      | 0      | 0  | 0     | 0     | 0     | 0     |  |  |  |  |

| Bit | Symbol | Bit Name                               | Function                                         | R/W |

|-----|--------|----------------------------------------|--------------------------------------------------|-----|

| b0  | CKST0  | Clock oscillator circuit oscillation   | Number of wait states                            | R/W |

| b1  | CKST1  | stabilization state select bits        | b3 b2 b1 b0<br>0 0 0 0: 4                        | R/W |

| b2  | CKST2  |                                        | 0001:16                                          | R/W |

| b3  | CKST3  |                                        | 0 0 1 0: 32                                      | R/W |

|     |        |                                        | 0011:64                                          |     |

|     |        |                                        | 0 1 0 0: 128                                     |     |

|     |        |                                        | 0 1 0 1: 256                                     |     |

|     |        |                                        | 0 1 1 0: 512                                     |     |

|     |        |                                        | 0 1 1 1: 1024                                    |     |

|     |        |                                        | 1 0 0 0: 2048                                    |     |

|     |        |                                        | 1 0 0 1: 4096                                    |     |

|     |        |                                        | 1 0 1 0: 8192                                    |     |

|     |        |                                        | 1 0 1 1: 16384                                   |     |

|     |        |                                        | 1 1 0 0: 32768                                   |     |

|     |        |                                        | 1 1 0 1: 65536                                   |     |

|     |        |                                        | 1 1 1 0: 131072                                  |     |

|     |        |                                        | 1 1 1 1: 262144                                  |     |

| b4  |        | Nothing is assigned. The write value m | nust be 0. The read value is 0.                  | —   |

| b5  | PHISRS | CPU clock division select bit when     | 0: The value set in bits PHISSEL0 to PHISSEL2 in | R/W |

|     |        | returning from wait mode or stop       | the SCKCR register is valid                      |     |

|     |        | mode                                   | 1: No division                                   |     |

| b6  | WAITRS | System base clock select bit when      | 0: Return using the system base clock used       | R/W |

|     |        | returning from wait mode               | immediately before entering wait mode            |     |

|     |        |                                        | 1: fHSCK <sup>(1, 2)</sup>                       |     |

| b7  | STOPRS | System base clock select bit when      | 0: Return using the system base clock used       | R/W |

|     |        | returning from stop mode               | immediately before entering stop mode            |     |

|     |        |                                        | 1: fHSCK <sup>(1, 2)</sup>                       |     |

Notes:

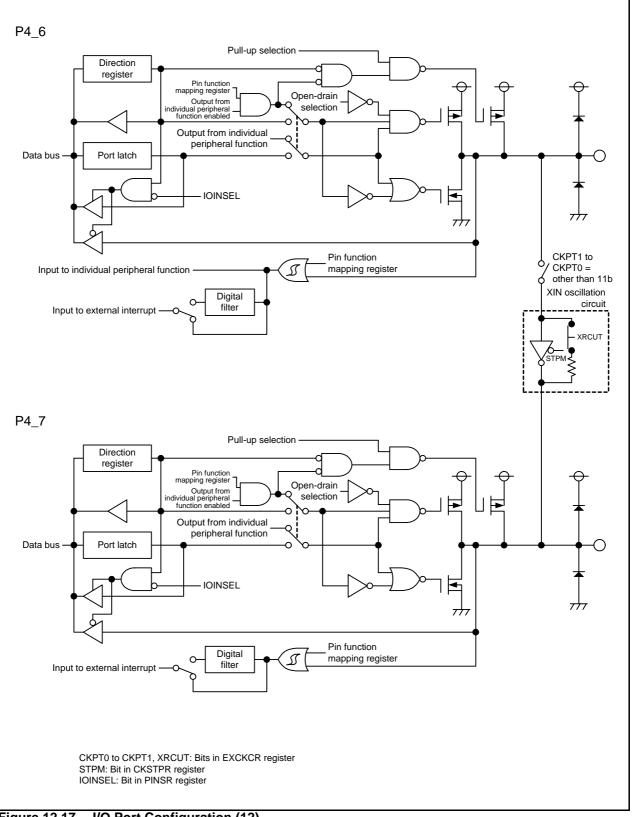

1. When the HSCKSEL bit in the SCKCR register is 0 (XIN clock), set pins P4\_6 and P4\_7 to XIN oscillation by a program before entering wait mode or stop mode.

2. Set this bit to 0 before entering wait mode or stop mode if the FMR27 bit in the FMR2 register is set to 1 (low-current-consumption read mode enabled).

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the CKRSCR register.

register.

R/W R/W

#### 9.2.9 High-Speed On-Chip Oscillator 18.432 MHz Control Register 1 (FR18S1)

| Addr     | ress 0                                                                                           | 0065h                                               |    |    |           |            |    |    |    |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|----|----|-----------|------------|----|----|----|--|--|--|--|

|          | Bit                                                                                              | b7                                                  | b6 | b5 | b4        | b3         | b2 | b1 | b0 |  |  |  |  |

| Syn      | nbol                                                                                             |                                                     | —  | _  |           | —          |    |    |    |  |  |  |  |

| After Re | eset                                                                                             |                                                     |    |    | Value whe | en shipped |    |    | •  |  |  |  |  |

|          |                                                                                                  |                                                     |    |    |           |            |    |    |    |  |  |  |  |

| Bit      |                                                                                                  | Function                                            |    |    |           |            |    |    |    |  |  |  |  |

| b7 to b0 | Freq                                                                                             | Frequency adjustment data for 18.432 MHz is stored. |    |    |           |            |    |    |    |  |  |  |  |

|          | The frequency of the high-speed on-chip oscillator can be adjusted to 18.432 MHz by transferring |                                                     |    |    |           |            |    |    |    |  |  |  |  |

|          | this value to the FRV2 register and the adjustment value in the FR18S0 register to the FRV1      |                                                     |    |    |           |            |    |    |    |  |  |  |  |

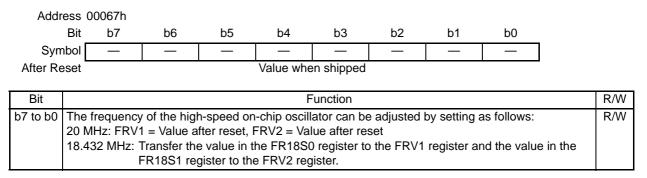

## 9.2.10 High-Speed On-Chip Oscillator Control Register 1 (FRV1)

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the FRV1 register.

#### 9.2.11 High-Speed On-Chip Oscillator Control Register 2 (FRV2)

| Bit      | Function                                                                                        | R/W |

|----------|-------------------------------------------------------------------------------------------------|-----|

| b7 to b0 | The frequency of the high-speed on-chip oscillator can be adjusted by setting as follows:       | R/W |

|          | 20 MHz: FRV1 = Value after reset, FRV2 = Value after reset                                      |     |

|          | 18.432 MHz: Transfer the value in the FR18S0 register to the FRV1 register and the value in the |     |

|          | FR18S1 register to the FRV2 register.                                                           |     |

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the FRV2 register.

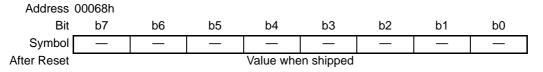

Figure 10.1 shows the Power Control State Transition Diagram.

#### **10.2 Standard Operating Mode**

In standard operating mode, the system clock is supplied to operate the CPU and the peripheral functions. Power consumption control is implemented by controlling the frequency of the system clock or CPU clock.

The higher the CPU clock frequency, the higher processing power. The lower the CPU clock frequency, the lower the power consumption. Stopping unnecessary oscillation circuits will further reduce power consumption.

When the clock sources for the CPU clock are switched, the new clock needs to be oscillating and stable. Assure the wait time for the new clock oscillation to stabilize by a program before switching the clocks.

Table 10.2 lists the Register Settings in Standard Operating Mode.

| Table 10.2 | Register Settings in Standard Operating Mode |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

|                                    | Register               | OCOCR                   |                         | SCKCR        | CKSTPR          | EXC          | KCR            |

|------------------------------------|------------------------|-------------------------|-------------------------|--------------|-----------------|--------------|----------------|

| Mode                               | Bit                    | HOCOE                   | LOCODIS                 | HSCKSEL      | SCKSEL          | CKPT1        | CKPT0          |

| Mode                               | Content to be Switched | fHOCO<br>Oscillate/Stop | fLOCO<br>Oscillate/Stop | XIN/fHOCO    | fLOCO/<br>fHSCK | P4_6 and P4_ | 7 Pin Function |

| High-speed clock mode              |                        | _                       | _                       | 0<br>(XIN)   | 1<br>(fHSCK)    | 1            | 1              |

| High-speed on-chip oscillator mode |                        | 1<br>(oscillate)        | _                       | 1<br>(fHOCO) | 1<br>(fHSCK)    | —            | —              |

| Low-speed on-chip oscillator mode  |                        | _                       | 0<br>(oscillate)        |              | 0<br>(fLOCO)    | _            | _              |

-: Indicates that either 0 or 1 can be set.

The setting in () is selected.

#### 10.2.1 High-Speed Clock Mode

When the HSCKSEL bit in the SCKCR register is 0 (XIN clock) and the SCKSEL bit in the CKSTPR register is 1 (fHSCK), the XIN clock is used as the system base clock (fBASE). At this time, the system clock is obtained by dividing the XIN clock by any value from 1 (no division) to 256. The CPU clock is obtained by dividing the system clock by 1 (no division), 2, 4, 8, 16, or 32. Also, the peripheral function clock is obtained by dividing the system clock with the prescaler. In addition, fHOCO can be used as the peripheral function clock when the HOCOE bit in the OCOCR register is 1 (high-speed on-chip oscillator on), and fLOCO when the LOCODIS bit is 0 (low-speed on-chip oscillator on).

#### 10.2.2 High-Speed On-Chip Oscillator Mode

When the HOCOE bit in the OCOCR register is 1 (high-speed on-chip oscillator on), the HSCKSEL bit in the SCKCR register is 1 (high-speed on-chip oscillator clock), and the SCKSEL bit in the CKSTPR register is 1 (fHSCK), the high-speed on-chip oscillator clock is used as the system base clock (fBASE). At this time, the system clock is obtained by dividing the high-speed on-chip oscillator clock by any value from 1 (no division) to 256. The CPU clock is obtained by dividing the system clock by 1 (no division), 2, 4, 8, 16, or 32. Also, the peripheral function clock is obtained by dividing the system clock with the prescaler. In addition, fLOCO can be used as the peripheral function clock when the LOCODIS bit is 0 (low-speed on-chip oscillator on).

### 10.2.3 Low-Speed On-Chip Oscillator Mode

When the LOCODIS bit in the OCOCR register is 0 (low-speed on-chip oscillator on) and the SCKSEL bit in the CKSTPR register is 0 (fLOCO), the low-speed on-chip oscillator clock is used as the system base clock (fBASE). At this time, the system clock is obtained by dividing the low-speed on-chip oscillator clock by any value from 1 (no division) to 256. The CPU clock is obtained by dividing the system clock by 1 (no division), 2, 4, 8, 16, or 32. Also, the peripheral function clock is obtained by dividing the system clock with the prescaler. In addition, fHOCO can be used as the peripheral function clock when the HOCOE bit in the OCOCR register is 1 (high-speed on-chip oscillator on).

In this mode, low-power operation can be enabled by stopping the XIN clock and the high-speed on-chip oscillator and setting the FMR27 bit in the FMR2 register to 1 (low-current-consumption read mode enabled). Furthermore, if wait mode is entered from this mode, power consumption in wait mode can be reduced even further by setting the VCA2 register LPE bit to 1 (low-power-consumption wait mode enabled). For details on how to reduce power consumption, see **10.5 Reducing Power Consumption**.

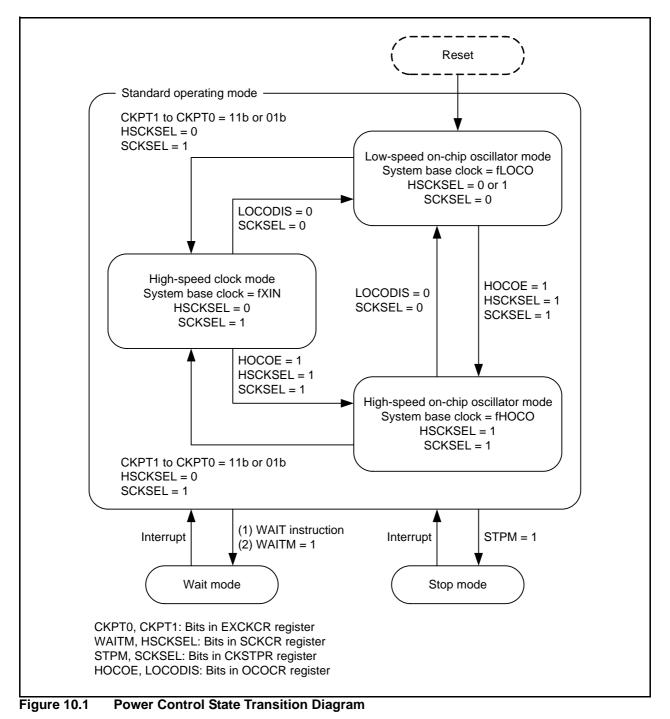

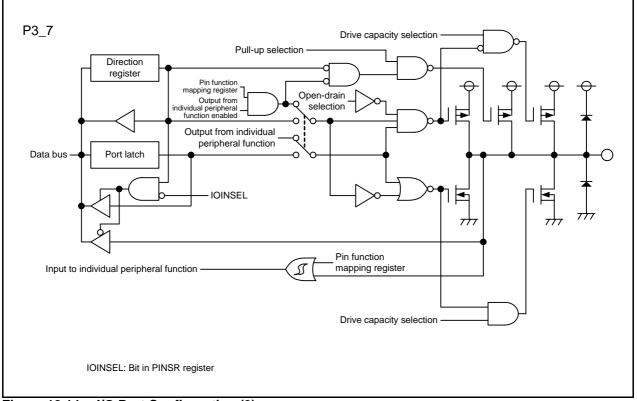

Figure 12.13 I/O Port Configuration (8)

RENESAS

Figure 12.14I/O Port Configuration (9)

## 15.2.10 Timer RC Digital Filter Function Select Register (TRCDF)

| Ado     | dress 0 | 000F          | 9h     |                                                   |               |                         |                              |             |                           |                                |     |  |

|---------|---------|---------------|--------|---------------------------------------------------|---------------|-------------------------|------------------------------|-------------|---------------------------|--------------------------------|-----|--|

|         | Bit     | b             | 7      | b6                                                | b5            | b4                      | b3                           | b2          | b1                        | b0                             |     |  |

| Sy      | mbol    | DF            | CK1    | DFCK0                                             |               | DFTRG                   | DFD                          | DFC         | DFB                       | DFA                            |     |  |

| After F | Reset   | (             | 0      | 0                                                 | 0             | 0                       | 0                            | 0           | 0                         | 0                              |     |  |

| Bit     | Symb    | ool           |        | В                                                 | it Name       |                         |                              |             | Function                  |                                | R/W |  |

| b0      | DFA     | 1             | TRC    | IOA digital                                       | filter functi | ion bit <sup>(1)</sup>  | 0: Funct                     | on is not u | sed                       |                                | R/W |  |

| b1      | DFE     | 3             | TRC    | IOB digital                                       | filter functi | ion bit <sup>(1)</sup>  | 1: Funct                     | on is used  |                           |                                | R/W |  |

| b2      | DFC     | 2             | TRC    | TRCIOC digital filter function bit <sup>(1)</sup> |               |                         |                              |             |                           |                                |     |  |

| b3      | DFD     | )             | TRC    | IOD digital                                       | filter funct  | ion bit <sup>(1)</sup>  |                              |             |                           |                                |     |  |

| b4      | DFTR    | RG            | TRC    | TRG digital                                       | filter func   | tion bit <sup>(2)</sup> |                              |             |                           |                                | R/W |  |

| b5      | _       |               | Noth   | ing is assig                                      | ned. The      | write value r           | nust be 0.                   | The read v  | alue is 0.                |                                | —   |  |

| b6      | DFC     | <b>&lt;</b> 0 | Digita | al filter cloc                                    | k select bi   | its <sup>(1, 2)</sup>   | <sup>b7 b6</sup><br>0 0: f32 |             |                           |                                | R/W |  |

| b7      | DFC     | <b>&lt;</b> 1 |        |                                                   |               |                         | 0 1: f8                      |             |                           |                                |     |  |

|         |         |               |        |                                                   |               |                         | 1 0: f1                      |             |                           |                                |     |  |

|         |         |               |        |                                                   |               |                         |                              |             | (clock seled<br>RCCR1 reg | cted by bits CKS2 t<br>gister) | :o  |  |

Notes:

1. Enabled in the input capture function.

2. Enabled when in PWM2 mode and bits TCEG1 to TCEG0 in the TRCCR2 register are set to 01b, 10b, or 11b (TRCTRG trigger input enabled).

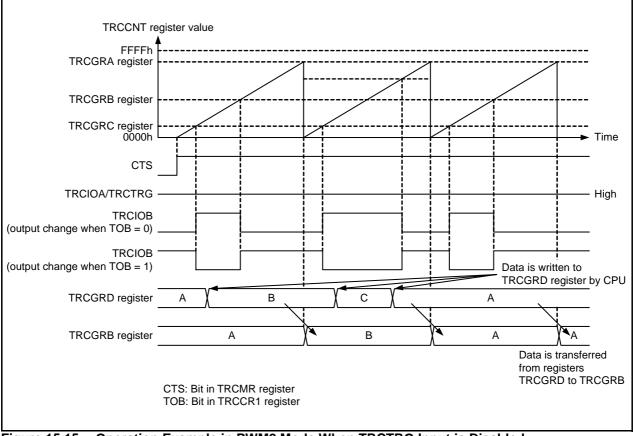

Figure 15.15 Operation Example in PWM2 Mode When TRCTRG Input is Disabled

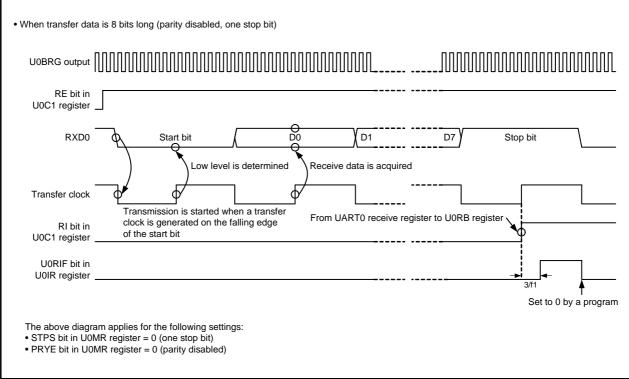

Figure 16.7 Receive Timing in Clock Asynchronous Serial I/O Mode

#### 16.4 UART0 Interrupt

The UART0 interrupt requests are the transmit buffer empty or transmit complete interrupt, and the receive complete interrupt.

Table 16.9 lists the Interrupt Requests.

#### Table 16.9 Interrupt Requests

| Interrupt Request Interrupt Generation Condition                                                          |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Transmit buffer empty U0TIF = 1 (transmit interrupt requested) and U0TIE = 1 (transmit interrupt enabled) |  |  |  |  |  |  |  |

| Transmit complete                                                                                         |  |  |  |  |  |  |  |

| Receive complete U0RIF = 1 (receive interrupt requested) and U0RIE = 1 (receive interrupt enabled)        |  |  |  |  |  |  |  |

| U0TIF, U0TIE, U0RIF, U0RIE: Bits in U0IR register                                                         |  |  |  |  |  |  |  |

Note:

1. The CPU executes interrupt exception handling when the interrupt generation conditions are met and the I flag in the FLG register is 1.

#### 17.3 Operation

This A/D converter provides operating four modes: One-shot, repeat, single sweep, and repeat sweep modes. This converter is a successive approximation type with 10-bit resolution.

The operating mode, analog input channel, and A/D conversion clock should be switched while the ADST bit in the ADCON0 register is 0 (A/D conversion stops).

#### 17.3.1 Items Common to Multiple Modes

#### 17.3.1.1 Input Sampling and A/D Conversion Time

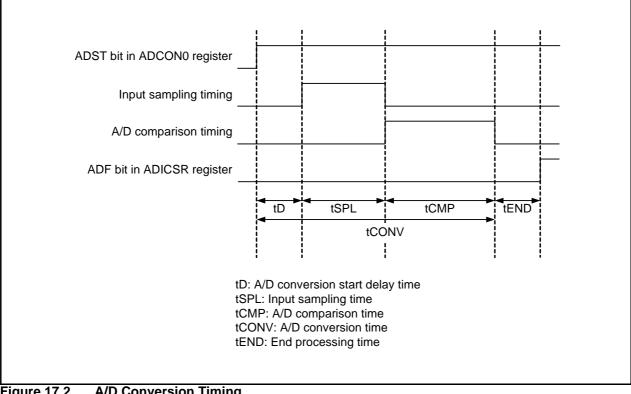

The A/D converter includes a sample and hold circuit. When the ADST bit in the ADCON0 register is set to 1 (A/D conversion starts), the A/D converter samples the input and starts conversion after the A/D conversion start delay time (tD) has elapsed.

Figure 17.2 shows the A/D Conversion Timing. Table 17.6 lists the A/D Conversion Time.

As shown in Figure 17.2, the A/D conversion time (tCONV) includes tD and the input sampling time (tSPL). Here, tD is determined by the timing for writing to the ADCON0 register and is not a fixed value. The conversion time, therefore, varies within the range shown in Table 17.6.

In one-shot mode and single sweep mode, the ADF bit in the ADICSR register is set to 1 during end processing time, and the last A/D conversion result is stored in the ADi register.

• In one-shot mode

A/D conversion time (tCONV) + end processing time (tEND)

• When two channels are selected in single sweep mode

A/D conversion time (tCONV) + A/D conversion time (tCONV with no start delay time (tD) included) + end processing time (tEND)

#### **19.6.7 Full Status Check**

If an error occurs, bits FST4 to FST5 in the FST register are set to 1, indicating the occurrence of the error. The execution result can be confirmed by checking these status bits (full status check).

Table 19.9 lists the Errors and FST Register States. Figure 19.19 shows the Full Status Check and Handling Procedures for Individual Errors.

| Table 19.9 | Errors and  | I FST Register States |  |

|------------|-------------|-----------------------|--|

| FST Regis  | ster States | Error                 |  |

| FST Register States |          | Error                  | Error Occurrence Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FST5 Bit            | FST4 Bit | Enor                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                   | 1        | Command sequence error | <ul> <li>When a command is not written correctly.</li> <li>When data other than valid data (i.e., D0h or FFh) is written as the second command of the block erase, lock bit program, read lock bit status, or block blank check command <sup>(1)</sup>.</li> <li>The erase command is executed during erase-suspend or the block blank check command is executed.</li> <li>The program, lock bit program, erase, or block blank check command is executed during program-suspend.</li> <li>The program, lock bit program, erase, or block blank check command is executed during suspend.</li> <li>The program, lock bit program, erase, or block blank check command is executed to the block during suspend.</li> <li>The lock bit program or read lock bit status commands are executed to the data flash.</li> </ul> |  |  |  |

| 1                   | 0        | Erase error            | When the block erase command is executed and auto-<br>erase does not complete normally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |          | Blank check error      | When the block blank check command is executed and data other than the blank data, FFh, is read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0                   | 1        | Program error          | When the program command is executed and auto-<br>programming does not complete normally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                     |          | Lock bit program error | When the lock bit command is executed, but the lock bit is not set to 0 (locked).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

Note:

1. When FFh is written as the second command of these commands, the MCU enters read array mode. At the same time, the command code written as the first command becomes invalid.

#### 19.8.2.3 Access Methods

To set one of the following bits to 1, first write 0 and then 1 immediately. Interrupts must be disabled between writing 0 and then writing 1.

- The FMR01 or FMR02 bit in the FMR0 register

- The FMR13 bit in the FMR1 register

- The FMR20, FMR22, or FMR27 bit in the FMR2 register

To set one of the following bits to 0, first write 1 and then 0 immediately. Interrupts must be disabled between writing 1 and then writing 0.

The FMR16 or FMR17 bit in the FMR1 register

#### 19.8.2.4 Rewriting User ROM Area

When EW0 mode is used and the supply voltage falls while rewriting a block where a rewrite control program is stored, the rewrite control program is not be rewritten correctly. As a result, it may not be possible to rewrite the flash memory afterwards. Use standard serial I/O mode to rewrite this block.

#### 19.8.2.5 Programming

Do not perform even a single additional write to an already programmed address.

#### 19.8.2.6 Entering Wait Mode or Stop Mode

Do not enter wait mode or stop mode during suspend.

When the FST7 bit in the FST register is 0 (busy) while programming or erasing the flash memory, do not enter wait mode or stop mode.

Do not set the FMR27 bit to 1 while the FMSTP bit (flash memory stop bit) in the FMR0 register is 1 (flash memory is stopped).

#### 19.8.2.7 Flash Memory Programming and Erase Voltages

When performing a program/erase operation, use a VCC supply voltage in the range of 1.8 V to 5.5 V. Do not perform a program/erase operation at less than 1.8 V.

#### 19.8.2.8 Block Blank Check

Do not execute a block blank check command during erase-suspend.

#### 19.8.2.9 EW1 Mode

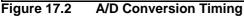

When setting the FMR01 bit in the FMR0 register to 1 (CPU rewrite mode enabled) and the FMR02 bit to 1 (EW1 mode) to execute CPU rewrite mode, follow the procedure below in EW1 mode. Figure 19.22 shows the Procedure for Software Command Execution When Suspend is Disabled. Figure 19.23 shows the Procedure for Software Command Execution When Suspend is Enabled.

|                 |                                           |                                            | Condition              |                      |                     |                   |                                               |                                                                         |          |          |      |      |

|-----------------|-------------------------------------------|--------------------------------------------|------------------------|----------------------|---------------------|-------------------|-----------------------------------------------|-------------------------------------------------------------------------|----------|----------|------|------|

| Symbol Paramete | Parameter                                 | ter                                        | Oscillation<br>Circuit | On-Chip (            | Chip Oscillator CPU |                   | Low-Power-<br>Consumption                     | Other                                                                   | Standard |          |      | Unit |

|                 |                                           |                                            | XIN (2)                | High-<br>Speed       | Low-<br>Speed       | Clock             | Setting                                       | Other                                                                   | Min.     | Тур. (3) | Max. |      |

| Icc             | Power<br>supply<br>current <sup>(1)</sup> | High-speed<br>clock mode                   | 20 MHz                 | Off                  | 125 kHz             | No<br>division    | —                                             |                                                                         | _        | 3        | 7.0  | mA   |

|                 |                                           |                                            | 16 MHz                 | Off                  | 125 kHz             | No<br>division    | —                                             |                                                                         |          | 2.5      | 6.0  | mA   |

|                 |                                           |                                            | 10 MHz                 | Off                  | 125 kHz             | No<br>division    | —                                             |                                                                         | _        | 1.7      | _    | mA   |

|                 |                                           |                                            | 20 MHz                 | Off                  | 125 kHz             | Division<br>by 8  | —                                             |                                                                         | —        | 1.5      | _    | mA   |

|                 |                                           |                                            | 16 MHz                 | Off                  | 125 kHz             | Division<br>by 8  | —                                             |                                                                         |          | 1.2      | -    | mA   |

|                 | on-c<br>osci                              |                                            | 10 MHz                 | Off                  | 125 kHz             | Division<br>by 8  | —                                             |                                                                         | _        | 1.0      | _    | mA   |

|                 |                                           | High-speed<br>on-chip                      | Off                    | 20 MHz               | 125 kHz             | No<br>division    |                                               |                                                                         |          | 3.5      | 7.5  | mA   |

|                 |                                           | oscillator<br>mode                         | Off                    | 20 MHz               | 125 kHz             | Division<br>by 8  |                                               |                                                                         |          | 2.0      | _    | mA   |

|                 |                                           |                                            | Off                    | 4 MHz <sup>(4)</sup> | 125 kHz             | Division<br>by 16 | MSTTRC = 1                                    |                                                                         | —        | 1.0      | _    | mA   |

|                 |                                           | Low-speed<br>on-chip<br>oscillator<br>mode | Off                    | Off                  | 125 kHz             | Division<br>by 8  | FMR27 = 1<br>LPE = 0                          |                                                                         | —        | 60       | 270  | μΑ   |