Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | -                                                                           |

| Core Size                  | -                                                                           |

| Speed                      | -                                                                           |

| Connectivity               | -                                                                           |

| Peripherals                | -                                                                           |

| Number of I/O              | -                                                                           |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | -                                                                           |

| EEPROM Size                | -                                                                           |

| RAM Size                   | -                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                           |

| Data Converters            | -                                                                           |

| Oscillator Type            | -                                                                           |

| Operating Temperature      | -                                                                           |

| Mounting Type              | -                                                                           |

| Package / Case             | -                                                                           |

| Supplier Device Package    | -                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36077lhv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

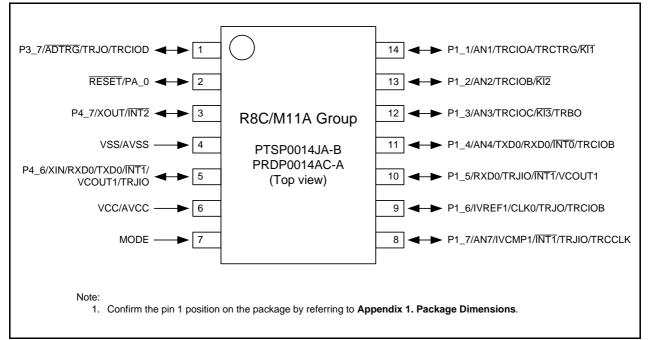

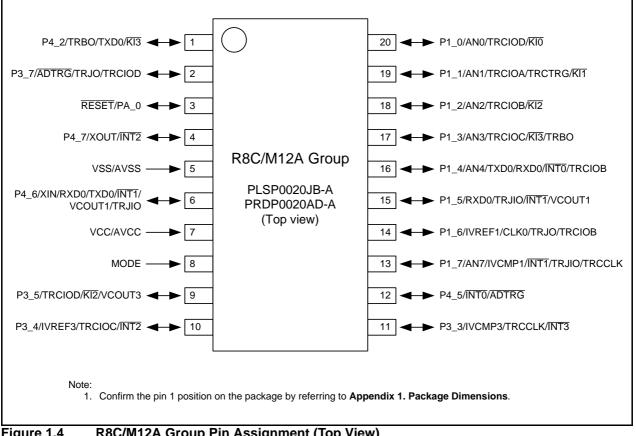

#### 1.4 **Pin Assignment**

Figures 1.3 and 1.4 show Pin Assignment (Top View). Table 1.6 lists the Pin Name Information by Pin Number.

Figure 1.3 R8C/M11A Group Pin Assignment (Top View)

R8C/M12A Group Pin Assignment (Top View) Figure 1.4

| Address                                                                                | Register Name                                                                                                                                                     | Symbol                        | After Reset                     |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------|

| 0007Ah                                                                                 | Register Hume                                                                                                                                                     | Cymbol                        |                                 |

| 0007Ah<br>0007Bh                                                                       |                                                                                                                                                                   |                               |                                 |

| 0007Ch                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0007Dh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0007Eh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0007Eh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00080h                                                                                 | UART0 Transmit/Receive Mode Register                                                                                                                              | UOMR                          | 00h                             |

| 00081h                                                                                 | UARTO Bit Rate Register                                                                                                                                           | U0BRG                         | XXh                             |

| 00081h                                                                                 | UARTO Transmit Buffer Register                                                                                                                                    | UOTBL                         | XXh                             |

| 00082h                                                                                 |                                                                                                                                                                   | UOTBH                         | XXh                             |

| 00083h<br>00084h                                                                       | UART0 Transmit/Receive Control Register 0                                                                                                                         | U0C0                          | 00001000b                       |

| 00084h                                                                                 | UARTO Transmit/Receive Control Register 0                                                                                                                         | U0C0                          | 00001000b                       |

|                                                                                        | UARTO Receive Buffer Register                                                                                                                                     | UORBL                         |                                 |

| 00086h                                                                                 | UARTU Receive Buffer Register                                                                                                                                     | UORBL                         | XXh                             |

| 00087h                                                                                 |                                                                                                                                                                   |                               | XXh                             |

| 00088h                                                                                 | UART0 Interrupt Flag and Enable Register                                                                                                                          | U0IR                          | 00h                             |

| 00089h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Ah                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Bh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Ch                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Dh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Eh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 0008Fh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00090h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00091h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00092h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00093h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00094h                                                                                 |                                                                                                                                                                   | 1                             | 1                               |

| 00095h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00096h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00097h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 00098h                                                                                 | A/D Register 0                                                                                                                                                    | ADOL                          | XXh                             |

| 00099h                                                                                 |                                                                                                                                                                   | ADOH                          | 000000XXb                       |

| 0009Ah                                                                                 | A/D Register 1                                                                                                                                                    | AD1L                          | XXh                             |

| 0009Bh                                                                                 |                                                                                                                                                                   | AD1H                          | 000000XXb                       |

| 0009Ch                                                                                 | A/D Mode Register                                                                                                                                                 | ADMOD                         | 00h                             |

| 0009Ch                                                                                 | A/D Input Select Register                                                                                                                                         | ADINSEL                       | 00h                             |

| 0009Eh                                                                                 | A/D Control Register 0                                                                                                                                            | ADCONO                        | 00h                             |

| 0009Eh                                                                                 | A/D Interrupt Control Status Register                                                                                                                             | ADICSR                        | 00h                             |

| 0009FN                                                                                 |                                                                                                                                                                   | ADICSK                        | 0011                            |

| 000A0h                                                                                 |                                                                                                                                                                   |                               |                                 |

|                                                                                        |                                                                                                                                                                   |                               |                                 |

| 000A2h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A3h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A4h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A5h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A6h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A7h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A8h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000A9h                                                                                 | Port P1 Direction Register                                                                                                                                        | PD1                           | 00h                             |

| 000AAh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000ABh                                                                                 | Port P3 Direction Register                                                                                                                                        | PD3                           | 00h                             |

| 000ACh                                                                                 | Port P4 Direction Register                                                                                                                                        | PD4                           | 00h                             |

| 000ADh                                                                                 | Port PA Direction Register                                                                                                                                        | PDA                           | 00h                             |

| 000AEh                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000AFh                                                                                 | Port P1 Register                                                                                                                                                  | P1                            | 00h                             |

| 000B0h                                                                                 |                                                                                                                                                                   |                               |                                 |

| 000B1h                                                                                 | Port P3 Register                                                                                                                                                  | P3                            | 00h                             |

| 000B2h                                                                                 | Port P4 Register                                                                                                                                                  | P4                            | 00h                             |

| 000B3h                                                                                 |                                                                                                                                                                   | PA                            | 00h                             |

|                                                                                        | Port PA Register                                                                                                                                                  |                               |                                 |

|                                                                                        | Port PA Register                                                                                                                                                  |                               |                                 |

| 000B4h                                                                                 | Port PA Register Pull-Up Control Register 1                                                                                                                       | PUR1                          | 00h                             |

| 000B4h<br>000B5h                                                                       |                                                                                                                                                                   | PUR1                          | 00h                             |

| 000B4h<br>000B5h<br>000B6h                                                             | Pull-Up Control Register 1                                                                                                                                        | PUR1<br>PUR3                  | 00h                             |

| 000B4h<br>000B5h<br>000B6h<br>000B7h                                                   | Pull-Up Control Register 1<br>Pull-Up Control Register 3                                                                                                          | PUR3                          | 00h                             |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h                                         | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4                                                                            | PUR3<br>PUR4                  | 00h<br>00h                      |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h                               | Pull-Up Control Register 1<br>Pull-Up Control Register 3                                                                                                          | PUR3                          | 00h                             |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h<br>000BAh                     | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4<br>Port I/O Function Control Register                                      | PUR3<br>PUR4<br>PINSR         | 00h<br>00h<br>00h<br>00h        |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h<br>000BAh                     | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4                                                                            | PUR3<br>PUR4                  | 00h<br>00h                      |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h<br>000BAh<br>000BBh<br>000BCh | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4<br>Port I/O Function Control Register<br>Drive Capacity Control Register 1 | PUR3<br>PUR4<br>PINSR<br>DRR1 | 00h<br>00h<br>00h<br>00h<br>00h |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h<br>000BAh<br>000BBh<br>000BCh | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4<br>Port I/O Function Control Register                                      | PUR3<br>PUR4<br>PINSR         | 00h<br>00h<br>00h<br>00h        |

| 000B4h<br>000B5h<br>000B6h<br>000B7h<br>000B8h<br>000B9h<br>000BAh<br>000BBh<br>000BCh | Pull-Up Control Register 1<br>Pull-Up Control Register 3<br>Pull-Up Control Register 4<br>Port I/O Function Control Register<br>Drive Capacity Control Register 1 | PUR3<br>PUR4<br>PINSR<br>DRR1 | 00h<br>00h<br>00h<br>00h<br>00h |

### Table 3.3SFR Information (3) (1)

X: Undefined Note:

1. The blank areas are reserved. No access is allowed.

| Address | Area Name                         | Symbol | After Reset |

|---------|-----------------------------------|--------|-------------|

| :       |                                   |        |             |

| 0FFDBh  | Option Function Select Register 2 | OFS2   | (Note 1)    |

| :       |                                   |        |             |

| 0FFDFh  | ID1                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFE3h  | ID2                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFEBh  | ID3                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFEFh  | ID4                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFF3h  | ID5                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFF7h  | ID6                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFFBh  | ID7                               |        | (Note 2)    |

| :       |                                   |        |             |

| 0FFFFh  | Option Function Select Register   | OFS    | (Note 1)    |

Table 3.9 ID Code Area and Option Function Select Area

Notes:

The option function select area is allocated in the flash memory, not in the SFRs. Set appropriate values as ROM data by a program. Do not perform an additional write to the option function select area. Erasure of the block including the option function select area causes the option function select area to be set to FFh.

When blank products are shipped, the option function select area is set to FFh. It is set to the written value after written by the user. When factory-programming products are shipped, the value of the option function select area is the value programmed by the user.

2. The ID code area is allocated in the flash memory, not in the SFRs. Set appropriate values as ROM data by a program. Do not perform an additional write to the ID code area. Erasure of the block including the ID code area causes the ID code area to be set to FFh. When blank products are shipped, the ID code areas are set to FFh. They are set to the written value after written by the user. When factory-programming products are shipped, the value of the ID code areas is the value programmed by the user.

### 5.2.1 Processor Mode Register 0 (PM0)

| Ado         | dress 00 | 010h  |                                                                      |             |             |            |             |                   |    |  |     |

|-------------|----------|-------|----------------------------------------------------------------------|-------------|-------------|------------|-------------|-------------------|----|--|-----|

|             | Bit      | b7    | b6                                                                   | b5          | b4          | b3         | b2          | b1                | b0 |  |     |

| Sy          | Symbol   |       | —                                                                    | _           | —           | SRST       | _           | —                 | _  |  |     |

| After F     | Reset    | 0     | 0                                                                    | 0           | 0           | 0          | 0           | 0                 | 0  |  |     |

| <b>D</b> '' |          |       |                                                                      | ··          |             |            |             | <b>-</b> <i>'</i> |    |  | R/W |

| Bit         | Symbo    |       | Bit Name Function                                                    |             |             |            |             |                   |    |  |     |

| b0          | —        | Noth  | Nothing is assigned. The write value must be 0. The read value is 0. |             |             |            |             |                   |    |  | —   |

| b1          | _        |       |                                                                      |             |             |            |             |                   |    |  |     |

| b2          | —        |       |                                                                      |             |             |            |             |                   |    |  |     |

| b3          | SRST     | Softv | vare reset                                                           | bit         |             | 0: State   | is retained |                   |    |  | R/W |

|             |          |       |                                                                      |             |             | 1: Reset   | is generat  | ed                |    |  |     |

| b4          | —        | Noth  | ing is assig                                                         | gned. The v | write value | must be 0. | The read v  | value is 0.       |    |  | —   |

| b5          | —        |       |                                                                      |             |             |            |             |                   |    |  |     |

| b6          | —        |       |                                                                      |             |             |            |             |                   |    |  |     |

| b7          | —        |       |                                                                      |             |             |            |             |                   |    |  |     |

Set the PRC1 bit in the PRCR register to 1 (write enabled) before rewriting the PM0 register.

### SRST Bit (Software reset bit)

When the SRST bit is set to 1, the entire MCU is reset. The read value is 0. For details, see 6. Resets.

### 6.2.2 Reset Source Determination Register (RSTFR)

| Ade     | dress 0005 | 5Fh                        |             |             |               |             |            |             |       |  |       |

|---------|------------|----------------------------|-------------|-------------|---------------|-------------|------------|-------------|-------|--|-------|

|         | Bit k      | o7                         | b6          | b5          | b4            | b3          | b2         | b1          | b0    |  |       |

| Sy      | /mbol -    | _                          | —           | —           | —             | WDR         | SWR        | HWR         | CWR   |  |       |

| After F | Reset      | 0                          | 0           | 0           | 0             | X (1)       | X (1)      | X (1)       | X (1) |  |       |

|         |            | 1                          |             | ·/ N1       |               | -           |            | <b>-</b> .: |       |  | D AA/ |

| Bit     | Symbol     |                            | В           | it Name     |               |             |            | Function    |       |  | R/W   |

| b0      | CWR        | Cold :                     | start-up/wa | arm start-u | р             | 0: Cold s   | start-up   |             |       |  | R/W   |

|         |            | determine flag             |             |             |               | 1: Warm     |            |             |       |  |       |

| b1      | HWR        | Hardware reset detect flag |             |             |               | 0: Not de   | etected    |             |       |  | R     |

|         |            |                            |             |             |               | 1: Detec    | ted        |             |       |  |       |

| b2      | SWR        | Softw                      | are reset o | detect flag |               | 0: Not de   | etected    |             |       |  | R     |

|         |            |                            |             | -           |               | 1: Detected |            |             |       |  |       |

| b3      | WDR        | Watch                      | ndog timer  | reset dete  | ect flag      | 0: Not de   | etected    |             |       |  | R     |

|         |            |                            | -           |             | -             | 1: Detected |            |             |       |  |       |

| b4      | —          | Nothi                      | ng is assig | ned. The v  | write value i | must be 0.  | The read v | value is 0. |       |  |       |

| b5      | —          |                            |             |             |               |             |            |             |       |  |       |

| b6      | —          |                            |             |             |               |             |            |             |       |  |       |

| b7      | —          |                            |             |             |               |             |            |             |       |  |       |

Note:

1. The value after a reset differs depending on the reset source.

### CWR Bit (Cold start-up/warm start-up determine flag)

This flag indicates whether a cold start-up or warm start-up has occurred. The CWR bit is set to 0 (cold start-up) after power-on or voltage monitor 0 reset. This bit remains unchanged after a hardware reset, software reset, or watchdog timer reset.

The CWR bit is set to 1 by writing 1 by a program, but writing 0 to this bit has no effect.

[Condition for setting to 0]

• When a reset occurs after power-on or voltage detection 0.

[Condition for setting to 1]

• When 1 is written to this bit by a program.

### HWR Bit (Hardware reset detect flag)

This flag indicates that a hardware reset has occurred.

[Condition for setting to 0]

• When a software reset, watchdog timer reset, power-on reset, or voltage monitor 0 reset occurs.

[Condition for setting to 1]

• When a hardware reset occurs.

### SWR Bit (Software reset detect flag)

This flag indicates that a reset has been generated by software.

[Condition for setting to 0]

• When a watchdog timer reset, hardware reset, power-on reset, or voltage monitor 0 reset occurs.

[Condition for setting to 1]

• When a software reset occurs.

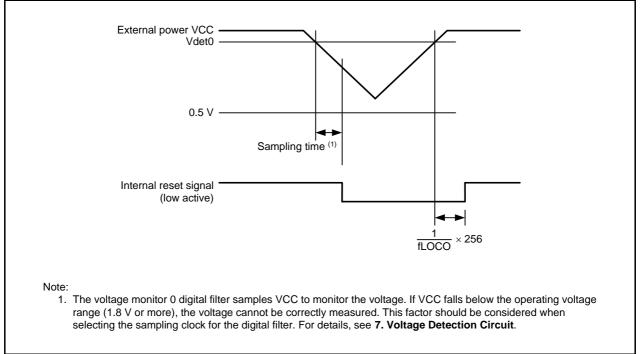

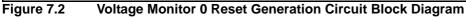

### 6.3.4 Voltage Monitor 0 Reset

The voltage monitor 0 reset is due to the on-chip voltage detection 0 circuit. The voltage detection 0 circuit monitors the voltage applied to the VCC pin. Vdet0 is the detection level. The Vdet0 level is set with bits VDSEL0 to VDSEL1 in the OFS register.

When the input voltage to the VCC pin falls to the Vdet0 level or lower, the CPU, SFRs and I/O ports are initialized. The internal RAM is not initialized. If the supply voltage falls to Vdet0 or lower while writing to the internal RAM, the RAM values will be undefined.

When the voltage applied to the VCC pin next rises to the Vdet0 level or higher, counting of the low-speed onchip oscillator clock starts. When the low-speed on-chip oscillator clock count reaches 256, the internal reset signal goes high and the MCU proceeds to the reset sequence (see Figure 6.2). The low-speed on-chip oscillator clock (no division) is automatically selected as the CPU clock after a reset.

The LVDAS bit in the OFS register can be used to enable or disable the voltage monitor 0 reset after a reset. The setting of the LVDAS bit is valid at all resets.

Bits VDSEL0 to VDSEL1, and LVDAS cannot be changed by a program. To change these bits, write values to b4 to b6 at address 0FFFFh using a flash programmer. For details on the OFS register, see **6.2.4 Option Function Select Register (OFS)**.

For details on the voltage monitor 0 reset, see **7. Voltage Detection Circuit**. Figure 6.5 shows an Example of Voltage Monitor 0 Reset Operation.

Figure 6.5 Example of Voltage Monitor 0 Reset Operation

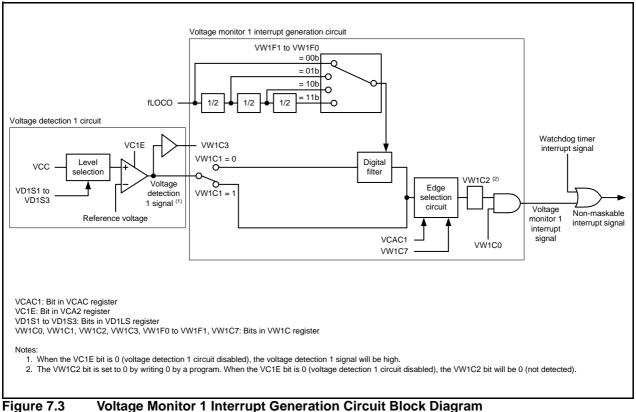

# 7.2.3 Voltage Detection 1 Level Select Register (VD1LS)

| Ado     | dress 0008 | 5Bh      |             |              |            |                                                    |                         |          |    |  |     |

|---------|------------|----------|-------------|--------------|------------|----------------------------------------------------|-------------------------|----------|----|--|-----|

|         | Bit I      | o7       | b6          | b5           | b4         | b3                                                 | b2                      | b1       | b0 |  |     |

| Sy      | mbol -     | _        |             | _            | _          | VD1S3                                              | VD1S2                   | VD1S1    |    |  |     |

| After F | Reset      | 0        | 0           | 0            | 0          | 0                                                  | 1                       | 1        | 1  |  |     |

| Dit     | Oursels al | <u> </u> |             | :4 N I       |            | 1                                                  |                         | E        |    |  |     |

| Bit     | Symbol     |          | В           | it Name      |            |                                                    |                         | Function |    |  | R/W |

| b0      | —          | Rese     | erved       |              |            | Set to 1.                                          |                         |          |    |  | R/W |

| b1      | VD1S1      | Volta    | ge detectio | on 1 level s | elect bits | b3 b2 b1                                           |                         |          |    |  |     |

| b2      | VD1S2      |          |             |              |            | 0 0 0: 2.35 V (Vdet1_1)<br>0 0 1: 2.65 V (Vdet1_3) |                         |          |    |  | R/W |

| b3      | VD1S3      |          |             |              |            |                                                    | 0 1 0: 2.95 V (Vdet1_5) |          |    |  |     |

|         |            |          |             |              |            |                                                    | 0 1 1: 3.25 V (Vdet1_7) |          |    |  |     |

|         |            |          |             |              |            | 1 0 0: 3.55 V (Vdet1_9)                            |                         |          |    |  |     |

|         |            |          |             |              |            | 101:3                                              |                         |          |    |  |     |

|         |            |          |             |              |            | 110:4                                              | .15 V (Vdet             | t1_D)    |    |  |     |

|         |            |          |             |              |            | 111:4                                              | .45 V (Vdet             | t1_F)    |    |  |     |

| b4      | _          | Rese     | erved       |              |            | Set to 0.                                          |                         |          |    |  | R/W |

| b5      |            |          |             |              |            |                                                    |                         |          |    |  |     |

| b6      | _          |          |             |              |            |                                                    |                         |          |    |  |     |

| b7      |            | 1        |             |              |            |                                                    |                         |          |    |  |     |

Set the PRC3 bit in the PRCR register to 1 (write enabled) before rewriting the VD1LS register.

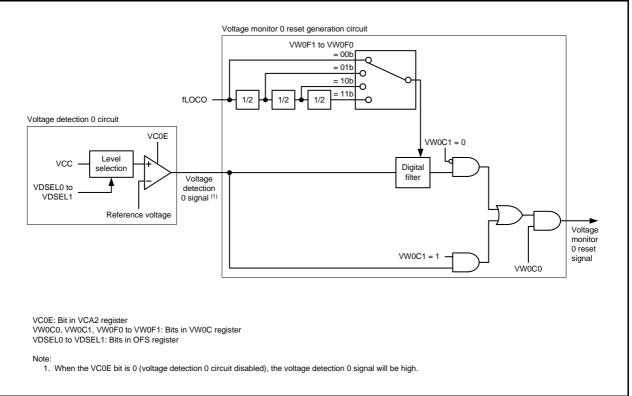

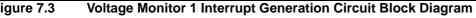

### 7.6 Digital Filter for Voltage Detection Circuits 0 and 1

Figure 7.6 shows a Block Diagram of Voltage Detection Circuit Digital Filter. In digital filter enabled mode, the voltage detection signal from the voltage detection circuit is used to generate a voltage monitor 0 reset signal and a voltage monitor 1 interrupt signal individually through the digital filter circuit. The filter width of the digital filter circuit is the sampling clock  $\times$  2.

Figure 7.6 Block Diagram of Voltage Detection Circuit Digital Filter

### 9.2.3 System Clock f Control Register (SCKCR)

| Ade      | dress 000 | )22h |                  |               |               |            |                                                  |               |               |            |  |  |

|----------|-----------|------|------------------|---------------|---------------|------------|--------------------------------------------------|---------------|---------------|------------|--|--|

|          | Bit       | b7   | b6               | b5            | b4            | b3         | b2                                               | b1            | b0            |            |  |  |

| Sy       | /mbol     |      | HSCKSEL          | WAITM         | —             | —          | PHISSEL2                                         | PHISSEL1      | PHISSEL0      |            |  |  |

| After F  | Reset     | 0    | 0                | 0             | 0             | 0          | 0                                                | 0             | 0             |            |  |  |

| <b>—</b> |           |      |                  |               |               |            |                                                  |               |               |            |  |  |

| Bit      | Symbo     |      |                  | Bit Name      |               |            |                                                  | Function      |               | R/W<br>R/W |  |  |

| b0       | PHISSE    | LO O | CPU clock divis  | sion ratio se | elect bits    | These      | These bits are used to select the division ratio |               |               |            |  |  |

| b1       | PHISSE    | L1   |                  |               |               |            | •                                                | < (f) to gene | erate the CPU | R/W        |  |  |

| b2       | PHISSE    | L2   |                  |               |               | clock      | (fs).                                            |               |               | R/W        |  |  |

|          |           |      |                  |               |               | b2 b1 b0   | fs = System                                      | clock with    | no division   |            |  |  |

|          |           |      |                  |               |               |            | fs = System                                      |               |               |            |  |  |

|          |           |      |                  |               |               |            | fs = System                                      |               | •             |            |  |  |

|          |           |      |                  |               |               | 011:       | fs = System                                      | clock divid   | led by 8      |            |  |  |

|          |           |      |                  |               |               | 100:       | fs = System                                      | clock divid   | led by 16     |            |  |  |

|          |           |      |                  |               |               |            | fs = System                                      | clock divid   | led by 32     |            |  |  |

|          |           |      |                  |               |               |            | Do not set.                                      |               |               |            |  |  |

|          |           |      |                  |               |               | 111:       | Do not set.                                      |               |               |            |  |  |

| b3       | —         | 1    | Nothing is assig | gned. The v   | vrite value m | nust be 0. | The read val                                     | ue is 0.      |               | —          |  |  |

| b4       | —         |      |                  |               |               |            |                                                  |               |               |            |  |  |

| b5       | WAITM     | ۱ ۱  | Wait control bit |               |               | 0: Not     | in wait mode                                     | е             |               | R/W        |  |  |

|          |           |      |                  |               |               | 1: Wai     | t mode is en                                     | tered         |               |            |  |  |

| b6       | HSCKS     | EL H | High-speed on-   | chip oscilla  | tor/XIN cloc  | k 0: XIN   | clock                                            |               |               | R/W        |  |  |

|          |           | 5    | select bit       |               |               | 1: Higl    | h-speed on-o                                     | chip oscillat | or clock      |            |  |  |

| b7       | _         | 1    | Nothing is assi  | gned. The v   | vrite value m | nust be 0. | The read val                                     | ue is 0.      |               | —          |  |  |

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the SCKCR register.

### Bits PHISSEL0 to PHISSEL2 (CPU clock division ratio select bits)

Bits PHISSEL2 to PHISSEL0 are set to 000b (system clock with no division) if the PHISRS bit in the CKRSCR register is 1 (no division) when the MCU returns from wait mode or stop mode.

### WAITM Bit (Wait control bit)

- [Condition for setting to 0]

- When a peripheral function interrupt is used to return from wait mode.

- [Condition for setting to 1]

- When 1 is written to the WAITM bit after the PRC0 bit in the PRCR register is set to 1 (write enabled).

### 11.3.2 Relocatable Vector Table

The relocatable vector table occupies 256 bytes beginning from the start address set in the INTB register. Table 11.6 lists the Relocatable Vector Table.

| Interrupt Source    | Vector Address <sup>(1)</sup><br>Address (L) to Address (H)               | Software Interrupt<br>Number | Priority Level Setting<br>(ILVL0 or ILVL2 to ILVLE) |

|---------------------|---------------------------------------------------------------------------|------------------------------|-----------------------------------------------------|

| BRK instruction (2) | +0 to +3 (+00000h to +00003h)                                             | 0                            |                                                     |

| Flash ready         | +4 to +7 (+00004h to +00007h)                                             | 1                            | ILVL05 to ILVL04                                    |

| Reserved            |                                                                           | 2 to 3                       | —                                                   |

| Comparator B1       | +16 to +19 (+00010h to +00013h)                                           | 4                            | ILVL21 to ILVL20                                    |

| Comparator B3       | +20 to +23 (+00014h to +00017h)                                           | 5                            | ILVL25 to ILVL24                                    |

| Reserved            | +24 to +27 (+00018h to +0001Bh)                                           | 6                            | <b>—</b>                                            |

| Timer RC            | +28 to +31 (+0001Ch to +0001Fh)                                           | 7                            | ILVL35 to ILVL34                                    |

| Reserved            | +32 to +35 (+00020h to +00023h)                                           | 8                            | <b>—</b>                                            |

| Reserved            | +36 to +39 (+00024h to +00027h)                                           | 9                            | —                                                   |

| Reserved            | +40 to +43 (+00028h to +0002Bh)                                           | 10                           | —                                                   |

| Reserved            | +44 to +47 (+0002Ch to +0002Fh)                                           | 11                           | —                                                   |

| Reserved            | +48 to +51 (+00030h to +00033h)                                           | 12                           | —                                                   |

| Key input           | +52 to +55 (+00034h to +00037h)                                           | 13                           | ILVL65 to ILVL64                                    |

| A/D conversion      | +56 to +59 (+00038h to +0003Bh)                                           | 14                           | ILVL71 to ILVL70                                    |

| Reserved            | +60 to +63 (+0003Ch to +0003Fh)                                           | 15                           | —                                                   |

| Reserved            |                                                                           | 16                           | —                                                   |

| UART0 transmission  | +68 to +71 (+00044h to +00047h)                                           | 17                           | ILVL85 to ILVL84                                    |

| UART0 reception     | +72 to +75 (+00048h to +0004Bh)                                           | 18                           | ILVL91 to ILVL90                                    |

| Reserved            | +76 to +79 (+0004Ch to +0004Fh)                                           | 19                           | —                                                   |

| Reserved            | +80 to +83 (+00050h to +00053h)                                           | 20                           | —                                                   |

| INT2                | +84 to +87 (+00054h to +00057h)                                           | 21                           | ILVLA5 to ILVLA4                                    |

| Timer RJ2           | +88 to +91 (+00058h to +0005Bh)                                           | 22                           | ILVLB1 to ILVLB0                                    |

| Periodic timer      | +92 to +95 (+0005Ch to +0005Fh)                                           | 23                           | ILVLB5 to ILVLB4                                    |

| Timer RB2           | +96 to +99 (+00060h to +00063h)                                           | 24                           | ILVLC1 to ILVLC0                                    |

| INT1                | +100 to +103 (+00064h to +00067h)                                         | 25                           | ILVLC5 to ILVLC4                                    |

| INT3                | +104 to +107 (+00068h to +0006Bh)                                         | 26                           | ILVLD1 to ILVLD0                                    |

| Reserved            |                                                                           | 27 to 28                     | 1-                                                  |

| INT0                | +116 to +119 (+00074h to +00077h)                                         | 29                           | ILVLE5 to ILVLE4                                    |

| Reserved            |                                                                           | 30                           | <b> </b>                                            |

| Reserved            |                                                                           | 31                           | <b> </b>                                            |

| Software (2)        | +128 to +131 (+00080h to +00083h) to<br>+252 to +255 (+000FCh to +000FFh) | 32 to 63                     | —                                                   |

| Table 11.6 | Relocatable Vector Table |

|------------|--------------------------|

|            |                          |

Notes:

1. These addresses are relative to those indicated by the INTB register.

2. These interrupts are not disabled by the I flag.

## 11.5 **INT** Interrupt

# 11.5.1 **INTi** Interrupt (i = 0 to 3)

The  $\overline{INTi}$  interrupt is generated by an  $\overline{INTi}$  input. To use the  $\overline{INTi}$  interrupt, set the INTiEN bit in the INTEN register is to 1 (enabled). The edge polarity can be selected by bits INTiSA to INTiSB in the ISCR0 register. The input pins used as the  $\overline{INT0}$  to  $\overline{INT2}$  input can be selected.

Inputs can be passed through a digital filter with three different sampling clocks.

The interrupt by the  $\overline{INTi}$  input can be used as a wakeup function to cancel wait mode or stop mode.

Table 11.11 lists the Pin Configuration for INTi Interrupt.

| Pin Name | Assigned Pin     | I/O | Function             |

|----------|------------------|-----|----------------------|

| INT0     | P1_4, P4_5       | I   | INT0 interrupt input |

| INT1     | P1_5, P1_7, P4_6 | I   | INT1 interrupt input |

| INT2     | P3_4, P4_7       | I   | INT2 interrupt input |

| INT3     | P3_3             | I   | INT3 interrupt input |

### Table 11.11 Pin Configuration for INTi Interrupt

### 12.3 Port 1

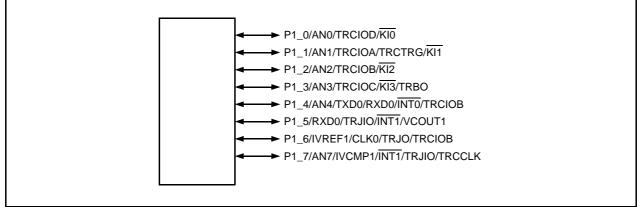

Figure 12.1 shows the Port 1 Pin Configuration.

### 12.3.1 Port P1 Direction Register (PD1)

| Ad    | dress | 000A | \9h  |                         |          |       |          |                                            |          |       |     |   |

|-------|-------|------|------|-------------------------|----------|-------|----------|--------------------------------------------|----------|-------|-----|---|

|       | Bit   | b    | 57   | b6                      | b5       | b4    | b3       | b2                                         | b1       | b0    |     |   |

| Sy    | ymbol | PD   | 1_7  | PD1_6                   | PD1_5    | PD1_4 | PD1_3    | PD1_2                                      | PD1_1    | PD1_0 |     |   |

| After | Reset |      | 0    | 0                       | 0        | 0     | 0        | 0                                          | 0        | 0     |     |   |

|       |       |      | 1    | _                       |          |       |          |                                            | Function |       |     |   |

| Bit   | Sym   | ibol |      | В                       | it Name  |       |          | R/V                                        | Ν        |       |     |   |

| b0    | PD1   | _0   | Port | P1_0 direc              | tion bit |       |          | 0: Input mode (functions as an input port) |          |       |     |   |

| b1    | PD1   | _1   | Port | P1_1 direc              | tion bit |       | 1: Outpu | utput mode (functions as an output port)   |          |       |     | W |

| b2    | PD1   | _2   | Port | P1_2 direc              | tion bit |       |          |                                            |          |       | R/V | Ν |

| b3    | PD1   | _3   | Port | P1_3 direc              | tion bit |       |          |                                            |          |       | R/V | Ν |

| b4    | PD1   | _4   | Port | P1_4 direc              | tion bit |       |          |                                            |          |       | R/V | Ν |

| b5    | PD1   | _5   | Port | Port P1_5 direction bit |          |       |          |                                            |          |       | R/V | Ν |

| b6    | PD1   | _6   | Port | P1_6 direc              | tion bit |       |          |                                            |          |       | R/V | Ν |

| b7    | PD1   | _7   | Port | P1_7 direc              | tion bit |       |          |                                            |          |       | R/V | Ν |

The PD1 register is used to select whether I/O ports are used as input or output. Each bit in the PD1 register corresponds to individual ports.

## 12.3.2 Port P1 Register (P1)

| Address     | Address 000AFh |      |      |      |      |      |      |      |  |  |  |  |

|-------------|----------------|------|------|------|------|------|------|------|--|--|--|--|

| Bit         | b7             | b6   | b5   | b4   | b3   | b2   | b1   | b0   |  |  |  |  |

| Symbol      | P1_7           | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0 |  |  |  |  |

| After Reset | 0              | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |  |

| Bit | Symbol | Bit Name      | Function      | R/W |

|-----|--------|---------------|---------------|-----|

| b0  | P1_0   | Port P1_0 bit | 0: Low level  | R/W |

| b1  | P1_1   | Port P1_1 bit | 1: High level | R/W |

| b2  | P1_2   | Port P1_2 bit |               | R/W |

| b3  | P1_3   | Port P1_3 bit |               | R/W |

| b4  | P1_4   | Port P1_4 bit |               | R/W |

| b5  | P1_5   | Port P1_5 bit |               | R/W |

| b6  | P1_6   | Port P1_6 bit |               | R/W |

| b7  | P1_7   | Port P1_7 bit |               | R/W |

The P1 register is an I/O port data register. Data input to and output from external devices are accomplished by reading from and writing to the P1 register. The P1 register consists of a port latch to retain output data and a circuit to read the pin states. The value written to the port latch is output from the pins. Each bit in the P1 register corresponds to individual ports.

### 12.8 Pin Settings for Peripheral Function I/O

Tables 12.21 to 12.24 list the pin settings for peripheral function I/O.

### Table 12.21 TRCIOA Pin Settings

| Register | TRCOER | TRCMR | Т    | RCIOR | 0    | TRCCR2 |       | Function                                             |

|----------|--------|-------|------|-------|------|--------|-------|------------------------------------------------------|

| Bit      | EA     | PWM2  | IOA2 | IOA1  | IOA0 | TCEG1  | TCEG0 | Function                                             |

|          | 0      | 1     | 0    | 0     | 1    | х      | х     | Timer mode waveform output (output compare function) |

|          | 0      | I     | 0    | 1     | Х    | ^      | ^     |                                                      |

| Setting  | 0      | 1     | 1    | х     | х    | х      | х     | Timer mode (input capture function)                  |

| value    | 1      | 1     | 1    | ^     | ^    | ^      | ^     |                                                      |

|          | 1      | 0     | v    | v     | х    | 0      | 1     | PWM2 mode (TRCTRG input)                             |

|          | I      | 0     | ~    | ~     | ^    | 1      | Х     |                                                      |

X: 0 or 1

### Table 12.22 TRCIOB Pin Settings

| Register         | TRCOER | TRC  | CMR  | TRCIOR0 |      |      | Function                                            |

|------------------|--------|------|------|---------|------|------|-----------------------------------------------------|

| Bit              | EB     | PWM2 | PWMB | IOB2    | IOB1 | IOB0 | Function                                            |

|                  | 0      | 0    | Х    | Х       | Х    | Х    | PWM2 mode waveform output                           |

| Setting<br>value | 0      | 1    | 1    | Х       | Х    | Х    | PWM mode waveform output                            |

|                  | 0      | 1    | 0    | 0       | 0    | 1    | Timer mode waveform output (output compare function |

|                  |        |      |      |         | 1    | Х    |                                                     |

|                  | 0      | 1    | 0    | 1       | х    | х    | Timer mode (input capture function)                 |

|                  | 1      | I    | 0    | 1       | ^    | ^    |                                                     |

X: 0 or 1

### Table 12.23 TRCIOC Pin Settings

| Register         | TRCOER | TRC  | CMR  | TRCIOR1 |      |      | Function                                                                                   |

|------------------|--------|------|------|---------|------|------|--------------------------------------------------------------------------------------------|

| Bit              | EC     | PWM2 | PWMC | IOC2    | IOC1 | IOC0 | T unction                                                                                  |

|                  | 0      | 1    | 1    | Х       | Х    | Х    | PWM mode waveform output                                                                   |

| Catting          | 0      | 1    | 0    | 0       | 0    | 1    | Timer mode waveform output (output compare function<br>Timer mode (input capture function) |

| Setting<br>value |        |      |      |         | 1    | Х    |                                                                                            |

|                  | 0      | 1    | 0    | 1       | х    | х    |                                                                                            |

|                  | 1      | I    | 0    |         |      |      |                                                                                            |

X: 0 or 1

#### Table 12.24 TRCIOD Pin Settings

| Register         | TRCOER | TRC  | MR   | TRCIOR1 |      |      | Function                                                                                   |

|------------------|--------|------|------|---------|------|------|--------------------------------------------------------------------------------------------|

| Bit              | ED     | PWM2 | PWMD | IOD2    | IOD1 | IOD0 | T unction                                                                                  |

|                  | 0      | 1    | 1    | Х       | Х    | Х    | PWM mode waveform output                                                                   |

| Setting<br>value | 0      | 1    | 0    | 0       | 0    | 1    | Timer mode waveform output (output compare function<br>Timer mode (input capture function) |

|                  |        |      |      |         | 1    | Х    |                                                                                            |

|                  | 0      | 1    | 0    | 1       | х    | v    |                                                                                            |

|                  | 1      | 1    | 0    | I       | ^    | X    |                                                                                            |

X: 0 or 1

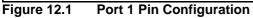

Figure 12.15 I/O Port Configuration (10)

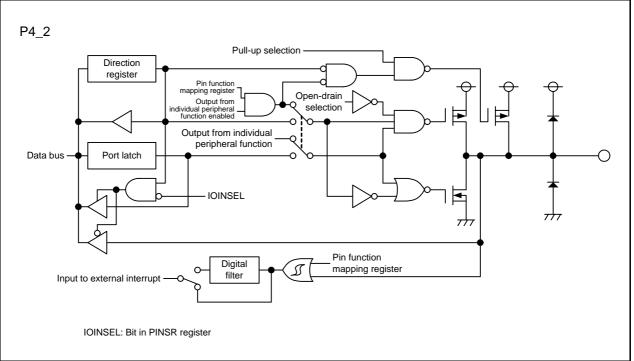

Figure 12.16 I/O Port Configuration (11)

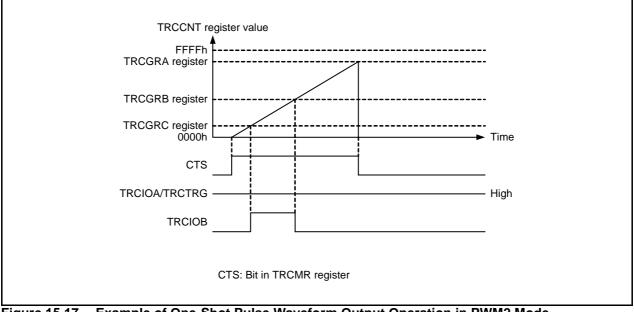

Figure 15.17 shows an Example of One-Shot Pulse Waveform Output Operation in PWM2 Mode.

The count is started when the CTS bit in the TRCMR register is set to 1 (count is started) under the following conditions. Then, the counter is changed to 0000h by a compare match with the TRCGRA register, the count operation is stopped, and a one-shot waveform is output.

- Bits TCEG1 to TCEG0 in the TRCCR2 register are set to 00b (TRCTRG input disabled) to disable the TRCTRG input.

- The CSTP bit in the TRCCR2 register is set to 1 (increment is stopped) to stop the increment when compare match A with the TRCGRA register occurs.

- The CCLR bit in the TRCCR1 register is set to 1 (TRCCNT counter is cleared by input capture/compare match A) to clear the TRCCNT register by compare match A.

- The TOB bit in the TRCCR1 register is set to 0 (output value 0) to set the initial value of the output level to 0.

Figure 15.17 Example of One-Shot Pulse Waveform Output Operation in PWM2 Mode

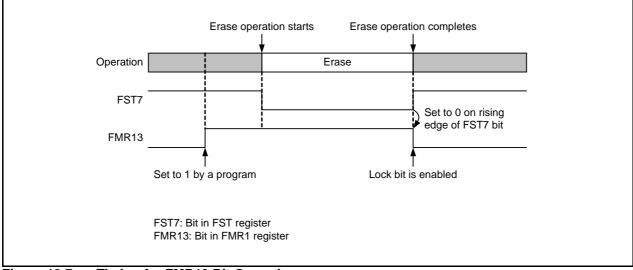

#### **19.6.5** Data Protect Function

Each block in the program ROM in the flash memory has a nonvolatile lock bit. The lock bit is enabled when the FMR13 bit in the FMR1 register is 0 (lock bit enabled). The lock bit can be used to disable (lock) programming/erasing each block. This prevents data from being written or erased inadvertently. The block status changes according to the lock bit as follows:

- When the lock bit data is 0: locked (the block cannot be programmed/erased)

- When the lock bit data is 1: not locked (the block can be programmed/erased)

The lock bit data is set to 0 (locked) when the lock bit program command is executed, and 1 (not locked) when the block is erased. There are no commands that can be used to set only the lock bit data to 1. The lock bit data can be read using the read lock bit status command.

When the FMR13 bit is set to 1 (lock bit disabled), the lock bit function is disabled and no blocks are locked. The lock bit data remains unchanged. When the FMR13 bit is set to 0 (lock bit enabled), the lock bit function is enabled. The lock bit data is retained.

When the block erase command is executed while the FMR13 bit is 1 (lock bit disabled), the target block is erased regardless of the lock bit status. The lock bit for the erase-target block is set to 1 after erase is completed. For details on individual commands, see **19.6.6 Software Commands**.

The FMR13 bit is set to 0 after auto-erase is completed. This bit is also set to 0 when one of the following conditions is met. To program/erase a block with a lock bit in a different state, set the FMR 13 bit to 1 (lock bit disabled) again and execute the program command or the block erase command.

- When the FST7 bit in the FST register is changed from 0 (busy) to 1 (ready) and the program/erase command completes.

- When the FST7 bit in the FST register is changed from 0 (busy) to 1 (ready) and program-suspend/erase-suspend is entered.

- When a command sequence error occurs.

- When the FMR01 bit in the FMR0 register is set to 0 (CPU rewrite mode disabled).

- When the FMSTP bit in the FMR0 register is set to 1 (flash memory is stopped).

- When the CMDRST bit in the FMR0 register is set to 1 (erase/write sequence reset).

Figure 19.7 shows the Timing for FMR13 Bit Operation.

# 21.5.5 INTi Input Filter (i = 0 to 3) When Returning from Wait Mode or Stop Mode to Standard Mode

When a transition is made to wait mode or stop mode with the WCKSTP bit in the CKSTPR register set to 1 (system clock stopped in wait mode) while in use of the  $\overline{INTi}$  input filter, the  $\overline{INTi}$  interrupt cannot be used to return to standard operating mode.

When the  $\overline{INTi}$  interrupt is used to return, set the WCKSTP bit to 1 and bits INTiF1 to INTiF0 in the INTF0 register to 00b (no filter) before a transition is made to wait mode or stop mode. When the  $\overline{INTi}$  input filter is used again, select the sampling clock with bits INTiF0 to INTiF1 to enable the INTIEN bit in the INTEN register.

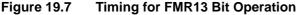

Figure 21.2 shows the Register Setting Procedure When  $\overline{INTi}$  Input Filter (i = 0 to 3) is Used.

Figure 21.2 Register Setting Procedure When INTi Input Filter (i = 0 to 3) is Used

### 21.9.5 Input Capture Function

• Set the pulse width of the input capture signal as follows: [When the digital filter is not used] Three or more cycles of the timer RC operation clock (refer to **Table 15.1 Timer RC Specifications**) [When the digital filter is used]

Five cycles of the digital filter sampling clock + three cycles of the timer RC operating clock, minimum (refer to **Figure 15.19 Digital Filter Circuit Block Diagram**)

• The value of the TRCCNT register is transferred to the TRCGRj register one or two cycles of the timer RC operation clock after the input capture signal is input to the TRCIOj (j = A, B, C, or D) pin (when the digital filter function is not used).

### 21.9.6 TRCMR Register in PWM2 Mode

When the CSTP bit in the TRCCR2 register is 1 (increment is stopped), do not set the TRCMR register when a compare match occurs between registers TRCCNT and TRCGRA.

### 21.9.7 MSTCR Register

After stopping the timer RC count, set the MSTTRC bit in the MSTCR register to 1 (standby).

### 21.9.8 Mode Switching

- When switching the modes during operation, set the CTS bit in the TRCMR register to 0 (count is stopped) before switching.

- After switching the modes, set each flag in the TRCSR register to 0 before operation is started.

### 21.9.9 Procedure for Setting Registers Associated with Timer RC

Set the registers associated with timer RC following the procedure below:

- (1) Set timer RC operating mode (bits PWMB, PWMC, PWMD, and PWM2 in the TRCMR register).

- (2) Set the registers other than that set in (1).

- (3) Set the port output to be enabled (bits EA to ED in the TRCOER register).