Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                            |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI               |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                    |

| Number of I/O              | 118                                                                                |

| Program Memory Size        | 1.6MB (1.6M × 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 138K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 24x10b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-144-13                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2787x200f100labkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 4.7<br>4.7.1 | AC Parameters                                      |

|--------------|----------------------------------------------------|

| 4.7.2        | Definition of Internal Timing                      |

| 4.7.2.1      | Wakeup Clock                                       |

| 4.7.2.3      | Selecting and Changing the Operating Frequency 114 |

| 4.7.3        | External Clock Input Parameters 115                |

| 4.7.4        | Pad Properties                                     |

| 4.7.5        | External Bus Timing 12'                            |

| 4.7.5.1      | Bus Cycle Control with the READY Input 126         |

| 4.7.6        | Synchronous Serial Interface Timing 129            |

| 4.7.7        | Debug Interface Timing 133                         |

| 5            | Package and Reliability 139                        |

| 5.1          | Packaging                                          |

| 5.2          | Thermal Considerations 14                          |

| 5.3          | Quality Declarations 142                           |

### **Summary of Features**

# 1.3 Definition of Feature Variants

The XC2787X types are offered with several Flash memory sizes. **Table 3** and **Table 4** describe the location of the available Flash memory.

### Table 3 Continuous Flash Memory Ranges

| Total Flash Size | 1st Range <sup>1)</sup>                      | 2nd Range                                    | 3rd Range                                    |

|------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| 1,600 Kbytes     | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>D8'FFFF <sub>H</sub> | n.a.                                         |

| 1,088 Kbytes     | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>CF'FFFF <sub>H</sub> | D8'0000 <sub>H</sub><br>D8'FFFF <sub>H</sub> |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

#### Table 4 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 01) | Flash 1 | Flash 2 | Flash 3 | Flash 4 | Flash 5 | Flash 6 |

|------------------|-----------|---------|---------|---------|---------|---------|---------|

| 1,600            | 256       | 255     | 256     | 256     | 256     | 256     | 64      |

| 1,088            | 256       | 255     | 256     | 256     | -       | -       | 64      |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFF<sub>H</sub>).

The XC2787X types are offered with different interface options. **Table 5** lists the available channels for each option.

#### Table 5 Interface Channel Association

| Total Number      | Available Channels / Message Objects |

|-------------------|--------------------------------------|

| 16 ADC0 channels  | CH0 CH15                             |

| 8 ADC1 channels   | CH0 CH7                              |

| 2 CAN nodes       | CAN0, CAN1<br>128 message objects    |

| 6 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1   |

#### **Summary of Features**

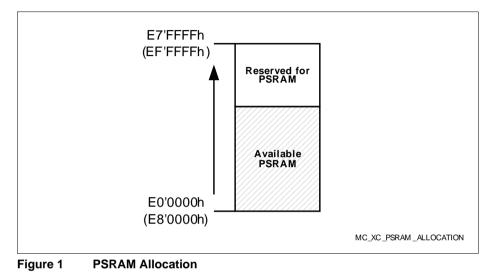

The XC2787X types are offered with several PSRAM memory sizes. Figure 1 shows the allocation rules. For example 80 Kbytes of PSRAM will be allocated at E0'0000h-E1'3FFFh.

#### **General Device Information**

| Table | e 6 Pin De        | finitior   | ns and | Functions (cont'd)                                                                                                                              |  |  |

|-------|-------------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol            | Ctrl.      | Туре   | Function                                                                                                                                        |  |  |

| 52    | P2.11             | O0 / I     | St/B   | Bit 11 of Port 2, General Purpose Input/Output                                                                                                  |  |  |

|       | U0C0_SELO<br>2    | O1         | St/B   | USIC0 Channel 0 Select/Control 2 Output                                                                                                         |  |  |

|       | U0C1_SELO<br>2    | O2         | St/B   | USIC0 Channel 1 Select/Control 2 Output                                                                                                         |  |  |

|       | U3C1_DOUT         | O3         | St/B   | USIC3 Channel 1 Shift Data Output                                                                                                               |  |  |

|       | BHE/WRH           | ОН         | St/B   | <b>External Bus Interf. High-Byte Control Output</b><br>Can operate either as Byte High Enable (BHE) or<br>as Write strobe for High Byte (WRH). |  |  |

| 53    | P11.5             | O0 / I     | St/B   | Bit 5 of Port 11, General Purpose Input/Output                                                                                                  |  |  |

|       | CCU61_CC6<br>0    | 01         | St/B   | CCU61 Channel 0 Output                                                                                                                          |  |  |

|       | CCU61_COU<br>T63  | O2         | St/B   | CCU61 Channel 3 Output                                                                                                                          |  |  |

|       | U3C1_SELO<br>1    | O3         | St/B   | USIC3 Channel 1 Select/Control 1 Output                                                                                                         |  |  |

|       | CCU61_CC6<br>0INB | 1          | St/B   | CCU61 Channel 0 Input                                                                                                                           |  |  |

|       | U3C1_DX2B         | I          | St/B   | USIC3 Channel 1 Shift Control Input                                                                                                             |  |  |

| 55    | P2.0              | O0 / I     | St/B   | Bit 0 of Port 2, General Purpose Input/Output                                                                                                   |  |  |

|       | CCU63_CC6<br>0    | O2         | St/B   | CCU63 Channel 0 Output                                                                                                                          |  |  |

|       | AD13              | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 13                                                                                                     |  |  |

|       | RxDC0C            | I          | St/B   | CAN Node 0 Receive Data Input                                                                                                                   |  |  |

|       | CCU63_CC6<br>0INB | I          | St/B   | CCU63 Channel 0 Input                                                                                                                           |  |  |

|       | T5INB             | I          | St/B   | GPT12E Timer T5 Count/Gate Input                                                                                                                |  |  |

#### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |  |

|-------|--------------------------------------------------------|------------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                       |  |  |  |  |

| 95    | P10.3                                                  | O0 / I     | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | CCU60_COU<br>T60                                       | O2         | St/B | CCU60 Channel 0 Output                         |  |  |  |  |

|       | AD3                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 3     |  |  |  |  |

|       | U0C0_DX2A                                              | I          | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |  |

|       | U0C1_DX2A                                              | I          | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |  |

|       | U3C0_DX0A                                              | I          | St/B | USIC3 Channel 0 Shift Data Input               |  |  |  |  |

| 96    | P0.5                                                   | O0 / I     | St/B | Bit 5 of Port 0, General Purpose Input/Output  |  |  |  |  |

|       | U1C1_SCLK<br>OUT                                       | 01         | St/B | USIC1 Channel 1 Shift Clock Output             |  |  |  |  |

|       | U1C0_SELO<br>2                                         | 02         | St/B | USIC1 Channel 0 Select/Control 2 Output        |  |  |  |  |

|       | CCU61_COU<br>T62                                       | O3         | St/B | CCU61 Channel 2 Output                         |  |  |  |  |

|       | A5                                                     | ОН         | St/B | External Bus Interface Address Line 5          |  |  |  |  |

|       | U1C1_DX1A                                              | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |  |  |

|       | U1C0_DX1C                                              | I          | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |  |

| 97    | P3.3                                                   | O0 / I     | St/B | Bit 3 of Port 3, General Purpose Input/Output  |  |  |  |  |

|       | U2C0_SELO<br>0                                         | 01         | St/B | USIC2 Channel 0 Select/Control 0 Output        |  |  |  |  |

|       | U2C1_SELO<br>1                                         | 02         | St/B | USIC2 Channel 1 Select/Control 1 Output        |  |  |  |  |

|       | U2C0_DX2A                                              | I          | St/B | USIC2 Channel 0 Shift Control Input            |  |  |  |  |

#### **General Device Information**

| Table           | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                    |  |  |  |  |

|-----------------|--------------------------------------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin             | Symbol                                                 | Ctrl.      | Туре | Function                                                                                                                                                           |  |  |  |  |

| 117             | P10.10                                                 | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |  |  |

|                 | U0C0_SELO<br>0                                         | O1         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |  |  |

|                 | CCU60_COU<br>T63                                       | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                             |  |  |  |  |

|                 | AD10                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                                        |  |  |  |  |

|                 | U0C0_DX2C                                              | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                |  |  |  |  |

|                 | U0C1_DX1A                                              | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                  |  |  |  |  |

|                 | TDI_B                                                  | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.           |  |  |  |  |

| 118             | P10.11                                                 | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |  |  |

| (<br> <br> <br> | U1C0_SCLK<br>OUT                                       | O1         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                 |  |  |  |  |

|                 | BRKOUT                                                 | 02         | St/B | OCDS Break Signal Output                                                                                                                                           |  |  |  |  |

|                 | U3C0_SELO<br>0                                         | O3         | St/B | USIC3 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |  |  |

|                 | AD11                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                                        |  |  |  |  |

|                 | U1C0_DX1D                                              | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                  |  |  |  |  |

|                 | TMS_B                                                  | IH         | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |  |  |  |  |

|                 | U3C0_DX2A                                              | I          | St/B | USIC3 Channel 0 Shift Control Input                                                                                                                                |  |  |  |  |

| 119             | P9.2                                                   | O0 / I     | St/B | Bit 2 of Port 9, General Purpose Input/Output                                                                                                                      |  |  |  |  |

|                 | CCU63_CC6<br>2                                         | O1         | St/B | CCU63 Channel 2 Output                                                                                                                                             |  |  |  |  |

|                 | CC1_CC4                                                | O2         | St/B | CAPCOM1 CC4 Compare Output                                                                                                                                         |  |  |  |  |

|                 | CCU63_CC6<br>2INA                                      | I          | St/B | CCU63 Channel 2 Input                                                                                                                                              |  |  |  |  |

|                 | CAPINB                                                 | I          | St/B | GPT12E Register CAPREL Capture Input                                                                                                                               |  |  |  |  |

#### **General Device Information**

| Table 6Pin Definitions and Functions (cont'd) |                   |            |      |                                                                                                                                                                               |  |  |  |

|-----------------------------------------------|-------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                           | Symbol            | Ctrl.      | Туре | Function                                                                                                                                                                      |  |  |  |

| 120                                           | P1.2              | O0 / I     | St/B | Bit 2 of Port 1, General Purpose Input/Output                                                                                                                                 |  |  |  |

|                                               | CCU62_CC6<br>2    | 01         | St/B | CCU62 Channel 2 Output                                                                                                                                                        |  |  |  |

|                                               | U1C0_SELO<br>6    | 02         | St/B | USIC1 Channel 0 Select/Control 6 Output                                                                                                                                       |  |  |  |

|                                               | U2C1_SCLK<br>OUT  | O3         | St/B | USIC2 Channel 1 Shift Clock Output                                                                                                                                            |  |  |  |

|                                               | A10               | ОН         | St/B | External Bus Interface Address Line 10                                                                                                                                        |  |  |  |

|                                               | ESR1_4            | I          | St/B | ESR1 Trigger Input 4                                                                                                                                                          |  |  |  |

|                                               | CCU61_T12<br>HRB  | I          | St/B | External Run Control Input for T12 of CCU61                                                                                                                                   |  |  |  |

|                                               | CCU62_CC6<br>2INA | I          | St/B | CCU62 Channel 2 Input                                                                                                                                                         |  |  |  |

|                                               | U2C1_DX0D         | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                              |  |  |  |

|                                               | U2C1_DX1C         | I          | St/B | USIC2 Channel 1 Shift Clock Input                                                                                                                                             |  |  |  |

| 121                                           | P10.12            | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |  |

|                                               | U1C0_DOUT         | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |  |  |

|                                               | TDO_B             | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |

|                                               | AD12              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 12                                                                                                                                   |  |  |  |

|                                               | U1C0_DX0C         | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |  |  |

|                                               | U1C0_DX1E         | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |  |  |

| 122                                           | P9.3              | O0 / I     | St/B | Bit 3 of Port 9, General Purpose Input/Output                                                                                                                                 |  |  |  |

|                                               | CCU63_COU<br>T60  | 01         | St/B | CCU63 Channel 0 Output                                                                                                                                                        |  |  |  |

|                                               | BRKOUT            | O2         | St/B | OCDS Break Signal Output                                                                                                                                                      |  |  |  |

### **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

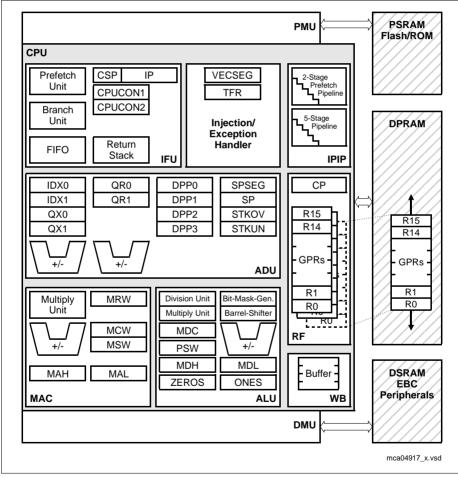

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

# **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

# 3.15 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

# 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz).

Time intervals between 2.56  $\mu$ s and 10.71 s can be monitored (@ 100 MHz).

# 4 Electrical Parameters

The operating range for the XC2787X is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

# 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

| Parameter                                                       | Symbol                  |      | Values | ;                      | Unit | Note /<br>Test Condition           |

|-----------------------------------------------------------------|-------------------------|------|--------|------------------------|------|------------------------------------|

|                                                                 |                         | Min. | Тур.   | Max.                   |      |                                    |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR      | -30  | -      | -                      | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR      | -    | -      | 30                     | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$    | -10  | -      | 10                     | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -    | -      | 100                    | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\sf J}{\sf SR}$     | -40  | -      | 150                    | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$     | -65  | -      | 150                    | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | -0.5 | -      | 6.0                    | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}~{\rm SR}$   | -0.5 | -      | V <sub>DDP</sub> + 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

Table 12 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

### Pullup/Pulldown Device Behavior

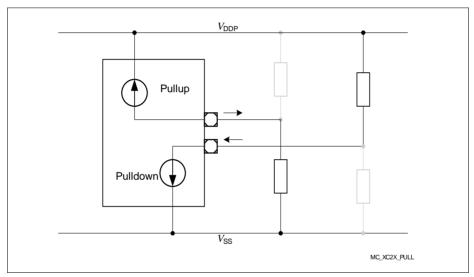

Most pins of the XC2787X feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 13** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 13 Pullup/Pulldown Current Definition

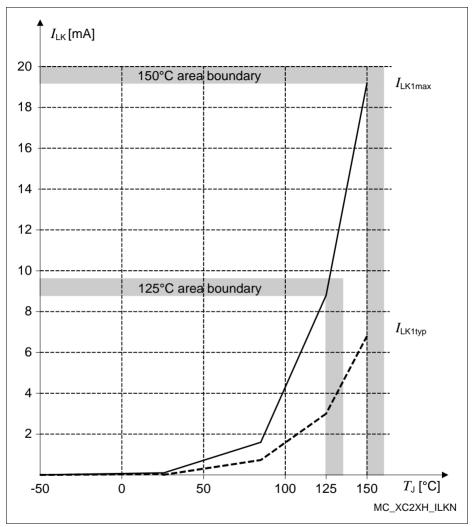

Figure 15 Leakage Supply Current as a Function of Temperature

# 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XC2787X into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 |                                         | Values       | ;                                     | Unit | Note /                                    |  |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------|--------------|---------------------------------------|------|-------------------------------------------|--|

|                                                                       |                        | Min.                                    | Тур.         | Max.                                  |      | Test Condition                            |  |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                      | -            | 1                                     | %    | $\Delta T_{\rm J} \le 10^{\circ} {\rm C}$ |  |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$  | 4.8                                     | 5.0          | 5.2                                   | MHz  |                                           |  |

| Wakeup clock source                                                   | $f_{\rm WU}{\rm CC}$   | 400                                     | -            | 700                                   | kHz  | FREQSEL= 00                               |  |

| frequency <sup>2)</sup>                                               |                        | 210                                     | -            | 390                                   | kHz  | FREQSEL= 01                               |  |

|                                                                       |                        | 140                                     | -            | 260                                   | kHz  | FREQSEL= 10                               |  |

|                                                                       |                        | 110                                     | -            | 200                                   | kHz  | FREQSEL= 11                               |  |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.9                                     | 2.6          | 3.2                                   | ms   | $f_{ m WU}$ = 500 kHz                     |  |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -            | 12 /<br>f <sub>WU</sub> <sup>3)</sup> | μS   |                                           |  |

| Core voltage (PVC)<br>supervision level                               | $V_{\rm PVC}{ m CC}$   | V <sub>LV</sub> -<br>0.03               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.07 <sup>4)</sup>  | V    | 5)                                        |  |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub> -<br>0.10 <sup>6)</sup> | $V_{\rm LV}$ | V <sub>LV</sub> + 0.15                | V    | voltage_range=<br>lower <sup>5)</sup>     |  |

|                                                                       |                        | V <sub>LV</sub> -<br>0.15               | $V_{\rm LV}$ | V <sub>LV</sub> +<br>0.15             | V    | voltage_range=<br>upper <sup>5)</sup>     |  |

### Table 22Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

3)  $f_{WU}$  in MHz

| Parameter                          | Symbol             |      | Values |                                   | Unit | Note /                                                                                                              |

|------------------------------------|--------------------|------|--------|-----------------------------------|------|---------------------------------------------------------------------------------------------------------------------|

|                                    |                    | Min. | Тур.   | Max.                              |      | Test Condition                                                                                                      |

| Rise and Fall times (10% -<br>90%) | t <sub>RF</sub> CC | -    | -      | 37 +<br>0.65 x<br>C <sub>L</sub>  | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Medium                            |

|                                    |                    | _    | _      | 24 +<br>0.3 x<br>C <sub>L</sub>   | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Medium |

|                                    |                    | -    | -      | 6.2 +<br>0.24 x<br>C <sub>L</sub> | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Sharp  |

|                                    |                    | -    | -      | 34 +<br>0.3 x<br>C <sub>L</sub>   | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Slow   |

|                                    |                    | -    | -      | 500 +<br>2.5 x<br>C <sub>L</sub>  | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Weak                              |

Table 29 Standard Pad Parameters for Lower Voltage Range (cont'd)

An output current above |I<sub>OXnom</sub>| may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

# XC2787X XC2000 Family / High Line

### **Electrical Parameters**

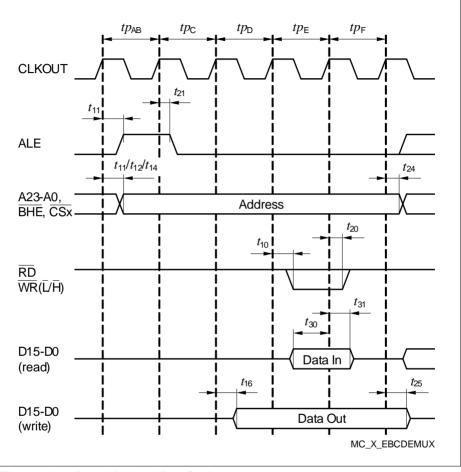

Figure 24 Demultiplexed Bus Cycle

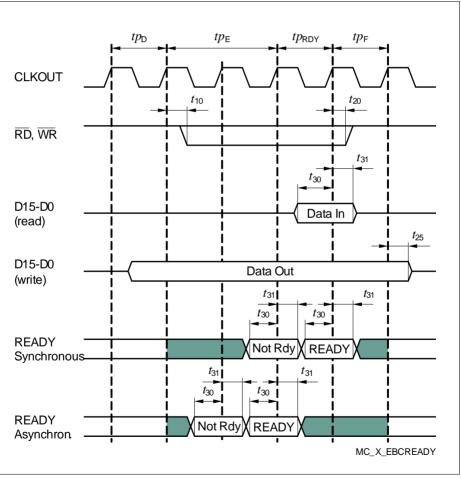

# 4.7.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum

duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command (RD or WR).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

Figure 25 READY Timing

### Package and Reliability

# 5.3 Quality Declarations

The operation lifetime of the XC2787X depends on the applied temperature profile in the application. For a typical example, please refer to **Table 44**; for other profiles, please contact your Infineon counterpart to calculate the specific lifetime within your application.

### Table 43Quality Parameters

| Parameter                                                    | Symbol             | Values |      |       | Unit | Note /                       |

|--------------------------------------------------------------|--------------------|--------|------|-------|------|------------------------------|

|                                                              |                    | Min.   | Тур. | Max.  |      | Test Condition               |

| Operation lifetime                                           | t <sub>OP</sub> CC | -      | -    | 20    | а    | See Table 44<br>and Table 45 |

| ESD susceptibility<br>according to Human Body<br>Model (HBM) | $V_{\rm HBM}$ SR   | -      | -    | 2 000 | V    | EIA/JESD22-<br>A114-B        |

| Moisture sensitivity level                                   | MSL CC             | -      | -    | 3     | -    | JEDEC<br>J-STD-020C          |

### Table 44 Typical Usage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.                           | Notes            |

|---------------------------------|-----------------------------------------------|------------------|

| 1 200 h                         | $T_{\rm J} = 150^{\circ}{\rm C}$              | Normal operation |

| 3 600 h                         | $T_{\rm J}$ = 125°C                           | Normal operation |

| 7 200 h                         | $T_{\rm J} = 110^{\circ}{\rm C}$              | Normal operation |

| 12 000 h                        | $T_{\rm J} = 100^{\circ}{\rm C}$              | Normal operation |

| 7 × 21 600 h                    | $T_{\rm J} = 010^{\circ} {\rm C},,$<br>6070°C | Power reduction  |

#### Table 45 Long Time Storage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.               | Notes            |

|---------------------------------|-----------------------------------|------------------|

| 2 000 h                         | $T_{\rm J} = 150^{\circ}{\rm C}$  | Normal operation |

| 16 000 h                        | $T_{\rm J} = 125^{\circ}{\rm C}$  | Normal operation |

| 6 000 h                         | $T_{\rm J} = 110^{\circ}{\rm C}$  | Normal operation |

| 151 200 h                       | $T_{\rm J} \le 150^{\circ}{ m C}$ | No operation     |

www.infineon.com

Published by Infineon Technologies AG