Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 87                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                             |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 112-LFBGA                                                                |

| Supplier Device Package    | 112-BGA (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg390f1024-bga112 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **2 System Summary**

## **2.1 System Introduction**

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32GG microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32GG390 devices. For a complete feature set and in-depth information on the modules, the reader is referred to the *EFM32GG Reference Manual*.

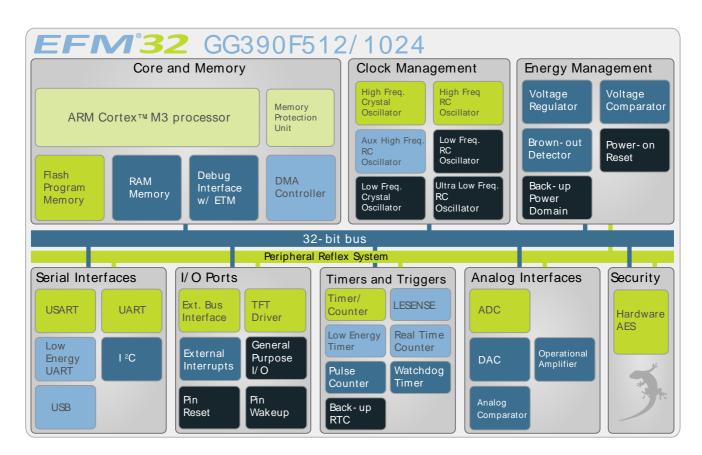

A block diagram of the EFM32GG390 is shown in Figure 2.1 (p. 3) .

### Figure 2.1. Block Diagram

### 2.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in *EFM32 Cortex-M3 Reference Manual*.

## 2.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface and an Embedded Trace Module (ETM) for data/instruction tracing. In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

## 2.1.26 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has two single ended output buffers which can be combined into one differential output. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

## 2.1.27 Operational Amplifier (OPAMP)

The EFM32GG390 features 3 Operational Amplifiers. The Operational Amplifier is a versatile general purpose amplifier with rail-to-rail differential input and rail-to-rail single ended output. The input can be set to pin, DAC or OPAMP, whereas the output can be pin, OPAMP or ADC. The current is programmable and the OPAMP has various internal configurations such as unity gain, programmable gain using internal resistors etc.

### 2.1.28 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface (LESENSE<sup>TM</sup>), is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable FSM which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

### 2.1.29 Backup Power Domain

The backup power domain is a separate power domain containing a Backup Real Time Counter, BURTC, and a set of retention registers, available in all energy modes. This power domain can be configured to automatically change power source to a backup battery when the main power drains out. The backup power domain enables the EFM32GG390 to keep track of time and retain data, even if the main power source should drain out.

### 2.1.30 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

## 2.1.31 General Purpose Input/Output (GPIO)

In the EFM32GG390, there are 86 General Purpose Input/Output (GPIO) pins, which are divided into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

## **2.2 Configuration Summary**

The features of the EFM32GG390 is a subset of the feature set described in the EFM32GG Reference Manual. Table 2.1 (p. 8) describes device specific implementation of the features.

| Module | Configuration      | Pin Connections                                                      |

|--------|--------------------|----------------------------------------------------------------------|

| VCMP   | Full configuration | NA                                                                   |

| ADC0   | Full configuration | ADC0_CH[7:0]                                                         |

| DAC0   | Full configuration | DAC0_OUT[1:0], DAC0_OUTxALT                                          |

| ОРАМР  | Full configuration | Outputs: OPAMP_OUTx,<br>OPAMP_OUTxALT, Inputs:<br>OPAMP_Px, OPAMP_Nx |

| AES    | Full configuration | NA                                                                   |

| GPIO   | 86 pins            | Available pins are shown in<br>Table 4.3 (p. 63)                     |

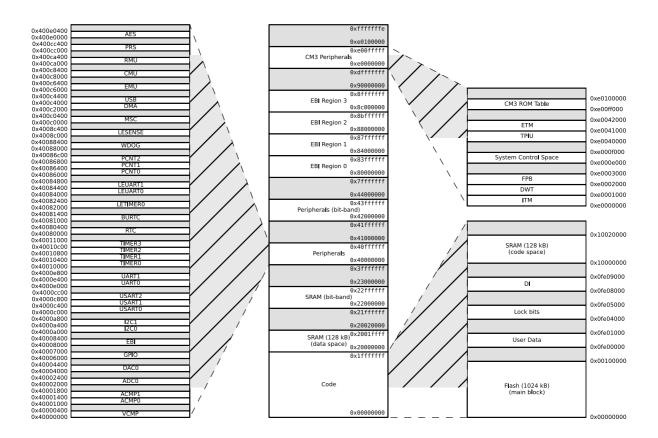

### 2.3 Memory Map

The *EFM32GG390* memory map is shown in Figure 2.2 (p. 9), with RAM and Flash sizes for the largest memory configuration.

### Figure 2.2. EFM32GG390 Memory Map with largest RAM and Flash sizes

### Table 3.5. Power Management

| Symbol                   | Parameter                                                                   | Condition                                                               | Min  | Тур  | Max  | Unit |

|--------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| M                        | BOD threshold on                                                            | EMO                                                                     | 1.74 |      | 1.96 | V    |

| V <sub>BODextthr</sub> - | falling external sup-<br>ply voltage                                        | EM2                                                                     | 1.74 |      | 1.98 | V    |

| V <sub>BODintthr</sub> - | BOD threshold on<br>falling internally reg-<br>ulated supply volt-<br>age   |                                                                         | 1.57 |      | 1.70 | V    |

| V <sub>BODextthr+</sub>  | BOD threshold on<br>rising external sup-<br>ply voltage                     |                                                                         |      | 1.85 | 1.98 | V    |

| V <sub>PORthr+</sub>     | Power-on Reset<br>(POR) threshold on<br>rising external sup-<br>ply voltage |                                                                         |      |      | 1.98 | V    |

| t <sub>RESET</sub>       | Delay from reset<br>is released until<br>program execution<br>starts        | Applies to Power-on Reset,<br>Brown-out Reset and pin reset.            |      | 163  |      | μs   |

| C <sub>DECOUPLE</sub>    | Voltage regulator<br>decoupling capaci-<br>tor.                             | X5R capacitor recommended.<br>Apply between DECOUPLE pin<br>and GROUND  |      | 1    |      | μF   |

| C <sub>USB_VREGO</sub>   | USB voltage regu-<br>lator out decoupling capacitor.                        | X5R capacitor recommended.<br>Apply between USB_VREGO<br>pin and GROUND |      | 1    |      | μF   |

| C <sub>USB_VREGI</sub>   | USB voltage regula-<br>tor in decoupling ca-<br>pacitor.                    | X5R capacitor recommended.<br>Apply between USB_VREGI<br>pin and GROUND |      | 4.7  |      | μF   |

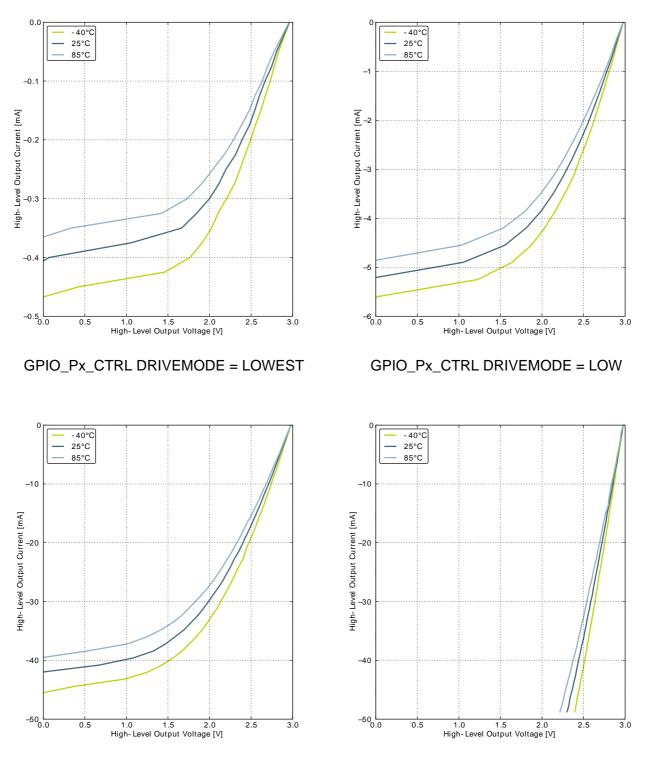

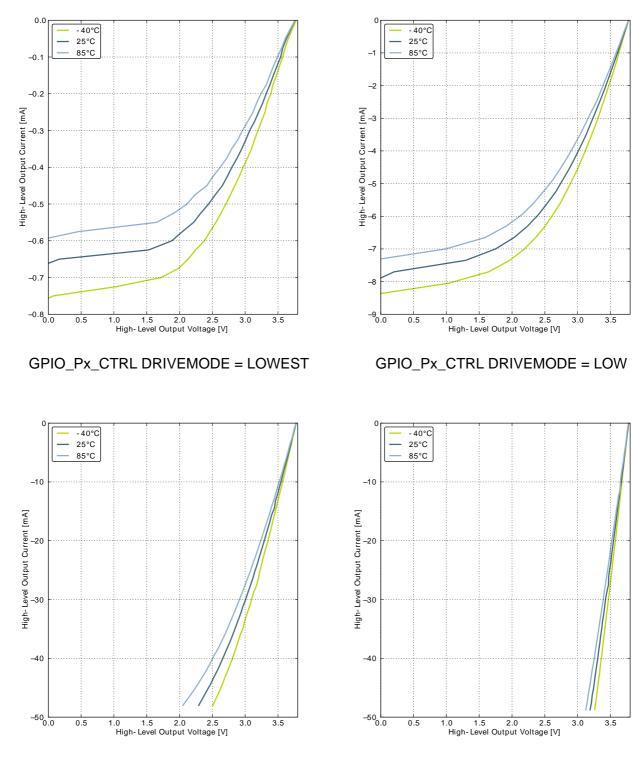

### Figure 3.7. Typical High-Level Output Current, 3V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

### Figure 3.8. Typical Low-Level Output Current, 3.8V Supply Voltage

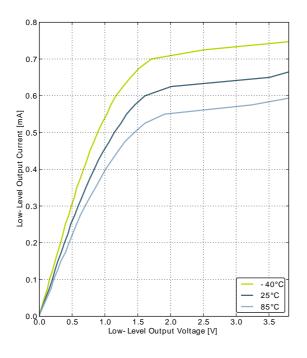

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

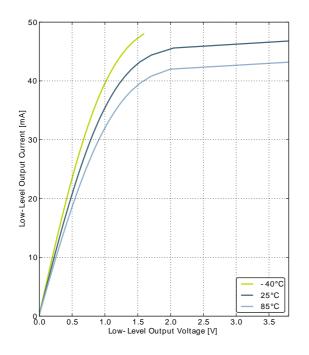

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

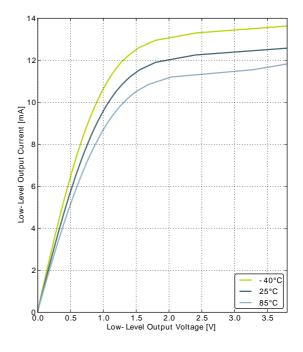

GPIO\_Px\_CTRL DRIVEMODE = LOW

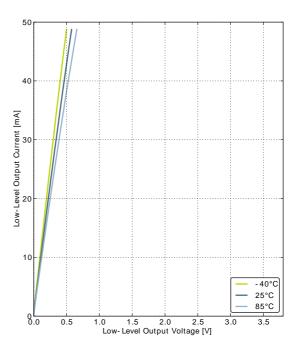

GPIO\_Px\_CTRL DRIVEMODE = HIGH

### Figure 3.9. Typical High-Level Output Current, 3.8V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

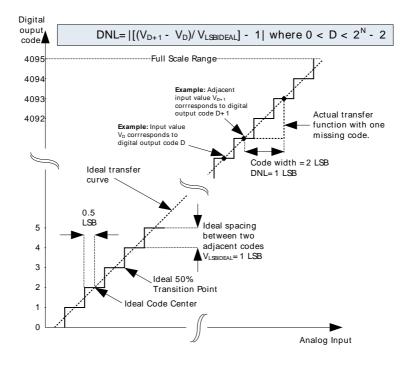

Figure 3.18. Differential Non-Linearity (DNL)

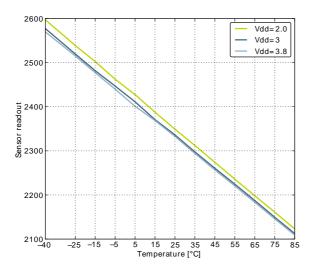

### Figure 3.24. ADC Temperature sensor readout

## 3.11 Digital Analog Converter (DAC)

### Table 3.15. DAC

| Symbol                 | Parameter                           | Condition                                                                | Min              | Тур              | Max              | Unit            |

|------------------------|-------------------------------------|--------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|

| M                      | Output voltage                      | VDD voltage reference, single ended                                      | 0                |                  | V <sub>DD</sub>  | V               |

| V <sub>DACOUT</sub>    | range                               | VDD voltage reference, differ-<br>ential                                 | -V <sub>DD</sub> |                  | V <sub>DD</sub>  | V               |

| V <sub>DACCM</sub>     | Output common<br>mode voltage range |                                                                          | 0                |                  | V <sub>DD</sub>  | V               |

|                        | Active current in-                  | 500 kSamples/s, 12 bit                                                   |                  | 400 <sup>1</sup> | 600 <sup>1</sup> | μA              |

| I <sub>DAC</sub>       | cluding references                  | 100 kSamples/s, 12 bit                                                   |                  | 200 <sup>1</sup> | 260 <sup>1</sup> | μA              |

|                        | for 2 channels                      | 1 kSamples/s 12 bit NORMAL                                               |                  | 17 <sup>1</sup>  | 25 <sup>1</sup>  | μA              |

| SR <sub>DAC</sub>      | Sample rate                         |                                                                          |                  |                  | 500              | ksam-<br>ples/s |

|                        | DAC clock frequen-                  | Continuous Mode                                                          |                  |                  | 1000             | kHz             |

| f <sub>DAC</sub>       |                                     | Sample/Hold Mode                                                         |                  |                  | 250              | kHz             |

|                        |                                     | Sample/Off Mode                                                          |                  |                  | 250              | kHz             |

| CYC <sub>DACCONV</sub> | Clock cyckles per conversion        |                                                                          |                  | 2                |                  |                 |

| t <sub>DACCONV</sub>   | Conversion time                     |                                                                          | 2                |                  |                  | μs              |

| t <sub>DACSETTLE</sub> | Settling time                       |                                                                          |                  | 5                |                  | μs              |

| SNR <sub>DAC</sub>     |                                     | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |                  | 58               |                  | dB              |

|                        | Signal to Noise Ra-<br>tio (SNR)    | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |                  | 59               |                  | dB              |

|                        |                                     | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |                  | 58               |                  | dB              |

| Symbol                    | nbol Parameter Condition      |                                                                                      | Min             | Тур  | Мах                  | Unit              |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|------|----------------------|-------------------|

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain                             |                 | 13   | 17                   | μA                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 101  |                      | dB                |

| G <sub>OL</sub>           | Open Loop Gain                | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 98   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 91   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 6.1  |                      | MHz               |

| GBW <sub>OPAMP</sub>      | Gain Bandwidth<br>Product     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 1.8  |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.25 |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, CL=75<br>pF                               |                 | 64   |                      | 0                 |

| PM <sub>OPAMP</sub>       | Phase Margin                  | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | o                 |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | o                 |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100  |                      | Mohm              |

| R <sub>LOAD</sub>         | Load Resistance               |                                                                                      | 200             |      |                      | Ohm               |

| I <sub>LOAD_DC</sub>      | DC Load Current               |                                                                                      |                 |      | 11                   | mA                |

| V <sub>INPUT</sub>        | Input Voltage                 | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub>      | V                 |

| * INPUT                   | input voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub> -1.2 | V                 |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |      | V <sub>DD</sub>      | V                 |

| Voffset                   | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     | -13             | 0    | 11                   | mV                |

| VOFFSET                   | input Onset Voltage           | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1    |                      | mV                |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |      | 0.02                 | mV/°C             |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 3.2  |                      | V/µs              |

| SR <sub>OPAMP</sub>       | Slew Rate                     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.8  |                      | V/µs              |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.1  |                      | V/µs              |

| N                         |                               | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=0</f<10>  |                 | 101  |                      | μV <sub>RMS</sub> |

| N <sub>OPAMP</sub>        | Voltage Noise                 | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=1</f<10>  |                 | 141  |                      | μV <sub>RMS</sub> |

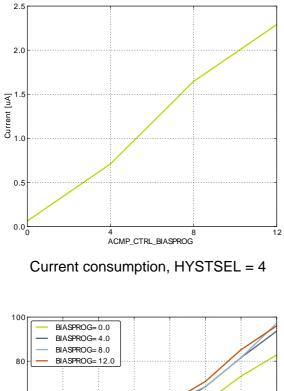

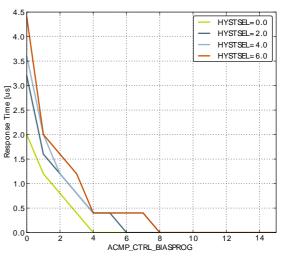

Figure 3.30. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

Response time

## 3.14 Voltage Comparator (VCMP)

### Table 3.18. VCMP

| Symbol                  | Parameter                             | Condition                                                             | Min  | Тур             | Max | Unit |

|-------------------------|---------------------------------------|-----------------------------------------------------------------------|------|-----------------|-----|------|

| V <sub>VCMPIN</sub>     | Input voltage range                   |                                                                       |      | V <sub>DD</sub> |     | V    |

| V <sub>VCMPCM</sub>     | VCMP Common<br>Mode voltage range     |                                                                       |      | V <sub>DD</sub> |     | V    |

|                         | Active current                        | BIASPROG=0b0000 and<br>HALFBIAS=1 in VCMPn_CTRL<br>register           |      | 0.3             | 0.6 | μΑ   |

| IVCMP                   | Active current                        | BIASPROG=0b1111 and<br>HALFBIAS=0 in VCMPn_CTRL<br>register. LPREF=0. |      | 22              | 30  | μΑ   |

| t <sub>VCMPREF</sub>    | Startup time refer-<br>ence generator | NORMAL                                                                |      | 10              |     | μs   |

| Maria                   | Offect veltage                        | Single ended                                                          | -230 | -40             | 190 | mV   |

| V <sub>VCMPOFFSET</sub> | Offset voltage                        | Differential                                                          |      | 10              |     | mV   |

| V <sub>VCMPHYST</sub>   | VCMP hysteresis                       |                                                                       |      | 40              |     | mV   |

| t <sub>VCMPSTART</sub>  | Startup time                          |                                                                       |      |                 | 10  | μs   |

The  $V_{DD}$  trigger level can be configured by setting the TRIGLEVEL field of the VCMP\_CTRL register in accordance with the following equation:

#### VCMP Trigger Level as a Function of Level Setting

V<sub>DD Trigger Level</sub>=1.667V+0.034 ×TRIGLEVEL

(3.2)

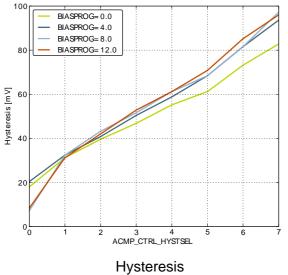

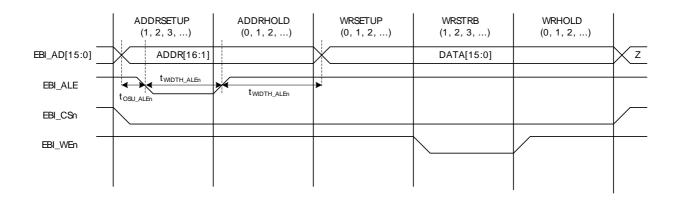

### 3.15 EBI

### Figure 3.31. EBI Write Enable Timing

### Table 3.19. EBI Write Enable Timing

| Symbol                             | Parameter                                                                                                  | Min                                                | Тур | Мах | Unit |

|------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|

| t <sub>OH_WEn<sup>1234</sup></sub> | Output hold time, from trailing EBI_WEn/<br>EBI_NANDWEn edge to EBI_AD, EBI_A,<br>EBI_CSn, EBI_BLn invalid | -6.00 + (WRHOLD *<br>t <sub>HFCORECLK</sub> )      |     |     | ns   |

| t <sub>OSU_WEn 12345</sub>         | Output setup time, from EBI_AD, EBI_A,<br>EBI_CSn, EBI_BLn valid to leading EBI_WEn/<br>EBI_NANDWEn edge   | -14.00 + (WRSETUP<br><sup>* t</sup> нғсопесік)     |     |     | ns   |

| twidth_wen <sup>12345</sup>        | EBI_WEn/EBI_NANDWEn pulse width                                                                            | -7.00 + ((WRSTRB<br>+1) * t <sub>HFCORECLK</sub> ) |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D16 addressing mode)

<sup>2</sup>Applies for both EBI\_WEn and EBI\_NANWEn (figure only shows EBI\_WEn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^4\text{Measurement}$  done at 10% and 90% of  $\text{V}_\text{DD}$  (figure shows 50% of  $_\text{VDD})$

<sup>5</sup> The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of  $t_{WIDTH_WEn}$  and increases the length of  $t_{OSU_WEn}$  by 1/2 \*  $t_{HFCLKNODIV}$ .

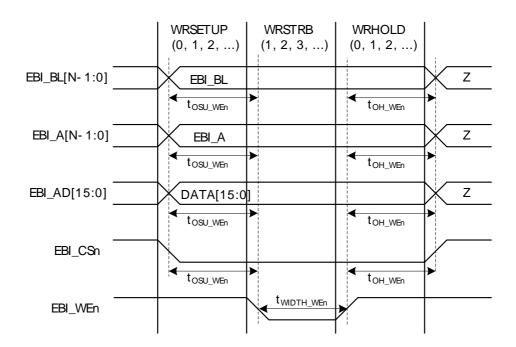

### Figure 3.32. EBI Address Latch Enable Related Output Timing

### Table 3.20. EBI Address Latch Enable Related Output Timing

| Symbol                      | Parameter                                                      | Min                                                                            | Тур | Max | Unit |

|-----------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|------|

| t <sub>OH_ALEn 1234</sub>   | Output hold time, from trailing EBI_ALE edge to EBI_AD invalid | -6.00 + (AD-<br>DRHOLD <sup>5</sup> * t <sub>HFCORE-</sub><br><sub>CLK</sub> ) |     |     | ns   |

| t <sub>OSU_ALEn 124</sub>   | Output setup time, from EBI_AD valid to leading EBI_ALE edge   | -13.00 + (0 * t <sub>HFCORE-</sub><br><sub>CLK</sub> )                         |     |     | ns   |

| twidth_Alen <sup>1234</sup> | EBI_ALEn pulse width                                           | -7.00 + (ADDRSET-<br>UP+1) * t <sub>HFCORECLK</sub> )                          |     |     | ns   |

<sup>1</sup>Applies to addressing modes D8A24ALE and D16A16ALE (figure only shows D16A16ALE)

<sup>2</sup>Applies for all polarities (figure only shows active low signals)

$^3$  The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFALE=0. The trailing edge of EBI\_ALE can be moved to the left by setting HALFALE=1. This decreases the length of t<sub>WIDTH\_ALEn</sub> and increases the length of tOH\_ALEn by t<sub>HFCORECLK</sub> - 1/2 \* t<sub>HFCLKNODIV</sub>.

$^4$ Measurement done at 10% and 90% of V\_DD (figure shows 50% of  $_{\text{VDD}})$

<sup>5</sup>Figure only shows a write operation. For a multiplexed read operation the address hold time is controlled via the RDSETUP state instead of via the ADDRHOLD state.

| Symbol                                 | Parameter                                                          | Min | Тур | Мах | Unit |

|----------------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>H_ARDY</sub> <sup>1 2 3 4</sup> | Hold time, from trailing EBI_REn, EBI_WEn edge to EBI_ARDY invalid | -1  |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D16A8.)

<sup>2</sup>Applies for EBI\_REn, EBI\_WEn (figure only shows EBI\_REn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^4$ Measurement done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $_{\text{VDD}})$

## 3.16 I2C

### Table 3.24. I2C Standard-mode (Sm)

| Symbol              | Parameter                                        | Min | Тур | Max                 | Unit |

|---------------------|--------------------------------------------------|-----|-----|---------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   |     | 100 <sup>1</sup>    | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 4.7 |     |                     | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 4.0 |     |                     | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 250 |     |                     | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8   |     | 3450 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 4.7 |     |                     | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 4.0 |     |                     | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 4.0 |     |                     | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 4.7 |     |                     | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Standard-mode, see the I2C chapter in the EFM32GG Reference Manual. <sup>2</sup>The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ). <sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((3450\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

### Table 3.25. I2C Fast-mode (Fm)

| Symbol              | Parameter                                        | Min | Тур | Max                | Unit |

|---------------------|--------------------------------------------------|-----|-----|--------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   |     | 400 <sup>1</sup>   | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 1.3 |     |                    | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.6 |     |                    | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 100 |     |                    | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8   |     | 900 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.6 |     |                    | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.6 |     |                    | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.6 |     |                    | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 1.3 |     |                    | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32GG Reference Manual. <sup>2</sup>The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

<sup>3</sup>When transmitting data, this number is guaranteed only when  $I2Cn_CLKDIV < ((900*10^{-9} [s] * f_{HFPERCLK} [Hz]) - 4)$ .

### ...the world's most energy friendly microcontrollers

| Alternate     |      |      | LOC  | OCATION |   |   |   |                                                                                                 |

|---------------|------|------|------|---------|---|---|---|-------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3       | 4 | 5 | 6 | Description                                                                                     |

|               |      |      |      |         |   |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO       | PF2  |      | PD1  | PD2     |   |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| EBI_A00       | PA12 | PA12 | PA12 |         |   |   |   | External Bus Interface (EBI) address output pin 00.                                             |

| EBI_A01       | PA13 | PA13 | PA13 |         |   |   |   | External Bus Interface (EBI) address output pin 01.                                             |

| EBI_A02       | PA14 | PA14 | PA14 |         |   |   |   | External Bus Interface (EBI) address output pin 02.                                             |

| EBI_A03       | PB9  | PB9  | PB9  |         |   |   |   | External Bus Interface (EBI) address output pin 03.                                             |

| EBI_A04       | PB10 | PB10 | PB10 |         |   |   |   | External Bus Interface (EBI) address output pin 04.                                             |

| EBI_A05       | PC6  | PC6  | PC6  |         |   |   |   | External Bus Interface (EBI) address output pin 05.                                             |

| EBI_A06       | PC7  | PC7  | PC7  |         |   |   |   | External Bus Interface (EBI) address output pin 06.                                             |

| EBI_A07       | PE0  | PE0  | PE0  |         |   |   |   | External Bus Interface (EBI) address output pin 07.                                             |

| EBI_A08       | PE1  | PE1  | PE1  |         |   |   |   | External Bus Interface (EBI) address output pin 08.                                             |

| EBI_A09       | PE2  | PC9  | PC9  |         |   |   |   | External Bus Interface (EBI) address output pin 09.                                             |

| EBI_A10       | PE3  | PC10 | PC10 |         |   |   |   | External Bus Interface (EBI) address output pin 10.                                             |

| EBI_A11       | PE4  | PE4  | PE4  |         |   |   |   | External Bus Interface (EBI) address output pin 11.                                             |

| EBI_A12       | PE5  | PE5  | PE5  |         |   |   |   | External Bus Interface (EBI) address output pin 12.                                             |

| EBI_A13       | PE6  | PE6  | PE6  |         |   |   |   | External Bus Interface (EBI) address output pin 13.                                             |

| EBI_A14       | PE7  | PE7  | PE7  |         |   |   |   | External Bus Interface (EBI) address output pin 14.                                             |

| EBI_A15       | PC8  | PC8  | PC8  |         |   |   |   | External Bus Interface (EBI) address output pin 15.                                             |

| EBI_A16       | PB0  | PB0  | PB0  |         |   |   |   | External Bus Interface (EBI) address output pin 16.                                             |

| EBI_A17       | PB1  | PB1  | PB1  |         |   |   |   | External Bus Interface (EBI) address output pin 17.                                             |

| EBI_A18       | PB2  | PB2  | PB2  |         |   |   |   | External Bus Interface (EBI) address output pin 18.                                             |

| EBI_A19       | PB3  | PB3  | PB3  |         |   |   |   | External Bus Interface (EBI) address output pin 19.                                             |

| EBI_A20       | PB4  | PB4  | PB4  |         |   |   |   | External Bus Interface (EBI) address output pin 20.                                             |

| EBI_A21       | PB5  | PB5  | PB5  |         |   |   |   | External Bus Interface (EBI) address output pin 21.                                             |

| EBI_A22       | PB6  | PB6  | PB6  |         |   |   |   | External Bus Interface (EBI) address output pin 22.                                             |

| EBI_A23       | PC0  | PC0  | PC0  |         |   |   |   | External Bus Interface (EBI) address output pin 23.                                             |

| EBI_A24       | PC1  | PC1  | PC1  |         |   |   |   | External Bus Interface (EBI) address output pin 24.                                             |

| EBI_A25       | PC2  | PC2  | PC2  |         |   |   |   | External Bus Interface (EBI) address output pin 25.                                             |

| EBI_A26       | PC4  | PC4  | PC4  |         |   |   |   | External Bus Interface (EBI) address output pin 26.                                             |

| EBI_A27       | PD2  | PD2  | PD2  |         |   |   |   | External Bus Interface (EBI) address output pin 27.                                             |

| EBI_AD00      | PE8  | PE8  | PE8  |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 00.                       |

| EBI_AD01      | PE9  | PE9  | PE9  |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 01.                       |

| EBI_AD02      | PE10 | PE10 | PE10 |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 02.                       |

| EBI_AD03      | PE11 | PE11 | PE11 |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 03.                       |

| EBI_AD04      | PE12 | PE12 | PE12 |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 04.                       |

| EBI_AD05      | PE13 | PE13 | PE13 |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 05.                       |

| EBI_AD06      | PE14 | PE14 | PE14 |         |   |   |   | External Bus Interface (EBI) address and data input / out-<br>put pin 06.                       |

### **EFM°32**

### ...the world's most energy friendly microcontrollers

| Alternate     |      |      | LOC  | ATION |      |      |   |                                                                                                |

|---------------|------|------|------|-------|------|------|---|------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3     | 4    | 5    | 6 | Description                                                                                    |

| PCNT1_S1IN    | PC5  | PB4  |      |       |      |      |   | Pulse Counter PCNT1 input number 1.                                                            |

| PCNT2_S0IN    | PD0  | PE8  |      |       |      |      |   | Pulse Counter PCNT2 input number 0.                                                            |

| PCNT2_S1IN    | PD1  | PE9  |      |       |      |      |   | Pulse Counter PCNT2 input number 1.                                                            |

| PRS_CH0       | PA0  |      |      |       |      |      |   | Peripheral Reflex System PRS, channel 0.                                                       |

| PRS_CH1       | PA1  |      |      |       |      |      |   | Peripheral Reflex System PRS, channel 1.                                                       |

| PRS_CH2       | PC0  | PF5  |      |       |      |      |   | Peripheral Reflex System PRS, channel 2.                                                       |

| PRS_CH3       | PC1  | PE8  |      |       |      |      |   | Peripheral Reflex System PRS, channel 3.                                                       |

| TIM0_CC0      | PA0  | PA0  | PF6  | PD1   | PA0  | PF0  |   | Timer 0 Capture Compare input / output channel 0.                                              |

| TIM0_CC1      | PA1  | PA1  | PF7  | PD2   | PC0  | PF1  |   | Timer 0 Capture Compare input / output channel 1.                                              |

| TIM0_CC2      | PA2  | PA2  | PF8  | PD3   | PC1  | PF2  |   | Timer 0 Capture Compare input / output channel 2.                                              |

| TIM0_CDTI0    | PA3  |      |      |       | PC2  |      |   | Timer 0 Complimentary Deat Time Insertion channel 0.                                           |

| TIM0_CDTI1    | PA4  |      |      |       | PC3  |      |   | Timer 0 Complimentary Deat Time Insertion channel 1.                                           |

| TIM0_CDTI2    | PA5  |      | PF5  |       | PC4  | PF5  |   | Timer 0 Complimentary Deat Time Insertion channel 2.                                           |

| TIM1_CC0      |      | PE10 | PB0  | PB7   | PD6  |      |   | Timer 1 Capture Compare input / output channel 0.                                              |

| TIM1_CC1      |      | PE11 | PB1  | PB8   | PD7  |      |   | Timer 1 Capture Compare input / output channel 1.                                              |

| TIM1_CC2      |      | PE12 | PB2  | PB11  |      |      |   | Timer 1 Capture Compare input / output channel 2.                                              |

| TIM2_CC0      | PA8  | PA12 | PC8  |       |      |      |   | Timer 2 Capture Compare input / output channel 0.                                              |

| TIM2_CC1      | PA9  | PA13 | PC9  |       |      |      |   | Timer 2 Capture Compare input / output channel 1.                                              |

| TIM2_CC2      | PA10 | PA14 | PC10 |       |      |      |   | Timer 2 Capture Compare input / output channel 2.                                              |

| TIM3_CC0      | PE14 | PE0  |      |       |      |      |   | Timer 3 Capture Compare input / output channel 0.                                              |

| TIM3_CC1      | PE15 | PE1  |      |       |      |      |   | Timer 3 Capture Compare input / output channel 1.                                              |

| TIM3_CC2      | PA15 | PE2  |      |       |      |      |   | Timer 3 Capture Compare input / output channel 2.                                              |

| U0_RX         | PF7  | PE1  | PA4  |       |      |      |   | UARTO Receive input.                                                                           |

| U0_TX         | PF6  | PE0  | PA3  |       |      |      |   | UART0 Transmit output. Also used as receive input in half duplex communication.                |

| U1_RX         |      | PF11 | PB10 | PE3   |      |      |   | UART1 Receive input.                                                                           |

| U1_TX         |      | PF10 | PB9  | PE2   |      |      |   | UART1 Transmit output. Also used as receive input in half duplex communication.                |

| US0_CLK       | PE12 | PE5  | PC9  |       | PB13 | PB13 |   | USART0 clock input / output.                                                                   |

| US0_CS        | PE13 | PE4  | PC8  |       | PB14 | PB14 |   | USART0 chip select input / output.                                                             |

|               |      |      |      |       |      |      |   | USART0 Asynchronous Receive.                                                                   |

| US0_RX        | PE11 | PE6  | PC10 | PE12  | PB8  | PC1  |   | USART0 Synchronous mode Master Input / Slave Output (MISO).                                    |

| US0_TX        | PE10 | PE7  | PC11 | PE13  | PB7  | PC0  |   | USART0 Asynchronous Transmit.Also used as receive in-<br>put in half duplex communication.     |

|               |      |      |      |       |      |      |   | USART0 Synchronous mode Master Output / Slave Input (MOSI).                                    |

| US1_CLK       | PB7  | PD2  | PF0  |       |      |      |   | USART1 clock input / output.                                                                   |

| US1_CS        | PB8  | PD3  | PF1  |       |      |      |   | USART1 chip select input / output.                                                             |

| US1_RX        | PC1  | PD1  | PD6  |       |      |      |   | USART1 Asynchronous Receive.<br>USART1 Synchronous mode Master Input / Slave Output<br>(MISO). |

|               | PC0  | PD0  | PD7  |       |      |      |   | USART1 Asynchronous Transmit.Also used as receive in-<br>put in half duplex communication.     |

| US1_TX        |      |      |      |       |      |      |   | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                    |

The BGA112 Package uses SAC105 solderballs.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

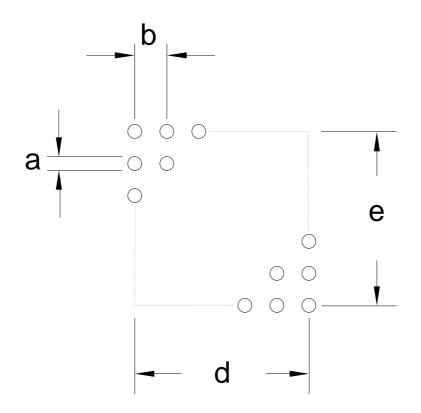

### Figure 5.2. BGA112 PCB Solder Mask

Table 5.2. BGA112 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.48      |

| b      | 0.80      |

| d      | 8.00      |

| e      | 8.00      |

Corrected BGA112 package drawing.

Updated PCB land pattern, solder mask and stencil design.

## 7.10 Revision 0.91

March 21th, 2011

Added new alternative locations for EBI and SWO.

Added new USB Pin to pinout table.

Corrected slew rate data for Opamps.

## 7.11 Revision 0.90

February 4th, 2011

Initial preliminary release.

# A Disclaimer and Trademarks

## A.1 Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

## A.2 Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISO-modem®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.