Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 42                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10wleafa-30 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RL78/L13 CHAPTER 1 OUTLINE

| Pin Count | Package                                               | Data Flash | Fields of<br>Application Note | Ordering Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------|------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64 pins   | 64-pin plastic LQFP<br>(12 × 12 mm, 0.65<br>mm pitch) | Mounted    | А                             | R5F10WLAAFA#30, R5F10WLAAFA#50, R5F10WLCAFA#30, R5F10WLCAFA#50, R5F10WLDAFA#50, R5F10WLEAFA#50, R5F10WLEAFA#30, R5F10WLFAFA#30, R5F10WLFAFA#30, R5F10WLFAFA#50, R5F10WLGAFA#50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | 64-pin plastic LFQFP<br>(10 × 10 mm, 0.5<br>mm pitch) | Mounted    | A                             | R5F10WLAAFB#30, R5F10WLAAFB#50, R5F10WLCAFB#30, R5F10WLCAFB#50, R5F10WLDAFB#50, R5F10WLEAFB#30, R5F10WLEAFB#30, R5F10WLFAFB#30, R5F10WLFAFB#30, R5F10WLFAFB#50, R5F10WLGAFB#50, R5F10WLGAFB#50 |

|           |                                                       |            | G                             | R5F10WLAGFB#30, R5F10WLAGFB#50, R5F10WLCGFB#30, R5F10WLCGFB#50, R5F10WLDGFB#30, R5F10WLDGFB#50, R5F10WLEGFB#30, R5F10WLFGFB#30, R5F10WLFGFB#30, R5F10WLFGFB#50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 80 pins   | 80-pin plastic LQFP<br>(14 × 14 mm, 0.65<br>mm pitch) | Mounted    | A                             | R5F10WMAAFA#30, R5F10WMAAFA#50, R5F10WMCAFA#30, R5F10WMCAFA#50, R5F10WMDAFA#50, R5F10WMEAFA#30, R5F10WMEAFA#30, R5F10WMFAFA#30, R5F10WMFAFA#50, R5F10WMGAFA#50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | 80-pin plastic LFQFP<br>(12 × 12 mm, 0.5<br>mm pitch) | Mounted    | A                             | R5F10WMAAFB#30, R5F10WMAAFB#50, R5F10WMCAFB#30, R5F10WMCAFB#50, R5F10WMDAFB#50, R5F10WMEAFB#50, R5F10WMFAFB#30, R5F10WMFAFB#30, R5F10WMFAFB#50, R5F10WMGAFB#50, R5F10WMGAFB#50, R5F10WMGAFB#50, R5F10WMGAFB#50, R5F10WMGAFB#50,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |                                                       |            | G                             | R5F10WMAGFB#30, R5F10WMAGFB#50, R5F10WMCGFB#30, R5F10WMCGFB#50, R5F10WMDGFB#30, R5F10WMEGFB#50, R5F10WMEGFB#30, R5F10WMEGFB#30, R5F10WMFGFB#50, R5F10WMGGFB#50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note For the fields of application, see Figure 1-1 Part Number, Memory Size, and Package of RL78/L13.

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

RL78/L13 CHAPTER 1 OUTLINE

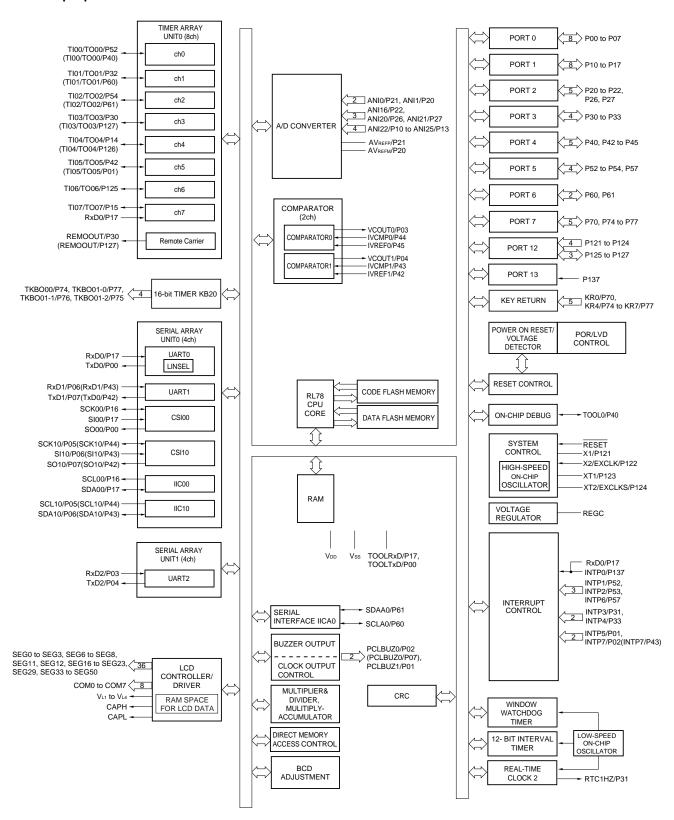

### 1.5 Block Diagram

#### 1.5.1 64-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR).

Table 5-4. Changing CPU Clock (2/2)

| CPU                      | Clock                                      | Condition Before Change                                                                                                                                                                  | Processing After Change                                          |

|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Before Change            | After Change                               |                                                                                                                                                                                          |                                                                  |

| XT1 clock                | High-speed on-<br>chip oscillator<br>clock | The high-speed on-chip oscillator is oscillating and the high-speed on-chip oscillator clock is selected as the main system clock  • HIOSTOP = 0, MCS = 0                                | XT1 oscillation can be stopped (XTSTOP = 1)                      |

|                          | X1 clock                                   | X1 oscillation is stable and the high-speed system clock is selected as the main system clock  OSCSEL = 1, EXCLK = 0, MSTOP = 0  The oscillation stabilization time has elapsed  MCS = 1 |                                                                  |

|                          | External main system clock                 | Inputting the external clock from the EXCLK pin is enabled and the high-speed system clock is selected as the main system clock  OSCSEL = 1, EXCLK = 1, MSTOP = 0  MCS = 1               |                                                                  |

|                          | External subsystem clock                   | Transition impossible                                                                                                                                                                    | -                                                                |

| External subsystem clock | High-speed on-<br>chip oscillator<br>clock | The high-speed on-chip oscillator is oscillating and the high-speed on-chip oscillator clock is selected as the main system clock  • HIOSTOP = 0, MCS = 0                                | Inputting external subsystem clock can be disabled (XTSTOP = 1). |

|                          | X1 clock                                   | X1 oscillation is stable and the high-speed system clock is selected as the main system clock  OSCSEL = 1, EXCLK = 0, MSTOP = 0  The oscillation stabilization time has elapsed  MCS = 1 |                                                                  |

|                          | External main system clock                 | Inputting the external clock from the EXCLK pin is enabled and the high-speed system clock is selected as the main system clock  OSCSEL = 1, EXCLK = 1, MSTOP = 0  MCS = 1               |                                                                  |

|                          | XT1 clock                                  | Transition impossible                                                                                                                                                                    | -                                                                |

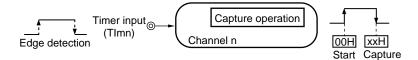

### (5) Measurement of high-/low-level width of input signal

Counting is started by a single edge of the signal input to the timer input pin (Tlmn), and the count value is captured at the other edge. In this way, the high-level or low-level width of the input signal can be measured.

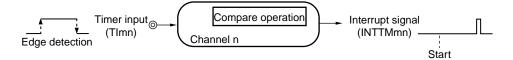

#### (6) Delay counter

Counting is started at the valid edge of the signal input to the timer input pin (Tlmn), and an interrupt is generated after any delay period.

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7)

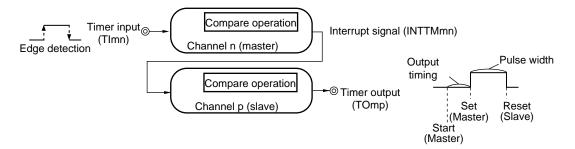

## 6.1.2 Simultaneous channel operation function

By using the combination of a master channel (a reference timer mainly controlling the cycle) and slave channels (timers operating according to the master channel), channels can be used for the following purposes.

### (1) One-shot pulse output

Two channels are used as a set to generate a one-shot pulse with a specified output timing and a specified pulse width.

### (2) PWM (Pulse Width Modulation) output

Two channels are used as a set to generate a pulse with a specified period and a specified duty factor.

(Caution and Remark are listed on the next page.)

### 6.5.3 Operation of counter

Here, the counter operation in each mode is explained.

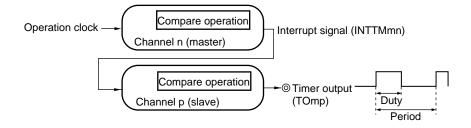

### (1) Operation of interval timer mode

- <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit. Timer count register mn (TCRmn) holds the initial value until count clock generation.

- <2> A start trigger is generated at the first count clock after operation is enabled.

- <3> When the MDmn0 bit is set to 1, INTTMmn is generated by the start trigger.

- <4> By the first count clock after the operation enable, the value of timer data register mn (TDRmn) is loaded to the TCRmn register and counting starts in the interval timer mode.

- <5> When the TCRmn register counts down and its count value is 0000H, INTTMmn is generated and the value of timer data register mn (TDRmn) is loaded to the TCRmn register and counting keeps on.

Figure 6-27. Operation Timing (In Interval Timer Mode)

Caution In the operation in the first count clock cycle after writing the TSmn bit, an error at a maximum of one count clock cycle occurs since count start delays until count clock has been generated.

When the information on count start timing is necessary, an interrupt can be generated when counting is started by setting MDmn0 = 1.

Remark fmck, the start trigger detection signal, and INTTMmn become active for one clock cycle in synchronization with fclk.

Figure 6-72. Operation Procedure When PWM Function Is Used (2/2)

|                     | Software operation                                                                                                                                                                                                                                                                                             | Hardware status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operation<br>start  | Sets the TOEmp bit (slave) to 1 (only when operation is resumed).  The TSmn (master) and TSmp (slave) bits of timer channel start register m (TSm) are set to 1 at the same time.  The TSmn and TSmp bits automatically return to 0 because they are trigger bits.                                             | TEmn = 1, TEmp = 1  ➤ When the master channel starts counting, INTTMmn is generated. Triggered by this interrupt, the slave channel also starts counting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| During<br>operation | Set values of the TMRmn and TMRmp registers, TOMmn, TOMmp, TOLmn, and TOLmp bits cannot be changed. Set values of the TDRmn and TDRmp registers can be changed after INTTMmn of the master channel is generated. The TCRmn and TCRmp registers can always be read. The TSRmn and TSRmp registers are not used. | The counter of the master channel loads the TDRmn register value to timer count register mn (TCRmn), and counts down. When the count value reaches TCRmn = 0000H, INTTMmn output is generated. At the same time, the value of the TDRmn register is loaded to the TCRmn register, and the counter starts counting down again. At the slave channel, the value of the TDRmp register is loaded to the TCRmp register, triggered by INTTMmn of the master channel, and the counter starts counting down. The output level of TOmp becomes active one count clock after generation of the INTTMmn output from the master channel. It becomes inactive when TCRmp = 0000H, and the counting operation is stopped. |  |  |

| Operation stop      | The TTmn (master) and TTmp (slave) bits are set to 1 at the same time.  The TTmn and TTmp bits automatically return to 0 because they are trigger bits.                                                                                                                                                        | TEmn, TEmp = 0, and count operation stops.  The TCRmn and TCRmp registers hold count value and stop.  The TOmp output is not initialized but holds current status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                     | The TOEmp bit of slave channel is cleared to 0 and value is set to the TOmp bit.                                                                                                                                                                                                                               | The TOmp pin outputs the TOmp set level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TAU<br>stop         | To hold the TOmp pin output level Clears the TOmp bit to 0 after the value to be held is set to the port register. When holding the TOmp pin output level is not necessary Setting not required.                                                                                                               | The TOmp pin output level is held by port function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                     | The TAUmEN bit of the PER0 register is cleared to 0.                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Remark m: Unit number (m = 0), n: Channel number (n = 0, 2, 4, 6)

p: Slave channel number (n \leq 7)

**Remark** Critical conduction mode is a PFC control method that activates a switching FET by detecting zero level of inductor current.

# 7.2 Configuration of 16-bit Timer KB20

16-bit timer KB20 includes the following hardware.

Table 7-1. Configuration of 16-bit Timer KB20

| Item              | Configuration                                                                    |

|-------------------|----------------------------------------------------------------------------------|

| Timer/counter     | 16-bit timer counter KB20 (TKBCNT0)                                              |

| Registers         | 16-bit timer KB2 compare registers 00 to 03 (TKBCR00 to TKBCR03)                 |

| Timer output      | TKBO00, TKBO01-0, TKBO01-1, TKBO01-2                                             |

| Control registers | Peripheral enable register (PER1)                                                |

|                   | Timer clock select register (TKBPSCS0)                                           |

|                   | 16-bit timer KB2 operation control register 00 (TKBCTL00)                        |

|                   | 16-bit timer KB2 operation control register 01 (TKBCTL01)                        |

|                   | 16-bit timer KB2 output control register 00 (TKBIOC00)                           |

|                   | 16-bit timer KB2 output control register 01 (TKBIOC01)                           |

|                   | 16-bit timer KB2 flag register 0 (TKBFLG0)                                       |

|                   | 16-bit timer KB2 trigger register 0 (TKBTRG0)                                    |

|                   | 16-bit timer KB2 flag clear trigger register 0 (TKBCLR0)                         |

|                   | 16-bit timer KB2 dithering count registers 00, 01 (TKBDNR00, TKBDNR01)           |

|                   | 16-bit timer KB2 compare 1L & dithering count register 00 (TKBCRLD00)            |

|                   | 16-bit timer KB2 compare 3L & dithering count register 01 (TKBCRLD01)            |

|                   | 16-bit timer KB2 smooth start initial duty registers 00, 01 (TKBSIR00, TKBSIR01) |

|                   | 16-bit timer KB2 smooth start step width registers 00, 01 (TKBSSR00, TKBSSR01)   |

|                   | 16-bit timer KB2 maximum frequency limit setting register 0 (TKBMFR0)            |

|                   | 16-bit timer KB2 counter restart select register (ELSELRn)                       |

|                   | 16-bit timer KB2 output switch register (PWCTKB)                                 |

|                   | Forced output stop function control register 0 (TKBPACTL00)                      |

|                   | Forced output stop function control register 1 (TKBPACTL01)                      |

|                   | Forced output stop function control register 2 (TKBPACTL02)                      |

|                   | Forced output stop function flag register (TKBPAFLG0)                            |

|                   | Forced output stop function 1 start register (TKBPAHFS0)                         |

|                   | Forced output stop function 1 stop register (TKBPAHFT0)                          |

|                   | Port mode register 7 (PM7)                                                       |

|                   | Port register 7 (P7)                                                             |

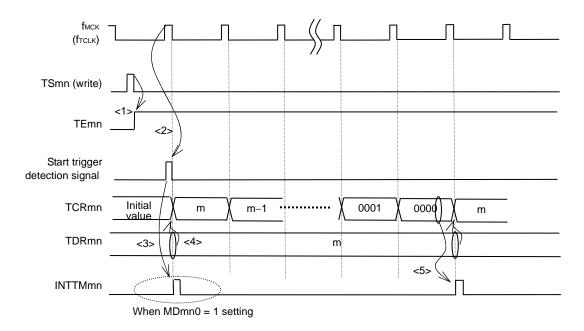

## (4) To combine PWM output smooth start function with PWM output dithering function

PWM output dithering function is invalid during the execution of PWM output smooth start function (TKBSSF0p = 1). PWM output dithering function will be valid when PWM output smooth start function is stopped (TKBSSF0p = 0).

## (5) Completion of PWM output smooth start function and operation of TKBSSF0p

The following figure shows when TKBCR01 is 0007H, TKBDNR0p is 70H and TKBSSR0p is 02H. At the timing that TKBCR01 = 0007H and the value of TKBCR01 buffer for internal smooth start matches, TKBSSF0p is cleared, and then dithering function begins.

Figure 7-63. Completion of PWM Output Smooth Start Function and Operation of TKBSSF0p

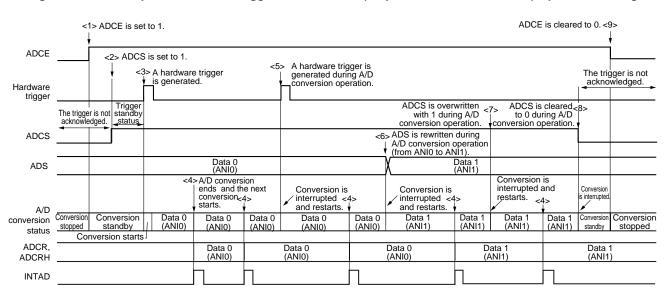

#### 12.6.3 Hardware trigger no-wait mode (sequential conversion mode)

- <1> In the stop status, the ADCE bit of A/D converter mode register 0 (ADM0) is set to 1, and the system enters the A/D conversion standby status.

- <2> After the software counts up to the stabilization wait time (1 µs), the ADCS bit of the ADM0 register is set to 1 to place the system in the hardware trigger standby status (and conversion does not start at this stage). Note that, while in this status, A/D conversion does not start even if ADCS is set to 1.

- <3> If a hardware trigger is input while ADCS = 1, A/D conversion is performed on the analog input specified by the analog input channel specification register (ADS).

- <4> When A/D conversion ends, the conversion result is stored in the A/D conversion result register (ADCR, ADCRH), and the A/D conversion end interrupt request signal (INTAD) is generated. After A/D conversion ends, the next A/D conversion immediately starts.

- <5> If a hardware trigger is input during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <6> When the value of the ADS register is rewritten or overwritten during conversion operation, the current A/D conversion is interrupted, and A/D conversion is performed on the analog input respecified by the ADS register. The partially converted data is discarded.

- <7> When ADCS is overwritten with 1 during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <8> When ADCS is cleared to 0 during conversion operation, the current A/D conversion is interrupted, and the system enters the A/D conversion standby status. However, the A/D converter does not stop in this status.

- <9> When ADCE is cleared to 0 while in the A/D conversion standby status, the A/D converter enters the stop status.

When ADCS = 0, inputting a hardware trigger is ignored and A/D conversion does not start.

Figure 12-19. Example of Hardware Trigger No-Wait Mode (Sequential Conversion Mode) Operation Timing

| C0VRF | Comparator 0 reference voltage selection Notes 1, 4, 5, 6             |  |

|-------|-----------------------------------------------------------------------|--|

| 0     | Comparator 0 reference voltage is IVREF0 input                        |  |

| 1     | Comparator 0 reference voltage is internal reference voltage (1.45 V) |  |

| C0WDE | Comparator 0 window mode selection Note 2 |  |

|-------|-------------------------------------------|--|

| 0     | Comparator 0 standard mode                |  |

| 1     | Comparator 0 window mode                  |  |

| C0ENB | Comparator 0 operation enable   |  |

|-------|---------------------------------|--|

| 0     | Comparator 0 operation disabled |  |

| 1     | Comparator 0 operation enabled  |  |

- Notes 1. Valid only when standard mode is selected. In window mode, the reference voltage in the comparator is selected regardless of the setting of this bit.

- 2. Window mode cannot be set when low-speed mode is selected (the SPDMD bit in the COMPOCR register

- 3. The initial value is 0 immediately after a reset is released. However, the value is undefined when C0ENB is set to 0 and C1ENB is set to 0 after operation of the comparator is enabled once.

- 4. The internal reference voltage (1.45 V) can be selected in HS (high-speed main) mode. When the internal reference voltage (1.45 V) is selected in HS (high-speed main) mode, the temperature sensor output cannot be A/D converted.

- 5. Do not select the internal reference voltage in STOP mode.

- 6. Do not select the internal reference voltage when the subsystem clock (fxT) is selected as the CPU clock and both the high-speed system clock (fmx) and high-speed on-chip oscillator clock (fih) are stopped.

- 7. Writing to this bit is ignored.

Reference input voltage (IVREFi or internal reference voltage (1.45 V))

CIMON bit in COMPMDR register 0

In low-speed mode, longer delay time until the determined-result output, but lower power consumption In high-speed mode, shorter delay time until the determined-result output, but lower power consumption In high-speed mode, shorter delay time until the determined-result output, but higher power consumption (A)

Figure 13-6. Example of Comparator i (i = 0 or 1) Operation in Standard Mode

Caution The above diagram applies when CiFCK1 and CiFCK0 in the COMPFIR register = 00B (no filter) and CiEDG = 1 (both edges). When CiEDG = 0 and CiEPO = 0 (rising edge), CMPIFi changes as shown by (A) only. When CiEDG = 0 and CiEPO = 1 (falling edge), CMPIFi changes as shown by (B) only.

Set to 0 by a program

Figure 13-7. Example of Comparator i (i = 0 or 1) Operation in Window Mode

Reference on high-voltage side

Reference on low-voltage side

CiMON bit in COMPMDR register 0

CMPIFi bit in interrupt control register 0

(A) (B) (A) (B) (B)

• Operation example in window mode

Caution The above diagram applies when CiFCK1 and CiFCK0 in the COMPFIR register = 00B (no filter) and CiEDG = 1 (both edges). When CiEDG = 0 and CiEPO = 0 (rising edge), CMPIFi changes as shown by (A) only. When CiEDG = 0 and CiEPO = 1 (falling edge), CMPIFi changes as shown by (B) only.

Figure 15-6. Format of IICA Control Register n0 (IICCTLn0) (3/4)

| STTn <sup>Notes</sup>                                                                                                                                                                                                                                                | Start condition trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| 0                                                                                                                                                                                                                                                                    | Do not generate a start condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |  |

| 1                                                                                                                                                                                                                                                                    | When bus is released (in standby state, when IICBSYn = 0):  If this bit is set (1), a start condition is generated (startup as the master).  When a third party is communicating:  • When communication reservation function is enabled (IICRSVn = 0)  Functions as the start condition reservation flag. When set to 1, automatically generates a start condition after the bus is released.  • When communication reservation function is disabled (IICRSVn = 1)  Even if this bit is set (1), the STTn bit is cleared and the STTn clear flag (STCFn) is set (1). No start condition is generated.  In the wait state (when master device):  Generates a restart condition after releasing the wait. |                                  |  |

| For maste     For maste                                                                                                                                                                                                                                              | Cautions concerning set timing  • For master reception: Cannot be set to 1 during transfer. Can be set to 1 only in the waiting period when the ACKEn bit has been cleared to 0 and slave has been notified of final reception.  • For master transmission: A start condition cannot be generated normally during the acknowledge period. Set to 1 during the wait period that follows output of the ninth clock.  • Cannot be set to 1 at the same time as stop condition trigger (SPTn).                                                                                                                                                                                                              |                                  |  |

|                                                                                                                                                                                                                                                                      | or clearing (STTn = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Condition for setting (STTn = 1) |  |

| Cleared by setting the STTn bit to 1 while communication reservation is prohibited. Cleared by loss in arbitration Cleared after start condition is generated by master device Cleared by LRELn = 1 (exit from communications) When IICEn = 0 (operation stop) Reset |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • Set by instruction             |  |

- Notes 1. The signal of this bit is invalid while IICEn is 0.

- 2. The STTn bit is always read as 0.

Remarks 1. Bit 1 (STTn) becomes 0 when it is read after data setting.

IICRSVn: Bit 0 of IIC flag register n (IICFn)STCFn: Bit 7 of IIC flag register n (IICFn)

**3.** n = 0

Figure 15-8. Format of IICA Flag Register n (IICFn)

| Address | : FFF52H | After r | eset: 00H | R/W <sup>No</sup> | ote |   |        |         |

|---------|----------|---------|-----------|-------------------|-----|---|--------|---------|

| Symbol  | <7>      | <6>     | 5         | 4                 | 3   | 2 | <1>    | <0>     |

| IICFn   | STCFn    | IICBSYn | 0         | 0                 | 0   | 0 | STCENn | IICRSVn |

| STCFn                                                                 | STTn clear flag                                              |                                                                                                                                       |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0                                                                     | Generate start condition                                     |                                                                                                                                       |  |  |

| 1                                                                     | Start condition generation unsuccessful: clear the STTn flag |                                                                                                                                       |  |  |

| Condition for clearing (STCFn = 0)  Condition for setting (STCFn = 1) |                                                              |                                                                                                                                       |  |  |

| Cleared by STTn = 1     When IICEn = 0 (operation stop)     Reset     |                                                              | Generating start condition unsuccessful and the<br>STTn bit cleared to 0 when communication<br>reservation is disabled (IICRSVn = 1). |  |  |

| IICBSYn                                                                   | I <sup>2</sup> C bus status flag                                        |                                                                                                    |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| 0                                                                         | Bus release status (communication initial status when STCENn = 1)       |                                                                                                    |  |  |

| 1                                                                         | Bus communication status (communication initial status when STCENn = 0) |                                                                                                    |  |  |

| Condition                                                                 | n for clearing (IICBSYn = 0)                                            | Condition for setting (IICBSYn = 1)                                                                |  |  |

| Detection of stop condition     When IICEn = 0 (operation stop)     Reset |                                                                         | <ul> <li>Detection of start condition</li> <li>Setting of the IICEn bit when STCENn = 0</li> </ul> |  |  |

| STCENn                                                                                          | Initial start enable trigger                                                                                       |                                                                                                                    |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0                                                                                               | After operation is enabled (IICEn = 1), enable generation of a start condition upon detection of a stop condition. |                                                                                                                    |  |  |  |  |  |  |

| 1                                                                                               | After operation is enabled (IICEn = 1), enable a stop condition.                                                   | After operation is enabled (IICEn = 1), enable generation of a start condition without detecting a stop condition. |  |  |  |  |  |  |

| Condition                                                                                       | for clearing (STCENn = 0)                                                                                          | Condition for setting (STCENn = 1)                                                                                 |  |  |  |  |  |  |

| <ul> <li>Cleared by instruction</li> <li>Detection of start condition</li> <li>Reset</li> </ul> |                                                                                                                    | Set by instruction                                                                                                 |  |  |  |  |  |  |

| IICRSVn                          | Communication reservation function disable bit |                                     |  |  |  |  |  |

|----------------------------------|------------------------------------------------|-------------------------------------|--|--|--|--|--|

| 0                                | Enable communication reservation               |                                     |  |  |  |  |  |

| 1                                | Disable communication reservation              | Disable communication reservation   |  |  |  |  |  |

| Condition                        | for clearing (IICRSVn = 0)                     | Condition for setting (IICRSVn = 1) |  |  |  |  |  |

| Cleared by instruction     Reset |                                                | Set by instruction                  |  |  |  |  |  |

Note Bits 6 and 7 are read-only.

Cautions 1. Write to the STCENn bit only when the operation is stopped (IICEn = 0).

- As the bus release status (IICBSYn = 0) is recognized regardless of the actual bus status when STCENn = 1, when generating the first start condition (STTn = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSVn only when the operation is stopped (IICEn = 0).

Remarks 1. STTn: Bit 1 of IICA control register no (IICCTLno)

IICEn: Bit 7 of IICA control register n0 (IICCTLn0)

**2.** n = 0

Table 16-4. Combinations of Display Waveform, Time Slices, Bias Method, and Frame Frequency

| Display Mode        |                             |           | Set Value |       |       |       |       |       | Driving Voltage Generation Method  |                                 |                        |  |

|---------------------|-----------------------------|-----------|-----------|-------|-------|-------|-------|-------|------------------------------------|---------------------------------|------------------------|--|

| Display<br>Waveform | Number<br>of Time<br>Slices | Bias Mode | LWAVE     | LDTY2 | LDTY1 | LDTY0 | LBAS1 | LBAS0 | External<br>Resistance<br>Division | Internal<br>Voltage<br>Boosting | Capacitor<br>Split     |  |

| Waveform A          | 8                           | 1/4       | 0         | 1     | 0     | 1     | 1     | 0     | O<br>(24 to 128<br>Hz)             | (24 to 64 Hz)                   | ×                      |  |

| Waveform A          | 4                           | 1/3       | 0         | 0     | 1     | 1     | 0     | 1     | O<br>(24 to 128<br>Hz)             | (24 to 128<br>Hz)               | O<br>(24 to 128<br>Hz) |  |

| Waveform A          | 3                           | 1/3       | 0         | 0     | 1     | 0     | 0     | 1     | (32 to 128<br>Hz)                  | (32 to 128<br>Hz)               | (32 to 128<br>Hz)      |  |

| Waveform A          | 3                           | 1/2       | 0         | 0     | 1     | 0     | 0     | 0     | (32 to 128<br>Hz)                  | ×                               | ×                      |  |

| Waveform A          | 2                           | 1/2       | 0         | 0     | 0     | 1     | 0     | 0     | (24 to 128<br>Hz)                  | ×                               | ×                      |  |

| Waveform A          | Static                      |           | 0         | 0     | 0     | 0     | 0     | 0     | (24 to 128<br>Hz)                  | ×                               | ×                      |  |

| Waveform B          | 8                           | 1/4       | 1         | 1     | 0     | 1     | 1     | 0     | O<br>(24 to 128<br>Hz)             | (24 to 64 Hz)                   | ×                      |  |

|                     | 4                           | 1/3       | 1         | 0     | 1     | 1     | 0     | 1     | O<br>(24 to 128                    | O<br>(24 to 128                 | O<br>(24 to 128        |  |

| Waveform B          |                             |           |           |       |       |       |       |       | Hz)                                | Hz)                             | Hz)                    |  |

Remark O: Supported

×: Not supported

### 16.3.4 LCD clock control register 0 (LCDC0)

LCDC0 specifies the LCD clock.

The frame frequency is determined according to the LCD clock and the number of time slices.

This register is set by using an 8-bit memory manipulation instruction.

Reset signal generation sets LCDC0 to 00H.

Figure 16-5. Format of LCD Clock Control Register 0 (LCDC0)

Address: FFF42H

After reset: 00H

R/W

Symbol

7

6

5

4

3

2

1

0

LCDC0

0

0

LCDC05

LCDC04

LCDC03

LCDC02

LCDC01

LCDC00

| LCDC05 | LCDC04 | LCDC03   | LCDC02   | LCDC01 | LCDC00 | LCD clock (LCDCL)                         |

|--------|--------|----------|----------|--------|--------|-------------------------------------------|

| 0      | 0      | 0        | 1        | 0      | 0      | fsuв/2 <sup>5</sup> or fi∟/2 <sup>5</sup> |

| 0      | 0      | 0        | 1        | 0      | 1      | fsuB/2 <sup>6</sup> or fiL/2 <sup>6</sup> |

| 0      | 0      | 0        | 1        | 1      | 0      | fsub/2 <sup>7</sup> or fit/2 <sup>7</sup> |

| 0      | 0      | 0        | 1        | 1      | 1      | fsuв/2 <sup>8</sup> or fi∟/2 <sup>8</sup> |

| 0      | 0      | 1        | 0        | 0      | 0      | fsuB/29 or fil/29                         |

| 0      | 0      | 1        | 0        | 0      | 1      | fsua/2 <sup>10</sup>                      |

| 0      | 1      | 0        | 0        | 1      | 1      | fmain/2 <sup>10</sup>                     |

| 0      | 1      | 0        | 1        | 0      | 0      | fmain/2 <sup>11</sup>                     |

| 0      | 1      | 0        | 1        | 0      | 1      | fmain/2 <sup>12</sup>                     |

| 0      | 1      | 0        | 1        | 1      | 0      | fmain/2 <sup>13</sup>                     |

| 0      | 1      | 0        | 1        | 1      | 1      | fmain/2 <sup>14</sup>                     |

| 0      | 1      | 1        | 0        | 0      | 0      | fmain/2 <sup>15</sup>                     |

| 0      | 1      | 1        | 0        | 0      | 1      | f <sub>MAIN</sub> /2 <sup>16</sup>        |

| 0      | 1      | 1        | 0        | 1      | 0      | fmain/2 <sup>17</sup>                     |

| 0      | 1      | 1        | 0        | 1      | 1      | f <sub>MAIN</sub> /2 <sup>18</sup>        |

| 1      | 0      | 1        | 0        | 1      | 1      | f <sub>MAIN</sub> /2 <sup>19</sup>        |

|        |        | Other th | an above |        |        | Setting prohibited                        |

Cautions 1. Do not set LCDC0 when the SCOC bit of the LCDM1 register is 1.

- 2. Be sure to set bits 6 and 7 to "0".

- 3. When the internal voltage boosting method or capacitor split method is set, set the LCD clock (LCDCL) as follows:

- 512 Hz or less when fsuB is selected.

- 235 Hz or less when fil is selected.

For details, see Table 16-4. Combinations of Display Waveform, Time Slices, Bias Method, and Frame Frequency.

Remark fmain: Main system clock frequency

fıL: Low-speed on-chip oscillator clock frequency

fsub: Subsystem clock frequency

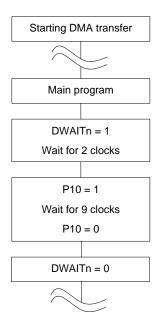

### 18.5.4 Holding DMA transfer pending by DWAITn bit

When DMA transfer is started, transfer is performed while an instruction is executed. At this time, the operation of the CPU is stopped and delayed for the duration of 2 clocks. If this poses a problem to the operation of the set system, a DMA transfer can be held pending by setting the DWAITn bit to 1. The DMA transfer for a transfer trigger that occurred while DMA transfer was held pending is executed after the pending status is canceled. However, because only one transfer trigger can be held pending for each channel, even if multiple transfer triggers occur for one channel during the pending status, only one DMA transfer is executed after the pending status is canceled.

To output a pulse with a width of 10 clocks of the operating frequency from the P10 pin, for example, the clock width increases to 12 if a DMA transfer is started midway. In this case, the DMA transfer can be held pending by setting the DWAITn bit to 1.

After setting the DWAITn bit to 1, it takes two clocks until a DMA transfer is held pending.

Figure 18-10. Example of Setting for Holding DMA Transfer Pending by DWAITn Bit

Caution When DMA transfer is held pending while using two or more DMA channels, be sure to held the DMA transfer pending for all channels (by setting DWAIT0, DWAIT1, DWAIT2, and DWAIT3 to 1). If the DMA transfer of one channel is executed while that of the other channel is held pending, DMA transfer might not be held pending for the latter channel.

**Remarks 1.** n: DMA channel number (n = 0 to 3)

2. 1 clock: 1/fclk (fclk: CPU clock)

Figure 27-2. Format of User Option Byte (000C1H/010C1H) (2/2)

Address: 000C1H/010C1HNote

| 7     | 6     | 5     | 4 | 3     | 2     | 1       | 0       |

|-------|-------|-------|---|-------|-------|---------|---------|

| VPOC2 | VPOC1 | VPOC0 | 1 | LVIS1 | LVIS0 | LVIMDS1 | LVIMDS0 |

### • LVD setting (interrupt mode)

| Detection voltage |              | Option byte setting value |         |       |                           |   |       |   |  |  |  |

|-------------------|--------------|---------------------------|---------|-------|---------------------------|---|-------|---|--|--|--|

| Vı                | _VD          | Mode                      | setting | VPOC2 | VPOC2 VPOC1 VPOC0 LVIS1 L |   | LVIS0 |   |  |  |  |

| Rising edge       | Falling edge | LVIMDS1                   | LVIMDS0 |       |                           |   |       |   |  |  |  |

| 1.67 V            | 1.63 V       | 0                         | 1       | 0     | 0                         | 0 | 1     | 1 |  |  |  |

| 1.77 V            | 1.73 V       |                           |         | 0     | 0                         | 0 | 1     | 0 |  |  |  |

| 1.88 V            | 1.84 V       |                           |         | 0     | 0                         | 1 | 1     | 1 |  |  |  |

| 1.98 V            | 1.94 V       |                           |         | 0     | 0                         | 1 | 1     | 0 |  |  |  |

| 2.09 V            | 2.04 V       |                           |         | 0     | 0                         | 1 | 0     | 1 |  |  |  |

| 2.50 V            | 2.45 V       |                           |         | 0     | 1                         | 0 | 1     | 1 |  |  |  |

| 2.61 V            | 2.55 V       |                           |         | 0     | 1                         | 0 | 1     | 0 |  |  |  |

| 2.71 V            | 2.65 V       |                           |         | 0     | 1                         | 0 | 0     | 1 |  |  |  |

| 2.81 V            | 2.75 V       |                           |         | 0     | 1                         | 1 | 1     | 1 |  |  |  |

| 2.92 V            | 2.86 V       |                           |         | 0     | 1                         | 1 | 1     | 0 |  |  |  |

| 3.02 V            | 2.96 V       |                           |         | 0     | 1                         | 1 | 0     | 1 |  |  |  |

| 3.13 V            | 3.06 V       |                           |         | 0     | 0                         | 1 | 0     | 0 |  |  |  |

| 3.75 V            | 3.67 V       |                           |         | 0     | 1                         | 0 | 0     | 0 |  |  |  |

| 4.06 V            | 3.98 V       |                           |         | 0     | 1                         | 1 | 0     | 0 |  |  |  |

| Other that        | an above     | Setting prohil            | bited   |       |                           |   |       |   |  |  |  |

## • LVD setting (LVDOFF)

| Detection voltage |              | Option byte setting value |                    |       |       |       |       |       |  |  |  |

|-------------------|--------------|---------------------------|--------------------|-------|-------|-------|-------|-------|--|--|--|

| V <sub>LVD</sub>  |              | Mode setting              |                    | VPOC2 | VPOC1 | VPOC0 | LVIS1 | LVIS0 |  |  |  |

| Rising edge       | Falling edge | LVIMDS1                   | LVIMDS0            |       |       |       |       |       |  |  |  |

| _                 | -            | ×                         | 1                  | 1     | ×     | ×     | ×     | ×     |  |  |  |

| Other than above  |              | Setting prohil            | Setting prohibited |       |       |       |       |       |  |  |  |

**Note** Set the same value as 000C1H to 010C1H when the boot swap operation is used because 000C1H is replaced by 010C1H.

### Cautions 1. Be sure to set bit 4 to "1".

2. After power is supplied, the reset state must be retained until the operating voltage becomes in the range defined in 32.4 or 33.4 AC Characteristics. This is done by utilizing the voltage detection circuit or controlling the externally input reset signal. After the power supply is turned off, this LSI should be placed in the STOP mode, or placed in the reset state by utilizing the voltage detection circuit or controlling the externally input reset signal, before the voltage falls below the operating range. The range of operating voltage varies with the setting of the user option byte (000C2H or 010C2H).

#### Remarks 1. x: don't care

- 2. For details on the LVD circuit, see CHAPTER 24 VOLTAGE DETECTOR.

- 3. The detection voltage is a typical value. For details, see 32.6.5 or 33.6.5 LVD circuit characteristics.

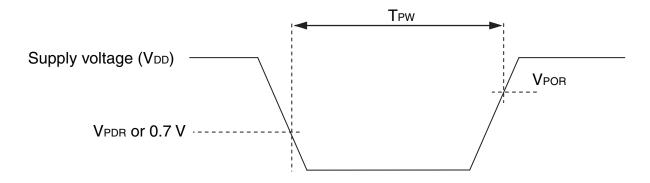

### 32.6.4 POR circuit characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{ Vss} = 0 \text{ V})$

| Parameter                           | Symbol           | Conditions                               | MIN. | TYP. | MAX. | Unit |

|-------------------------------------|------------------|------------------------------------------|------|------|------|------|

| Detection voltage                   | VPOR             | V <sub>POR</sub> When power supply rises |      | 1.51 | 1.55 | V    |

|                                     | V <sub>PDR</sub> | When power supply falls                  | 1.46 | 1.50 | 1.54 | V    |

| Minimum pulse width <sup>Note</sup> | Tpw              |                                          | 300  |      |      | μs   |

Note This is the time required for the POR circuit to execute a reset operation when VDD falls below VPDR. When the microcontroller enters STOP mode and when the main system clock (fMAIN) has been stopped by setting bit 0 (HIOSTOP) and bit 7 (MSTOP) of the clock operation status control register (CSC), this is the time required for the POR circuit to execute a reset operation between when VDD falls below 0.7 V and when VDD rises to VPOR or higher.

(Ta = -40 to +105°C, 2.4 V  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V)

| Parameter                                             | Symbol                          |                                                                                      | Condition                              | MIN.                             | TYP.                                                                        | MAX. | Unit       |            |          |

|-------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|-----------------------------------------------------------------------------|------|------------|------------|----------|

| Low-speed on-<br>chip oscillator<br>operating current | I <sub>FIL</sub> Note 1         |                                                                                      |                                        | 0.20                             |                                                                             | μΑ   |            |            |          |

| RTC2 operating current                                | IRTC Notes 1, 2, 3              | fsuв = 32.768 kHz                                                                    | fsuB = 32.768 kHz                      |                                  |                                                                             |      |            |            | μΑ       |

| 12-bit interval timer operating current               | I <sub>TMKA</sub> Notes 1, 2, 4 |                                                                                      |                                        | 0.04                             |                                                                             | μΑ   |            |            |          |

| Watchdog timer operating current                      | Notes 1, 2, 5                   | fı∟ = 15 kHz                                                                         |                                        | 0.22                             |                                                                             | μΑ   |            |            |          |

| A/D converter operating current                       | IADC Notes 1, 6                 | When conversion at maximum speed                                                     | Normal mode                            |                                  |                                                                             |      | 1.3<br>0.5 | 1.7<br>0.7 | mA<br>mA |

| A/D converter reference voltage current               | ladref Note 1                   |                                                                                      | Low voltage mode, AVREFP = VDD = 3.0 V |                                  |                                                                             |      | 75.0       |            | μΑ       |

| Temperature sensor operating current                  | ITMPS Note 1                    |                                                                                      |                                        |                                  |                                                                             |      | 75.0       |            | μΑ       |

| LVD operating current                                 | I <sub>LVD</sub> Notes 1, 7     |                                                                                      |                                        |                                  |                                                                             |      | 0.08       |            | μΑ       |

| Comparator                                            | ICMP Notes 1, 11                | V <sub>DD</sub> = 5.0 V,                                                             | Window mode                            |                                  |                                                                             |      | 12.5       |            | μΑ       |

| operating current                                     |                                 | Regulator output                                                                     | Comparator                             | high-speed m                     | node                                                                        |      | 6.5        |            | μΑ       |

|                                                       |                                 | voltage = 2.1 V                                                                      | Comparator                             | low-speed mo                     | ode                                                                         |      | 1.7        |            | μΑ       |

|                                                       |                                 | V <sub>DD</sub> = 5.0 V,                                                             | Window mod                             | le                               |                                                                             |      | 8.0        |            | μΑ       |

|                                                       |                                 | Regulator output voltage = 1.8 V                                                     | Comparator                             |                                  | 4.0                                                                         |      | μΑ         |            |          |

|                                                       |                                 | voltage = 1.6 v                                                                      | Comparator                             | low-speed mo                     | ode                                                                         |      | 1.3        |            | μΑ       |

| Self-<br>programming<br>operating current             | IFSP Notes 1, 9                 |                                                                                      |                                        |                                  |                                                                             |      | 2.00       | 12.20      | mA       |

| BGO operating current                                 | I <sub>BGO</sub> Notes 1, 8     |                                                                                      |                                        |                                  |                                                                             |      | 2.00       | 12.20      | mA       |