Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 52                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                |                                                                         |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 68-LCC (J-Lead)                                                         |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c658-e-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

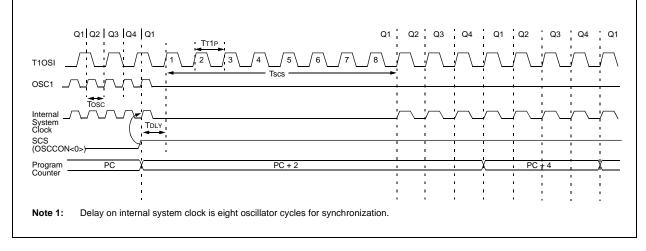

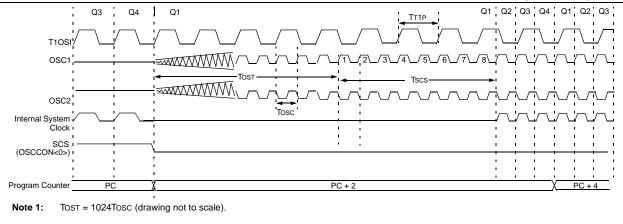

#### 2.6.2 OSCILLATOR TRANSITIONS

The PIC18CXX8 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-7. The Timer1 oscillator is assumed to be running all the time. After the SCS bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles. The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place.

If the main oscillator is configured for an external crystal (HS, XT, LP), the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes is shown in Figure 2-8.

#### FIGURE 2-7: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

#### FIGURE 2-8: TIMING DIAGRAM FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS,XT,LP)

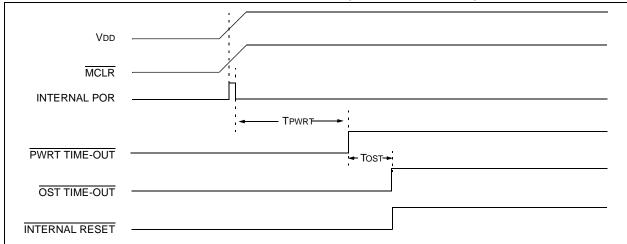

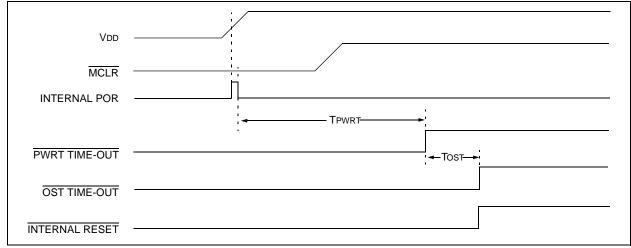

# FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

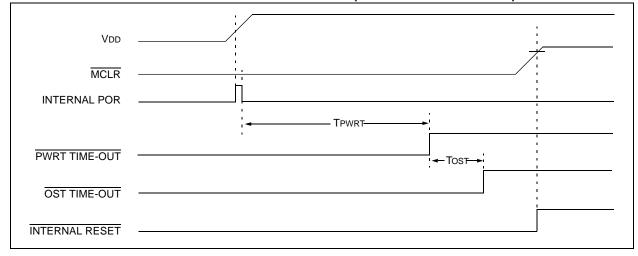

# FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

| Filename | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS <sup>(3)</sup> |

|----------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------------|------------------------------------------------|

| TXB2D7   | TXB2D77 | TXB2D76 | TXB2D75 | TXB2D74 | TXB2D73 | TXB2D72 | TXB2D71 | TXB2D70 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2D6   | TXB2D67 | TXB2D66 | TXB2D65 | TXB2D64 | TXB2D63 | TXB2D62 | TXB2D61 | TXB2D60 | XXXX XXXX               | uuuu uuuu                                      |

| TXB2D5   | TXB2D57 | TXB2D56 | TXB2D55 | TXB2D54 | TXB2D53 | TXB2D52 | TXB2D51 | TXB2D50 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2D4   | TXB2D47 | TXB2D46 | TXB2D45 | TXB2D44 | TXB2D43 | TXB2D42 | TXB2D41 | TXB2D40 | XXXX XXXX               | uuuu uuuu                                      |

| TXB2D3   | TXB2D37 | TXB2D36 | TXB2D35 | TXB2D34 | TXB2D33 | TXB2D32 | TXB2D31 | TXB2D30 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2D2   | TXB2D27 | TXB2D26 | TXB2D25 | TXB2D24 | TXB2D23 | TXB2D22 | TXB2D21 | TXB2D20 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2D1   | TXB2D17 | TXB2D16 | TXB2D15 | TXB2D14 | TXB2D13 | TXB2D12 | TXB2D11 | TXB2D10 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2D0   | TXB2D07 | TXB2D06 | TXB2D05 | TXB2D04 | TXB2D03 | TXB2D02 | TXB2D01 | TXB2D00 | xxxx xxxx               | uuuu uuuu                                      |

| TXB2DLC  | _       | TXRTR   | -       | _       | DLC3    | DLC2    | DLC1    | DLC0    | 0x00 xxxx               | 0u00 uuuu                                      |

| TXB2EIDL | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| TXB2EIDH | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx               | uuuu uuuu                                      |

| TXB2SIDL | SID2    | SID1    | SID0    |         | EXIDEN  | _       | EID17   | EID16   | xxx0 x0xx               | uuu0 u0uu                                      |

| TXB2SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

| TXB2CON  | _       | TXABT   | TXLARB  | TXERR   | TXREQ   | _       | TXPRI1  | TXPRI0  | 0000 0000               | 0000 0000                                      |

| RXM1EIDL | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| RXM1EIDH | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx               | uuuu uuuu                                      |

| RXM1SIDL | SID2    | SID1    | SID0    |         | _       | _       | EID17   | EID16   | xxxxx                   | uuuuu                                          |

| RXM1SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

| RXM0EIDL | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| RXM0EIDH | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX               | uuuu uuuu                                      |

| RXM0SIDL | SID2    | SID1    | SID0    | _       | _       | _       | EID17   | EID16   | xxxxx                   | uuuuu                                          |

| RXM0SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

| RXF5EID0 | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| RXF5EID8 | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | XXXX XXXX               | uuuu uuuu                                      |

| RXF5SIDL | SID2    | SID1    | SID0    | _       | EXIDEN  | _       | EID17   | EID16   | xxx- x-xx               | uuu- u-uu                                      |

| RXF5SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

| RXF4EID0 | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| RXF4EID8 | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx               | uuuu uuuu                                      |

| RXF4SIDL | SID2    | SID1    | SID0    | —       | EXIDEN  | —       | EID17   | EID16   | xxx- x-xx               | uuu- u-uu                                      |

| RXF4SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

| RXF3EID0 | EID7    | EID6    | EID5    | EID4    | EID3    | EID2    | EID1    | EID0    | xxxx xxxx               | uuuu uuuu                                      |

| RXF3EID8 | EID15   | EID14   | EID13   | EID12   | EID11   | EID10   | EID9    | EID8    | xxxx xxxx               | uuuu uuuu                                      |

| RXF3SIDL | SID2    | SID1    | SID0    |         | EXIDEN  |         | EID17   | EID16   | xxx- x-xx               | uuu- u-uu                                      |

| RXF3SIDH | SID10   | SID9    | SID8    | SID7    | SID6    | SID5    | SID4    | SID3    | xxxx xxxx               | uuuu uuuu                                      |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: Other (non-power-up) RESETs include external RESET through MCLR and Watchdog Timer Reset.

4: These registers are reserved on PIC18C658.

#### 5.1 **Control Registers**

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include:

- RCON register

- TABLAT register

- TBLPTR registers

#### RCON REGISTER 5.1.1

The LWRT bit specifies the operation of Table Writes to internal memory when the VPP voltage is applied to the MCLR pin. When the LWRT bit is set, the controller continues to execute user code, but long table writes are allowed (for programming internal program memory) from user mode. The LWRT bit can be cleared only by performing either a POR or MCLR Reset.

#### REGISTER 5-1: RCON REGISTER (ADDRESS: 0xFD0h)

|                | R/W-0                                                                                                                                                                                                                       | R/W-0                                         | U-0        | R/W-1        | R/W-1         | R/W-1    | R/W-0        | R/W-0   |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------|--------------|---------------|----------|--------------|---------|--|--|--|

|                | IPEN                                                                                                                                                                                                                        | LWRT                                          |            | RI           | TO            | PD       | POR          | BOR     |  |  |  |

|                | bit 7                                                                                                                                                                                                                       |                                               |            |              |               |          |              | bit 0   |  |  |  |

| bit 7<br>bit 6 | IPEN: Interrupt Priority Enable<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (16CXXX compatibility mode)<br>LWRT: Long Write Enable                                             |                                               |            |              |               |          |              |         |  |  |  |

|                |                                                                                                                                                                                                                             | TBLWT to int                                  |            |              |               |          |              |         |  |  |  |

|                | <ul> <li>Disable TBLWT to internal program memory.</li> <li>Note 1: Only cleared on a POR or MCLR reset.<br/>This bit has no effect on TBLWTs to external program memory.</li> </ul>                                        |                                               |            |              |               |          |              |         |  |  |  |

| bit 5          | Unimplem                                                                                                                                                                                                                    | ented: Read                                   | as '0'     |              |               |          |              |         |  |  |  |

| bit 4          | 1 = No res                                                                                                                                                                                                                  | Instruction Fl<br>SET instructio              | n occurred |              |               |          |              |         |  |  |  |

| bit 3          |                                                                                                                                                                                                                             | out bit<br>ower-up, CLR<br>time-out occ       |            | on, or SLEEP | o instruction |          |              |         |  |  |  |

| bit 2          |                                                                                                                                                                                                                             | -down bit<br>ower-up or by<br>cution of the s |            |              |               |          |              |         |  |  |  |

| bit 1          | <ul> <li>POR: Power-on Reset Status bit</li> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>                                   |                                               |            |              |               |          |              |         |  |  |  |

| bit 0          | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset or POR Reset occurred</li> <li>0 = A Brown-out Reset or POR Reset occurred<br/>(must be set in software after a Brown-out Reset occurs)</li> </ul> |                                               |            |              |               |          |              |         |  |  |  |

|                | Legend:                                                                                                                                                                                                                     |                                               |            |              |               |          |              |         |  |  |  |

|                | R = Reada                                                                                                                                                                                                                   | ble bit                                       | W = Wri    | table bit    | U = Unimp     | lemented | bit, read as | '0'     |  |  |  |

|                | - n = Value                                                                                                                                                                                                                 | at POR                                        | '1' = Bit  | is set       | '0' = Bit is  | cleared  | x = Bit is   | unknown |  |  |  |

#### 7.1 <u>Control Registers</u>

This section contains the control and status registers.

#### 7.1.1 INTCON REGISTERS

The INTCON Registers are readable and writable registers, which contain various enable, priority, and flag bits.

### **REGISTER 7-1:** INTCON REGISTER

| R/W-0                                                   | R/W-0                                                 | R/W-0          | R/W-0         | R/W-0          | R/W-0        | R/W-0          | R/W-x |  |  |

|---------------------------------------------------------|-------------------------------------------------------|----------------|---------------|----------------|--------------|----------------|-------|--|--|

| GIE/GIEH                                                | PEIE/GIEL                                             | TMR0IE         | <b>INTOIE</b> | RBIE           | TMR0IF       | <b>INT0IF</b>  | RBIF  |  |  |

| bit 7                                                   |                                                       |                |               |                |              |                | bi    |  |  |

| GIF/GIFH:                                               | Global Interru                                        | int Enable b   | it            |                |              |                |       |  |  |

| GIE/GIEH: Global Interrupt Enable bit<br>When IPEN = 0: |                                                       |                |               |                |              |                |       |  |  |

| 1 = Enable                                              | s all un-mask<br>s all interrupt                      |                | i             |                |              |                |       |  |  |

|                                                         | <u>l = 1:</u><br>s all high prio<br>s all high prio   |                |               |                |              |                |       |  |  |

|                                                         | : Peripheral Ir                                       | • •            |               |                |              |                |       |  |  |

| When IPEN<br>1 = Enables                                | •                                                     | ed periphera   |               |                |              |                |       |  |  |

|                                                         | <u>I = 1:</u><br>s all low priori<br>s all priority p |                |               |                |              |                |       |  |  |

| 1 = Enables                                             | MR0 Overflov<br>s the TMR0 o<br>s the TMR0 o          | verflow inter  | rupt          |                |              |                |       |  |  |

| 1 = Enables                                             | T0 External In<br>s the INT0 ex<br>s the INT0 ex      | ternal interru | ıpt           |                |              |                |       |  |  |

| 1 = Enable                                              | Port Change I<br>s the RB port<br>s the RB port       | change inte    | rrupt         |                |              |                |       |  |  |

| 1 = TMR0 r                                              | MR0 Overflov<br>register has o<br>register did no     | verflowed (m   |               | ed in softwa   | ıre)         |                |       |  |  |

| 1 = The IN                                              | Γ0 External In<br>Γ0 external in<br>Γ0 external in    | terrupt occu   | rred (must be | e cleared in   | software b   | y reading P    | ORTB) |  |  |

| 1 = At least                                            | Port Change I<br>t one of the R<br>f the RB7:RB       | B7:RB4 pins    | changed sta   |                | e cleared ir | n software)    |       |  |  |

| Legend:                                                 |                                                       |                |               |                |              |                |       |  |  |

| R = Readab                                              | ole bit                                               | W = Writ       | table bit     | U = Unimpl     | lemented b   | oit, read as ' | 0'    |  |  |

|                                                         |                                                       |                | is set        | '0' = Bit is o |              | x = Bit is u   |       |  |  |

allows software polling.

the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature

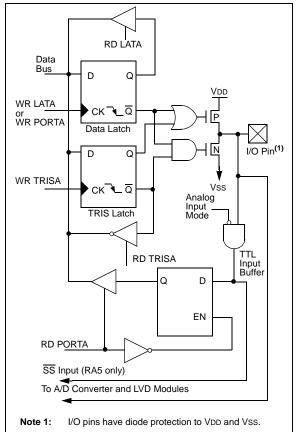

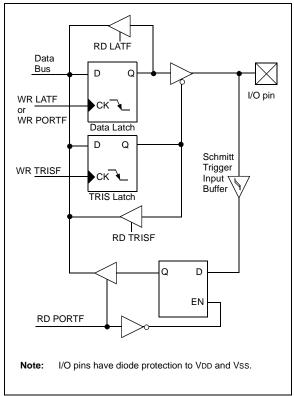

# 8.0 I/O PORTS

Depending on the device selected, there are up to eleven ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The data latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving.

### 8.1 PORTA, TRISA and LATA Registers

PORTA is a 6-bit wide, bi-directional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). On a Power-on Reset, these pins are configured as inputs and read as '0'.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

Read-modify-write operations on the LATA register, reads and writes the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1). On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 8-1: INITIALIZING PORTA

| CLRF  | PORTA  | ; Initialize PORTA by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | ; data latches                             |

|       |        | ; uata fatenes                             |

| CLRF  | LATA   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0x07   | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVLW | 0xCF   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISA  | ; Set RA3:RA0 as inputs                    |

|       |        | ; RA5:RA4 as outputs                       |

|       |        |                                            |

#### FIGURE 8-1: RA3:RA0 AND RA5 PINS BLOCK DIAGRAM

Q

D

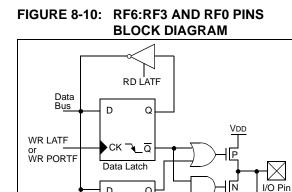

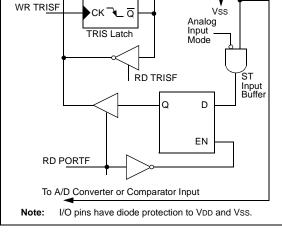

#### FIGURE 8-11: RF7 PIN BLOCK DIAGRAM

#### TABLE 8-11: PORTF FUNCTIONS

| Name               | Bit# | Buffer Type | Function                                                                                  |

|--------------------|------|-------------|-------------------------------------------------------------------------------------------|

| RF0/AN5            | bit0 | ST          | Input/output port pin or analog input.                                                    |

| RF1/AN6/C2OUT      | bit1 | ST          | Input/output port pin or analog input or comparator 2 output.                             |

| RF2/AN7/C1OUT      | bit2 | ST          | Input/output port pin or analog input or comparator 1 output.                             |

| RF3/AN8            | bit3 | ST          | Input/output port pin or analog input or comparator input.                                |

| RF4/AN9            | bit4 | ST          | Input/output port pin or analog input or comparator input.                                |

| RF5/AN10/<br>CVREF | bit5 | ST          | Input/output port pin or analog input or comparator input or comparator reference output. |

| RF6/AN11           | bit6 | ST          | Input/output port pin or analog input or comparator input.                                |

| RF7                | bit7 | ST          | Input/output port pin.                                                                    |

Legend: ST = Schmitt Trigger input

### TABLE 8-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Name   | Bit 7                                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value<br>PO<br>BC | R,   | Value on all other RESETS |

|--------|----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------|------|---------------------------|

| TRISF  | PORTF Data Direction Control Register        |       |       |       |       |       |       |       |                   | 1111 | 1111 1111                 |

| PORTF  | Read PORTF pin / Write PORTF Data Latch      |       |       |       |       |       |       |       |                   | xxxx | uuuu uuuu                 |

| LATF   | Read PORTF Data Latch/Write PORTF Data Latch |       |       |       |       |       |       |       |                   | 0000 | uuuu uuuu                 |

| ADCON1 | _                                            | _     | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 00                | 0000 | 00 0000                   |

| CMCON  | C2OUT                                        | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000              | 0000 | 0000 0000                 |

|        | = unknow                                     |       |       | CTINV | 015   | CIVI2 | CIVIT | CIVIU | 0000              | 0000 |                           |

Legend: x = unknown, u = unchanged

### 14.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### 14.2 CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

TABLE 14-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer1 or Timer3 |

| PWM      | Timer2           |

### 14.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR registers) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 14.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### 14.3.2 TIMER1/TIMER3 MODE SELECTION

The timers used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer used with each CCP module is selected in the T3CON register.

#### TABLE 14-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                                                              |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | TMR1 or TMR3 time-base. Time-base can be different for each CCP.                                                                         |

| Capture   | Compare   | The compare could be configured for the special event trigger, which clears either TMR1 or TMR3, depending upon which time-base is used. |

| Compare   | Compare   | The compare(s) could be configured for the special event trigger, which clears TMR1 or TMR3 depending upon which time-base is used.      |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                  |

| PWM       | Capture   | None                                                                                                                                     |

| PWM       | Compare   | None                                                                                                                                     |

#### 15.2 Control Registers

The MSSP module has three associated registers. These include a status register and two control registers.

### REGISTER 15-1: SSPSTAT REGISTER

Register 15-1 shows the MSSP Status Register (SSPSTAT), Register 15-2 shows the MSSP Control Register 1 (SSPCON1), and Register 15-3 shows the MSSP Control Register 2 (SSPCON2).

|       | R/W-0                                              | R/W-0                                | R-0                        | R-0           | R-0           | R-0            | R-0            | R-0          |

|-------|----------------------------------------------------|--------------------------------------|----------------------------|---------------|---------------|----------------|----------------|--------------|

|       | SMP                                                | CKE                                  | D/A                        | Р             | S             | R/W            | UA             | BF           |

|       | bit 7                                              |                                      |                            |               |               |                |                | bit 0        |

|       |                                                    |                                      |                            |               |               |                |                |              |

| bit 7 | SMP: Sam                                           | -                                    |                            |               |               |                |                |              |

|       | SPI Master                                         |                                      |                            |               |               |                |                |              |

|       | •                                                  | ata sampled ata sampled              |                            | •             |               |                |                |              |

|       | <u>SPI Slave</u>                                   |                                      |                            |               |               |                |                |              |

|       |                                                    | be cleared w                         | hen SPI is us              | sed in Slave  | mode          |                |                |              |

|       | In I <sup>2</sup> C Mas                            | ter or Slave n                       | node:                      |               |               |                |                |              |

|       |                                                    | te control dis                       |                            |               |               |                | MHz)           |              |

| h.:   |                                                    | te control ena                       | -                          | speed mode    | e (400 kHz)   |                |                |              |

| bit 6 | $\frac{CKE:SPIC}{CKP = 0}$                         | Clock Edge S                         | elect                      |               |               |                |                |              |

|       |                                                    | ansmitted on                         | rising edge of             | of SCK        |               |                |                |              |

|       | 0 = Data tr                                        | ansmitted on                         | falling edge               | of SCK        |               |                |                |              |

|       | $\frac{\text{CKP} = 1}{1 \text{ Dete } \text{tr}}$ | onomittad on                         | folling odgo               |               |               |                |                |              |

|       |                                                    | ansmitted on<br>ansmitted on         |                            |               |               |                |                |              |

| bit 5 |                                                    | Address bit (I                       |                            |               |               |                |                |              |

|       |                                                    | es that the la                       |                            | • /           | itted was d   | ata            |                |              |

|       |                                                    | es that the la                       | st byte receiv             | ed or transm  | itted was a   | ddress         |                |              |

| bit 4 | P: STOP b                                          | it<br>only. This bit                 | is closed with             | on the MSS    | D modulo in   | disabled       |                | loared )     |

|       |                                                    | es that a STC                        |                            |               |               |                |                | iealeu.)     |

|       |                                                    | bit was not de                       |                            |               |               |                | _0_1)          |              |

| bit 3 | S: START                                           |                                      |                            |               |               |                |                |              |

|       |                                                    | only. This bit                       |                            |               |               |                |                | leared.)     |

|       |                                                    | es that a STA<br>bit was not c       |                            | een detected  | last (this bi | it is '0' on F | RESET)         |              |

| bit 2 | R/W: Read                                          | /Write bit info                      | ormation (I <sup>2</sup> C | mode only)    |               |                |                |              |

|       |                                                    | ds the R/W bi                        |                            |               |               |                | his bit is onl | y valid from |

|       | -                                                  | s match to the                       | e next STAR                | T bit, STOP b | oit, or not A | CK bit.        |                |              |

|       | <u>In I<sup>2</sup>C Slav</u><br>1 = Read          | <u>e mode:</u>                       |                            |               |               |                |                |              |

|       | 0 = Write                                          |                                      |                            |               |               |                |                |              |

|       | In I <sup>2</sup> C Mas                            |                                      |                            |               |               |                |                |              |

|       |                                                    | it is in progre                      |                            |               |               |                |                |              |

|       |                                                    | it is not in pro<br>this bit with \$ |                            | PEN, RCEN     | , or ACKEN    | will indica    | te if the MS   | SP is in     |

|       | IDLE m                                             |                                      | , ,                        | ,             | ,             |                |                | -            |

| <b>TABLE 16-4</b> : | <b>BAUD RATES FOR ASYNCHRONOUS MODE (</b> | BRGH = 0) |

|---------------------|-------------------------------------------|-----------|

|                     |                                           |           |

| BAUD           | Fosc = 40 MHz |            | SPBRG              | 33 MHz 5 |            | SPBRG     | 25     | 25 MHz     |                    | 20     | MHz        | SPBRG              |

|----------------|---------------|------------|--------------------|----------|------------|-----------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD         | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | (docimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA            | -          | -                  | NA       | -          | -         | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | NA            | -          | -                  | NA       | -          | -         | NA     | -          | -                  | NA     | -          | -                  |

| 2.4            | NA            | -          | -                  | 2.40     | -0.07      | 214       | 2.40   | -0.15      | 162                | 2.40   | +0.16      | 129                |

| 9.6            | 9.62          | +0.16      | 64                 | 9.55     | -0.54      | 53        | 9.53   | -0.76      | 40                 | 9.47   | -1.36      | 32                 |

| 19.2           | 18.94         | -1.36      | 32                 | 19.10    | -0.54      | 26        | 19.53  | +1.73      | 19                 | 19.53  | +1.73      | 15                 |

| 76.8           | 78.13         | +1.73      | 7                  | 73.66    | -4.09      | 6         | 78.13  | +1.73      | 4                  | 78.13  | +1.73      | 3                  |

| 96             | 89.29         | -6.99      | 6                  | 103.13   | +7.42      | 4         | 97.66  | +1.73      | 3                  | 104.17 | +8.51      | 2                  |

| 300            | 312.50        | +4.17      | 1                  | 257.81   | -14.06     | 1         | NA     | -          | -                  | 312.50 | +4.17      | 0                  |

| 500            | 625           | +25.00     | 0                  | NA       | -          | -         | NA     | -          | -                  | NA     | -          | -                  |

| HIGH           | 625           | -          | 0                  | 515.63   | -          | 0         | 390.63 | -          | 0                  | 312.50 | -          | 0                  |

| LOW            | 2.44          | -          | 255                | 2.01     | -          | 255       | 1.53   | -          | 255                | 1.22   | -          | 255                |

| BAUD           | Fosc = | = 16 MHz   | SPBRG              | 10     | 10 MHz SPBRG 7.15909 MHz S |     | SPBRG  | 5.0688 MHz |                    | SPBRG |            |                    |

|----------------|--------|------------|--------------------|--------|----------------------------|-----|--------|------------|--------------------|-------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR                 |     | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA     | -                          | -   | NA     | -          | -                  | NA    | -          | -                  |

| 1.2            | 1.20   | +0.16      | 207                | 1.20   | +0.16                      | 129 | 1.20   | +0.23      | 92                 | 1.20  | 0          | 65                 |

| 2.4            | 2.40   | +0.16      | 103                | 2.40   | +0.16                      | 64  | 2.38   | -0.83      | 46                 | 2.40  | 0          | 32                 |

| 9.6            | 9.62   | +0.16      | 25                 | 9.77   | +1.73                      | 15  | 9.32   | -2.90      | 11                 | 9.90  | +3.13      | 7                  |

| 19.2           | 19.23  | +0.16      | 12                 | 19.53  | +1.73                      | 7   | 18.64  | -2.90      | 5                  | 19.80 | +3.13      | 3                  |

| 76.8           | 83.33  | +8.51      | 2                  | 78.13  | +1.73                      | 1   | 111.86 | +45.65     | 0                  | 79.20 | +3.13      | 0                  |

| 96             | 83.33  | -13.19     | 2                  | 78.13  | -18.62                     | 1   | NA     | -          | -                  | NA    | -          | -                  |

| 300            | 250    | -16.67     | 0                  | 156.25 | -47.92                     | 0   | NA     | -          | -                  | NA    | -          | -                  |

| 500            | NA     | -          | -                  | NA     | -                          | -   | NA     | -          | -                  | NA    | -          | -                  |

| HIGH           | 250    | -          | 0                  | 156.25 | -                          | 0   | 111.86 | -          | 0                  | 79.20 | -          | 0                  |

| LOW            | 0.98   | -          | 255                | 0.61   | -                          | 255 | 0.44   | -          | 255                | 0.31  | -          | 255                |

| BAUD           | Fosc  | = 4 MHz    | SPBRG              | 3.579545 MHz SPBRG |            | 1 MHz |       | SPBRG      | 32.768 kHz         |       | SPBRG      |                    |

|----------------|-------|------------|--------------------|--------------------|------------|-------|-------|------------|--------------------|-------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD              | %<br>ERROR |       | KBAUD | %<br>ERROR | value<br>(decimal) | KBAUD | %<br>ERROR | value<br>(decimal) |

| 0.3            | 0.30  | -0.16      | 207                | 0.30               | +0.23      | 185   | 0.30  | +0.16      | 51                 | 0.26  | -14.67     | 1                  |

| 1.2            | 1.20  | +1.67      | 51                 | 1.19               | -0.83      | 46    | 1.20  | +0.16      | 12                 | NA    | -          | -                  |

| 2.4            | 2.40  | +1.67      | 25                 | 2.43               | +1.32      | 22    | 2.23  | -6.99      | 6                  | NA    | -          | -                  |

| 9.6            | 8.93  | -6.99      | 6                  | 9.32               | -2.90      | 5     | 7.81  | -18.62     | 1                  | NA    | -          | -                  |

| 19.2           | 20.83 | +8.51      | 2                  | 18.64              | -2.90      | 2     | 15.63 | -18.62     | 0                  | NA    | -          | -                  |

| 76.8           | 62.50 | -18.62     | 0                  | 55.93              | -27.17     | 0     | NA    | -          | -                  | NA    | -          | -                  |

| 96             | NA    | -          | -                  | NA                 | -          | -     | NA    | -          | -                  | NA    | -          | -                  |

| 300            | NA    | -          | -                  | NA                 | -          | -     | NA    | -          | -                  | NA    | -          | -                  |

| 500            | NA    | -          | -                  | NA                 | -          | -     | NA    | -          | -                  | NA    | -          | -                  |

| HIGH           | 62.50 | -          | 0                  | 55.93              | -          | 0     | 15.63 | -          | 0                  | 0.51  | -          | 0                  |

| LOW            | 0.24  | -          | 255                | 0.22               | -          | 255   | 0.06  | -          | 255                | 0.002 | -          | 255                |

#### 16.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA register).

#### 16.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 16.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

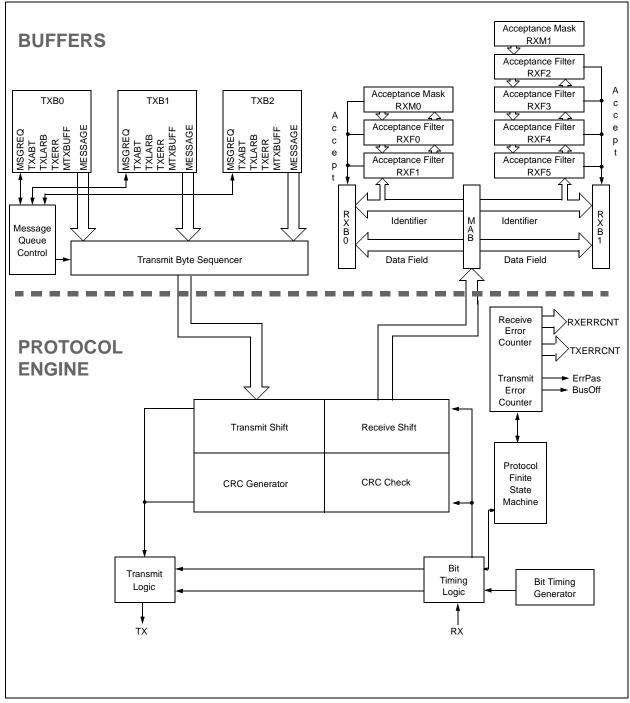

#### 17.1.2 TRANSMIT/RECEIVE BUFFERS

The PIC18CXX8 has three transmit and two receive buffers, two acceptance masks (one for each receive buffer), and a total of six acceptance filters. Figure 17-1 is a block diagram of these buffers and their connection to the protocol engine.

## FIGURE 17-1: CAN BUFFERS AND PROTOCOL ENGINE BLOCK DIAGRAM

#### 17.2.3 CAN RECEIVE BUFFER REGISTERS

This section shows the Receive Buffer registers with its associated control registers.

|         | R/C-0                                                                                                                                                                                                | R/W-0                                     | R/W-0                               | U-0                                     | R-0                                                 | R/W-0           | R-0          | R/W-0         |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------|--------------|---------------|--|--|

|         | RXFUL                                                                                                                                                                                                | R/W-0                                     | R/W-0                               | 0-0                                     | -                                                   | RXB0DBEN        | JTOFF        | FILHIT0       |  |  |

|         | bit 7                                                                                                                                                                                                |                                           | TOTINO                              |                                         |                                                     | IN DODDEN       |              | bit 0         |  |  |

| bit 7   | <b>RXFUL:</b> Receive Full Status bit<br>1 = Receive buffer contains a received message<br>0 = Receive buffer is open to receive a new message                                                       |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

|         |                                                                                                                                                                                                      | This bit is s<br>is read.                 | set by the C                        | CAN modu                                | le and should                                       | l be cleared by | software aft | er the buffer |  |  |

| bit 6-5 | 10 = Recei                                                                                                                                                                                           | ve all mess<br>ve only val<br>ve only val | ages (incluid message<br>id message | uding thos<br>es with ex<br>es with sta | e with errors)<br>tended identif<br>indard identifi | fier            |              |               |  |  |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                           |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

| bit 3   | •                                                                                                                                                                                                    |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

| bit 2   |                                                                                                                                                                                                      |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

| bit 1   | JTOFF: Ju<br>1 = Allows<br>0 = Allows                                                                                                                                                                | Jump Table                                | e offset bet                        | ween 6 ai                               |                                                     | BEN)            |              |               |  |  |

|         | Note:                                                                                                                                                                                                | This bit allo                             | ows same                            | filter jump                             | table for both                                      | n RXB0CON a     | nd RXB1CO    | N.            |  |  |

| bit 0   | <b>FILHIT0:</b> Filter Hit bit<br>This bit indicates which acceptance filter enabled the message reception into receive buffer 0<br>1 = Acceptance Filter 1 (RXF1)<br>0 = Acceptance Filter 0 (RXF0) |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

|         | Legend:                                                                                                                                                                                              |                                           |                                     |                                         |                                                     |                 |              |               |  |  |

|         | R = Reada                                                                                                                                                                                            | ble bit                                   | W = Wri                             | table bit                               | U = U                                               | nimplemented    | bit, read as | '0'           |  |  |

|         | - n = Value                                                                                                                                                                                          | at POR                                    | '1' = Bit                           | is set                                  | '0' = E                                             | Bit is cleared  | x = Bit is ι | unknown       |  |  |

#### REGISTER 17-12: RXB0CON - RECEIVE BUFFER 0 CONTROL REGISTER

x = Bit is unknown

#### 17.2.6 CAN MODULE I/O CONTROL REGISTER

This subsection describes the CAN Module I/O Control register.

#### **REGISTER 17-32: CIOCON – CAN I/O CONTROL REGISTER**

- n = Value at POR

|         | R/W-0                     | R/W-0                                                                                          | R/W-0      | R/W-0        | U-0     | U-0        | U-0          | U-0   |  |  |

|---------|---------------------------|------------------------------------------------------------------------------------------------|------------|--------------|---------|------------|--------------|-------|--|--|

|         | TX1SRC                    | TX1EN                                                                                          | ENDRHI     | CANCAP       | _       | —          | —            | _     |  |  |

|         | bit 7                     |                                                                                                |            |              |         |            |              | bit 0 |  |  |

|         |                           |                                                                                                |            |              |         |            |              |       |  |  |

| bit 7   | TX1SRC: C                 |                                                                                                |            |              |         |            |              |       |  |  |

|         |                           | . = CAN TX1 pin will output the CAN clock<br>= CAN TX1 pin will output TXD                     |            |              |         |            |              |       |  |  |

| bit 6   |                           | X1EN: CAN TX1 Pin Enable                                                                       |            |              |         |            |              |       |  |  |

|         |                           | 1 = CAN TX1 pin will output TXD or CAN clock<br>0 = CAN TX1 pin will have digital I/O function |            |              |         |            |              |       |  |  |

| bit 5   | ENDRHI: E                 |                                                                                                |            |              |         |            |              |       |  |  |

|         |                           |                                                                                                | -          | rive VDD whe |         | /e         |              |       |  |  |

| bit 4   | CANCAP:                   | CAN Messa                                                                                      | ge Receive | Capture Ena  | able    |            |              |       |  |  |

|         | 1 = Enable<br>0 = Disable |                                                                                                |            |              |         |            |              |       |  |  |

| bit 3-0 |                           | •                                                                                              |            |              |         |            |              |       |  |  |

| DII 3-0 | ommpleme                  |                                                                                                | ias U      |              |         |            |              |       |  |  |

|         | Legend:                   |                                                                                                |            |              |         |            |              |       |  |  |

|         | R = Readat                | ole bit                                                                                        | W = Writa  | ble bit      | U = Uni | mplemented | bit, read as | 0'    |  |  |

'0' = Bit is cleared

'1' = Bit is set

### 18.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2Tosc

- 4Tosc

- 8Tosc

- 16Tosc

- 32Tosc

- 64Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 18-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## 18.3 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume current out of the device's specification limits.

#### TABLE 18-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S | ource (TAD) | Maximum Device Frequency |                           |  |  |  |

|------------|-------------|--------------------------|---------------------------|--|--|--|

| Operation  | ADCS2:ADCS0 | PIC18CXX8                | PIC18LCXX8 <sup>(6)</sup> |  |  |  |

| 2Tosc      | 000         | 1.25 MHz                 | 666 kHz                   |  |  |  |

| 4Tosc      | 100         | 2.50 MHz                 | 1.33 MHz                  |  |  |  |

| 8Tosc      | 001         | 5.00 MHz                 | 2.67 MHz                  |  |  |  |

| 16Tosc     | 101         | 10.0 MHz                 | 5.33 MHz                  |  |  |  |

| 32Tosc     | 010         | 20.0 MHz                 | 10.67 MHz                 |  |  |  |

| 64Tosc     | 110         | 40.0 MHz                 | 21.33 MHz                 |  |  |  |

| RC         | x11         | _                        | —                         |  |  |  |

**Note 1:** The RC source has a typical TAD time of 4 ms.

2: The RC source has a typical TAD time of 6 ms.

- **3:** These values violate the minimum required TAD time.

- 4: For faster conversion times, the selection of another clock source is recommended.

- 5: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion or the A/D accuracy may be out of specification.

6: This column is for the LC devices only.

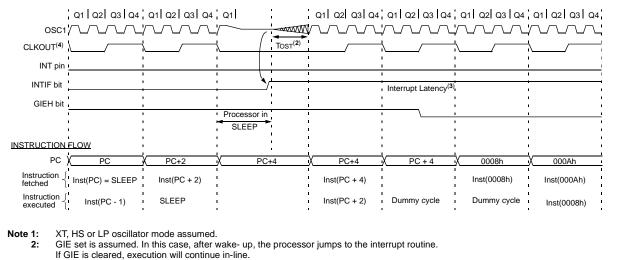

#### 22.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overrightarrow{PD}$  bit. If the  $\overrightarrow{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# FIGURE 22-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT<sup>(1,2)</sup>

3: TOST = 1024TOSC (drawing not to scale). This delay will not occur for RC and EC osc modes.

4: CLKOUT is not available in these oscillator modes, but shown here for timing reference.

| POF        | 5                                | Рор Тор                                                                                                                | Pop Top of Return Stack                                             |                                                 |                                      |                                                  |  |  |  |

|------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------|--------------------------------------|--------------------------------------------------|--|--|--|

| Synt       | tax:                             | [ label ]                                                                                                              | [label] POP                                                         |                                                 |                                      |                                                  |  |  |  |

| Ope        | rands:                           | None                                                                                                                   |                                                                     |                                                 |                                      |                                                  |  |  |  |

| Ope        | ration:                          | $({\rm TOS}) \rightarrow$                                                                                              | bit buc                                                             | ket                                             |                                      |                                                  |  |  |  |

| Stat       | us Affected:                     | None                                                                                                                   |                                                                     |                                                 |                                      |                                                  |  |  |  |

| Enco       | oding:                           | 0000                                                                                                                   | 0000 0000 0000 0110                                                 |                                                 |                                      |                                                  |  |  |  |

| Des        | cription:                        | The TOS<br>return sta<br>TOS value<br>ous value<br>return sta<br>This instru<br>enable the<br>the return<br>software s | ck and<br>e then<br>that wa<br>ck.<br>uction i<br>e user t<br>stack | is disc<br>pecom<br>as pus<br>s provi<br>o prop | card<br>les t<br>hed<br>ided<br>erly | ed. The<br>he previ-<br>onto the<br>to<br>manage |  |  |  |

| Wor        | ds:                              | 1                                                                                                                      |                                                                     |                                                 |                                      |                                                  |  |  |  |

| Cycl       | les:                             | 1                                                                                                                      |                                                                     |                                                 |                                      |                                                  |  |  |  |

| QC         | ycle Activity:                   |                                                                                                                        |                                                                     |                                                 |                                      |                                                  |  |  |  |

|            | Q1                               | Q2                                                                                                                     | C                                                                   | 3                                               |                                      | Q4                                               |  |  |  |

|            | Decode                           | No<br>operation                                                                                                        | Pop <sup>·</sup><br>val                                             |                                                 | ор                                   | No<br>peration                                   |  |  |  |

| <u>Exa</u> | mple:                            | POP<br>GOTO                                                                                                            | NEW                                                                 |                                                 |                                      |                                                  |  |  |  |

|            | Before Instru<br>TOS<br>Stack (1 | iction<br>level down)                                                                                                  | =<br>=                                                              | 0031A<br>01433                                  |                                      |                                                  |  |  |  |

|            | After Instruct<br>TOS<br>PC      | ion                                                                                                                    | =<br>=                                                              | 01433<br>NEW                                    | 2h                                   |                                                  |  |  |  |

| PUSH                                   | Push Top                                                | Push Top of Return Stack                                                                                                                                                                                                                    |                               |                |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|--|--|--|--|--|

| Syntax:                                | [ label ]                                               | PUSH                                                                                                                                                                                                                                        |                               |                |  |  |  |  |  |

| Operands:                              | None                                                    |                                                                                                                                                                                                                                             |                               |                |  |  |  |  |  |

| Operation:                             | (PC+2) $\rightarrow$                                    | $(PC+2) \rightarrow TOS$                                                                                                                                                                                                                    |                               |                |  |  |  |  |  |

| Status Affected:                       | None                                                    |                                                                                                                                                                                                                                             |                               |                |  |  |  |  |  |

| Encoding:                              | 0000                                                    | 0000                                                                                                                                                                                                                                        | 0000                          | 0101           |  |  |  |  |  |

| Description:                           | the return<br>value is pu<br>This instru<br>ing a softv | The PC+2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implement-<br>ing a software stack by modifying<br>TOS, and then push it onto the<br>return stack |                               |                |  |  |  |  |  |

| Words:                                 | 1                                                       | σκ.                                                                                                                                                                                                                                         |                               |                |  |  |  |  |  |

| Cycles:                                | 1                                                       |                                                                                                                                                                                                                                             |                               |                |  |  |  |  |  |

| Q Cycle Activity                       |                                                         |                                                                                                                                                                                                                                             |                               |                |  |  |  |  |  |