Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 52                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 1.5К х 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP                                                                  |

| Supplier Device Package    | 64-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c658-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |              | Pin N       | umber |        |             |                |                                     |

|--------------|--------------|-------------|-------|--------|-------------|----------------|-------------------------------------|

| Pin Name     | PIC1         | 8C658       | PIC1  | 8C858  | Pin<br>Type | Buffer<br>Type |                                     |

|              | TQFP         | PLCC        | TQFP  | PLCC   | турс        | iype           | Description                         |

|              |              |             |       |        |             |                | PORTG is a bi-directional I/O port  |

| RG0/CANTX1   | 3            | 12          | 5     | 16     |             |                |                                     |

| RG0          |              |             |       |        | I/O         | ST             | Digital I/O                         |

| CANTX1       |              |             |       |        | 0           | CAN Bus        | CAN bus output                      |

| RG1/CANTX2   | 4            | 13          | 6     | 17     |             |                |                                     |

| RG1          |              |             |       |        | I/O         | ST             | Digital I/O                         |

| CANTX2       |              |             |       |        | 0           | CAN Bus        | Complimentary CAN bus output        |

|              | _            |             |       |        |             |                | or CAN bus bit time clock           |

| RG2/CANRX    | 5            | 14          | 7     | 18     |             | ST             |                                     |

| RG2<br>CANRX |              |             |       |        | I/O<br>I    | CAN Bus        | Digital I/O<br>CAN bus input        |

|              | <u> </u>     | 45          |       | 10     |             | ST             | ·                                   |

| RG3          | 6            | 15          | 8     | 19     | I/O         | -              | Digital I/O                         |

| RG4          | 8            | 17          | 10    | 21     | I/O         | ST             | Digital I/O                         |

|              |              |             |       |        |             |                | PORTH is a bi-directional I/O port. |

| RH0          |              | —           | 79    | 10     | I/O         | ST             | Digital I/O                         |

| RH1          | —            | —           | 80    | 11     | I/O         | ST             | Digital I/O                         |

| RH2          | —            | —           | 1     | 12     | I/O         | ST             | Digital I/O                         |

| RH3          | —            |             | 2     | 13     | I/O         | ST             | Digital I/O                         |

| RH4/AN12     | _            | —           | 22    | 34     |             |                |                                     |

| RH4          |              |             |       |        | I/O         | ST             | Digital I/O                         |

| AN12         |              |             |       |        | I           | Analog         | Analog input 12                     |

| RH5/AN13     | —            | —           | 21    | 33     |             |                |                                     |

| RH5          |              |             |       |        | I/O         | ST             | Digital I/O                         |

| AN13         |              |             |       |        | I           | Analog         | Analog input 13                     |

| RH6/AN14     | —            |             | 20    | 32     |             | о <del>т</del> |                                     |

| RH6<br>AN14  |              |             |       |        | I/O         | ST             | Digital I/O                         |

|              |              |             |       |        | I           | Analog         | Analog input 14                     |

| RH7/AN15     | _            | —           | 19    | 31     |             | ст             |                                     |

| RH7<br>AN15  |              |             |       |        | I/O         | ST<br>Analog   | Digital I/O<br>Analog input 15      |

|              | L compatible | l<br>ninnut | 1     | 1      |             | -              | S compatible input or output        |

|              | nmitt Trigge |             |       |        |             | alog = Analog  |                                     |

|              |              | i input wi  |       | 101013 |             | alog – Analo   |                                     |

0

g = Analog input

= Output

= Open Drain (no P diode to VDD) OD

= Input = Power

I Ρ

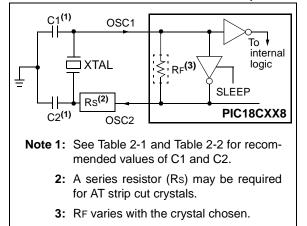

# 2.0 OSCILLATOR CONFIGURATIONS

### 2.1 Oscillator Types

The PIC18CXX8 can be operated in one of eight oscillator modes, programmable by three configuration bits (FOSC2, FOSC1, and FOSC0).

- 1. LP Low Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High Speed Crystal/Resonator

- 4. HS4 High Speed Crystal/Resonator with PLL enabled

- 5. RC External Resistor/Capacitor

- 6. RCIO External Resistor/Capacitor with I/O pin enabled

- 7. EC External Clock

- 8. ECIO External Clock with I/O pin enabled

## 2.2 <u>Crystal Oscillator/Ceramic</u> <u>Resonators</u>

In XT, LP, HS or HS4 (PLL) oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections. An external clock source may also be connected to the OSC1 pin, as shown in Figure 2-3 and Figure 2-4.

The PIC18CXX8 oscillator design requires the use of a parallel cut crystal.

| Note: | Use of a series cut crystal may give a fre- |

|-------|---------------------------------------------|

|       | quency out of the crystal manufacturer's    |

|       | specifications.                             |

# FIGURE 2-1: CRYS

#### : CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

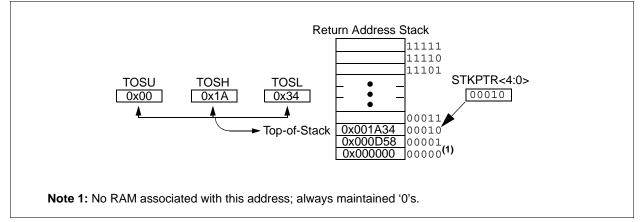

|         | R/C-0                                                                                                         | R/C-0                                           | U-0           | R/W-0     | R/W-0          | R/W-0      | R/W-0        | R/W-0   |  |  |

|---------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------|-----------|----------------|------------|--------------|---------|--|--|

|         | STKFUL                                                                                                        | STKUNF                                          | —             | SP4       | SP3            | SP2        | SP1          | SP0     |  |  |

|         | bit 7                                                                                                         |                                                 |               |           |                |            |              | bit 0   |  |  |

| bit 7   | 1 = Stack                                                                                                     | Stack Full Fla<br>became full o<br>has not beco | or overflowed | -         |                |            |              |         |  |  |

| bit 6   | <b>STKUNF</b> : Stack Underflow Flag bit<br>1 = Stack underflow occurred<br>0 = Stack underflow did not occur |                                                 |               |           |                |            |              |         |  |  |

| bit 5   | Unimplem                                                                                                      | ented: Read                                     | as '0'        |           |                |            |              |         |  |  |

| bit 4-0 | SP4:SP0: 8                                                                                                    | Stack Pointer                                   | Location bits | 5         |                |            |              |         |  |  |

|         | <b>Note:</b> Bit 7 and bit 6 can only be cleared in user software or by a POR.                                |                                                 |               |           |                |            |              |         |  |  |

|         | Legend                                                                                                        |                                                 |               |           |                |            |              |         |  |  |

|         | R = Reada                                                                                                     | able bit                                        | W = Wri       | table bit | U = Unimp      | lemented b | oit, read as | '0'     |  |  |

|         | - n = Value                                                                                                   | at POR                                          | '1' = Bit     | is set    | '0' = Bit is c | leared     | C = Cleara   | ble bit |  |  |

|         |                                                                                                               |                                                 |               |           |                |            |              |         |  |  |

# FIGURE 4-2: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

### 7.1 <u>Control Registers</u>

This section contains the control and status registers.

### 7.1.1 INTCON REGISTERS

The INTCON Registers are readable and writable registers, which contain various enable, priority, and flag bits.

### **REGISTER 7-1:** INTCON REGISTER

| R/W-0                    | R/W-0                                                 | R/W-0          | R/W-0         | R/W-0          | R/W-0        | R/W-0          | R/W-x |  |  |

|--------------------------|-------------------------------------------------------|----------------|---------------|----------------|--------------|----------------|-------|--|--|

| GIE/GIEH                 | PEIE/GIEL                                             | TMR0IE         | <b>INTOIE</b> | RBIE           | TMR0IF       | <b>INT0IF</b>  | RBIF  |  |  |

| bit 7                    |                                                       |                |               |                |              |                | bi    |  |  |

| GIF/GIFH:                | Global Interru                                        | int Enable b   | it            |                |              |                |       |  |  |

| When IPEN = 0:           |                                                       |                |               |                |              |                |       |  |  |

| 1 = Enable               | s all un-mask<br>s all interrupt                      |                | i             |                |              |                |       |  |  |

|                          | <u>l = 1:</u><br>s all high prio<br>s all high prio   |                |               |                |              |                |       |  |  |

|                          | : Peripheral Ir                                       | • •            |               |                |              |                |       |  |  |

| When IPEN<br>1 = Enables | •                                                     | ed periphera   |               |                |              |                |       |  |  |

|                          | <u>I = 1:</u><br>s all low priori<br>s all priority p |                |               |                |              |                |       |  |  |

| 1 = Enables              | MR0 Overflov<br>s the TMR0 o<br>s the TMR0 o          | verflow inter  | rupt          |                |              |                |       |  |  |

| 1 = Enables              | T0 External In<br>s the INT0 ex<br>s the INT0 ex      | ternal interru | ıpt           |                |              |                |       |  |  |

| 1 = Enable               | Port Change I<br>s the RB port<br>s the RB port       | change inte    | rrupt         |                |              |                |       |  |  |

| 1 = TMR0 r               | MR0 Overflov<br>register has o<br>register did no     | verflowed (m   |               | ed in softwa   | ıre)         |                |       |  |  |

| 1 = The IN               | Γ0 External In<br>Γ0 external in<br>Γ0 external in    | terrupt occu   | rred (must be | e cleared in   | software b   | y reading P    | ORTB) |  |  |

| 1 = At least             | Port Change I<br>t one of the R<br>f the RB7:RB       | B7:RB4 pins    | changed sta   |                | e cleared ir | n software)    |       |  |  |

| Legend:                  |                                                       |                |               |                |              |                |       |  |  |

| R = Readab               | ole bit                                               | W = Writ       | table bit     | U = Unimpl     | lemented b   | oit, read as ' | 0'    |  |  |

|                          |                                                       |                | is set        | '0' = Bit is o |              | x = Bit is u   |       |  |  |

allows software polling.

the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature

#### PIR REGISTERS (CONT'D) **REGISTER 7-5:**

| PIR2 | bit 7   | Unimplemented: Read as'0'                                                                                                                                                                                                                                                      |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | bit 6   | <b>CMIF:</b> Comparator Interrupt Flag bit<br>1 = Comparator input has changed<br>0 = Comparator input has not changed                                                                                                                                                         |

|      | bit 5-4 | Unimplemented: Read as'0'                                                                                                                                                                                                                                                      |

|      | bit 3   | <ul> <li>BCLIF: Bus Collision Interrupt Flag bit</li> <li>1 = A Bus Collision occurred<br/>(must be cleared in software)</li> <li>0 = No Bus Collision occurred</li> </ul>                                                                                                     |

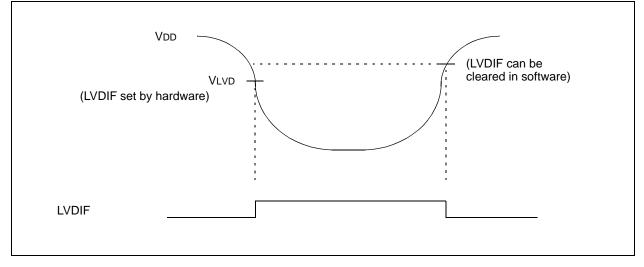

|      | bit 2   | <ul> <li>LVDIF: Low Voltage Detect Interrupt Flag bit</li> <li>1 = A low voltage condition occurred<br/>(must be cleared in software)</li> <li>0 = The device voltage is above the Low Voltage Detect trip point</li> </ul>                                                    |

|      | bit 1   | <ul> <li>TMR3IF: TMR3 Overflow Interrupt Flag bit</li> <li>1 = TMR3 register overflowed         (must be cleared in software)</li> <li>0 = TMR3 register did not overflow</li> </ul>                                                                                           |

|      | bit 0   | CCP2IF: CCPx Interrupt Flag bit<br><u>Capture Mode</u><br>1 = A TMR1 register capture occurred<br>(must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode</u><br>1 = A TMR1 register compare match occurred<br>(must be cleared in software) |

0 = No TMR1 register compare match occurred <u>PWM Mode</u>

Unused in this mode

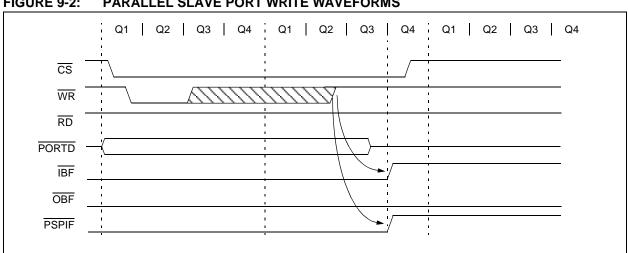

| <b>TABLE 8-7:</b> | PORTD FUNCTIONS |

|-------------------|-----------------|

|-------------------|-----------------|

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

Legend: ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port mode.

TABLE 8-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name   | Bit 7                             | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-----------------------------------|-------|-------|---------|-------|-------|-------|-------|-------------------------|---------------------------------|

| PORTD  | RD7                               | RD6   | RD5   | RD4     | RD3   | RD2   | RD1   | RD0   | xxxx xxxx               | uuuu uuuu                       |

| LATD   | LATD Data Output Register xxxx ut |       |       |         |       |       |       |       |                         | uuuu uuuu                       |

| TRISD  | SD PORTD Data Direction Register  |       |       |         |       |       |       |       | 1111 1111               | 1111 1111                       |

| PSPCON | IBF                               | OBF   | IBOV  | PSPMODE |       |       | _     |       | 0000                    | 0000                            |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

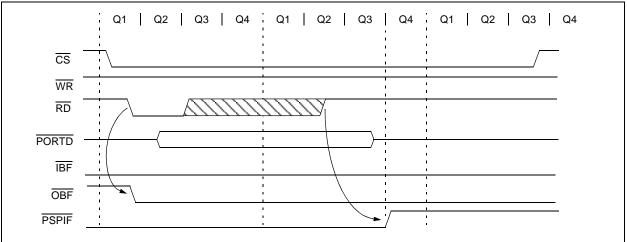

#### FIGURE 9-2: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### FIGURE 9-3: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 9-1: **REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT**

| Name   | Bit 7                     | Bit 6         | Bit 5      | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value o<br>POR, B |     | Value<br>oth<br>RES | ner  |

|--------|---------------------------|---------------|------------|--------|-------|--------|--------|--------|-------------------|-----|---------------------|------|

| PORTD  | Port data                 | latch wh      |            | XXXX X | xxx   | uuuu   | uuuu   |        |                   |     |                     |      |

| LATD   | LATD Da                   | ita Output    |            | XXXX X | xxx   | uuuu   | uuuu   |        |                   |     |                     |      |

| TRISD  | PORTD Data Direction Bits |               |            |        |       |        |        |        |                   | 111 | 1111                | 1111 |

| PORTE  | RE7                       | RE6           | RE5        | RE4    | RE3   | RE2    | RE1    | RE0    | 0000 0            | 000 | 0000                | 0000 |

| LATE   | LATE Da                   | ta Output     | Bits       |        |       |        |        |        | XXXX X            | xxx | uuuu                | uuuu |

| TRISE  | PORTE I                   | Data Dire     | ction Bits |        |       |        |        |        | 1111 1            | 111 | 1111                | 1111 |

| INTCON | GIE/<br>GIEH              | PEIE/<br>GIEL | TMR0IE     | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 0            | 00x | 0000                | 000u |

| PIR1   | PSPIF                     | ADIF          | RCIF       | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0            | 000 | 0000                | 0000 |

| PIE1   | PSPIE                     | ADIE          | RCIE       | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0            | 000 | 0000                | 0000 |

| IPR1   | PSPIP                     | ADIP          | RCIP       | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000 0            | 000 | 0000                | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

NOTES:

- **UA:** Update Address (10-bit I<sup>2</sup>C mode only) bit 1

- 1 = Indicates that the user needs to update the address in the SSPADD register

- 0 = Address does not need to be updated

- bit 0 BF: Buffer Full Status bit Receive (SPI and I<sup>2</sup>C modes)

- 1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only)

- 1 = Data Transmit in progress (does not include the ACK and STOP bits), SSPBUF is full

- 0 = Data Transmit complete (does not include the ACK and STOP bits), SSPBUF is empty

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 15-2: SSPCON1 REGISTER

|   | R/W-0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| Γ | WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

|   | bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 WCOL: Write Collision Detect bit

#### Master mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

- $0 = No \ collision$

#### Slave mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

bit 6 SSPOV: Receive Overflow Indicator bit

#### In SPI mode:

- 1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software.)

0 = No overflow

- In  $l^2C$  mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

0 = No overflow

bit 5 **SSPEN:** Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output. In SPI mode:

- 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

#### In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4 **CKP:** Clock Polarity Select bit

#### In SPI mode:

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

#### In I<sup>2</sup>C Slave mode:

- SCK release control

- 1 = Enable clock

- 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

### In I<sup>2</sup>C Master mode

Unused in this mode

#### 15.3.6 SLEEP OPERATION

In Master mode, all module clocks are halted, and the transmission/reception will remain in that state until the device wakes from SLEEP. After the device returns to normal mode, the module will continue to transmit/receive data.

In Slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in SLEEP mode, and data to be shifted into the SPI transmit/receive shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and, if enabled, will wake the device from SLEEP.

#### 15.3.7 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

#### 15.3.8 BUS MODE COMPATIBILITY

Table 15-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| TABLE 15-1: | SPI BUS MODES |

|-------------|---------------|

|-------------|---------------|

| Standard SPI Mode | Control E | Bits State |  |  |

|-------------------|-----------|------------|--|--|

| Terminology       | СКР       | CKE        |  |  |

| 0, 0              | 0         | 1          |  |  |

| 0, 1              | 0         | 0          |  |  |

| 1, 0              | 1         | 1          |  |  |

| 1, 1              | 1         | 0          |  |  |

There is also a SMP bit that controls when the data will be sampled.

| Name    | Bit 7        | Bit 6         | Bit 5                                        | Bit 4       | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value<br>PO<br>BO | R,   |      | e on<br>ther<br>ETS |

|---------|--------------|---------------|----------------------------------------------|-------------|------------|----------|--------|--------|-------------------|------|------|---------------------|

| INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE                                       | INTOIE      | RBIE       | TMR0IF   | INTOIF | RBIF   | 0000              | 000x | 0000 | 000u                |

| PIR1    | PSPIF        | ADIF          | RCIF                                         | TXIF        | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000              | 0000 | 0000 | 0000                |

| PIE1    | PSPIE        | ADIE          | RCIE                                         | TXIE        | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000              | 0000 | 0000 | 0000                |

| IPR1    | PSPIP        | ADIP          | RCIP                                         | TXIP        | SSPIP      | CCP1IP   | TMR2IP | TMR1IP | 0000              | 0000 | 0000 | 0000                |

| TRISC   | PORTC Da     | ata Direct    | tion Regist                                  | er          |            |          |        |        | 1111              | 1111 | 1111 | 1111                |

| SSPBUF  | Synchronc    | ous Serial    | Port Rece                                    | eive Buffer | r/Transmit | Register |        |        | xxxx              | xxxx | uuuu | uuuu                |

| SSPCON  | WCOL         | SSPOV         | SSPEN                                        | CKP         | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000              | 0000 | 0000 | 0000                |

| TRISA   | —            | PORTA         | PORTA Data Direction Register <sup>(1)</sup> |             |            |          |        |        |                   | 1111 | 11   | 1111                |

| SSPSTAT | SMP          | CKE           | D/A                                          | Р           | S          | R/W      | UA     | BF     | 0000              | 0000 | 0000 | 0000                |

### TABLE 15-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

Note 1: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

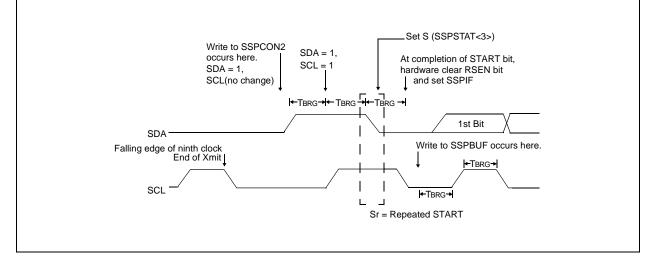

#### 15.4.7 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2 register) is programmed high and the I<sup>2</sup>C logic module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is re-loaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2 register) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT register) will be set. The SSPIF bit will not be set until the baud rate generator has timed-out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

15.4.7.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

# FIGURE 15-14: REPEAT START CONDITION WAVEFORM

#### 17.2.2 CAN TRANSMIT BUFFER REGISTERS

This section describes the CAN Transmit Buffer Register and the associated Transmit Buffer Control Registers.

| SIER 17-4. | INDICON     | I - IKANSI                                                                                                                                                                                                                                                                               |                |               |               | SIER          |           |        |  |  |  |  |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|---------------|-----------|--------|--|--|--|--|

|            | U-0         | R-0                                                                                                                                                                                                                                                                                      | R-0            | R-0           | R/W-0         | U-0           | R/W-0     | R/W-0  |  |  |  |  |

|            | _           | TXABT                                                                                                                                                                                                                                                                                    | TXLARB         | TXERR         | TXREQ         | _             | TXPRI1    | TXPRI0 |  |  |  |  |

|            | bit 7       |                                                                                                                                                                                                                                                                                          |                |               |               |               |           | bit 0  |  |  |  |  |

| bit 7      | Unimplem    | ented: Read                                                                                                                                                                                                                                                                              | as '0'         |               |               |               |           |        |  |  |  |  |

| bit 6      | 1 = Messa   | ansmission A<br>ge was abort<br>ge was not al                                                                                                                                                                                                                                            | ed             | s bit         |               |               |           |        |  |  |  |  |

| bit 5      | 1 = Messa   | Transmission<br>ge lost arbitra<br>ge did not los                                                                                                                                                                                                                                        | ation while be | eing sent     |               |               |           |        |  |  |  |  |

| bit 4      | 1 = A bus e | ransmission E<br>error occurre<br>error did not o                                                                                                                                                                                                                                        | d while the m  | essage was    | 0             | ent           |           |        |  |  |  |  |

| bit 3      | 1 = Reque   | <ul> <li>0 = A bus error did not occur while the message was being sent</li> <li>TXREQ: Transmit Request Status bit</li> <li>1 = Requests sending a message. Clears the TXABT, TLARB, and TXERR bits</li> <li>0 = Automatically cleared when the message is successfully sent</li> </ul> |                |               |               |               |           |        |  |  |  |  |

|            | Note:       | Clearing this                                                                                                                                                                                                                                                                            | bit in softwa  | re, while the | bit is set, w | ill request a | a message | abort. |  |  |  |  |

|            |             |                                                                                                                                                                                                                                                                                          |                |               |               |               |           |        |  |  |  |  |

# REGISTER 17-4: TXBnCON – TRANSMIT BUFFER n CONTROL REGISTER

| '0' |

|-----|

|     |

- bit 1-0 **TXPRI1:TXPRI0:** Transmit Priority bits

- 11 = Priority Level 3 (Highest Priority)

- 10 = Priority Level 2

- 01 = Priority Level 1

- 00 = Priority Level 0 (Lowest Priority)

**Note:** These bits set the order in which Transmit buffer will be transferred. They do not alter CAN message identifier.

| Legend:            |                  |                        |                    |

|--------------------|------------------|------------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit  | , read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x | a = Bit is unknown |

### REGISTER 17-5: TXBnSIDH: TRANSMIT BUFFER n STANDARDIDENTIFIER HIGH BYTEREGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 **SID10:SID3:** Standard Identifier bits, if EXIDE = 0 (TXBnSID Register). Extended Identifier bits EID28:EID21, if EXIDE = 1.

| Legend:            |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### 17.2.4 MESSAGE ACCEPTANCE FILTERS

bit 7-0

This subsection describes the Message Acceptance filters.

# REGISTER 17-21: RXFnSIDH – RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER HIGH BYTE

| R/W-x        | R/W-x          | R/W-x                              | R/W-x         | R/W-x    | R/W-x      | R/W-x        | R/W-x |

|--------------|----------------|------------------------------------|---------------|----------|------------|--------------|-------|

| SID10        | SID9           | SID8                               | SID7          | SID6     | SID5       | SID4         | SID3  |

| bit 7        |                |                                    |               |          |            |              | b     |

|              | <b>.</b>       |                                    |               |          |            |              |       |

|              |                | Identifier Filte<br>er bits EID28: | ,             |          |            |              |       |

| Extended Ide | entifier Filte |                                    | EID21, if EXI | DEN = 1, | lemented I | bit, read as | ·0'   |

# REGISTER 17-22: RXFnSIDL – RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER LOW BYTE

|         | R/W-x        | R/W-x                                            | R/W-x         | U-0        | R/W-x  | U-0 | R/W-x | R/W-x |

|---------|--------------|--------------------------------------------------|---------------|------------|--------|-----|-------|-------|

|         | SID2         | SID1                                             | SID0          | —          | EXIDEN | _   | EID17 | EID16 |

|         | bit 7        |                                                  |               |            |        |     |       | bit 0 |

|         |              |                                                  |               |            |        |     |       |       |

| bit 7-5 |              | : Standard Ide                                   |               | ,          | -      |     |       |       |

| bit 4   | Unimplem     | ented: Read                                      | as '0'        |            |        |     |       |       |

| bit 3   | 1 = Filter w | xtended Iden<br>ill only accep<br>ill only accep | t Extended I  | D messages |        |     |       |       |

| bit 2   | Unimplem     | ented: Read                                      | as '0'        |            |        |     |       |       |

| bit 1-0 | EID17:EID    | 16: Extended                                     | Identifier Fi | lter bits  |        |     |       |       |

|         |              |                                                  |               |            |        |     |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 17-23: RXFnEIDH – RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER HIGH BYTE

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EID15:EID8: Extended Identifier Filter bits

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

## FIGURE 25-3: LOW VOLTAGE DETECT CHARACTERISTICS

# TABLE 25-1: LOW VOLTAGE DETECT CHARACTERISTICS

|              |        |             | Standard Operating Co | nditions (u | nless other | wise state | ed)        |

|--------------|--------|-------------|-----------------------|-------------|-------------|------------|------------|

|              |        |             | Operating temperature |             | TA ≤ +85°   |            |            |

|              | I      | 1           |                       | -40°C ≤     | Ta ≤ +125   | ℃ for ext  | ended      |

| Param<br>No. | Symbol | Char        | acteristic/           | Min         | Max         | Units      | Conditions |

| D420         | Vlvd   | LVD Voltage | LVDL<3:0> = 0100      | 2.5         | ∫2.66       | V          |            |

|              |        | C C         | LVDL<3:0> = 01,01     | 12.7        | 2.86        | V          |            |

|              |        |             | LVDL<3:0> = 0110      | 2.8         | 2.98        | V          |            |

|              |        |             | LVDL<3:03=0441        | 3.0         | 3.2         | V          |            |

|              |        |             | LVPL<3:0x = 1000      | 3.3         | 3.52        | V          |            |

|              |        |             | LVDL 3:0> = 1001      | 3.5         | 3.72        | V          |            |

|              |        |             | LVDL<3:0> = 1010      | 3.6         | 3.84        | V          |            |

|              |        | $\square$   | LVDL<3:0> = 1011      | 3.8         | 4.04        | V          |            |

|              |        |             | LVDL<3:0> = 1100      | 4.0         | 4.26        | V          |            |

|              |        |             | LVDL<3:0> = 1101      | 4.2         | 4.46        | V          |            |

|              |        |             | LVDL<3:0> = 1110      | 4.5         | 4.78        | V          |            |

#### 25.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

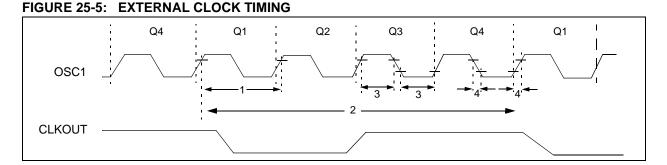

# TABLE 25-4: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param. No. | Symbol                    | Characteristic                        | Min | Max                  | Units            | Conditions    |

|------------|---------------------------|---------------------------------------|-----|----------------------|------------------|---------------|

| 1A         | Fosc                      | External CLKIN                        | DC  | 40                   | MHz              | XT osc        |

|            |                           | Frequency <sup>(1)</sup>              | DC  | 40                   | MHz              | HS osc        |

|            |                           |                                       | 4   | 10                   | MHz              | HS + PLL osc  |

|            |                           |                                       | DC  | 40                   | kHz <sub>/</sub> | LP-osq        |

|            |                           |                                       | DC  | 40                   | MHz              | EC            |

|            |                           | Oscillator Frequency <sup>(1)</sup>   | DC  | 4                    | MHz              | RC osc        |

|            |                           |                                       | 0.1 | 4                    | MHz              | XT osc        |

|            |                           |                                       | 4   | 25                   | MHz `            | HS osc        |

|            |                           |                                       | 4   | \ (10 <sup>2</sup> ) | MHz              | HS + PLL osc  |

|            |                           |                                       | 5   | \ <u>\</u> 200 ~     | kHz              | LP osc mode   |

| 1          | Tosc                      | External CLKIN Period <sup>(1)</sup>  | 250 | $\sqrt{-}$           | ns               | XT and RC osc |

|            |                           |                                       | 40  | _                    | ns               | HS osc        |

|            |                           |                                       | 100 | —                    | ns               | HS + PLL osc  |

|            |                           |                                       | 5 5 | —                    | μs               | LP osc        |

|            |                           |                                       | 5   | _                    | ns               | EC            |

|            |                           | Oscillator Period <sup>(1)</sup>      | 250 | —                    | ns               | RC osc        |

|            | $\langle$                 | $\nabla$                              | 250 | 10,000               | ns               | XT osc        |

|            | Ň                         |                                       | 100 | 10,000               | ns               | HS osc        |

| ``         | $\langle \rangle \rangle$ | $\searrow$                            | 40  | 100                  | ns               | HS + PLL osc  |

|            | $\backslash \langle$      |                                       | 5   | —                    | μs               | LP osc        |

| 2          | TCY                       | Instruction Cycle Time <sup>(1)</sup> | 100 | _                    | ns               | TCY = 4/FOSC  |

| 3          | TosL,                     | External Clock in (OSC1)              | 30  | —                    | ns               | XT osc        |

|            | TosH                      | High or Low Time                      | 2.5 | —                    | ns               | LP osc        |

|            |                           |                                       | 10  | _                    | μs               | HS osc        |

| 4          | TosR,                     | External Clock in (OSC1)              | —   | 20                   | ns               | XT osc        |

|            | TosF                      | Rise or Fall Time                     | —   | 50                   | ns               | LP osc        |

|            |                           |                                       |     | 7.5                  | ns               | HS osc        |

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

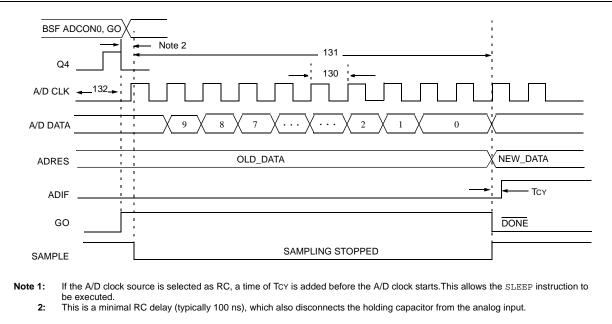

## FIGURE 25-22: A/D CONVERSION TIMING

| TABLE 25-22: | A/D CONVERSION REQUIREMENTS |

|--------------|-----------------------------|

|--------------|-----------------------------|

| Param<br>No. | Sym-<br>bol | Characteristic                                                     | Min              | Max      | Units             | Conditions |                                                                                                                                                                        |

|--------------|-------------|--------------------------------------------------------------------|------------------|----------|-------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD         | A/D clock period PIC18 <b>C</b> XX8                                | 5                | 1.6      | 20 <sup>(5)</sup> | μs         | Tosc based, VREF $\geq$ 3.0V                                                                                                                                           |

|              |             | PIC18LCXX                                                          | (8               | 3.0      | 20(5)             | pt\$       | Tosc based, VREF full range                                                                                                                                            |

|              |             | PIC18CXX8                                                          |                  | 2.0      | 6.0               | Jμs        | A/D RC mode                                                                                                                                                            |

|              |             | PIC18LCXX                                                          | (8               | 3.0      | 9.0               | μs         | A/D RC mode                                                                                                                                                            |

| 131          | TCNV        | Conversion time<br>(not including acquisition time) <sup>(1)</sup> | $\overline{(n)}$ | AN I     | <u>j</u> 12       | TAD        |                                                                                                                                                                        |

| 132          | TACQ        | Acquisition time <sup>(3)</sup>                                    | 77               | 15<br>10 |                   | μs<br>μs   | $\begin{array}{l} -40^{\circ}\text{C} \leq \text{Temp} \leq 125^{\circ}\text{C} \\ 0^{\circ}\text{C} \leq \text{Temp} \leq 125^{\circ}\text{C} \end{array}$            |

| 135          | Tswc        | Switching time from convert - sampl                                | le               | _        | (Note 4)          |            |                                                                                                                                                                        |

| 136          | Тамр        | Amplifier settling time (Note 2)                                   |                  | 1        |                   | μs         | This may be used if the<br>"new" input voltage has not<br>changed by more than 1 LSb<br>(i.e., 5 mV @ 5.12V) from<br>the last sampled voltage (as<br>stated on CHOLD). |

Note 1: ADRES register may be read on the following TCY cycle.

- 2: See Section 18.0 for minimum conditions, when input voltage has changed more than 1 LSb.

- **3:** The time for the holding capacitor to acquire the "New" input voltage, when the voltage changes full scale after the conversion (AVDD to AVss, or AVss to AVDD). The source impedance (*Rs*) on the input channels is 50 Ω.

- **4:** On the next Q4 cycle of the device clock.

- 5: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

## Package Marking Information (Cont'd)

## 84-Lead PLCC

Example

# **PIC18CXX8 PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery refer to the factory or the listed sales office

| PART NO.<br>Device | X /XX XXX<br>     <br>Temperature Package Pattern<br>Range                                                                                                             | <ul> <li>Examples:</li> <li>a) PIC18LC658 - I/L 301 = Industrial temp., PLCC package, Extended VDD limits, QTP pattern #301.</li> <li>b) PIC18LC858 - I/PT = Industrial temp., TQFP</li> </ul>                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device             | PIC18CXX8 <sup>(1)</sup> , PIC18CXX8T <sup>(2)</sup> ;<br>VDD range 4.2V to 5.5V<br>PIC18LCXX5 <sup>(1)</sup> , PIC18LCXX8T <sup>(2)</sup> ;<br>VDD range 2.5V to 5.5V | <ul> <li>package, Extended VDD limits.</li> <li>c) PIC18C658 - E/L = Extended temp., PLCC package, normal VDD limits.</li> </ul>                                                                                                                         |

| Temperature Range  | $ \begin{array}{rcl} I &=& -40^\circ C \text{ to } +85^\circ C & (Industrial) \\ E &=& -40^\circ C \text{ to } +125^\circ C & (Extended) \end{array} $                 |                                                                                                                                                                                                                                                          |

| Package            | CL = Windowed JCERPACK<br>PT = TQFP (Thin Quad Flatpack)<br>L = PLCC                                                                                                   | <ul> <li>Note 1: C = Standard Voltage Range<br/>LC = Wide Voltage Range</li> <li>2: T = in tape and reel PLCC, and TQFP<br/>packages only.</li> <li>3: CL devices are UV erasable and can be pro-<br/>grammed to any device configuration. CL</li> </ul> |

| Pattern            | QTP, SQTP, Code or Special Requirements<br>(blank otherwise)                                                                                                           | devices meet the electrical requirement of<br>each oscillator type (including LC devices).                                                                                                                                                               |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.