Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                              |

| Number of I/O              | 68                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 84-LCC (J-Lead)                                                         |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c858-e-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

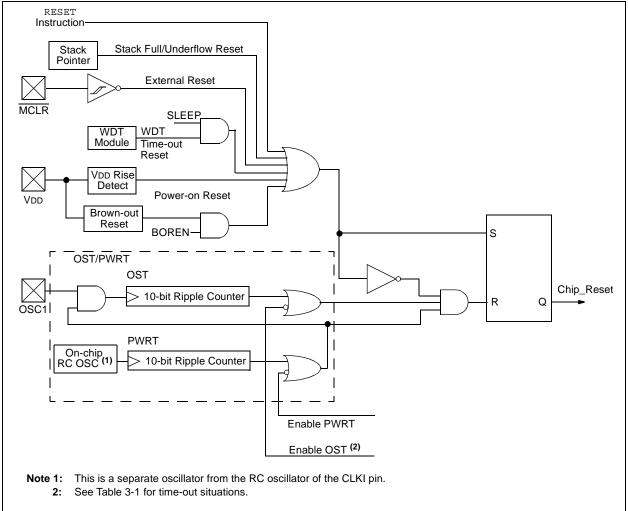

### 3.0 RESET

The PIC18CXX8 differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (PBOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETs. The other registers are forced to a "RESET" state on Power-on Reset, MCLR, WDT Reset, Brown-out Reset, MCLR Reset during SLEEP and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 3-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

A WDT Reset does not drive MCLR pin low.

### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Filename             | Bit 7          | Bit 6                | Bit 5          | Bit 4           | Bit 3           | Bit 2       | Bit 1      | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS <sup>(3)</sup> |

|----------------------|----------------|----------------------|----------------|-----------------|-----------------|-------------|------------|---------|-------------------------|------------------------------------------------|

| LATJ <sup>(4)</sup>  | Read PORTJ     | Data Latch, W        | rite PORTJ Dat | a Latch         |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATH <sup>(4)</sup>  | Read PORTH     | Data Latch, W        | /rite PORTH Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATG                 | _              | _                    |                | Read PORTO      | B Data Latch,   | Write PORTG | Data Latch |         | x xxxx                  | u uuuu                                         |

| LATF                 | Read PORTF     | Data Latch, W        | /rite PORTF Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATE                 | Read PORTE     | Data Latch, W        | /rite PORTE Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATD                 | Read PORTD     | Data Latch, W        | /rite PORTD Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATC                 | Read PORTC     | Data Latch, W        | /rite PORTC Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATB                 | Read PORTB     | Data Latch, W        | /rite PORTB Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATA                 | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | Data Latch, Wr  | ite PORTA Da    | ata Latch   |            |         | xx xxxx                 | uu uuuu                                        |

| PORTJ <sup>(4)</sup> | Read PORTJ     | pins, Write PC       | RTJ Data Latch | ı               |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTH <sup>(4)</sup> | Read PORTH     | l pins, Write PO     | ORTH Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTG                | _              | _                    |                | Read PORTO      | 6 pins, Write F | ORTG Data L | .atch      |         | x xxxx                  | uuuu uuuu                                      |

| PORTF                | Read PORTF     | pins, Write PC       | ORTF Data Latc | h               |                 |             |            |         | 0000 0000               | 0000 0000                                      |

| PORTE                | Read PORTE     | pins, Write PC       | ORTE Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTD                | Read PORTD     | pins, Write PC       | ORTD Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTC                | Read PORTC     | pins, Write PO       | ORTC Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTB                | Read PORTB     | pins, Write PC       | ORTB Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTA                | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | pins, Write POI | RTA Data Late   | ch          |            |         | 0x 0000                 | 0u 0000                                        |

| TRISK <sup>(4)</sup> | Data Directior | n Control Regis      | ster for PORTK |                 |                 |             |            |         | 1111 1111               | 1111 1111                                      |

| LATK <sup>(4)</sup>  | Read PORTK     | Data Latch, W        | /rite PORTK Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTK <sup>(4)</sup> | Read PORTK     | pins, Write PC       | ORTK Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| TXERRCNT             | TEC7           | TEC6                 | TEC5           | TEC4            | TEC3            | TEC2        | TEC1       | TEC0    | 0000 0000               | 0000 0000                                      |

| RXERRCNT             | REC7           | REC6                 | REC5           | REC4            | REC3            | REC2        | REC1       | REC0    | 0000 0000               | 0000 0000                                      |

| COMSTAT              | RXB00VFL       | RXB10VFL             | TXBO           | TXBP            | RXBP            | TXWARN      | RXWARN     | EWARN   | 0000 0000               | 0000 0000                                      |

| CIOCON               | TX1SRC         | TX1EN                | ENDRHI         | CANCAP          | —               | —           | —          | —       | 1000                    | 1000                                           |

| BRGCON3              | —              | WAKFIL               | —              | —               | —               | SEG2PH2     | SEG2PH1    | SEG2PH0 | -0000                   | -0000                                          |

| BRGCON2              | SEG2PHTS       | SAM                  | SEG1PH2        | SEG1PH1         | SEG1PH0         | PRSEG2      | PRSEG1     | PRSEG0  | 0000 0000               | 0000 0000                                      |

| BRGCON1              | SJW1           | SJW0                 | BRP5           | BRP4            | BRP3            | BRP2        | BRP1       | BRP0    | 0000 0000               | 0000 0000                                      |

| CANCON               | REQOP2         | REQOP1               | REQOP0         | ABAT            | WIN2            | WIN1        | WIN0       | _       | xxxx xxx-               | uuuu uuu-                                      |

| CANSTAT              | OPMODE2        | OPMODE1              | OPMODE0        | —               | ICODE2          | ICODE1      | ICOED0     | _       | xxx- xxx-               | uuu- uuu-                                      |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: Other (non-power-up) RESETs include external RESET through MCLR and Watchdog Timer Reset.

4: These registers are reserved on PIC18C658.

### 4.12 Indirect Addressing, INDF and FSR Registers

Indirect addressing is a mode of addressing data memory, where the data memory address in the instruction is not fixed. A SFR register is used as a pointer to the data memory location that is to be read or written. Since this pointer is in RAM, the contents can be modified by the program. This can be useful for data tables in the data memory and for software stacks. Figure 4-6 shows the operation of indirect addressing. This shows the moving of the value to the data memory address specified by the value of the FSR register.

Indirect addressing is possible by using one of the INDF registers. Any instruction using the INDF register actually accesses the register indicated by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation. The FSR register contains a 12-bit address, which is shown in Figure 4-6.

The INDFn ( $0 \le n \le 2$ ) register is not a physical register. Addressing INDFn actually addresses the register whose address is contained in the FSRn register (FSRn is a pointer). This is indirect addressing.

Example 4-4 shows a simple use of indirect addressing to clear the RAM in Bank 1 (locations 100h-1FFh) in a minimum number of instructions.

### EXAMPLE 4-4: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|      | LFSR  | FSR0, 0x100 | ; |                |

|------|-------|-------------|---|----------------|

| NEXT | CLRF  | POSTINC0    | ; | Clear INDF     |

|      |       |             | ; | register       |

|      |       |             | ; | & inc pointer  |

|      | BTFSS | FSROH, 1    | ; | All done       |

|      |       |             | ; | w/ Bank1?      |

|      | GOTO  | NEXT        | ; | NO, clear next |

| CONT | INUE  |             | ; |                |

|      | :     |             | ; | YES, continue  |

|      |       |             |   |                |

There are three indirect addressing registers. To address the entire data memory space (4096 bytes), these registers are 12-bit wide. To store the 12-bits of addressing information, two 8-bit registers are required. These indirect addressing registers are:

- 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

In addition, there are registers INDF0, INDF1 and INDF2, which are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data.

If an instruction writes a value to INDF0, the value will be written to the address indicated by FSR0H:FSR0L. A read from INDF1 reads the data from the address indicated by FSR1H:FSR1L. INDFn can be used in code anywhere an operand can be used.

If INDF0, INDF1 or INDF2 are read indirectly via an FSR, all '0's are read (zero bit is set). Similarly, if INDF0, INDF1 or INDF2 are written to indirectly, the operation will be equivalent to a NOP instruction and the STATUS bits are not affected.

### 4.12.1 INDIRECT ADDRESSING OPERATION

Each FSR register has an INDF register associated with it, plus four additional register addresses. Performing an operation on one of these five registers determines how the FSR will be modified during indirect addressing.

When data access is done to one of the five INDFn locations, the address selected will configure the FSRn register to:

- Do nothing to FSRn after an indirect access (no change) INDFn

- Auto-decrement FSRn after an indirect access (post-decrement) POSTDECn

- Auto-increment FSRn after an indirect access (post-increment) POSTINCn

- Auto-increment FSRn before an indirect access (pre-increment) PREINCn

- Use the value in the WREG register as an offset to FSRn. Do not modify the value of the WREG or the FSRn register after an indirect access (no change) - PLUSWn

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the STATUS register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

Incrementing or decrementing an FSR affects all 12 bits. That is, when FSRnL overflows from an increment, FSRnH will be incremented automatically.

Adding these features allows the FSRn to be used as a software stack pointer in addition to its uses for table operations in data memory.

Each FSR has an address associated with it that performs an indexed indirect access. When a data access to this INDFn location (PLUSWn) occurs, the FSRn is configured to add the 2's complement value in the WREG register and the value in FSR to form the address before an indirect access. The FSR value is not changed.

If an FSR register contains a value that indicates one of the INDFn, an indirect read will read 00h (zero bit is set), while an indirect write will be equivalent to a NOP (STATUS bits are not affected).

If an indirect addressing operation is done where the target address is an FSRnH or FSRnL register, the write operation will dominate over the pre- or post-increment/decrement functions.

### 5.2 Program Memory Read/Writes

### 5.2.1 TABLE READ OVERVIEW (TBLRD)

The TBLRD instructions are used to read data from program memory to data memory.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next Table Read operation.

Table Reads from program memory are performed one byte at a time. The instruction will load TABLAT with the one byte from program memory pointed to by TBLPTR.

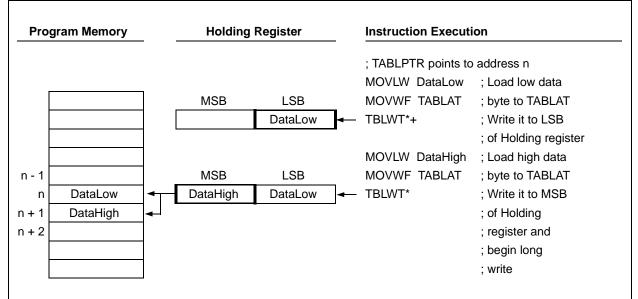

#### 5.2.2 PROGRAM MEMORY WRITE BLOCK SIZE

The program memory of PIC18CXX8 devices is written in blocks. For PIC18CXX8 devices, the write block size is 2 bytes. Consequently, Table Write operations to program memory are performed in pairs, one byte at a time. When a Table Write occurs to an even program memory address (TBLPTR<0> = 0), the contents of TABLAT are transferred to an internal holding register. This is performed as a short write and the program memory block is not actually programmed at this time. The holding register is not accessible by the user.

When a Table Write occurs to an odd program memory address (TBLPTR<0> = 1), a long write is started. During the long write, the contents of TABLAT are written to the high byte of the program memory block and the contents of the holding register are transferred to the low byte of the program memory block.

Figure 5-3 shows the holding register and the program memory write blocks.

If a single byte is to be programmed, the low (even) byte of the destination program word should be read using TBLRD\*, modified or changed, if required, and written back to the same address using TBLWT\*+. The high (odd) byte should be read using TBLRD\*, modified or changed if required, and written back to the same address using TBLWT. The write to an odd address will cause a long write to begin. This process ensures that existing data in either byte will not be changed unless desired.

### FIGURE 5-3: HOLDING REGISTER AND THE WRITE

#### EXAMPLE 5-1: TABLE READ CODE EXAMPLE

| ; Read | a byte from | locati | on 0x0020             |

|--------|-------------|--------|-----------------------|

| CLRF   | TBLPTRU     | ;      | Load upper 5 bits of  |

|        |             | ;      | 0x0020                |

| CLRF   | TBLPTRH     | ;      | Load higher 8 bits of |

|        |             | ;      | 0x0020                |

| MOVLW  | 0x20        | ;      | Load 0x20 into        |

| MOVWF  | TBLPTRL     | ;      | TBLPTRL               |

| MOVWF  | TBLRD*      | ;      | Data is in TABLAT     |

|        |             |        |                       |

### REGISTER 7-7: IPR REGISTERS (CONT'D)

| IPR2 | bit 7   | Unimplemented: Read as '0'                                   |                                         |                      |                    |

|------|---------|--------------------------------------------------------------|-----------------------------------------|----------------------|--------------------|

|      | bit 6   | CMIP: Comparator Interrupt P                                 | riority bit                             |                      |                    |

|      |         | 1 = High priority                                            |                                         |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 5-4 | Unimplemented: Read as '0'                                   |                                         |                      |                    |

|      | bit 3   | <b>BCLIP</b> : Bus Collision Interrupt<br>1 = High priority  | Priority bit                            |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 2   | LVDIP: Low Voltage Detect Int                                | errupt Priority bit                     |                      |                    |

|      |         | 1 = High priority                                            |                                         |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 1   | TMR3IP: TMR3 Overflow Inter                                  | rupt Priority bit                       |                      |                    |

|      |         | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |                                         |                      |                    |

|      | bit 0   | CCP2IP: CCP2 Interrupt Priori                                | ty bit                                  |                      |                    |

|      | Dit 0   | 1 = High priority                                            |                                         |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

| IPR3 | bit 7   | IVRP: Invalid Message Receiv                                 | ed Interrupt Priority                   | <i>i</i> bit         |                    |

|      |         | 1 = High priority                                            |                                         |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 6   | WAKIP: Bus Activity Wake-up                                  | Interrupt Priority bi                   | t                    |                    |

|      |         | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |                                         |                      |                    |

|      | bit 5   | ERRIP: CAN Bus Error Interru                                 | pt Priority bit                         |                      |                    |

|      |         | 1 = High priority                                            | , , , , , , , , , , , , , , , , , , , , |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 4   | TXB2IP: Transmit Buffer 2 Inte                               | errupt Priority bit                     |                      |                    |

|      |         | <ul><li>1 = High priority</li><li>0 = Low priority</li></ul> |                                         |                      |                    |

|      | bit 3   | <b>TXB1IP:</b> Transmit Buffer 1 Inte                        | errunt Priority hit                     |                      |                    |

|      | bit 0   | 1 = High priority                                            | indper noncy bie                        |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 2   | TXB0IP: Transmit Buffer 0 Inte                               | errupt Priority bit                     |                      |                    |

|      |         | 1 = High priority                                            |                                         |                      |                    |

|      | bit 1   | 0 = Low priority                                             | reunt Driarity hit                      |                      |                    |

|      | bit 1   | <b>RXB1IP:</b> Receive Buffer 1 Inte<br>1 = High priority    | frupt Phonty bit                        |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      | bit 0   | RXB0IP: Receive Buffer 0 Inte                                | rrupt Priority bit                      |                      |                    |

|      |         | 1 = High priority                                            |                                         |                      |                    |

|      |         | 0 = Low priority                                             |                                         |                      |                    |

|      |         | Legend:                                                      |                                         |                      |                    |

|      |         | R = Readable bit W                                           | = Writable bit                          | U = Unimplemented    | bit, read as '0'   |

|      |         | - n = Value at POR '1                                        | = Bit is set                            | '0' = Bit is cleared | x = Bit is unknown |

### 7.1.6 INT INTERRUPTS

External interrupts on the RB0/INT0, RB1/INT1, RB2/INT2, and RB3/INT3 pins are edge triggered: either rising if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxIF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxIE. Flag bit INTxIF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1, INT2, and INT3) can wake-up the processor from SLEEP, if bit INTxIE was set prior to going into SLEEP. If the global interrupt vector following wake-up.

Interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the interrupt priority bits INT1IP (INTCON3 register), INT3IP (INTCON3 register), and INT2IP (INTCON2 register). There is no priority bit associated with INT0; it is always a high priority interrupt source.

### 7.1.7 TMR0 INTERRUPT

In 8-bit mode (which is the default), an overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (FFFh  $\rightarrow$  0000h) in the

TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON register). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2 register). See Section 10.0 for further details on the Timer0 module.

### 7.1.8 PORTB INTERRUPT-ON-CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON register). The interrupt can be enabled/ disabled by setting/clearing enable bit RBIE (INTCON register). Interrupt priority for PORTB interrupton-change is determined by the value contained in the interrupt priority bit RBIP (INTCON2 register).

### 7.2 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 7-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF<br>MOVFF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP | ; W_TEMP is in Low Access bank<br>; STATUS_TEMP located anywhere<br>; BSR located anywhere |

|-------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

| ;<br>; USER<br>;        | ISR CODE                                       |                                                                                            |

| MOVFF                   | BSR_TEMP, BSR                                  | ; Restore BSR                                                                              |

| MOVF                    | W_TEMP, W                                      | ; Restore WREG                                                                             |

| MOVFF                   | STATUS_TEMP, STATUS                            | ; Restore STATUS                                                                           |

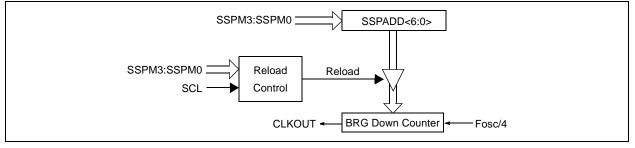

### 15.4.5 BAUD RATE GENERATOR

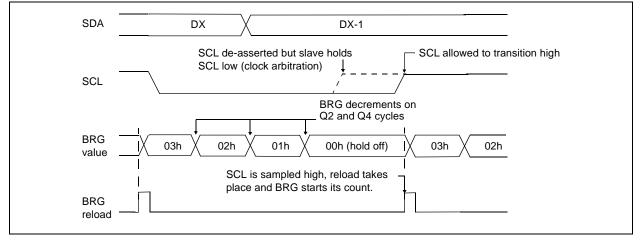

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 15-11). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is dec-

remented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In  $I^2C$  Master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place, for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 15-12).

### FIGURE 15-11: BAUD RATE GENERATOR BLOCK DIAGRAM

### FIGURE 15-12: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

| REGISTER 17-9: | TXBnDm ·    | - TRANSM      | IT BUFFE       | R n DATA I                       | FIELD BY1    | E m REG     | ISTER        |         |

|----------------|-------------|---------------|----------------|----------------------------------|--------------|-------------|--------------|---------|

|                | R/W-x       | R/W-x         | R/W-x          | R/W-x                            | R/W-x        | R/W-x       | R/W-x        | R/W-x   |

|                | TXBnDm7     | TXBnDm6       | TXBnDm5        | TXBnDm4                          | TXBnDm3      | TXBnDm2     | TXBnDm1      | TXBnDm0 |

|                | bit 7       |               |                |                                  |              |             |              | bit 0   |

| bit 1-0        |             | mit Buffer ha |                | ıffer n Data F<br>f registers. F | •            | •           |              |         |

|                | Legend:     |               |                |                                  |              |             |              |         |

|                | R = Reada   | ole bit       | W = Writab     | ole bit                          | U = Unim     | plemented b | oit, read as | ʻ0'     |

|                | - n = Value | at POR        | '1' = Bit is s | set                              | '0' = Bit is | cleared     | x = Bit is u | nknown  |

|                |             |               |                |                                  |              |             |              |         |

## REGISTER 17-10: TXBnDLC – TRANSMIT BUFFER n DATA LENGTH CODE REGISTER

|         |                   |                                  | -             |              |            | -     |       |       |

|---------|-------------------|----------------------------------|---------------|--------------|------------|-------|-------|-------|

|         | U-0               | R/W-x                            | U-0           | U-0          | R/W-x      | R/W-x | R/W-x | R/W-x |

|         | —                 | TXRTR                            | -             | _            | DLC3       | DLC2  | DLC1  | DLC0  |

|         | bit 7             |                                  |               |              |            |       |       | bit 0 |

|         |                   |                                  |               |              |            |       |       |       |

| bit 7   | Unimplem          | ented: Read                      | as '0'        |              |            |       |       |       |

| bit 6   | TXRTR: T          | ransmission F                    | rame Remot    | e Transmiss  | ion Reques | t bit |       |       |

|         | 1 = Transn        | nitted messag                    | e will have T | XRTR bit se  | t          |       |       |       |

|         | 0 = Transn        | nitted messag                    | e will have T | XRTR bit cle | eared.     |       |       |       |

| bit 5-4 | Unimplem          | nented: Read                     | as '0'        |              |            |       |       |       |

| bit 3-0 | DLC3:DLC          | <b>:</b> Data Leng               | th Code bits  |              |            |       |       |       |

|         | 1111 <b>= R</b> e | eserved                          |               |              |            |       |       |       |

|         | 1110 <b>= Re</b>  | eserved                          |               |              |            |       |       |       |

|         | 1101 <b>= R</b> e |                                  |               |              |            |       |       |       |

|         | 1100 <b>= Re</b>  |                                  |               |              |            |       |       |       |

|         | 1011 <b>= Re</b>  |                                  |               |              |            |       |       |       |

|         | 1010 = Re         |                                  |               |              |            |       |       |       |

|         | 1001 = Re         |                                  |               |              |            |       |       |       |

|         |                   | ta Length = 8                    |               |              |            |       |       |       |

|         |                   | ata Length = 7<br>ata Length = 6 | -             |              |            |       |       |       |

|         |                   | ata Length = $5$                 | •             |              |            |       |       |       |

|         |                   | ata Length = $4$                 |               |              |            |       |       |       |

|         |                   | ata Length = 3                   |               |              |            |       |       |       |

|         |                   | ata Length = 2                   | -             |              |            |       |       |       |

|         |                   | Ų                                |               |              |            |       |       |       |

|         | 0001 = Da         | ata Length = 1                   | DVIES         |              |            |       |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Instruction Set 23.1

| ADD        | DLW            | ADD liter           | al to W                                                                                   |     |    |          |

|------------|----------------|---------------------|-------------------------------------------------------------------------------------------|-----|----|----------|

| Synt       | ax:            | [label] A           | DDLW                                                                                      | k   |    |          |

| Ope        | rands:         | $0 \le k \le 25$    | 5                                                                                         |     |    |          |

| Ope        | ration:        | (WREG) -            | (WREG) + k $\rightarrow$ WREG                                                             |     |    |          |

| State      | us Affected:   | N,OV, C,            | DC, Z                                                                                     |     |    |          |

| Enco       | oding:         | 0000                | 1111                                                                                      | kkk | k  | kkkk     |

| Des        | cription:      | to the 8-bi         | The contents of WREG are added to the 8-bit literal 'k' and the result is placed in WREG. |     |    |          |

| Wor        | ds:            | 1                   |                                                                                           |     |    |          |

| Cycl       | es:            | 1                   |                                                                                           |     |    |          |

| QC         | ycle Activity: |                     |                                                                                           |     |    |          |

|            | Q1             | Q2                  | Q3                                                                                        |     |    | Q4       |

|            | Decode         | Read<br>literal 'k' | Proce<br>Data                                                                             |     | Wr | ite to W |

| <u>Exa</u> | mple:          |                     | 0x15                                                                                      |     |    |          |

|            | Before Instru  |                     |                                                                                           |     |    |          |

|            | WREG<br>N      | = 0x10<br>= ?       |                                                                                           |     |    |          |

|            | OV             | = ?                 |                                                                                           |     |    |          |

|            | C              | = ?                 |                                                                                           |     |    |          |

|            | DC             | = ?                 |                                                                                           |     |    |          |

|            | Z              | = ?                 |                                                                                           |     |    |          |

= 0

= 0

= 0

= 0

0x25

0 =

Ν

С

Ζ

OV

DC

After Instruction WREG =

| ADDWF                                                                                               | ADD W to                                                                               | o f                                                 |                                                               |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| Syntax:                                                                                             | [ label ] A                                                                            | DDWF f[,                                            | d] [,a]                                                       |

| Operands:                                                                                           | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                   | 5                                                   |                                                               |

| Operation:                                                                                          |                                                                                        | + (f) $\rightarrow$ dest                            |                                                               |

| Status Affected:                                                                                    | N,OV, C,                                                                               | DC, Z                                               |                                                               |

| Encoding:                                                                                           | 0010                                                                                   | 01da ff                                             | ff ffff                                                       |

| Description:                                                                                        | the result<br>is 1, the re<br>ister 'f' (de<br>Access B                                | efault). If 'a'<br>ank will be se<br>Bank will be s | WREG. If 'd'<br>d back in reg<br>is 0, the<br>elected. If 'a' |

| Words:                                                                                              | 1                                                                                      |                                                     |                                                               |

| Cycles:                                                                                             | 1                                                                                      |                                                     |                                                               |

| Q Cycle Activity:                                                                                   |                                                                                        |                                                     |                                                               |

| Q1                                                                                                  | Q2                                                                                     | Q3                                                  | Q4                                                            |

| Decode                                                                                              | Read<br>register 'f'                                                                   | Process<br>Data                                     | Write to destination                                          |

| Example:                                                                                            | ADDWF                                                                                  | REG, W                                              |                                                               |

|                                                                                                     |                                                                                        |                                                     |                                                               |

| Before Instru                                                                                       | iction                                                                                 |                                                     |                                                               |

| Before Instru<br>WREG                                                                               | = 0x17                                                                                 |                                                     |                                                               |

| Before Instru<br>WREG<br>REG                                                                        | = 0x17<br>= 0xC2                                                                       |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N                                                                   | = 0x17<br>= 0xC2<br>= ?                                                                |                                                     |                                                               |

| Before Instru<br>WREG<br>REG                                                                        | = 0x17<br>= 0xC2                                                                       |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV                                                             | = 0x17<br>= 0xC2<br>= ?<br>= ?                                                         |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C                                                        | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?                                                  |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct                           | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>= ?                                    |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>WREG                   | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>= ?<br>tion<br>= 0xD9                  |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>WREG<br>REG            | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>= ?<br>tion<br>= 0xD9<br>= 0xC2        |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>WREG<br>REG<br>N       | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>tion<br>= 0xD9<br>= 0xC2<br>= 1        |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>WREG<br>REG            | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>= ?<br>tion<br>= 0xD9<br>= 0xC2        |                                                     |                                                               |

| Before Instru<br>WREG<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>WREG<br>REG<br>N<br>OV | = 0x17<br>= 0xC2<br>= ?<br>= ?<br>= ?<br>= ?<br>tion<br>= 0xD9<br>= 0xC2<br>= 1<br>= 0 |                                                     |                                                               |

| BNC                                                                      | Branch if                                          | Not Carry                    |                 | В              | NN                                                | Branch if                                             | Not Negati                                  | ve                                                                                        |  |

|--------------------------------------------------------------------------|----------------------------------------------------|------------------------------|-----------------|----------------|---------------------------------------------------|-------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Syntax:                                                                  | [ <i>label</i> ] B                                 | NC n                         |                 | Sy             | ntax:                                             | [ <i>label</i> ] B                                    | [ <i>label</i> ] BNN n                      |                                                                                           |  |

| Operands:                                                                | -128 ≤ n ≤                                         | 127                          |                 | O              | perands:                                          | -128 ≤ n ≤                                            | $-128 \le n \le 127$                        |                                                                                           |  |

| Operation:                                                               | if carry bit<br>(PC) + 2 +                         | is '0'<br>- 2n → PC          |                 | O              | peration:                                         | if negative bit is '0' (PC) + 2 + 2n $\rightarrow$ PC |                                             |                                                                                           |  |

| Status Affecte                                                           | Status Affected: None                              |                              | St              | atus Affected: | None                                              |                                                       |                                             |                                                                                           |  |

| Encoding:                                                                | coding: 1110 0011 nnnn nnnn                        |                              | Er              | ncoding:       | 1110                                              | 0111 nn                                               | nn nnnn                                     |                                                                                           |  |

| Description: If the Carry bit is '0', then the pro-<br>gram will branch. |                                                    | De                           | escription:     |                | ative bit is '0<br>vill branch.                   | ', then the                                           |                                             |                                                                                           |  |

|                                                                          | added to t<br>have incre<br>instruction<br>PC+2+2n | he PC. Since                 |                 |                |                                                   | added to t<br>have incre<br>instruction<br>PC+2+2n.   | he PC. Since<br>mented to for<br>the new ac | umber '2n' is<br>ce the PC will<br>etch the next<br>ddress will be<br>ction is then<br>n. |  |

| Words:                                                                   | 1                                                  |                              |                 | W              | ords:                                             | 1                                                     |                                             |                                                                                           |  |

| Cycles:                                                                  | 1(2)                                               |                              |                 | Cy             | cles:                                             | 1(2)                                                  |                                             |                                                                                           |  |

| Q Cycle Activi<br>If Jump:                                               | ty:                                                |                              |                 |                | Cycle Activity:<br>Jump:                          |                                                       |                                             |                                                                                           |  |

| Q1                                                                       | Q2                                                 | Q3                           | Q4              |                | Q1                                                | Q2                                                    | Q3                                          | Q4                                                                                        |  |

| Decode                                                                   | Read literal<br>'n'                                | Process<br>Data              | Write to PC     |                | Decode                                            | Read literal<br>'n'                                   | Process<br>Data                             | Write to PC                                                                               |  |

| No<br>operation                                                          | No<br>operation                                    | No<br>operation              | No<br>operation |                | No<br>operation                                   | No<br>operation                                       | No<br>operation                             | No<br>operation                                                                           |  |

| If No Jump:                                                              |                                                    |                              |                 | lf             | No Jump:                                          |                                                       |                                             |                                                                                           |  |

| Q1                                                                       | Q2                                                 | Q3                           | Q4              |                | Q1                                                | Q2                                                    | Q3                                          | Q4                                                                                        |  |

| Decode                                                                   | Read literal<br>'n                                 | Process<br>Data              | No<br>operation |                | Decode                                            | Read literal<br>'n'                                   | Process<br>Data                             | No<br>operation                                                                           |  |

| Example:                                                                 | HERE                                               | BNC Jump                     | )               | <u>E&gt;</u>   | ample:                                            | HERE                                                  | BNN Jump                                    | )                                                                                         |  |

| Before In                                                                | struction                                          |                              |                 |                | Before Instr                                      | uction                                                |                                             |                                                                                           |  |

| PC                                                                       | = ad                                               | dress (HERE)                 | )               |                | PC                                                | = ad                                                  | dress (HERE)                                | )                                                                                         |  |

| If Car                                                                   | ry = 0;<br>PC = ad<br>ry = 1;                      | dress (Jump)<br>dress (HERE- |                 |                | After Instruc<br>If Negat<br>PC<br>If Negat<br>PC | ive = 0;<br>= ad<br>ive = 1;                          | dress (Jump)<br>dress (HERE-                |                                                                                           |  |

| GOT   | 0                                        | Uncondit                                                                        | ional B                                    | ranch                               |                                        | INCF                  |

|-------|------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|----------------------------------------|-----------------------|

| Synt  | ax:                                      | [ label ]                                                                       | GOTO                                       | k                                   |                                        | Synta                 |

| Ope   | rands:                                   | $0 \le k \le 10$                                                                | 48575                                      |                                     |                                        | Oper                  |

| Ope   | ration:                                  | $k \rightarrow PC < 2$                                                          | 20:1>                                      |                                     |                                        |                       |

| State | us Affected:                             | None                                                                            |                                            |                                     |                                        | Oner                  |

| 1st v | oding:<br>vord (k<7:0>)<br>word(k<19:8>  |                                                                                 | 1111<br>k <sub>19</sub> kkk                | k <sub>7</sub> kkk<br>kkkk          | kkkk <sub>0</sub><br>kkkk <sub>8</sub> | Oper<br>Statu<br>Enco |

| Des   | cription:                                | GOTO allo<br>branch an<br>byte mem<br>value 'k' is<br>GOTO is al<br>instruction | iywhere<br>ory rang<br>s loadec<br>lways a | within er<br>ge. The :<br>I into PC | ntire 2M<br>20-bit<br><20:1>.          | Desc                  |

| Wor   | ds:                                      | 2                                                                               |                                            |                                     |                                        |                       |

| Cycl  | es:                                      | 2                                                                               |                                            |                                     |                                        |                       |

| QC    | vcle Activity:                           |                                                                                 |                                            |                                     |                                        | Word                  |

|       | Q1                                       | Q2                                                                              | Q                                          | 3                                   | Q4                                     | Cycle                 |

|       | Decode                                   | Read literal<br>'k'<7:0>,                                                       | No<br>operat                               | ion 'k                              | ad literal<br><19:8>,<br>ite to PC     | Q Cy                  |

|       | No<br>operation                          | No<br>operation                                                                 | No<br>operat                               |                                     | No<br>peration                         | ] [                   |

|       | <u>mple</u> :<br>After Instructi<br>PC = | GOTO THE<br>on<br>Address (TH                                                   |                                            |                                     |                                        | <u>Exan</u><br>F      |

| INCF                                                    | Incremen                                                                                                                  | tf                                                                      |                                                           |                                            |                                                            |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|------------------------------------------------------------|--|--|

| Syntax:                                                 | [ label ]                                                                                                                 |                                                                         | ] b, ]                                                    | ,a]]                                       |                                                            |  |  |

| Operands:                                               | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                       |                                                                         |                                                           |                                            |                                                            |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ c                                                                                                   | dest                                                                    |                                                           |                                            |                                                            |  |  |

| Status Affected:                                        | C,DC,N,C                                                                                                                  | DV,Z                                                                    |                                                           |                                            |                                                            |  |  |

| Encoding:                                               | 0010                                                                                                                      | 10da                                                                    | fff                                                       | f                                          | ffff                                                       |  |  |

| Description:                                            | The conte<br>increment<br>placed in V<br>result is pl<br>(default).<br>Bank will b<br>the BSR v<br>will be sele<br>value. | ed. If 'd'<br>WREG.<br>laced ba<br>If 'a' is (<br>pe selec<br>ralue. If | is 0,<br>If 'd' i<br>ack in<br>0, the<br>ted, o<br>'a' is | the<br>is 1,<br>reg<br>Acc<br>over<br>1, t | result is<br>the<br>ister 'f'<br>cess<br>riding<br>he Bank |  |  |

| Words:                                                  | 1                                                                                                                         |                                                                         |                                                           |                                            |                                                            |  |  |

| Cycles:                                                 | 1                                                                                                                         |                                                                         |                                                           |                                            |                                                            |  |  |

| Q Cycle Activity:                                       |                                                                                                                           |                                                                         |                                                           |                                            |                                                            |  |  |

| Q1                                                      | Q2                                                                                                                        | Q3                                                                      | 3                                                         |                                            | Q4                                                         |  |  |

| Decode                                                  | Read<br>register 'f'                                                                                                      | Proce<br>Data                                                           |                                                           |                                            | /rite to<br>stination                                      |  |  |

| Example:                                                | INCF                                                                                                                      | CNT                                                                     |                                                           |                                            |                                                            |  |  |

| Before Instru<br>CNT<br>Z<br>C<br>DC<br>After Instructi | = 0xFF<br>= 0<br>= ?<br>= ?                                                                                               |                                                                         |                                                           |                                            |                                                            |  |  |

| ter Instruction |             |  |  |  |  |

|-----------------|-------------|--|--|--|--|

| =               | 0x00        |  |  |  |  |

| =               | 1           |  |  |  |  |

| =               | 1           |  |  |  |  |

| =               | 1           |  |  |  |  |

|                 | =<br>=<br>= |  |  |  |  |

| LFS                                                                                                    | R              | Load FSF                                                           | R                                                                    |  |           |                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------|----------------------------------------------------------------------|--|-----------|------------------------------------|--|--|--|

| Synt                                                                                                   | ax:            | [ label ]                                                          | [ <i>label</i> ] LFSR f,k                                            |  |           |                                    |  |  |  |

| Operands:                                                                                              |                | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 4095 \end{array}$ |  |           |                                    |  |  |  |

| Operation:                                                                                             |                | $k \to FSRf$                                                       | $k \rightarrow FSRf$                                                 |  |           |                                    |  |  |  |

| Status Affected:                                                                                       |                | None                                                               | None                                                                 |  |           |                                    |  |  |  |

| Enco                                                                                                   | oding:         | 1110<br>1111                                                       |                                                                      |  |           | k <sub>11</sub> kkk<br>kkkk        |  |  |  |

| Description:                                                                                           |                | The 12-bit<br>the file se<br>by 'f'                                |                                                                      |  |           |                                    |  |  |  |

| Wor                                                                                                    | ds:            | 2                                                                  |                                                                      |  |           |                                    |  |  |  |

| Cycles:                                                                                                |                | 2                                                                  | 2                                                                    |  |           |                                    |  |  |  |

| QC                                                                                                     | vcle Activity: |                                                                    |                                                                      |  |           |                                    |  |  |  |

|                                                                                                        | Q1             | Q2                                                                 | Q3                                                                   |  |           | Q4                                 |  |  |  |

|                                                                                                        | Decode         | Read literal<br>'k' MSB                                            | Proce:<br>Data                                                       |  | lite<br>M | Vrite<br>eral 'k'<br>SB to<br>SRfH |  |  |  |

|                                                                                                        | Decode         | Read literal<br>'k' LSB                                            | Proce:<br>Data                                                       |  |           | te literal<br>o FSRfL              |  |  |  |

| Example:     LFSR FSR2, 0x3AB       After Instruction     FSR2H       FSR2H     =       0x03     FSR2L |                |                                                                    |                                                                      |  |           |                                    |  |  |  |

|                                                                                                | Move f                                                                                                                                                                                                                                                             |                                                                                   |                                                                                |                                                            |  |  |  |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| Syntax:                                                                                        | [label]                                                                                                                                                                                                                                                            | [ <i>label</i> ] MOVF f[,d[,a]]                                                   |                                                                                |                                                            |  |  |  |

| Operands:                                                                                      |                                                                                                                                                                                                                                                                    | 0 ≤ f ≤ 255                                                                       |                                                                                |                                                            |  |  |  |

|                                                                                                | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                             |                                                                                   |                                                                                |                                                            |  |  |  |