Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 68                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 80-TQFP                                                                  |

| Supplier Device Package    | 80-TQFP (12x12)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c858-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name |       |       | umber |       |             |                |                                                                      |

|----------|-------|-------|-------|-------|-------------|----------------|----------------------------------------------------------------------|

|          | PIC18 | BC658 | PIC18 | BC858 | Pin<br>Type | Buffer<br>Type |                                                                      |

|          | TQFP  | PLCC  | TQFP  | PLCC  |             |                | Description                                                          |

|          |       |       |       |       |             |                | PORTE is a bi-directional I/O port                                   |

| RE0/RD   | 2     | 11    | 4     | 15    |             |                |                                                                      |

| RE0      |       |       |       |       | I/O         | ST             | Digital I/O                                                          |

| RD       |       |       |       |       | I           | TTL            | Read control for parallel slave port<br>(See WR and CS pins)         |

| RE1/WR   | 1     | 10    | 3     | 14    |             |                |                                                                      |

| RE1      |       |       |       |       | I/O         | ST             | Digital I/O                                                          |

| WR       |       |       |       |       | I           | TTL            | Write <u>control</u> for parallel slave port<br>(See CS and RD pins) |

| RE2/CS   | 64    | 9     | 78    | 9     |             |                |                                                                      |

| RE2      |       |       |       |       | I/O         | ST             | Digital I/O                                                          |

| CS       |       |       |       |       | I           | TTL            | Chip select control for parallel slave<br>port (See RD and WR)       |

| RE3      | 63    | 8     | 77    | 8     | I/O         | ST             | Digital I/O                                                          |

| RE4      | 62    | 7     | 76    | 7     | I/O         | ST             | Digital I/O                                                          |

| RE5      | 61    | 6     | 75    | 6     | I/O         | ST             | Digital I/O                                                          |

| RE6      | 60    | 5     | 74    | 5     | I/O         | ST             | Digital I/O                                                          |

| RE7/CCP2 | 59    | 4     | 73    | 4     |             |                | _                                                                    |

| RE7      |       |       |       |       | I/O         | ST             | Digital I/O                                                          |

| CCP2     |       |       |       |       | I/O         | ST             | Capture2 input, Compare2 output,<br>PWM2 output                      |

#### **PINOUT I/O DESCRIPTIONS (CONTINUED) TABLE 1-2:**

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input 0

= Input = Power L Ρ

= Output

OD = Open Drain (no P diode to VDD)

### 4.7.1 TWO WORD INSTRUCTIONS

The PIC18CXX8 devices have 4 two word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSB's set to 1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to Section 19.0 for further details of the instruction set.

### 4.8 Lookup Tables

Lookup tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

#### 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A lookup table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

```

Warning: The LSb of PCL is fixed to a value of '0'.

Hence, computed GOTO to an odd

address is not possible.

```

4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Lookup table data may be stored as 2 bytes per program word by using table reads and writes. The table pointer (TBLPTR) specifies the byte address and the table latch (TABLAT) contains the data that is read from, or written to, program memory. Data is transferred to/from program memory one byte at a time.

A description of the Table Read/Table Write operation is shown in Section 5.0.

|      | CASE 1:                 |        |                                             |  |  |  |  |  |  |

|------|-------------------------|--------|---------------------------------------------|--|--|--|--|--|--|

|      | Object Code Source Code |        |                                             |  |  |  |  |  |  |

| 0110 | 0110 0000 0000          | TSTFSZ | REG1 ; is RAM location 0?                   |  |  |  |  |  |  |

| 1100 | 0001 0010 0011          | MOVFF  | REG1, REG2 ; No, execute 2-word instruction |  |  |  |  |  |  |

| 1111 | 0100 0101 0110          |        | ; 2nd operand holds address of REG2         |  |  |  |  |  |  |

| 0010 | 0100 0000 0000          | ADDWF  | REG3 ; continue code                        |  |  |  |  |  |  |

|      |                         |        | CASE 2:                                     |  |  |  |  |  |  |

|      | Object Code             |        | Source Code                                 |  |  |  |  |  |  |

| 0110 | 0110 0000 0000          | TSTFSZ | REG1 ; is RAM location 0?                   |  |  |  |  |  |  |

| 1100 | 0001 0010 0011          | MOVFF  | REG1, REG2 ; Yes                            |  |  |  |  |  |  |

| 1111 | 0100 0101 0110          |        | ; 2nd operand becomes NOP                   |  |  |  |  |  |  |

| 0010 | 0100 0000 0000          | ADDWF  | REG3 ; continue code                        |  |  |  |  |  |  |

### EXAMPLE 4-3: TWO WORD INSTRUCTIONS

## 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 4-4 shows the data memory organization for the PIC18CXX8 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFR's are used for control and status of the controller and peripheral functions, while GPR's are used for data storage and scratch pad operations in the user's application. The SFR's start at the last location of Bank 15 (0xFFF) and grow downwards. GPR's start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of the File Select Register (FSR). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two word/two cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFR's and select GPR's) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates through the File Select Registers (FSR). The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPR's are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. Bank 15 (0xF00 to 0xFFF) contains SFR's. All other banks of data memory contain GPR registers starting with bank 0.

### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFR's) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2.

The SFR's can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFR's are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's. See Table 4-2 for addresses for the SFR's.

# TABLE 4-2: SPECIAL FUNCTION REGISTER MAP

| Address | Address Name Address Name A |      | Address               | Name | Address | Name |                      |

|---------|-----------------------------|------|-----------------------|------|---------|------|----------------------|

| FFFh    | TOSU                        | FDFh | INDF2 <sup>(2)</sup>  | FBFh | CCPR1H  | F9Fh | IPR1                 |

| FFEh    | TOSH                        | FDEh | POSTINC2(2)           | FBEh | CCPR1L  | F9Eh | PIR1                 |

| FFDh    | TOSL                        | FDDh | POSTDEC2(2)           | FBDh | CCP1CON | F9Dh | PIE1                 |

| FFCh    | STKPTR                      | FDCh | PREINC2(2)            | FBCh | CCPR2H  | F9Ch |                      |

| FFBh    | PCLATU                      | FDBh | PLUSW2 <sup>(2)</sup> | FBBh | CCPR2L  | F9Bh | _                    |

| FFAh    | PCLATH                      | FDAh | FSR2H                 | FBAh | CCP2CON | F9Ah | TRISJ <sup>(5)</sup> |

| FF9h    | PCL                         | FD9h | FSR2L                 | FB9h | —       | F99h | TRISH <sup>(5)</sup> |

| FF8h    | TBLPTRU                     | FD8h | STATUS                | FB8h | _       | F98h | TRISG                |

| FF7h    | TBLPTRH                     | FD7h | TMR0H                 | FB7h | _       | F97h | TRISF                |

| FF6h    | TBLPTRL                     | FD6h | TMR0L                 | FB6h | —       | F96h | TRISE                |

| FF5h    | TABLAT                      | FD5h | TOCON                 | FB5h | CVRCON  | F95h | TRISD                |

| FF4h    | PRODH                       | FD4h | _                     | FB4h | CMCON   | F94h | TRISC                |

| FF3h    | PRODL                       | FD3h | OSCCON                | FB3h | TMR3H   | F93h | TRISB                |

| FF2h    | INTCON                      | FD2h | LVDCON                | FB2h | TMR3L   | F92h | TRISA                |

| FF1h    | INTCON2                     | FD1h | WDTCON                | FB1h | T3CON   | F91h | LATJ <sup>(5)</sup>  |

|         | INTCON3                     | FD0h | RCON                  | FB0h | PSPCON  | F90h | LATH <sup>(5)</sup>  |

|         | INDF0 <sup>(2)</sup>        | FCFh | TMR1H                 | FAFh | SPBRG   | F8Fh | LATG                 |

|         | POSTINC0 <sup>(2)</sup>     | FCEh | TMR1L                 | FAEh | RCREG   | F8Eh | LATF                 |

|         | POSTDEC0(2)                 | FCDh | T1CON                 | FADh | TXREG   | F8Dh | LATE                 |

|         | PREINC0 <sup>(2)</sup>      | FCCh | TMR2                  | FACh | TXSTA   | F8Ch | LATD                 |

| FEBh    | PLUSW0(2)                   | FCBh | PR2                   | FABh | RCSTA   | F8Bh | LATC                 |

| FEAh    | FSR0H                       | FCAh | T2CON                 | FAAh |         | F8Ah | LATB                 |

| FE9h    | FSR0L                       | FC9h | SSPBUF                | FA9h |         |      | LATA                 |

|         | WREG                        | FC8h | SSPADD                | FA8h |         | F88h | PORTJ <sup>(5)</sup> |

|         | INDF1 <sup>(2)</sup>        | FC7h | SSPSTAT               | FA7h |         | F87h | PORTH <sup>(5)</sup> |

|         | POSTINC1 <sup>(2)</sup>     | FC6h | SSPCON1               | FA6h |         | F86h | PORTG                |

|         | POSTDEC1(2)                 | FC5h | SSPCON2               | FA5h | IPR3    | F85h | PORTF                |

|         | PREINC1 <sup>(2)</sup>      | FC4h | ADRESH                | FA4h | PIR3    | F84h | PORTE                |

| FE3h    | PLUSW1 <sup>(2)</sup>       | FC3h | ADRESL                | FA3h | PIE3    | F83h | PORTD                |

| FE2h    | FSR1H                       | FC2h | ADCON0                | FA2h | IPR2    | F82h | PORTC                |

| FE1h    | FSR1L                       | FC1h | ADCON1                | FA1h | PIR2    | F81h | PORTB                |

| FE0h    | BSR                         | FC0h | ADCON2                | FA0h | PIE2    | F80h | PORTA                |

Note 1: Unimplemented registers are read as '0'.

- **2:** This is not a physical register.

- 3: Contents of register is dependent on WIN2:WIN0 bits in CANCON register.

- **4:** CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the CANSTAT register due to the Microchip Header file requirement.

- 5: Available on PIC18C858 only.

### 4.12 Indirect Addressing, INDF and FSR Registers

Indirect addressing is a mode of addressing data memory, where the data memory address in the instruction is not fixed. A SFR register is used as a pointer to the data memory location that is to be read or written. Since this pointer is in RAM, the contents can be modified by the program. This can be useful for data tables in the data memory and for software stacks. Figure 4-6 shows the operation of indirect addressing. This shows the moving of the value to the data memory address specified by the value of the FSR register.

Indirect addressing is possible by using one of the INDF registers. Any instruction using the INDF register actually accesses the register indicated by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation. The FSR register contains a 12-bit address, which is shown in Figure 4-6.

The INDFn ( $0 \le n \le 2$ ) register is not a physical register. Addressing INDFn actually addresses the register whose address is contained in the FSRn register (FSRn is a pointer). This is indirect addressing.

Example 4-4 shows a simple use of indirect addressing to clear the RAM in Bank 1 (locations 100h-1FFh) in a minimum number of instructions.

### EXAMPLE 4-4: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|      | LFSR  | FSR0, 0x100 | ; |                |

|------|-------|-------------|---|----------------|

| NEXT | CLRF  | POSTINC0    | ; | Clear INDF     |

|      |       |             | ; | register       |

|      |       |             | ; | & inc pointer  |

|      | BTFSS | FSROH, 1    | ; | All done       |

|      |       |             | ; | w/ Bank1?      |

|      | GOTO  | NEXT        | ; | NO, clear next |

| CONT | INUE  |             | ; |                |

|      | :     |             | ; | YES, continue  |

|      |       |             |   |                |

There are three indirect addressing registers. To address the entire data memory space (4096 bytes), these registers are 12-bit wide. To store the 12-bits of addressing information, two 8-bit registers are required. These indirect addressing registers are:

- 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

In addition, there are registers INDF0, INDF1 and INDF2, which are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data.

If an instruction writes a value to INDF0, the value will be written to the address indicated by FSR0H:FSR0L. A read from INDF1 reads the data from the address indicated by FSR1H:FSR1L. INDFn can be used in code anywhere an operand can be used.

If INDF0, INDF1 or INDF2 are read indirectly via an FSR, all '0's are read (zero bit is set). Similarly, if INDF0, INDF1 or INDF2 are written to indirectly, the operation will be equivalent to a NOP instruction and the STATUS bits are not affected.

### 4.12.1 INDIRECT ADDRESSING OPERATION

Each FSR register has an INDF register associated with it, plus four additional register addresses. Performing an operation on one of these five registers determines how the FSR will be modified during indirect addressing.

When data access is done to one of the five INDFn locations, the address selected will configure the FSRn register to:

- Do nothing to FSRn after an indirect access (no change) INDFn

- Auto-decrement FSRn after an indirect access (post-decrement) POSTDECn

- Auto-increment FSRn after an indirect access (post-increment) POSTINCn

- Auto-increment FSRn before an indirect access (pre-increment) PREINCn

- Use the value in the WREG register as an offset to FSRn. Do not modify the value of the WREG or the FSRn register after an indirect access (no change) - PLUSWn

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the STATUS register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

Incrementing or decrementing an FSR affects all 12 bits. That is, when FSRnL overflows from an increment, FSRnH will be incremented automatically.

Adding these features allows the FSRn to be used as a software stack pointer in addition to its uses for table operations in data memory.

Each FSR has an address associated with it that performs an indexed indirect access. When a data access to this INDFn location (PLUSWn) occurs, the FSRn is configured to add the 2's complement value in the WREG register and the value in FSR to form the address before an indirect access. The FSR value is not changed.

If an FSR register contains a value that indicates one of the INDFn, an indirect read will read 00h (zero bit is set), while an indirect write will be equivalent to a NOP (STATUS bits are not affected).

If an indirect addressing operation is done where the target address is an FSRnH or FSRnL register, the write operation will dominate over the pre- or post-increment/decrement functions.

## 8.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output ( i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

|       | $LL 0^{-2}$ . |                         |

|-------|---------------|-------------------------|

| CLRF  | PORTB         | ; Initialize PORTB by   |

|       |               | ; clearing output       |

|       |               | ; data latches          |

| CLRF  | LATB          | ; Alternate method      |

|       |               | ; to clear output       |

|       |               | ; data latches          |

| MOVLW | 0xCF          | ; Value used to         |

|       |               | ; initialize data       |

|       |               | ; direction             |

| MOVWF | TRISB         | ; Set RB3:RB0 as inputs |

|       |               | ; RB5:RB4 as outputs    |

|       |               | ; RB7:RB6 as inputs     |

|       |               |                         |

EXAMPLE 8-2: INITIALIZING PORTB

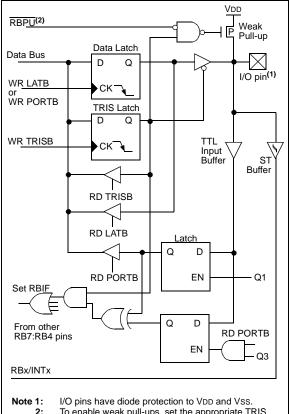

# FIGURE 8-4: RB7:RB4 PINS BLOCK DIAGRAM

To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (INTCON2 register).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\mathsf{RBPU}}$  (INTCON2 register). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'd together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON register).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

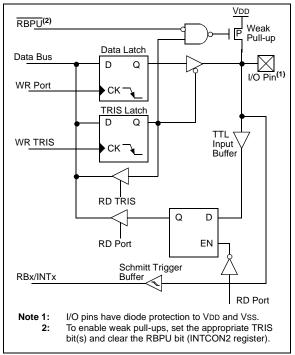

### FIGURE 8-5: RB3:RB0 PINS BLOCK DIAGRAM

## 13.2 <u>Timer1 Oscillator</u>

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN bit (T1CON Register). The oscillator is a low power oscillator rated up to 200 kHz. Refer to "Timer1 Module", Section 11.0 for Timer1 oscillator details.

# 13.3 <u>Timer3 Interrupt</u>

The TMR3 Register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR3IF (PIR Registers). This interrupt can be enabled/disabled by setting/clearing TMR3 interrupt enable bit TMR3IE (PIE Registers).

# 13.4 <u>Resetting Timer3 Using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CCP |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit  |

|       | TMR3IF (PIR registers).                 |

Timer3 must be configured for either timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this RESET operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L registers pair becomes the period register for Timer3. Refer to "Capture/Compare/PWM (CCP) Modules", Section 14.0 for CCP details.

| Name   | Bit 7        | Bit 6         | Bit 5         | Bit 4         | Bit 3          | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|--------|--------------|---------------|---------------|---------------|----------------|-------------|--------|--------|-------------------------|---------------------------------|

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE        | INTOIE        | RBIE           | TMR0IF      | INTOIF | RBIF   | 0000 000x               | 0000 000u                       |

| PIR2   | _            | CMIF          | _             | _             | BCLIF          | LVDIF       | TMR3IF | CCP2IF | -0 0000                 | -0 0000                         |

| PIE2   | —            | CMIE          | —             | _             | BCLIE          | LVDIE       | TMR3IE | CCP2IE | -0 0000                 | -0 0000                         |

| IPR2   | —            | CMIP          | —             | _             | BCLIP          | LVDIP       | TMR3IP | CCP2IP | -0 0000                 | -0 0000                         |

| TMR3L  | Holding      | register fo   | r the Least S | Significant B | yte of the 16- | bit TMR3 re | gister |        | xxxx xxxx               | uuuu uuuu                       |

| TMR3H  | Holding      | register fo   |               | xxxx xxxx     | uuuu uuuu      |             |        |        |                         |                                 |

| T1CON  | RD16         | —             | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS | TMR10N | 0-00 0000               | u-uu uuuu                       |

| T3CON  | RD16         | T3CCP2        | T3CKPS1       | T3CKPS0       | T3CCP1         | T3SYNC      | TMR3CS | TMR3ON | 0000 0000               | uuuu uuuu                       |

TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

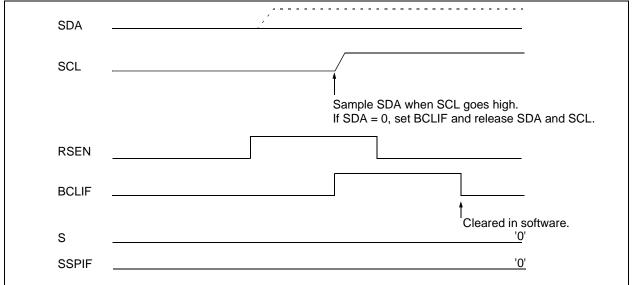

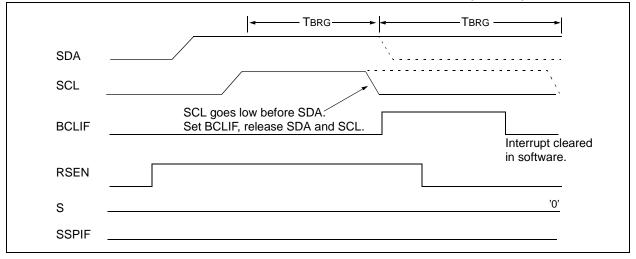

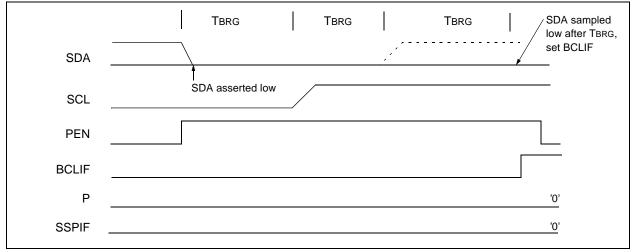

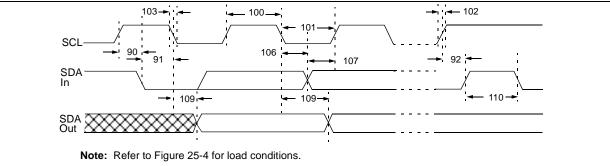

### 15.4.16.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e, another master is attempting to transmit a data '0', see Figure 15-24). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition (Figure 15-25).

If at the end of the BRG time-out both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

# FIGURE 15-24: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 15-25: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

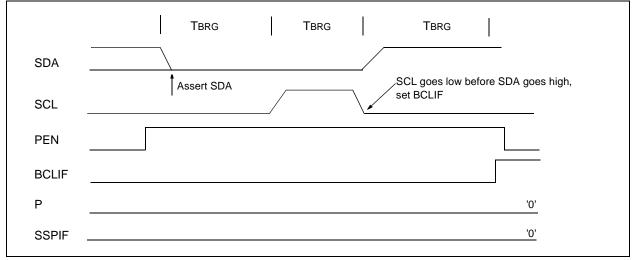

15.4.16.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 15-26). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 15-27).

# FIGURE 15-26: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 15-27: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| bit 7 bit 7 <b>RXFUL:</b> Receive Full Status bit<br>1 = Receive buffer contains a received message<br>0 = Receive buffer is open to receive a new message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ISTER 17-13: RXB1CON – RECEIVE BUFFER 1 CONTROL REGISTER |                                                                                                                                                                                                                   |                |                |           |                  |            |              |         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----------|------------------|------------|--------------|---------|--|--|--|

| bit 7       bit 7         bit 7       RXFUL: Receive Full Status bit         1 = Receive buffer contains a received message       0 = Receive buffer is open to receive a new message         0 = Receive buffer is open to receive a new message       0 = Receive buffer is open to receive a new message         Note:       This bit is set by the CAN module and should be cleared by software after the buffer is read.         bit 6-5       RXM1:RXM0: Receive Buffer Mode bits         11 = Receive all messages (including those with errors)       10 = Receive only valid messages with extended identifier         01 = Receive only valid messages with standard identifier       0 = Receive all valid messages         bit 4       Unimplemented: Read as '0'         bit 3       RXRTRRO: Receive Remote Transfer Request bit (read only)         1 = Remote transfer request       0 = No remote transfer request         bit 2-0       FILHIT2:FILHIT0: Filter Hit bits         These bits indicate which acceptance filter enabled the last message reception into Receive         Buffer 1.       11 = Reserved         10 = Receptance Filter 5 (RXF5)       100 = Acceptance Filter 4 (RXF4)         01 = Acceptance Filter 4 (RXF3)       010 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set         00 = Acceptance Filter 1 (RXF0) only possible when RXB0DBEN bit is set       000 = Acceptance Filter 1 (RXF0) only possible when RXB0DBEN bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          | R/C-0                                                                                                                                                                                                             | R/W-0          | R/W-0          | U-0       | R-0              | R-0        | R-0          | R-0     |  |  |  |

| bit 7 <b>RXFUL:</b> Receive Full Status bit<br>1 = Receive buffer contains a received message<br>0 = Receive buffer is open to receive a new message<br>Note: This bit is set by the CAN module and should be cleared by software after the buff<br>is read.<br>bit 6-5 <b>RXM1:RXM0:</b> Receive Buffer Mode bits<br>11 = Receive all messages (including those with errors)<br>10 = Receive only valid messages with extended identifier<br>01 = Receive only valid messages with standard identifier<br>02 = Receive all valid messages with standard identifier<br>03 = Receive all valid messages<br>bit 4 <b>Unimplementet:</b> Read as '0'<br>bit 3 <b>RXRTRR0:</b> Receive Remote Transfer Request bit (read only)<br>1 = Remote transfer request<br>0 = No remote transfer request<br>0 = No remote transfer request<br>bit 2-0 <b>FILHIT2:FILHIT0:</b> Filter Hit bits<br>These bits indicate which acceptance filter enabled the last message reception into Receive<br>Buffer 1.<br>111 = Reserved<br>110 = Reserved<br>110 = Receptance Filter 5 (RXF5)<br>100 = Acceptance Filter 7 (RXF1)<br>011 = Acceptance Filter 7 (RXF2)<br>011 = Acceptance Filter 7 (RXF1)<br>012 = Acceptance Filter 7 (RXF2)<br>013 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>00 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>100 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>101 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>102 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>103 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set |                                                          | RXFUL                                                                                                                                                                                                             | RXM1           | RXM0           | —         | RXRTRRO          | FILHIT2    | FILHIT1      | FILHIT0 |  |  |  |

| <ul> <li>1 = Receive buffer contains a received message</li> <li>0 = Receive buffer is open to receive a new message</li> <li>Note: This bit is set by the CAN module and should be cleared by software after the buff is read.</li> <li>bit 6-5 RXM1:RXM0: Receive Buffer Mode bits         <ol> <li>1 = Receive all messages (including those with errors)</li> <li>10 = Receive only valid messages with extended identifier</li> <li>01 = Receive only valid messages with standard identifier</li> <li>01 = Receive all valid messages with standard identifier</li> <li>00 = Receive all valid messages</li> </ol> </li> <li>bit 4 Unimplemented: Read as '0'</li> <li>bit 3 RXRTRRO: Receive Remote Transfer Request bit (read only)         <ol> <li>1 = Remote transfer request</li> <li>0 = No remote transfer request</li> <li>0 = No remote transfer request</li> <li>bit 2-0 FILHIT2:FILHIT0: Filter Hit bits</li> <li>These bits indicate which acceptance filter enabled the last message reception into Receive Buffer 1.</li> <li>111 = Reserved</li> <li>100 = Acceptance Filter 5 (RXF5)</li> <li>100 = Acceptance Filter 5 (RXF3)</li> <li>101 = Acceptance Filter 7 (RXF4)</li> <li>111 = Acceptance Filter 7 (RXF2)</li> <li>112 = Acceptance Filter 7 (RXF3)</li> <li>113 = Acceptance Filter 7 (RXF4)</li> <li>114 = Acceptance Filter 7 (RXF4)</li> <li>115 = Acceptance Filter 7 (RXF4)</li> <li>116 = Acceptance Filter 7 (RXF4)</li> <li>117 = Acceptance Filter 7 (RXF4)</li> <li>118 = Acceptance Filter 7 (RXF4)</li> <li>118 = Acceptance Filter 7 (RXF4)</li> <li>119 = Acceptance Filter 7 (RXF4)</li> <li>110 = Acceptance Filter 7 (RXF4)</li> <li>111 = Reserved</li> <li>1114 = Reserved</li> <li>11</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | bit 7                                                                                                                                                                                                             |                |                |           |                  |            |              | bit 0   |  |  |  |

| is read.         bit 6-5       RXM1:RXM0: Receive Buffer Mode bits         11 = Receive all messages (including those with errors)         10 = Receive only valid messages with extended identifier         01 = Receive only valid messages with standard identifier         00 = Receive all valid messages         bit 4       Unimplemented: Read as '0'         bit 3       RXRTRRO: Receive Remote Transfer Request bit (read only)         1 = Remote transfer request         0 = No remote transfer request         bit 2-0         FILHIT2:FILHIT0: Filter Hit bits         These bits indicate which acceptance filter enabled the last message reception into Receive         Buffer 1.         111 = Reserved         100 = Receptance Filter 5 (RXF5)         100 = Acceptance Filter 5 (RXF4)         011 = Acceptance Filter 2 (RXF2)         001 = Acceptance Filter 2 (RXF2)         001 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 7                                                    | 1 = Receive buffer contains a received message                                                                                                                                                                    |                |                |           |                  |            |              |         |  |  |  |

| 11 = Receive all messages (including those with errors)         10 = Receive only valid messages with extended identifier         01 = Receive only valid messages         bit 4         Unimplemented: Read as '0'         bit 3         RXRTRRO: Receive Remote Transfer Request bit (read only)         1 = Remote transfer request         0 = No remote transfer request         0 = No remote transfer request         bit 2-0       FILHIT2:FILHIT0: Filter Hit bits         These bits indicate which acceptance filter enabled the last message reception into Receive         Buffer 1.         111 = Reserved         100 = Receptance Filter 5 (RXF5)         100 = Acceptance Filter 4 (RXF4)         011 = Acceptance Filter 3 (RXF3)         010 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         001 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         001 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | ,                                                                                                                                                                                                                 |                |                |           |                  |            |              |         |  |  |  |

| bit 3 <b>RXRTRRO</b> : Receive Remote Transfer Request bit (read only)<br>1 = Remote transfer request<br>0 = No remote transfer request<br>bit 2-0 <b>FILHIT2:FILHIT0:</b> Filter Hit bits<br>These bits indicate which acceptance filter enabled the last message reception into Receive<br>Buffer 1.<br>111 = Reserved<br>100 = Reserved<br>101 = Acceptance Filter 5 (RXF5)<br>100 = Acceptance Filter 4 (RXF4)<br>011 = Acceptance Filter 3 (RXF3)<br>010 = Acceptance Filter 2 (RXF2)<br>001 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set<br>000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 6-5                                                  | <ul> <li>11 = Receive all messages (including those with errors)</li> <li>10 = Receive only valid messages with extended identifier</li> <li>01 = Receive only valid messages with standard identifier</li> </ul> |                |                |           |                  |            |              |         |  |  |  |

| 1 = Remote transfer request         0 = No remote transfer request         bit 2-0       FILHIT2:FILHIT0: Filter Hit bits         These bits indicate which acceptance filter enabled the last message reception into Receive Buffer 1.         111 = Reserved         101 = Acceptance Filter 5 (RXF5)         100 = Acceptance Filter 4 (RXF4)         011 = Acceptance Filter 3 (RXF3)         010 = Acceptance Filter 2 (RXF2)         001 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 4                                                    | Unimplem                                                                                                                                                                                                          | ented: Read    | l as '0'       |           |                  |            |              |         |  |  |  |

| These bits indicate which acceptance filter enabled the last message reception into Receive Buffer 1.         111 = Reserved         100 = Reserved         101 = Acceptance Filter 5 (RXF5)         100 = Acceptance Filter 4 (RXF4)         011 = Acceptance Filter 3 (RXF3)         010 = Acceptance Filter 2 (RXF2)         001 = Acceptance Filter 1 (RXF1) only possible when RXB0DBEN bit is set         000 = Acceptance Filter 0 (RXF0) only possible when RXB0DBEN bit is set         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3                                                    | 1 = Remot                                                                                                                                                                                                         | e transfer red | quest          | er Reques | t bit (read only | /)         |              |         |  |  |  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 2-0                                                  | e when RXB0                                                                                                                                                                                                       | DBEN bit is    | s set          | Receive   |                  |            |              |         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          | Legend:                                                                                                                                                                                                           |                |                |           |                  |            |              |         |  |  |  |

| - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          | R = Reada                                                                                                                                                                                                         | ble bit        | W = Writab     | le bit    | U = Unimp        | lemented b | oit, read as | '0'     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          | - n = Value                                                                                                                                                                                                       | at POR         | '1' = Bit is s | et        | '0' = Bit is     | cleared    | x = Bit is u | nknown  |  |  |  |

#### \_... REGIST

# **REGISTER 17-14: RXBnSIDH – RECEIVE BUFFER n STANDARD IDENTIFIER HIGH BYTE** REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 SID10:SID3: Standard Identifier bits, if EXID = 0 (RXBnSIDL Register). Extended Identifier bits EID28:EID21, if EXID = 1.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

x = Bit is unknown

### 17.2.6 CAN MODULE I/O CONTROL REGISTER

This subsection describes the CAN Module I/O Control register.

## **REGISTER 17-32: CIOCON – CAN I/O CONTROL REGISTER**

- n = Value at POR

|         | R/W-0                     | R/W-0                      | R/W-0      | R/W-0         | U-0     | U-0        | U-0          | U-0   |  |  |

|---------|---------------------------|----------------------------|------------|---------------|---------|------------|--------------|-------|--|--|

|         | TX1SRC                    | TX1EN                      | ENDRHI     | CANCAP        |         | _          | —            |       |  |  |

|         | bit 7                     |                            |            |               |         |            |              | bit 0 |  |  |

|         |                           |                            |            |               |         |            |              |       |  |  |

| bit 7   | TX1SRC: C                 |                            |            |               |         |            |              |       |  |  |

|         | 1 = CAN T><br>0 = CAN T>  | •                          | •          | AIN CIUCK     |         |            |              |       |  |  |

| bit 6   | TX1EN: CA                 |                            |            |               |         |            |              |       |  |  |

|         | 1 = CAN T><br>0 = CAN T>  |                            |            | or CAN clock  |         |            |              |       |  |  |

| bit 5   | ENDRHI: E                 |                            |            |               |         |            |              |       |  |  |

|         |                           |                            | -          | lrive VDD whe |         | /e         |              |       |  |  |

| bit 4   | CANCAP:                   | CAN Messa                  | ge Receive | Capture Ena   | able    |            |              |       |  |  |

|         | 1 = Enable<br>0 = Disable | •                          |            |               |         |            |              |       |  |  |

| bit 3-0 |                           | •                          |            |               |         |            |              |       |  |  |

| DII 3-0 | ommpleme                  | Unimplemented: Read as '0' |            |               |         |            |              |       |  |  |

|         | Legend:                   |                            |            |               |         |            |              |       |  |  |

|         | R = Readab                | ole bit                    | W = Writa  | ble bit       | U = Uni | mplemented | bit, read as | '0'   |  |  |

'0' = Bit is cleared

'1' = Bit is set

### 17.2.7 CAN INTERRUPT REGISTERS

| FER 17-33: | PIR3 – PE                                                                                                                                                                                                           | RIPHERAL                                                                                                                              | INTERRUI    | PT FLAG R | EGISTER   |            |              |        |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|-----------|------------|--------------|--------|--|--|

|            | R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                                                 | R/W-0       | R/W-0     | R/W-0     | R/W-0      | R/W-0        | R/W-0  |  |  |

|            | IRXIF                                                                                                                                                                                                               | WAKIF                                                                                                                                 | ERRIF       | TXB2IF    | TXB1IF    | TXB0IF     | RXB1IF       | RXB0IF |  |  |

|            | bit 7                                                                                                                                                                                                               |                                                                                                                                       |             |           |           |            |              | bit 0  |  |  |

|            |                                                                                                                                                                                                                     |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 7      | IRXIF: CAN Invalid Received Message Interrupt Flag bit<br>1 = An invalid message has occurred on the CAN bus<br>0 = No invalid message on CAN bus                                                                   |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 6      | 1 = Activity                                                                                                                                                                                                        | WAKIF: CAN Bus Activity Wake-up Interrupt Flag bit<br>1 = Activity on CAN bus has occurred<br>0 = No activity on CAN bus              |             |           |           |            |              |        |  |  |

| bit 5      | 1 = An erro                                                                                                                                                                                                         | ERRIF: CAN Bus Error Interrupt Flag bit<br>1 = An error has occurred in the CAN module (multiple sources)<br>0 = No CAN module errors |             |           |           |            |              |        |  |  |

| bit 4      | <b>TXB2IF:</b> CAN Transmit Buffer 2 Interrupt Flag bit<br>1 = Transmit Buffer 2 has completed transmission of a message, and may be re-loaded<br>0 = Transmit Buffer 2 has not completed transmission of a message |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 3      | <b>TXB1IF:</b> CAN Transmit Buffer 1 Interrupt Flag bit<br>1 = Transmit Buffer 1 has completed transmission of a message, and may be re-loaded<br>0 = Transmit Buffer 1 has not completed transmission of a message |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 2      | <b>TXB0IF:</b> CAN Transmit Buffer 0 Interrupt Flag bit<br>1 = Transmit Buffer 0 has completed transmission of a message, and may be re-loaded<br>0 = Transmit Buffer 0 has not completed transmission of a message |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 1      | <b>RXB1IF:</b> CAN Receive Buffer 1 Interrupt Flag bit<br>1 = Receive Buffer 1 has received a new message<br>0 = Receive Buffer 1 has not received a new message                                                    |                                                                                                                                       |             |           |           |            |              |        |  |  |

| bit 0      | <b>RXBOIF:</b> CAN Receive Buffer 0 Interrupt Flag bit<br>1 = Receive Buffer 0 has received a new message<br>0 = Receive Buffer 0 has not received a new message                                                    |                                                                                                                                       |             |           |           |            |              |        |  |  |

|            | Legend:                                                                                                                                                                                                             |                                                                                                                                       |             |           |           |            |              |        |  |  |

|            | R = Reada                                                                                                                                                                                                           | ble bit                                                                                                                               | W = Writabl | e bit     | U = Unimp | lemented b | oit, read as | '0'    |  |  |

# REGISTER 17-33: PIR3 – PERIPHERAL INTERRUPT FLAG REGISTER

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown