Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 68                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

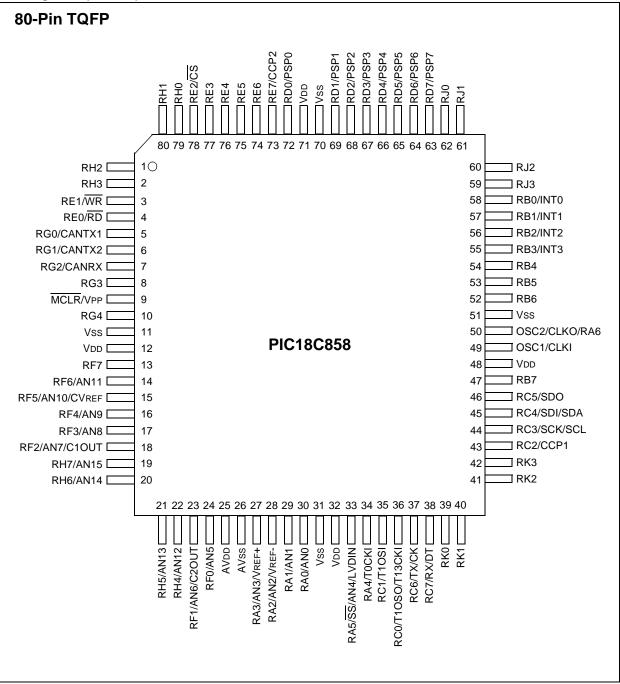

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c858t-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams (Cont.'d)

| TABLE 3-3 |             |               |                                    |                                                              |                                 |  |  |  |  |  |

|-----------|-------------|---------------|------------------------------------|--------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register  |             | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Reset<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| TOSU      | OSU 658 858 |               | 0 0000                             | 0 0000                                                       | 0 uuuu <sup>(3)</sup>           |  |  |  |  |  |

| TOSH      | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu <sup>(3)</sup>        |  |  |  |  |  |

| TOSL      | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu <sup>(3)</sup>        |  |  |  |  |  |

| STKPTR    | 658         | 858           | 00-0 0000                          | 00-0 0000                                                    | uu-u uuuu <sup>(3)</sup>        |  |  |  |  |  |

| PCLATU    | 658         | 858           | 0 0000                             | 0 0000                                                       | u uuuu                          |  |  |  |  |  |

| PCLATH    | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |  |  |  |  |

| PCL       | 658         | 858           | 0000 0000                          | 0000 0000                                                    | PC + 2 <sup>(2)</sup>           |  |  |  |  |  |

| TBLPTRU   | 658         | 858           | 00 0000                            | 00 0000                                                      | uu uuuu                         |  |  |  |  |  |

| TBLPTRH   | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |  |  |  |  |

| TBLPTRL   | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |  |  |  |  |

| TABLAT    | 658         | 858           | 0000 0000                          | 0000 0000                                                    | uuuu uuuu                       |  |  |  |  |  |

| PRODH     | 658         | 858           | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |  |  |  |  |  |

| PRODL     | 658         | 858           | XXXX XXXX                          | uuuu uuuu                                                    | uuuu uuuu                       |  |  |  |  |  |

| INTCON    | 658         | 858           | 0000 000x                          | 0000 000u                                                    | uuuu uuuu <sup>(1)</sup>        |  |  |  |  |  |

| INTCON2   | 658         | 858           | 1111 1111                          | 1111 1111                                                    | uuuu uuuu <sup>(1)</sup>        |  |  |  |  |  |

| INTCON3   | 658         | 858           | 1100 0000                          | 1100 0000                                                    | uuuu uuuu <sup>(1)</sup>        |  |  |  |  |  |

| INDF0     | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| POSTINC0  | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| POSTDEC0  | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| PREINC0   | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| PLUSW0    | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| FSR0H     | 658         | 858           | 0000                               | 0000                                                         | uuuu                            |  |  |  |  |  |

| FSR0L     | 658         | 858           | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |  |  |  |  |  |

| WREG      | 658         | 858           | xxxx xxxx                          | uuuu uuuu                                                    | uuuu uuuu                       |  |  |  |  |  |

| INDF1     | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| POSTINC1  | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| POSTDEC1  | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| PREINC1   | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

| PLUSW1    | 658         | 858           | N/A                                | N/A                                                          | N/A                             |  |  |  |  |  |

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition **Note 1:** One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

**6:** The long write enable is only reset on a POR or  $\overline{\text{MCLR}}$ .

7: Available on PIC18C858 only.

| Filename             | Bit 7          | Bit 6                | Bit 5          | Bit 4           | Bit 3           | Bit 2       | Bit 1      | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS <sup>(3)</sup> |

|----------------------|----------------|----------------------|----------------|-----------------|-----------------|-------------|------------|---------|-------------------------|------------------------------------------------|

| LATJ <sup>(4)</sup>  | Read PORTJ     |                      | xxxx xxxx      | uuuu uuuu       |                 |             |            |         |                         |                                                |

| LATH <sup>(4)</sup>  | Read PORTH     | xxxx xxxx            | uuuu uuuu      |                 |                 |             |            |         |                         |                                                |

| LATG                 | _              | _                    |                | Read PORTG      | B Data Latch,   | Write PORTG | Data Latch |         | x xxxx                  | u uuuu                                         |

| LATF                 | Read PORTF     | Data Latch, W        | /rite PORTF Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATE                 | Read PORTE     | Data Latch, W        | /rite PORTE Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATD                 | Read PORTD     | Data Latch, W        | /rite PORTD Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATC                 | Read PORTC     | Data Latch, W        | /rite PORTC Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATB                 | Read PORTB     | Data Latch, W        | /rite PORTB Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATA                 | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | Data Latch, Wr  | ite PORTA Da    | ata Latch   |            |         | xx xxxx                 | uu uuuu                                        |

| PORTJ <sup>(4)</sup> | Read PORTJ     | pins, Write PC       | RTJ Data Latch | ı               |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTH <sup>(4)</sup> | Read PORTH     | l pins, Write PO     | ORTH Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTG                | _              | _                    |                | Read PORTO      | 6 pins, Write F | ORTG Data L | .atch      |         | x xxxx                  | uuuu uuuu                                      |

| PORTF                | Read PORTF     | pins, Write PC       | ORTF Data Latc | h               |                 |             |            |         | 0000 0000               | 0000 0000                                      |

| PORTE                | Read PORTE     | pins, Write PC       | ORTE Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTD                | Read PORTD     | pins, Write PC       | ORTD Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTC                | Read PORTC     | pins, Write PO       | ORTC Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTB                | Read PORTB     | pins, Write PC       | ORTB Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTA                | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | pins, Write POI | RTA Data Late   | ch          |            |         | 0x 0000                 | 0u 0000                                        |

| TRISK <sup>(4)</sup> | Data Directior | n Control Regis      | ster for PORTK |                 |                 |             |            |         | 1111 1111               | 1111 1111                                      |

| LATK <sup>(4)</sup>  | Read PORTK     | Data Latch, W        | /rite PORTK Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTK <sup>(4)</sup> | Read PORTK     | pins, Write PC       | ORTK Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| TXERRCNT             | TEC7           | TEC6                 | TEC5           | TEC4            | TEC3            | TEC2        | TEC1       | TEC0    | 0000 0000               | 0000 0000                                      |

| RXERRCNT             | REC7           | REC6                 | REC5           | REC4            | REC3            | REC2        | REC1       | REC0    | 0000 0000               | 0000 0000                                      |

| COMSTAT              | RXB00VFL       | RXB10VFL             | TXBO           | TXBP            | RXBP            | TXWARN      | RXWARN     | EWARN   | 0000 0000               | 0000 0000                                      |

| CIOCON               | TX1SRC         | TX1EN                | ENDRHI         | CANCAP          | —               | —           | —          | —       | 1000                    | 1000                                           |

| BRGCON3              | —              | WAKFIL               | —              | —               | —               | SEG2PH2     | SEG2PH1    | SEG2PH0 | -0000                   | -0000                                          |

| BRGCON2              | SEG2PHTS       | SAM                  | SEG1PH2        | SEG1PH1         | SEG1PH0         | PRSEG2      | PRSEG1     | PRSEG0  | 0000 0000               | 0000 0000                                      |

| BRGCON1              | SJW1           | SJW0                 | BRP5           | BRP4            | BRP3            | BRP2        | BRP1       | BRP0    | 0000 0000               | 0000 0000                                      |

| CANCON               | REQOP2         | REQOP1               | REQOP0         | ABAT            | WIN2            | WIN1        | WIN0       | _       | xxxx xxx-               | uuuu uuu-                                      |

| CANSTAT              | OPMODE2        | OPMODE1              | OPMODE0        | —               | ICODE2          | ICODE1      | ICOED0     | _       | xxx- xxx-               | uuu- uuu-                                      |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: Other (non-power-up) RESETs include external RESET through MCLR and Watchdog Timer Reset.

4: These registers are reserved on PIC18C658.

|      |       | R/W-1                          | R/W-1          | R/W-1           | R/W-1           | R/W-1        | R/W-1  | R/W-1  | R/W-1  |  |  |  |

|------|-------|--------------------------------|----------------|-----------------|-----------------|--------------|--------|--------|--------|--|--|--|

| IPR1 |       | PSPIP                          | ADIP           | RCIP            | TXIP            | SSPIP        | CCP1IP | TMR2IP | TMR1IP |  |  |  |

|      |       | bit 7                          |                |                 |                 |              |        |        | bit 0  |  |  |  |

|      |       |                                |                |                 |                 |              |        |        |        |  |  |  |

|      |       | U-0                            | R/W-1          | U-0             | U-0             | R/W-1        | R/W-1  | R/W-1  | R/W-1  |  |  |  |

| IPR2 |       | _                              | CMIP           | —               |                 | BCLIP        | LVDIP  | TMR3IP | CCP2IP |  |  |  |

|      |       | bit 7                          |                |                 |                 |              |        |        | bit 0  |  |  |  |

|      |       | R/W-1                          | R/W-1          | R/W-1           | R/W-1           | R/W-1        | R/W-1  | R/W-1  | R/W-1  |  |  |  |

| IPR3 |       | IVRP                           | WAKIP          | ERRIP           | TXB2IP          | TXB1IP       | TXB0IP | RXB1IP | RXB0IP |  |  |  |

|      |       | bit 7                          |                |                 |                 |              |        |        | bit 0  |  |  |  |

|      |       |                                |                |                 |                 |              |        |        |        |  |  |  |

|      |       |                                |                |                 |                 |              |        |        |        |  |  |  |

| IPR1 | bit 7 | <b>PSPIP:</b> Pa<br>1 = High p | rallel Slave P | ort Read/Wr     | ite Interrupt I | Priority bit |        |        |        |  |  |  |

|      |       | 1 = 1  light  p<br>0 = Low pi  | •              |                 |                 |              |        |        |        |  |  |  |

|      | bit 6 | -                              | Converter Int  | errupt Priori   | ty bit          |              |        |        |        |  |  |  |

|      |       | 1 = High p                     |                |                 |                 |              |        |        |        |  |  |  |

|      |       | 0 = Low pr                     | •              |                 |                 |              |        |        |        |  |  |  |

|      | bit 5 | 1 = High p                     | RT Receive     | Interrupt Pric  | ority bit       |              |        |        |        |  |  |  |

|      |       | 0 = Low pr                     |                |                 |                 |              |        |        |        |  |  |  |

|      | bit 4 |                                | RT Transmit    | Interrupt Price | ority bit       |              |        |        |        |  |  |  |

|      |       | 1 = High p                     | •              |                 |                 |              |        |        |        |  |  |  |

|      | bit 3 |                                | ster Synchro   | noue Sorial I   | Dort Interrupt  | Driority hit |        |        |        |  |  |  |

|      | DIL 3 | 1 = High p                     |                | nous Senai i    |                 |              |        |        |        |  |  |  |

|      |       | 0 = Low pr                     |                |                 |                 |              |        |        |        |  |  |  |

|      | bit 2 |                                | CP1 Interrup   | t Priority bit  |                 |              |        |        |        |  |  |  |

|      |       | 1 = High p<br>0 = Low pi       |                |                 |                 |              |        |        |        |  |  |  |

|      | bit 1 | •                              | MR2 to PR2     | Match Interr    | upt Priority b  | t            |        |        |        |  |  |  |

|      |       | 1 = High p                     | riority        |                 |                 | -            |        |        |        |  |  |  |

|      |       | 0 = Low pr                     | -              |                 |                 |              |        |        |        |  |  |  |

|      | bit 0 |                                | MR1 Overflov   | w Interrupt P   | riority bit     |              |        |        |        |  |  |  |

|      |       | 1 = High p<br>0 = Low pi       | ,              |                 |                 |              |        |        |        |  |  |  |

|      |       | r                              | ,              |                 |                 |              |        |        |        |  |  |  |

# REGISTER 7-7: IPR REGISTERS

| Name             | Bit# | Buffer Type | Function                                                                                              |

|------------------|------|-------------|-------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T13CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1/Timer3 clock input.                       |

| RC1/T1OSI        | bit1 | ST          | Input/output port pin or Timer1 oscillator input.                                                     |

| RC2/CCP1         | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                  |

| RC3/SCK/SCL      | bit3 | ST          | Input/output port pin or Synchronous Serial clock for SPI/I <sup>2</sup> C.                           |

| RC4/SDI/SDA      | bit4 | ST          | Input/output port pin or SPI Data in (SPI mode) or Data I/O (I <sup>2</sup> C mode).                  |

| RC5/SDO          | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                         |

| RC6/TX/CK        | bit6 | ST          | Input/output port pin Addressable USART Asynchronous Transmit or Addressable USART Synchronous Clock. |

| RC7/RX/DT        | bit7 | ST          | Input/output port pin Addressable USART Asynchronous Receive or Addressable USART Synchronous Data.   |

# TABLE 8-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6     | Bit 5      | Bit 4     | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|--------|-----------|------------|-----------|-----------|-----------|-------|-------|-------------------------|---------------------------------|

| PORTC | RC7    | RC6       | RC5        | RC4       | RC3       | RC2       | RC1   | RC0   | xxxx xxxx               | uuuu uuuu                       |

| LATC  | LATC D | ata Outpu |            | xxxx xxxx | uuuu uuuu |           |       |       |                         |                                 |

| TRISC | PORTC  | Data Dire | ection Reg |           | 1111 1111 | 1111 1111 |       |       |                         |                                 |

Legend: x = unknown, u = unchanged

# 10.0 TIMER0 MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/counter

- Readable and writable

- Dedicated 8-bit software programmable prescaler

- Clock source selectable to be external or internal

- Interrupt on overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

# REGISTER 10-1: TOCON REGISTER

Register 10-1 shows the Timer0 Control register (T0CON).

Figure 10-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 10-1 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The TOCON register is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

**Note:** Timer0 is enabled on POR.

|         | R/W-1                                                                             | R/W-1                                                                                                                                                       | R/W-1                    | R/W-1         | R/W-1      | R/W-1      | R/W-1         | R/W-1 |  |  |  |  |

|---------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|------------|------------|---------------|-------|--|--|--|--|

|         | TMR0ON                                                                            | T08BIT                                                                                                                                                      | TOCS                     | TOSE          | PSA        | T0PS2      | T0PS1         | T0PS0 |  |  |  |  |

|         | bit 7                                                                             |                                                                                                                                                             |                          |               |            |            |               | bit 0 |  |  |  |  |

| bit 7   | <b>TMR0ON:</b> T<br>1 = Enables<br>0 = Stops Ti                                   |                                                                                                                                                             | Control bit              |               |            |            |               |       |  |  |  |  |

| bit 6   | 1 = Timer0 i                                                                      | 08BIT: Timer0 8-bit/16-bit Control bit<br>= Timer0 is configured as an 8-bit timer/counter<br>= Timer0 is configured as a 16-bit timer/counter              |                          |               |            |            |               |       |  |  |  |  |

| bit 5   | 1 = Transitio                                                                     | <b>0CS</b> : Timer0 Clock Source Select bit<br>= Transition on T0CKI pin<br>= Internal instruction cycle clock (CLKOUT)                                     |                          |               |            |            |               |       |  |  |  |  |

| bit 4   | 1 = Increme                                                                       | <b>TOSE</b> : Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                          |               |            |            |               |       |  |  |  |  |

| bit 3   | ן TImer0 I = T                                                                    | ) Prescaler A<br>prescaler is N<br>prescaler is a                                                                                                           | IOT assigned             | d. Timer0 clo |            |            |               |       |  |  |  |  |

| bit 2-0 | T0PS2:T0P                                                                         | <b>S0</b> : Timer0 P                                                                                                                                        | rescaler Sele            | ect bits      |            |            |               |       |  |  |  |  |

|         | 110 = 1:128<br>101 = 1:64<br>100 = 1:32<br>011 = 1:16<br>010 = 1:8  <br>001 = 1:4 | prescale val<br>prescale val<br>prescale val<br>prescale val<br>prescale val<br>prescale val<br>prescale val<br>prescale val<br>prescale val                | ue<br>ie<br>ie<br>e<br>e |               |            |            |               |       |  |  |  |  |

|         | Logondi                                                                           |                                                                                                                                                             |                          |               |            |            |               | ]     |  |  |  |  |

|         | Legend:<br>R = Readab                                                             | le hit                                                                                                                                                      | W = Writ                 | ahla hit      | II – Unimp | lamantad h | it, read as ' | n'    |  |  |  |  |

|         | r = readab                                                                        |                                                                                                                                                             | vv = vvrit               | anie ni       | o = ommp   |            | in, reau as t | J     |  |  |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|--------------------|------------------|----------------------|--------------------|

|                    |                  |                      |                    |

|                    |                  |                      |                    |

### 14.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### 14.2 CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

TABLE 14-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer1 or Timer3 |

| PWM      | Timer2           |

### 14.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR registers) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 14.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### 14.3.2 TIMER1/TIMER3 MODE SELECTION

The timers used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer used with each CCP module is selected in the T3CON register.

#### TABLE 14-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                                                                              |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | TMR1 or TMR3 time-base. Time-base can be different for each CCP.                                                                         |

| Capture   | Compare   | The compare could be configured for the special event trigger, which clears either TMR1 or TMR3, depending upon which time-base is used. |

| Compare   | Compare   | The compare(s) could be configured for the special event trigger, which clears TMR1 or TMR3 depending upon which time-base is used.      |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                  |

| PWM       | Capture   | None                                                                                                                                     |

| PWM       | Compare   | None                                                                                                                                     |

#### 16.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA register). In addition, enable bit SPEN (RCSTA register) is set, in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA register).

#### 16.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 16-1. The heart of the transmitter is the Transmit (serial) Shift register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register (TXREG). The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG is empty and interrupt bit TXIF (PIR registers) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE registers). Flag bit TXIF will be set, regardless of the state of enable bit TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA register) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 16.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

| Name   | Bit 7                   | Bit 6        | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------------------------|--------------|---------|--------|-------|--------|--------|--------|-------------------------|---------------------------------|

| INTCON | GIE/GIEH                | PEIE/GIEL    | TMR0IE  | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | x000 000x               | 0000 000u                       |

| PIR1   | PSPIF                   | ADIF         | RCIF    | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| PIE1   | PSPIE                   | ADIE         | RCIE    | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| IPR1   | PSPIP                   | ADIP         | RCIP    | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000 0000               | 0000 0000                       |

| RCSTA  | SPEN                    | RX9          | SREN    | CREN   |       | FERR   | OERR   | RX9D   | x00- 0000               | 0000 -00x                       |

| TXREG  | USART Transmit Register |              |         |        |       |        |        |        |                         | 0000 0000                       |

| TXSTA  | CSRC                    | TX9          | TXEN    | SYNC   | ADDEN | BRGH   | TRMT   | TX9D   | 0000 0010               | 0000 0010                       |

| SPBRG  | Baud Rate               | Generator Re | egister | -      | -     |        |        |        | 0000 0000               | 0000 0000                       |

### TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

NOTES:

#### 17.2.5 CAN BAUD RATE REGISTERS

This subsection describes the CAN Baud Rate registers.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 BRP0 SJW1 SJW0 BRP5 BRP4 BRP3 BRP2 BRP1 bit 7 bit 0 bit 7-6 SJW1:SJW0: Synchronized Jump Width bits 11 = Synchronization Jump Width Time = $4 \times TQ$ 10 = Synchronization Jump Width Time = $3 \times TQ$ 01 = Synchronization Jump Width Time = $2 \times TQ$ 00 = Synchronization Jump Width Time = 1 x TQ bit 5-0 BRP5:BRP0: Baud Rate Prescaler bits 111111 = TQ = (2 x 64)/FOSC 111110 = TQ = (2 x 63)/FOSC 000001 = TQ = (2 x 2)/FOSC 000000 = Tq = (2 x 1)/Fosc Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### REGISTER 17-29: BRGCON1 – BAUD RATE CONTROL REGISTER 1

Note: This register is only accessible in Configuration mode.

#### 17.9 Programming Time Segments

Some requirements for programming of the time segments:

- Prop Seg + Phase Seg  $1 \ge$  Phase Seg 2

- Phase Seg  $2 \ge$  Sync Jump Width

For example, assuming that a 125 kHz CAN baud rate with FOSC = 20 MHz is desired:

Tosc = 50nsec, choose BRP<5:0> = 04h, then TQ = 500nsec. To obtain 125 kHz, the bit time must be 16 TQ.

Sync Seg = 1 TQ; Prop Seg = 2 TQ; So, setting Phase Seg 1 = 7 TQ would place the sample at 10 TQ after the transition. This would leave 6 TQ for Phase Seg 2.

Since Phase Seg 2 is 6, by the rules, SJW could be the maximum of 4 Tq. However, normally a large SJW is only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. So an SJW of 1 is typically enough.

#### 17.10 Oscillator Tolerance

The bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 kbit/sec, as a rule of thumb. For the full bus speed range of the CAN protocol, a quartz oscillator is required. A maximum node-to-node oscillator variation of 1.7% is allowed.

#### 17.11 Bit Timing Configuration Registers

The configuration registers (BRGCON1, BRGCON2, BRGCON3) control the bit timing for the CAN bus interface. These registers can only be modified when the PIC18CXX8 is in Configuration mode.

#### 17.11.1 BRGCON1

The BRP bits control the baud rate prescaler. The SJW < 1:0 > bits select the synchronization jump width in terms of number of Tq's.

#### 17.11.2 BRGCON2

The PRSEG bits set the length, in To's, of the propagation seament. The SEG1PH bits set the length, in TQ's. of phase segment 1. The SAM bit controls how many times the RXCAN pin is sampled. Setting this bit to a '1' causes the bus to be sampled three times; twice at TQ/2 before the sample point, and once at the normal sample point (which is at the end of phase segment 1). The value of the bus is determined to be the value read during at least two of the samples. If the SAM bit is set to a '0', then the RXCAN pin is sampled only once at the sample point. The SEG2PHTS bit controls how the length of phase segment 2 is determined. If this bit is set to a '1', then the length of phase segment 2 is determined by the SEG2PH bits of BRGCON3. If the SEG2PHTS bit is set to a '0', then the length of phase segment 2 is the greater of phase segment 1 and the information processing time (which is fixed at 2 TQ for the PIC18CXX8).

#### 17.11.3 BRGCON3

The PHSEG2<2:0> bits set the length, in TQ's, of phase segment 2, if the SEG2PHTS bit is set to a '1'. If the SEG2PHTS bit is set to a '0', then the PHSEG2<2:0> bits have no effect.

x = Bit is unknown

### **REGISTER 18-3: ADCON2 REGISTER**

- n = Value at POR

|         | R/W-0            | U-0          | U-0          | U-0           | U-0        | R/W-0      | R/W-0          | R/W-0 |

|---------|------------------|--------------|--------------|---------------|------------|------------|----------------|-------|

|         | ADFM             | —            | —            | —             | —          | ADCS2      | ADCS1          | ADCS0 |

|         | bit 7            |              |              |               |            |            |                | bit 0 |

|         |                  |              |              |               |            |            |                |       |

| bit 7   |                  |              | mat Select b | oit           |            |            |                |       |

|         | 1 = Right ju     |              |              |               |            |            |                |       |

|         | 0 = Left jus     | stified      |              |               |            |            |                |       |

| bit 6-3 | Unimplem         | ented: Rea   | d as '0'     |               |            |            |                |       |

| bit 2-0 | ADCS1:AD         | DCS0: A/D (  | Conversion C | Clock Select  | bits       |            |                |       |

|         | 000 = Fos        | c/2          |              |               |            |            |                |       |

|         | 001 = FOS        | C/8          |              |               |            |            |                |       |

|         | 010 = FOS        | c/32         |              |               |            |            |                |       |

|         | 011 = FRC        | (clock deriv | ed from an F | RC oscillator | = 1 MHz ma | ax)        |                |       |

|         | 100 = FOS        | c/4          |              |               |            |            |                |       |

|         | 101 <b>= Fos</b> | c/16         |              |               |            |            |                |       |

|         | 110 = FOS        | c/64         |              |               |            |            |                |       |

|         | 111 = FRC        | (clock deriv | ed from an F | RC oscillator | = 1 MHz ma | ax)        |                |       |

|         | _                |              |              |               |            |            |                |       |

|         | Legend:          |              |              |               |            |            |                |       |

|         | R = Readal       | ble bit      | W = W        | /ritable bit  | U = Unin   | nplemented | bit, read as ' | 0'    |

'0' = Bit is cleared

'1' = Bit is set

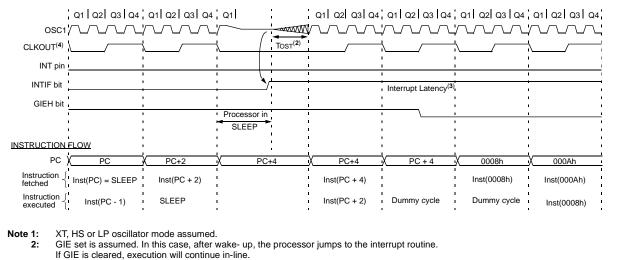

#### 22.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overrightarrow{PD}$  bit. If the  $\overrightarrow{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# FIGURE 22-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT<sup>(1,2)</sup>

3: TOST = 1024TOSC (drawing not to scale). This delay will not occur for RC and EC osc modes.

4: CLKOUT is not available in these oscillator modes, but shown here for timing reference.

#### 24.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F877 and can be used to develop this and other PICmicro microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the incircuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost effective in-circuit FLASH programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB ICD is also a programmer for the FLASH PIC16F87X family.

#### 24.9 <u>PRO MATE II Universal Device</u> <u>Programmer</u>

The PRO MATE II universal device programmer is a full featured programmer, capable of operating in standalone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PICmicro devices. It can also set code-protect bits in this mode.

# 24.10 <u>PICSTART Plus Entry Level</u> <u>Development Programmer</u>

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PICmicro devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 24.11 <u>PICDEM 1 Low Cost PICmicro</u> <u>Demonstration Board</u>

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 24.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

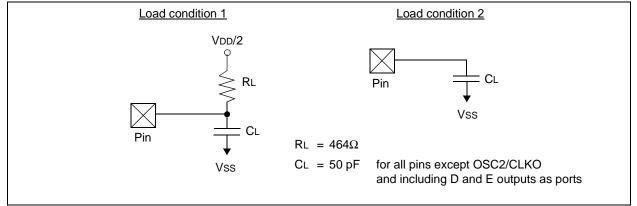

#### 25.3.2 TIMING CONDITIONS

The temperature and voltages specified in Table 25-3 apply to all timing specifications, unless otherwise noted. Figure 25-4 specifies the load conditions for the timing specifications.

#### TABLE 25-3: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions (unless otherwise stated)                       |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------|--|--|--|--|

|                    | Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial |  |  |  |  |

| AC CHARACTERISTICS | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended                        |  |  |  |  |

|                    | Operating voltage VDD range as described in DC spec Section 25.1.             |  |  |  |  |

|                    | LC parts operate for industrial temperatures only.                            |  |  |  |  |

# FIGURE 25-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

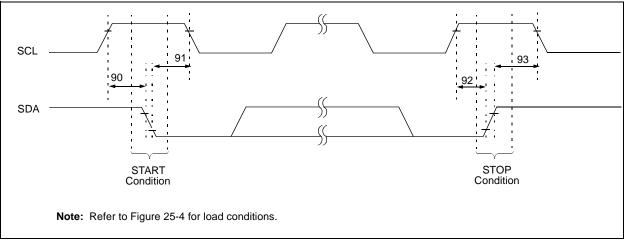

# FIGURE 25-16: I<sup>2</sup>C BUS START/STOP BITS TIMING

# TABLE 25-15: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Parm.<br>No. | Symbol  | Characteristic  |                | Min  | Max | Units | Conditions                   |  |

|--------------|---------|-----------------|----------------|------|-----|-------|------------------------------|--|

| 90           | TSU:STA | START condition | 100 kHz møde 🖒 | 4700 |     | ns    | Only relevant for Repeated   |  |

|              |         | Setup time      | 400 kHz mode   | 600  | —   |       | START condition              |  |

| 91           | THD:STA | START condition | 100 MHZ mode   | 4000 | _   | ns    | After this period, the first |  |

|              |         | Hold time       | 400 kHz mode   | 600  |     |       | clock pulse is generated     |  |

| 92           | TSU:STO | STOP condition  | 100 kHz mode   | 4700 |     | ns    |                              |  |

|              |         | Setup time      | 400 kHz mode   | 600  | _   |       |                              |  |

| 93           | THD:STO | STOReprodution  | 100 kHz mode   | 4000 | _   | ns    |                              |  |

|              |         | Hold time       | 400 kHz mode   | 600  | _   |       |                              |  |

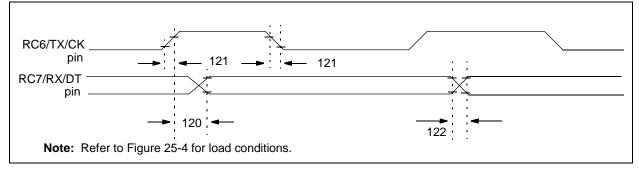

#### FIGURE 25-20: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 25-19: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                    | B                   | Min | Мах | Units | Conditions |

|---------------|----------|-----------------------------------|---------------------|-----|-----|-------|------------|

| 120           | TckH2dtV | SYNC XMIT (Master & Slave)        | A L                 |     |     |       |            |

|               |          | Clock high to data-out valid      | PIC18 <b>C</b> XX8  | —   | 40  | ns    |            |

|               |          | nTMULL                            | PIC18 <b>LC</b> XX8 | _   | 100 | ns    |            |

| 121           | Tckrf    | Clock out rise time and fall time | PIC18 <b>C</b> XX8  | _   | 20  | ns    |            |

|               |          |                                   | PIC18 <b>LC</b> XX8 | _   | 50  | ns    |            |

| 122           | Tdtrf    | Data-out rise time and fall time  | PIC18 <b>C</b> XX8  | —   | 20  | ns    |            |

|               |          | ×                                 | PIC18 <b>LC</b> XX8 | _   | 50  | ns    |            |

| SSPOV                            |          |

|----------------------------------|----------|

| SSPSTAT                          |          |

| SSPSTAT Register                 |          |

| R/ <del>W</del> Bit              | 148, 149 |

| Stuff Error                      |          |

| SUBLW                            |          |

| SUBWF                            | 297, 298 |

| SUBWFB                           |          |

| SWAPF                            |          |

| Synchronization                  |          |

| Synchronization Rules            |          |

| Synchronization Segment          | 219      |

| Synchronous Serial Port. See SSP |          |

# Т

| TABLRD                                               |

|------------------------------------------------------|

| TABLWT                                               |

| Time Quanta219                                       |

| Timer Modules                                        |

| Timer3                                               |

| Block Diagram124                                     |

| Timer0                                               |

| Clock Source Edge Select (T0SE Bit)                  |

| Clock Source Select (T0CS Bit)                       |

| Overflow Interrupt                                   |

| Prescaler. See Prescaler, Timer0                     |

| Timing Diagram                                       |

| Timer1                                               |

| Block Diagram                                        |

| Oscillator                                           |

| Overflow Interrupt                                   |

| Prescaler. See Prescaler, Timer1                     |

|                                                      |

| Special Event Trigger (CCP)                          |

| Timing Diagram                                       |

| TMR1H Register                                       |

| TMR1L Register                                       |

| TMR3L Register                                       |

| Timer2                                               |

| Block Diagram                                        |

| Postscaler. See Postscaler, Timer2                   |

| PR2 Register                                         |

| Prescaler. See Prescaler, Timer2                     |

| SSP Clock Shift                                      |

| TMR2 Register                                        |

| TMR2 to PR2 Match Interrupt 121, 122, 132            |

| Timer3                                               |

| Oscillator123, 125                                   |

| Overflow Interrupt123, 125                           |

| Special Event Trigger (CCP) 125                      |

| TMR3H Register123                                    |

| Timing Diagrams                                      |

| Acknowledge Sequence Timing159                       |

| Baud Rate Generator with Clock Arbitration           |

| BRG Reset Due to SDA Collision164                    |

| Bus Collision                                        |

| START Condition Timing163                            |

| Bus Collision During a RESTART Condition             |

| (Case 1)165                                          |

| Bus Collision During a RESTART Condition             |

| (Case2)165                                           |

| Bus Collision During a START Condition (SCL = 0) 164 |

| Bus Collision During a STOP Condition                |

| Bus Collision for Transmit and Acknowledge 162       |

| I <sup>2</sup> C Bus Data                            |

| I <sup>2</sup> C Master Mode First Start bit timing  |

| I <sup>2</sup> C Master Mode Reception timing        |

| I <sup>2</sup> C Master Mode Transmission timing     |

| -                                                    |

| Master Mode Transmit Clock Arbitration            |

|---------------------------------------------------|

| Repeat Start Condition155                         |

| Slave Synchronization144                          |

| Slow Rise Time                                    |

| SPI Mode Timing (Master Mode) SPI Mode            |

| Master Mode Timing Diagram                        |

| SPI Mode Timing (Slave Mode with CKE = 0) 145     |

| SPI Mode Timing (Slave Mode with CKE = 1) 145     |

| Stop Condition Receive or Transmit                |

| Time-out Sequence on Power-up                     |

| USART Asynchronous Master Transmission 174        |

| USART Asynchronous Reception 176                  |

| USART Synchronous Reception                       |

| USART Synchronous Transmission                    |

| Wake-up from SLEEP via Interrupt                  |

| Timing Diagrams and Specifications                |

| A/D Conversion                                    |

| Brown-out Reset (BOR) 325                         |

| Capture/Compare/PWM (CCP)                         |

| CLKOUT and I/O 324                                |

| External Clock 322                                |

| I <sup>2</sup> C Bus Data                         |

| I <sup>2</sup> C Bus START/STOP Bits              |

| Oscillator Start-up Timer (OST) 325               |

| Parallel Slave Port (PSP) 328                     |

| Power-up Timer (PWRT) 325                         |

| Reset                                             |

| Timer0 and Timer1 326                             |

| USART Synchronous Receive (Master/Slave) 338      |

| USART Synchronous Transmission (Master/Slave) 337 |

| Watchdog Timer (WDT) 325                          |

| Transmit Interrupt 225                            |

| Transmit Message Aborting 211                     |

| Transmit Message Buffering                        |

| Transmit Message Buffers                          |

| Transmit Message flowchart                        |

| Transmit Message Priority                         |

| Transmitter Error Passive                         |

| Transmitter Warning                               |

| TRISE Register                                    |

| TSTFSZ                                            |

| TXSTA Register                                    |

| BRGH Bit 169                                      |

# U

Universal Synchronous Asynchronous Receiver Transmitter. See USART

| USART 167                                    |

|----------------------------------------------|

| Asynchronous Mode 173                        |

| Master Transmission 174                      |

| Receive Block Diagram 175                    |

| Reception176                                 |

| Transmit Block Diagram 173                   |

| Baud Rate Generator (BRG) 169                |

| Baud Rate Error, Calculating                 |

| Baud Rate Formula 169                        |

| High Baud Rate Select (BRGH Bit) 169         |

| Sampling 169                                 |

| Serial Port Enable (SPEN Bit) 167            |

| Synchronous Master Mode 177                  |

| Reception179                                 |

| Timing Diagram, Synchronous Receive          |

| Timing Diagram, Synchronous Transmission 337 |

| Transmission178                              |

| Synchronous Slave Mode 180                   |

|                                              |

NOTES:

# WORLDWIDE SALES AND SERVICE

## AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3838 Fax: 978-692-3821

Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Dayton Two Prestige Place, Suite 130 Miamisburg, OH 45342

Tel: 937-291-1654 Fax: 937-291-9175 Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

Los Angeles 18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

San Jose Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto 6285 Northam Drive, Suite 108

Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

# ASIA/PACIFIC

China - Beijing Microchip Technology Beijing Office Unit 915 New China Hong Kong Manhattan Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

China - Shanghai Microchip Technology Shanghai Office Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

Hong Kong

Microchip Asia Pacific RM 2101, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 India Microchip Technology Inc. India Liaison Office

**Divyasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062 Japan Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934

# **ASIA/PACIFIC** (continued)

Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139 EUROPE

#### Denmark

Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Arizona Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy Arizona Microchip Technology SRL Centro Direzionale Colleoni

Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883 United Kingdom Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU

Tel: 44 118 921 5869 Fax: 44-118 921-5820

10/01/00

Microchip received QS-9000 quality system certification for its worldwide headquarters design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro<sup>®</sup> 8-bit MCUs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

All rights reserved. © 2000 Microchip Technology Incorporated. Printed in the USA. 11/00 🤹 Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, except as maybe explicitly expressed herein, under any intellectual trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.

Advanced Information