Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc658t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

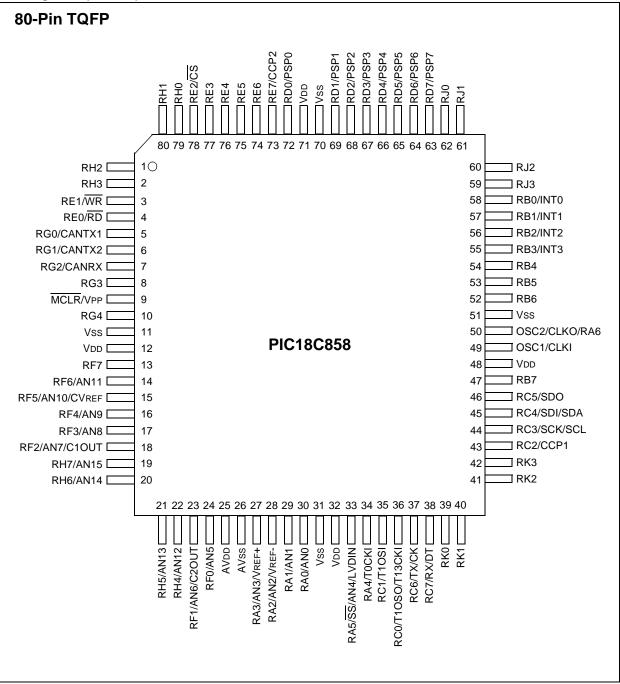

### Pin Diagrams (Cont.'d)

# 3.0 RESET

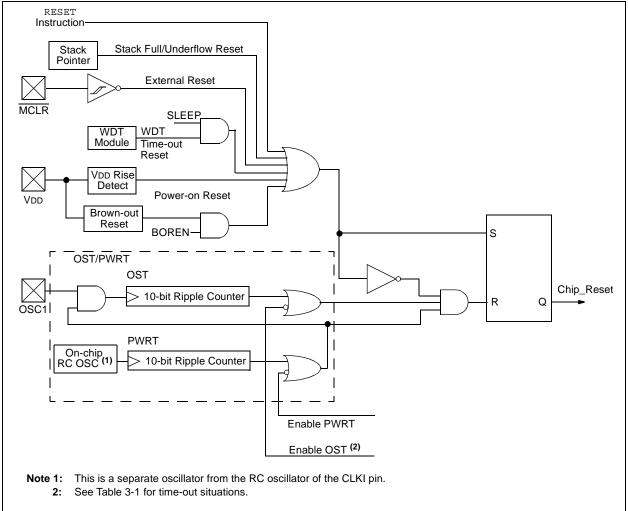

The PIC18CXX8 differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (PBOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETs. The other registers are forced to a "RESET" state on Power-on Reset, MCLR, WDT Reset, Brown-out Reset, MCLR Reset during SLEEP and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 3-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

A WDT Reset does not drive MCLR pin low.

### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 4-4 shows the data memory organization for the PIC18CXX8 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFR's are used for control and status of the controller and peripheral functions, while GPR's are used for data storage and scratch pad operations in the user's application. The SFR's start at the last location of Bank 15 (0xFFF) and grow downwards. GPR's start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of the File Select Register (FSR). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two word/two cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFR's and select GPR's) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates through the File Select Registers (FSR). The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPR's are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. Bank 15 (0xF00 to 0xFFF) contains SFR's. All other banks of data memory contain GPR registers starting with bank 0.

### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFR's) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2.

The SFR's can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFR's are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's. See Table 4-2 for addresses for the SFR's.

| Filename             | Bit 7          | Bit 6                | Bit 5          | Bit 4           | Bit 3           | Bit 2       | Bit 1      | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS <sup>(3)</sup> |

|----------------------|----------------|----------------------|----------------|-----------------|-----------------|-------------|------------|---------|-------------------------|------------------------------------------------|

| LATJ <sup>(4)</sup>  | Read PORTJ     | Data Latch, W        | rite PORTJ Dat | a Latch         |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATH <sup>(4)</sup>  | Read PORTH     | Data Latch, W        | /rite PORTH Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATG                 | _              | _                    |                | Read PORTO      | B Data Latch,   | Write PORTG | Data Latch |         | x xxxx                  | u uuuu                                         |

| LATF                 | Read PORTF     | Data Latch, W        | /rite PORTF Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATE                 | Read PORTE     | xxxx xxxx            | uuuu uuuu      |                 |                 |             |            |         |                         |                                                |

| LATD                 | Read PORTD     | Data Latch, W        | /rite PORTD Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATC                 | Read PORTC     | Data Latch, W        | /rite PORTC Da | ata Latch       |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATB                 | Read PORTB     | Data Latch, W        | /rite PORTB Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| LATA                 | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | Data Latch, Wr  | ite PORTA Da    | ata Latch   |            |         | xx xxxx                 | uu uuuu                                        |

| PORTJ <sup>(4)</sup> | Read PORTJ     | pins, Write PC       | RTJ Data Latch | ı               |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTH <sup>(4)</sup> | Read PORTH     | l pins, Write PO     | ORTH Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTG                | _              | _                    |                | Read PORTO      | 6 pins, Write F | ORTG Data L | .atch      |         | x xxxx                  | uuuu uuuu                                      |

| PORTF                | Read PORTF     | pins, Write PC       | ORTF Data Latc | h               |                 |             |            |         | 0000 0000               | 0000 0000                                      |

| PORTE                | Read PORTE     | pins, Write PC       | ORTE Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTD                | Read PORTD     | pins, Write PC       | ORTD Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTC                | Read PORTC     | pins, Write PO       | ORTC Data Late | ch              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTB                | Read PORTB     | pins, Write PC       | ORTB Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTA                | _              | Bit 6 <sup>(1)</sup> | Read PORTA     | pins, Write POI | RTA Data Late   | ch          |            |         | 0x 0000                 | 0u 0000                                        |

| TRISK <sup>(4)</sup> | Data Directior | n Control Regis      | ster for PORTK |                 |                 |             |            |         | 1111 1111               | 1111 1111                                      |

| LATK <sup>(4)</sup>  | Read PORTK     | Data Latch, W        | /rite PORTK Da | ta Latch        |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| PORTK <sup>(4)</sup> | Read PORTK     | pins, Write PC       | ORTK Data Lato | :h              |                 |             |            |         | xxxx xxxx               | uuuu uuuu                                      |

| TXERRCNT             | TEC7           | TEC6                 | TEC5           | TEC4            | TEC3            | TEC2        | TEC1       | TEC0    | 0000 0000               | 0000 0000                                      |

| RXERRCNT             | REC7           | REC6                 | REC5           | REC4            | REC3            | REC2        | REC1       | REC0    | 0000 0000               | 0000 0000                                      |

| COMSTAT              | RXB00VFL       | RXB10VFL             | TXBO           | TXBP            | RXBP            | TXWARN      | RXWARN     | EWARN   | 0000 0000               | 0000 0000                                      |

| CIOCON               | TX1SRC         | TX1EN                | ENDRHI         | CANCAP          | —               | —           | —          | —       | 1000                    | 1000                                           |

| BRGCON3              | —              | WAKFIL               | —              | —               | —               | SEG2PH2     | SEG2PH1    | SEG2PH0 | -0000                   | -0000                                          |

| BRGCON2              | SEG2PHTS       | SAM                  | SEG1PH2        | SEG1PH1         | SEG1PH0         | PRSEG2      | PRSEG1     | PRSEG0  | 0000 0000               | 0000 0000                                      |

| BRGCON1              | SJW1           | SJW0                 | BRP5           | BRP4            | BRP3            | BRP2        | BRP1       | BRP0    | 0000 0000               | 0000 0000                                      |

| CANCON               | REQOP2         | REQOP1               | REQOP0         | ABAT            | WIN2            | WIN1        | WIN0       | _       | xxxx xxx-               | uuuu uuu-                                      |

| CANSTAT              | OPMODE2        | OPMODE1              | OPMODE0        | —               | ICODE2          | ICODE1      | ICOED0     | _       | xxx- xxx-               | uuu- uuu-                                      |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: Other (non-power-up) RESETs include external RESET through MCLR and Watchdog Timer Reset.

4: These registers are reserved on PIC18C658.

### REGISTER 7-2: INTCON2 REGISTER

|      | R/W-1                                                                                                                                                           | R/W-1                                                                                                          | R/W-1          | R/W-1       | R/W-1          | R/W-1      | R/W-1        | R/W-1  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|-------------|----------------|------------|--------------|--------|--|--|--|

|      | RBPU                                                                                                                                                            | INTEDG0                                                                                                        | INTEDG1        | INTEDG2     | INTEDG3        | TMR0IP     | INT3IP       | RBIP   |  |  |  |

|      | bit 7                                                                                                                                                           |                                                                                                                |                |             |                |            |              | bit 0  |  |  |  |

| it 7 | 1 = All PO                                                                                                                                                      | RTB Pull-up I<br>RTB pull-ups<br>B pull-ups are                                                                | are disabled   |             | ort latch valu | es         |              |        |  |  |  |

| it 6 | INTEDG0: External Interrupt 0 Edge Select bit<br>1 = Interrupt on rising edge<br>0 = Interrupt on falling edge<br>INTEDG1: External Interrupt 1 Edge Select bit |                                                                                                                |                |             |                |            |              |        |  |  |  |

| it 5 | 1 = Interru                                                                                                                                                     | INTEDG1: External Interrupt 1 Edge Select bit<br>1 = Interrupt on rising edge<br>0 = Interrupt on falling edge |                |             |                |            |              |        |  |  |  |

| it 4 | 1 = Interru                                                                                                                                                     | External Inter<br>pt on rising e<br>pt on falling e                                                            | dge            | Select bit  |                |            |              |        |  |  |  |

| it 3 | 1 = Interru                                                                                                                                                     | External Inte<br>pt on rising e<br>pt on falling e                                                             | dge            | Select bit  |                |            |              |        |  |  |  |

| it 2 | <b>TMR0IP</b> : T<br>1 = High p<br>0 = Low p                                                                                                                    | ,                                                                                                              | w Interrupt P  | riority bit |                |            |              |        |  |  |  |

| it 1 | INT3IP: IN<br>1 = High (<br>0 = Low p                                                                                                                           | •                                                                                                              | nterrupt Prior | ity bit     |                |            |              |        |  |  |  |

| it O | <b>RBIP</b> : RB  <br>1 = High  <br>0 = Low p                                                                                                                   | •                                                                                                              | Interrupt Pric | rity bit    |                |            |              |        |  |  |  |

|      | Legend:                                                                                                                                                         |                                                                                                                |                |             |                |            |              |        |  |  |  |

|      | R = Reada                                                                                                                                                       | ble bit                                                                                                        | W = Wri        | table bit   | U = Unimp      | lemented l | oit, read as | '0'    |  |  |  |

|      | - n = Value                                                                                                                                                     | at POR                                                                                                         | '1' = Bit      | is set      | '0' = Bit is o | cleared    | x = Bit is u | nknown |  |  |  |

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

bit 5

### REGISTER 9-1: PSPCON REGISTER

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|---------|-----|-----|-----|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | —   |     | _     |

| bit 7 |     |       |         |     |     |     | bit 0 |

bit 7 **IBF:** Input Buffer Full Status bit

1 = A word has been received and waiting to be read by the CPU

0 = No word has been received

- bit 6 **OBF**: Output Buffer Full Status bit

- 1 = The output buffer still holds a previously written word

- 0 = The output buffer has been read

- **IBOV**: Input Buffer Overflow Detect bit (in Microprocessor mode)

- 1 = A write occurred when a previously input word has not been read (must be cleared in software)

- 0 = No overflow occurred

bit 4 **PSPMODE**: Parallel Slave Port Mode Select bit

- 1 = Parallel Slave Port mode

- 0 = General purpose I/O mode

- bit 3-0 Unimplemented: Read as '0'

| Legend             |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

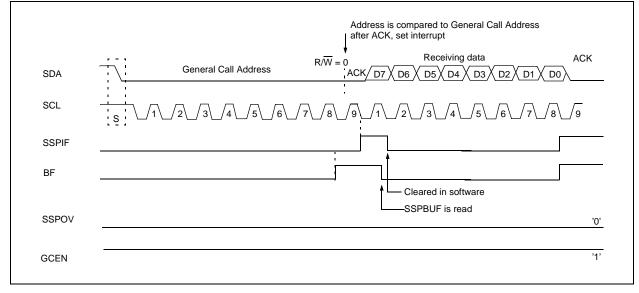

#### 15.4.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0.

The general call address is recognized (enabled) when the General Call Enable (GCEN) bit is set (SSPCON2 register). Following a START bit detect, eight bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware. If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT register). If the general call address is sampled when the GCEN bit is set, and while the slave is configured in 10-bit address mode; then, the second half of the address is not necessary. The UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 15-9).

### FIGURE 15-9: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT ADDRESS)

#### 15.4.3 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge Transmit

- · Repeated START condition

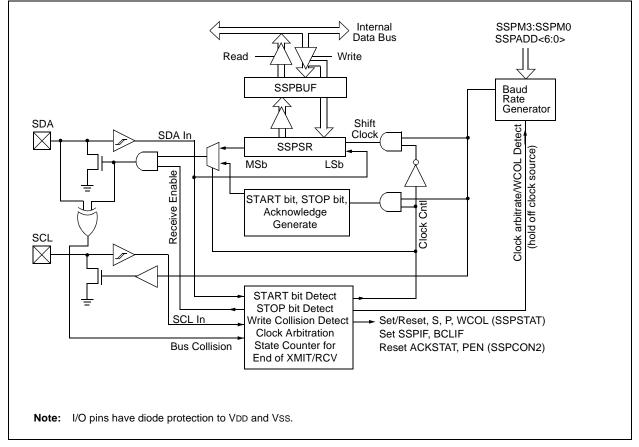

### 15.4.4 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. Once Master mode is enabled, the user has the following six options:

- 1. Assert a START condition on SDA and SCL.

- 2. Assert a Repeated START condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Generate a STOP condition on SDA and SCL.

- 5. Configure the I<sup>2</sup>C port to receive data.

- 6. Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to imitate transmission before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

# FIGURE 15-10: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

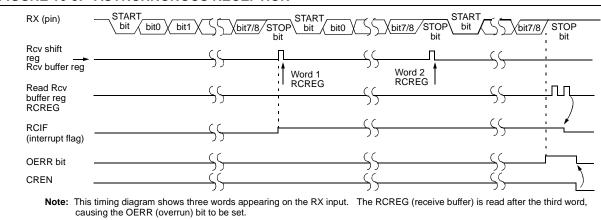

### FIGURE 16-5: ASYNCHRONOUS RECEPTION

### TABLE 16-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7     | Bit 6         | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|--------|-----------|---------------|-----------|-----------|-------|--------|--------|--------|-------------------------|---------------------------------|

| INTCON | GIE/GIEH  | PEIE/GIEL     | TMR0IE    | INT0IE    | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x               | 0000 000u                       |

| PIR1   | PSPIF     | ADIF          | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| PIE1   | PSPIE     | ADIE          | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| IPR1   | PSPIP     | ADIP          | RCIP      | TXIP      | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000 0000               | 0000 0000                       |

| RCSTA  | SPEN      | RX9           | SREN      | CREN      | -     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| RCREG  | USART Red | ceive Registe | r         |           |       |        |        |        | 0000 0000               | 0000 0000                       |

| TXSTA  | CSRC      | TX9           | TXEN      | SYNC      | ADDEN | BRGH   | TRMT   | TX9D   | 0000 0010               | 0000 0010                       |

| SPBRG  | Baud Rate |               | 0000 0000 | 0000 0000 |       |        |        |        |                         |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

RXB0Interrupt bcf PIR3, RXB0IF ; Clear the interrupt flag goto AccessBuffer AccessBuffer ; This is either TX or RX interrupt ; Copy CANCON.ICODE bits to CANSTAT.WIN bits TempCANCON, W ; Clear CANCON.WIN bits before copying movf ; new ones. ; Use previously saved CANCON value to andlw b'11110001' ; make sure same value. movwf TempCANCON ; Copy masked value back to TempCANCON TempCANSTAT, W movf ; Retrieve ICODE bits andlw b'00001110' ; Use previously saved CANSTAT value ; to make sure same value. TempCANCON ; Copy ICODE bits to WIN bits. iorwf movff TempCANCON, CANCON ; Copy the result to actual CANCON ; Access current buffer ... ; Your code ; Restore CANCON.WIN bits movf CANCON, W ; Preserve current non WIN bits andlw b'11110001' iorwf TempCANCON ; Restore original WIN bits ; Do not need to restore CANSTAT - it is read-only register. ; Return from interrupt or check for another module interrupt source

### 17.2.3 CAN RECEIVE BUFFER REGISTERS

This section shows the Receive Buffer registers with its associated control registers.

|         | R/C-0                                                                                                                                                                                                | R/W-0                                     | R/W-0                               | U-0                                     | R-0                                                 | R/W-0          | R-0          | R/W-0   |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------------------|----------------|--------------|---------|--|--|

|         | RXFUL                                                                                                                                                                                                | RXM1                                      | RXM0                                | _                                       | RXRTRRO                                             | RXB0DBEN       | JTOFF        | FILHIT0 |  |  |

|         | bit 7                                                                                                                                                                                                |                                           |                                     |                                         | -                                                   |                |              | bit 0   |  |  |

| bit 7   | <b>RXFUL:</b> Receive Full Status bit<br>1 = Receive buffer contains a received message<br>0 = Receive buffer is open to receive a new message                                                       |                                           |                                     |                                         |                                                     |                |              |         |  |  |

|         | <b>Note:</b> This bit is set by the CAN module and should be cleared by software after the buffer is read.                                                                                           |                                           |                                     |                                         |                                                     |                |              |         |  |  |

| bit 6-5 | 10 <b>= Rece</b> i                                                                                                                                                                                   | ve all mess<br>ve only val<br>ve only val | ages (incluid message<br>id message | uding thos<br>es with ex<br>es with sta | e with errors)<br>tended identif<br>andard identifi | ier            |              |         |  |  |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                           |                                           |                                     |                                         |                                                     |                |              |         |  |  |

| bit 3   | <b>RXRTRRO</b><br>1 = Remote<br>0 = No rem                                                                                                                                                           | e transfer re                             | equest                              | ansfer Re                               | quest Read O                                        | nly bit        |              |         |  |  |

| bit 2   | 1 = Receive                                                                                                                                                                                          | e Buffer 0 d                              | overflow wi                         | Il write to                             | fer Enable bit<br>Receive Buffe<br>ive Buffer 1     |                |              |         |  |  |

| bit 1   | JTOFF: Jump Table Offset bit (read only copy of RX0DBEN)<br>1 = Allows Jump Table offset between 6 and 7<br>0 = Allows Jump Table offset between 1 and 0                                             |                                           |                                     |                                         |                                                     |                |              |         |  |  |

|         | Note:                                                                                                                                                                                                | This bit allo                             | ows same                            | filter jump                             | table for both                                      | RXB0CON a      | nd RXB1CO    | N.      |  |  |

| bit 0   | <b>FILHIT0:</b> Filter Hit bit<br>This bit indicates which acceptance filter enabled the message reception into receive buffer 0<br>1 = Acceptance Filter 1 (RXF1)<br>0 = Acceptance Filter 0 (RXF0) |                                           |                                     |                                         |                                                     |                |              |         |  |  |

|         | Legend:                                                                                                                                                                                              |                                           |                                     |                                         |                                                     |                |              |         |  |  |

|         | R = Reada                                                                                                                                                                                            | ble bit                                   | W = Wri                             | table bit                               | U = U                                               | nimplemented   | bit, read as | '0'     |  |  |

|         | - n = Value                                                                                                                                                                                          | at POR                                    | '1' = Bit                           | is set                                  | '0' = E                                             | Bit is cleared | x = Bit is ι | Inknown |  |  |

### REGISTER 17-12: RXB0CON - RECEIVE BUFFER 0 CONTROL REGISTER

### 17.2.5 CAN BAUD RATE REGISTERS

This subsection describes the CAN Baud Rate registers.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 BRP0 SJW1 SJW0 BRP5 BRP4 BRP3 BRP2 BRP1 bit 7 bit 0 bit 7-6 SJW1:SJW0: Synchronized Jump Width bits 11 = Synchronization Jump Width Time = $4 \times TQ$ 10 = Synchronization Jump Width Time = $3 \times TQ$ 01 = Synchronization Jump Width Time = $2 \times TQ$ 00 = Synchronization Jump Width Time = 1 x TQ bit 5-0 BRP5:BRP0: Baud Rate Prescaler bits 111111 = TQ = (2 x 64)/FOSC 111110 = TQ = (2 x 63)/FOSC 000001 = TQ = (2 x 2)/FOSC 000000 = Tq = (2 x 1)/Fosc Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 17-29: BRGCON1 – BAUD RATE CONTROL REGISTER 1

Note: This register is only accessible in Configuration mode.

# 18.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has twelve inputs for the PIC18C658 devices and sixteen for the PIC18C858 devices. This module has the ADCON0, ADCON1, and ADCON2 registers.

The A/D allows conversion of an analog input signal to a corresponding 10-bit digital number.

The A/D module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 18-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 18-2, configures the functions of the port pins. The ADCON2, shown in Register 16-3, configures the A/D clock source and justification.

### REGISTER 18-1: ADCON0 REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-----|-------|-------|-------|-------|---------|-------|

| —     | —   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |     |       |       |       |       |         | bit 0 |

### bit 7-6 Unimplemented: Read as '0'

bit 5-2

2 CHS3:CHS0: Analog Channel Select bits

| Chos. Chos. Analog Channel               |

|------------------------------------------|

| 0000 = channel 00, (AN0)                 |

| 0001 = channel 01, (AN1)                 |

| 0010 = channel 02, (AN2)                 |

| 0011 = channel 03, (AN3)                 |

| 0100 = channel 04, (AN4)                 |

| 0101 = channel 05, (AN5)                 |

| 0110 = channel 06, (AN6)                 |

| 0111 = channel 07, (AN7)                 |

| 1000 = channel 08, (AN8)                 |

| 1001 = channel 09, (AN9)                 |

| 1010 = channel 10, (AN10)                |

| 1011 = channel 11, (AN11)                |

| 1100 = channel 12, (AN12) <sup>(1)</sup> |

| 1101 = channel 13, (AN13) <sup>(1)</sup> |

| 1110 = channel 14, (AN14) <sup>(1)</sup> |

| 1111 = channel 15, (AN15) <sup>(1)</sup> |

|                                          |

**Note 1:** These channels are not available on the PIC18C658 devices.

bit 1

- 1 = A/D conversion in progress. Setting this bit starts an A/D conversion cycle. This bit is automatically cleared by hardware when the A/D conversion is complete.

- 0 = A/D conversion not in progress

GO/DONE: A/D Conversion Status bit

bit 0 ADON: A/D On bit

When ADON = 1

- 1 = A/D converter module is operating

- 0 = A/D converter module is shut off and consumes no operating current

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

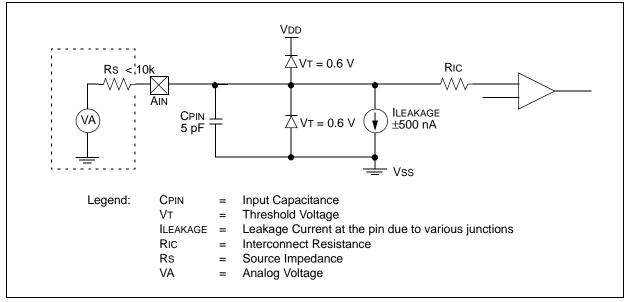

### 19.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 19-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6 V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### FIGURE 19-4: ANALOG INPUT MODEL

### TABLE 19-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name   | Bit 7        | Bit 6         | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|-------------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| CMCON  | C2OUT        | C1OUT         | C2INV       | C1INV | CIS   | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| VRCON  | VREN         | VROE          | VRR         | VRSS  | VR3   | VR2    | VR1    | VR0    | 0000 0000       | 0000 0000                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE      | INTIE | RBIE  | TMR0IF | INTIF  | RBIF   | 0000 000x       | 0000 000u                       |

| PIR2   | —            | CMIF          | —           | -     | BCLIF | LVDIF  | TMR3IF | CCP2IF | -0 0000         | -0 0000                         |

| PIE2   | —            | CMIE          | —           | -     | BCLIE | LVDIE  | TMR3IE | CCP2IE | -0 0000         | -0 0000                         |

| IPR2   | —            | CMIP          | —           | _     | BCLIP | LVDIP  | TMR3IP | CCP2IP | -1 1111         | -1 1111                         |

| PORTF  | RF7          | RF6           | RF5         | RF4   | RF3   | RF2    | RF1    | RF0    | x000 0000       | u000 0000                       |

| LATF   | LATF7        | LATF6         | LATF5       | LATF4 | LATF3 | LATF2  | LATF1  | LATF0  | xxxx xxxx       | uuuu uuuu                       |

| TRISF  | PORTF D      | Data Direct   | tion Regist | ter   |       |        |        |        | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as "0"

| TBL   | NТ                                                                   | Table V                                                                                               | /rite                                                                                                             |                                                                                                         | TBLWT                                                                                                                                                                                                                                                                                                                                                                                 | Table Wr                                                                                   | ite (Continued)                                 |  |  |  |

|-------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|

| Synta | ax:                                                                  | [ label ]                                                                                             | TBLWT                                                                                                             | · ( *; *+; *-; +*)                                                                                      | Example 1:                                                                                                                                                                                                                                                                                                                                                                            | TBLWT *                                                                                    | +;                                              |  |  |  |

| Oper  | ands:                                                                | None                                                                                                  |                                                                                                                   |                                                                                                         | Before Ins                                                                                                                                                                                                                                                                                                                                                                            | truction                                                                                   |                                                 |  |  |  |

| •     | ation:                                                               |                                                                                                       |                                                                                                                   | Mem (TBLPTR) or                                                                                         | TABLA<br>TBLPT                                                                                                                                                                                                                                                                                                                                                                        | TABLAT=0x55TBLPTR=0x00A356MEMORY(0x00A356)=0xFFAfter Instructions (table write completion) |                                                 |  |  |  |

|       |                                                                      | TBLPTF<br>if TBLW<br>(TABLA<br>Holding<br>(TBLPT<br>if TBLW<br>(TABLA<br>Holding<br>(TBLPT<br>if TBLW | R - No Cha<br>T*+,<br>T) → Prog<br>Register;<br>R) +1 → T<br>T*-,<br>T) → Prog<br>Register;<br>R) -1 → TE<br>T+*, | Mem (TBLPTR) or<br>BLPTR;<br>Mem (TBLPTR) or<br>BLPTR;                                                  | TABLAT       =       0x55         TBLPTR       =       0x00A357         MEMORY(0x00A356)       =       0x55         Example 2:       TBLWT       +*;         Before Instruction       TABLAT       =       0x34         TBLPTR       =       0x01389A       MEMORY(0x01389A)       =       0xFF         MEMORY(0x01389B)       =       0xFF       MEMORY(0x01389B)       =       0xFF |                                                                                            |                                                 |  |  |  |

| Ctat  |                                                                      | (TABLA<br>Holding                                                                                     | R) +1 $\rightarrow$ T<br>T) $\rightarrow$ Prog<br>Register;                                                       | BLPTR;<br>Mem (TBLPTR) or                                                                               | TABLA<br>TBLPT                                                                                                                                                                                                                                                                                                                                                                        |                                                                                            | e completion)<br>= 0x34<br>= 0x01389B<br>= 0xFF |  |  |  |

|       | us Affected                                                          | None                                                                                                  |                                                                                                                   |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       | RY(0x01389B)                                                                               | = 0x34                                          |  |  |  |

| Enco  | oding:                                                               | 0000                                                                                                  | 0000                                                                                                              | 0000 11nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +*                                                          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| Desc  | cription:                                                            |                                                                                                       |                                                                                                                   | used to program the m Memory (P.M.).                                                                    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       |                                                                      | to each<br>TBLPTF<br>range. <sup>-</sup><br>selects                                                   | byte in the<br>R has a 2 M<br>The LSb of                                                                          | I-bit pointer) points<br>program memory.<br>//Btye address<br>the TBLPTR<br>of the program<br>p access. |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       |                                                                      | TB                                                                                                    | LPTR[0] =                                                                                                         | 0:Least Significant<br>Byte of Program<br>Memory Word                                                   |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       |                                                                      | TB                                                                                                    | LPTR[0] =                                                                                                         | 1:Most Significant<br>Byte of Program<br>Memory Word                                                    |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       |                                                                      |                                                                                                       | LWT instruct<br>TBLPTR a                                                                                          | tion can modify the as follows:                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       |                                                                      | <ul> <li>post-</li> </ul>                                                                             | ange<br>ncrement<br>decrement<br>icrement                                                                         |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| Word  | ds:                                                                  | 1                                                                                                     |                                                                                                                   |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| Cycle | Cycles: 2 (many if long write is to on-chip<br>EPROM program memory) |                                                                                                       |                                                                                                                   |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| Q Cv  | cle Activity                                                         |                                                                                                       |                                                                                                                   | 27                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| )     | Q1                                                                   | Q2                                                                                                    | Q3                                                                                                                | Q4                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

|       | Decode                                                               | No<br>operation                                                                                       | No<br>operation                                                                                                   | No<br>operation                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

| Ī     | N.L.                                                                 | NL.                                                                                                   | NL.                                                                                                               |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |                                                 |  |  |  |

No

operation

No

operation

(Read TABLAT)

No

operation

No operation (Write to Holding Register or Memory)

MCP2510 > 7. 74, 76, . MCRFXXX > 5 5 5 73, 2, XXXSOH > > 5 5 65, 63CXX 52CXX\ 54CXX\ 63, 64, >  $\mathbf{i}$ Contact the Microchip Technology Inc. web site at www.microchip.com for information on how to use the MPLAB® ICD In-Circuit Debugger (DV164001) with PIC16C62, Contact Microchip Technology Inc. for availability date. PIC18CXX2 > > >  $\mathbf{i}$  $\mathbf{i}$ > > XX73713I9 > 5 > > >  $\mathbf{\mathbf{N}}$ 5 PIC17C4X >  $\mathbf{i}$ > > 5 > > 7X6C91CIA  $\mathbf{i}$ >  $\mathbf{i}$ > 5 > > PIC16F8XX  $\mathbf{i}$ > > > > > PIC16C8X  $\mathbf{i}$ > 5 5 > 1  $\mathbf{i}$ XX7O31OI9  $\mathbf{i}$ >  $\mathbf{i}$ >  $\mathbf{i}$ 5 ╧ X72812I9 \* ╧  $\mathbf{i}$  $\mathbf{i}$  $\mathbf{i}$ > 1 \*\* \ \*\* \ \*\*\ PIC16F62X  $\mathbf{i}$  $\mathbf{i}$ PIC16CXXX > 5  $\mathbf{i}$ 1  $\mathbf{i}$ > 5 PIC16C6X \* > ╧ > > 5 5 > PIC16C5X  $\mathbf{i}$ >  $\mathbf{i}$ >  $\mathbf{i}$ > 5 PIC14000 > > > > > > PIC12CXXX  $\mathbf{i}$ >  $\mathbf{i}$ > 5 > MPLAB<sup>®</sup> ICE In-Circuit Emulator 125 kHz Anticollision microlD™ Developer's Kit MCP2510 CAN Developer's Kit PRO MATE<sup>®</sup> II Universal Device Programmer PICDEM™ 14A Demonstration Board CEPIC<sup>TM</sup> In-Circuit Emulator PICSTART<sup>®</sup> Plus Entry Level Development Programmer PICDEM<sup>TM</sup> 17 Demonstration Board microID<sup>TM</sup> Programmer's Kit PICDEM<sup>TM</sup> 1 Demonstration Board PICDEM™ 2 Demonstration Board PICDEM<sup>TM</sup> 3 Demonstration Board **Development** Environment KEELoq® Transponder Kit 13.56 MHz Anticollision microlD<sup>TM</sup> Developer's Kit MPLAB<sup>®</sup> C17 C Compiler MPLAB<sup>®</sup> C18 C Compiler MPASM<sup>TM</sup> Assembler/ MPLINK<sup>TM</sup> Object Linker KEELoo® Evaluation Kit MPLAB<sup>®</sup> ICD In-Circuit MPLAB<sup>®</sup> Integrated 125 kHz microlD™ Developer's Kit Debugger ž Programmers Debugger Emulators Software Tools Demo Boards and Eval Kits

© 2000 Microchip Technology Inc.

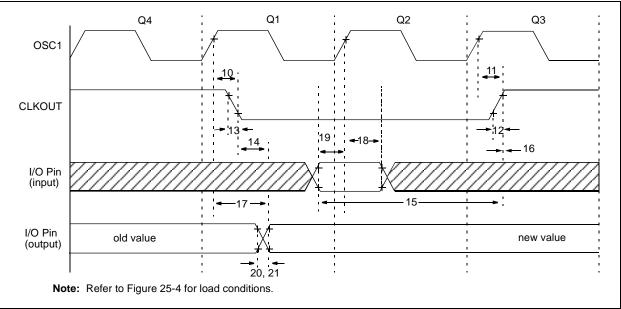

### FIGURE 25-6: CLKOUT AND I/O TIMING

| TABLE 25-6: CLKOUT AND I/O TIMING REQUIREMENTS |                   |                                                  |                     |                       |        |             |       |            |

|------------------------------------------------|-------------------|--------------------------------------------------|---------------------|-----------------------|--------|-------------|-------|------------|

| Param.<br>No.                                  | Symbol            | Characteris                                      | stic                | Min                   | Тур    | Max         | Units | Conditions |

| 10                                             | TosH2ckL          | OSC1 <sup>↑</sup> to CLKOUT↓                     |                     | _                     | 75     | 200         | ns    | (1)        |

| 11                                             | TosH2ckH          | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>         |                     |                       | 75     | 200         | ns    | (1)        |

| 12                                             | TckR              | CLKOUT rise time                                 |                     | $- \langle$           | 35     | 100         | ns    | (1)        |

| 13                                             | TckF              | CLKOUT fall time                                 |                     |                       | 35     | 100         | ns    | (1)        |

| 14                                             | TckL2ioV          | CLKOUT ↓ to Port out valid                       |                     | $\leq + V$            | $\sum$ | 0.5Tcy + 20 | ns    | (1)        |

| 15                                             | TioV2ckH          | Port in valid before CLKOUT 1                    |                     | \0.25 <b>T</b> cy\+25 | -      | _           | ns    | (1)        |

| 16                                             | TckH2iol          | Port in hold after CLKOUT                        |                     |                       | _      | _           | ns    | (1)        |

| 17                                             | TosH2ioV          | OSC1↑ (Q1 cycle) to Port out valid               |                     | $\vee$ –              | 50     | 150         | ns    |            |

| 18                                             | TosH2iol          | OSC1↑ (Q2 cycle) <sub>&lt;</sub> to <sub>∖</sub> | PIC18CXX8           | 100                   | _      | _           | ns    |            |

| 18A                                            |                   | Port input invalid<br>(I/O in hold time)         | PIC18LCXX8          | 200                   |        | —           | ns    |            |

| 19                                             | TioV2osH          | Port input valid to OSC11<br>(I/O in setup time) |                     | 0                     |        | _           | ns    |            |

| 20                                             | TioR              | Port output rise time                            | PIC18 <b>C</b> XX8  | _                     | 10     | 25          | ns    |            |

| 20A                                            | $\langle \rangle$ | ) \                                              | PIC18 <b>LC</b> XX8 | _                     | _      | 60          | ns    |            |

| 21                                             | TioF              | Port output fall time                            | PIC18 <b>C</b> XX8  |                       | 10     | 25          | ns    |            |

| 21A                                            | $\searrow$        |                                                  | PIC18 <b>LC</b> XX8 |                       | _      | 60          | ns    |            |

| 22††                                           | TINP              | INT pin high or low time                         |                     | Тсү                   | —      | _           | ns    |            |

| 23††                                           | Trbp              | RB7:RB4 change INT high or low time              |                     | Тсү                   | _      |             | ns    |            |

| 24††                                           | TRCP              | RC7:RC4 change INT high or low time              |                     | 20                    | —      | _           | ns    |            |

††These parameters are asynchronous events, not related to any internal clock edges.

Note 1: Measurements are taken in RC mode where CLKO pin output is 4 x Tosc.

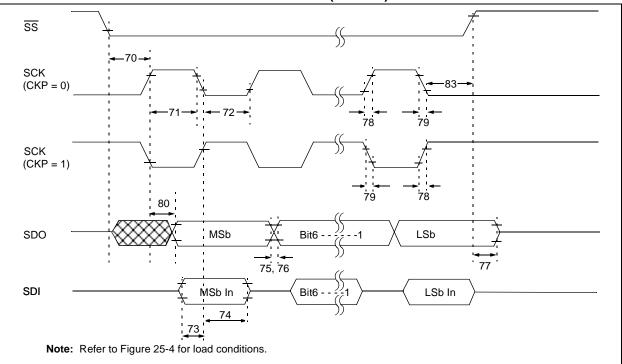

# TABLE 25-13: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING (CKE = 0))

| Parm.<br>No. | Symbol                | Characteristic                                                        |                     | Min          | Max                 | Units    | Conditions |

|--------------|-----------------------|-----------------------------------------------------------------------|---------------------|--------------|---------------------|----------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input |                     | Тсү          | - (                 | ns       |            |

| 71           | TscH                  | SCK input high time                                                   | Continuous          | 1.25Tcy + 30 | $\langle - \rangle$ | ns       |            |

| 71A          |                       | (Slave mode)                                                          | Single Byte         |              | <u></u>             | ns       | (Note 1)   |

| 72           | TscL                  | SCK input low time                                                    | Continuous          | 1.25TCY + 30 | $\searrow$          | ns       |            |

| 72A          |                       | (Slave mode)                                                          | Single Byte         | 1 D40 V      |                     | ns       | (Note 1)   |

| 73           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK e                                 | 100                 |              | ns                  |          |            |

| 73A          | Тв2в                  | Last clock edge of Byte1 to the 1st clo                               | 1.5Tcy + 40         | _            | ns                  | (Note 2) |            |

| 74           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               |                     | 100          |                     | ns       |            |

| 75           | TdoR                  | SDO data output rişê time                                             | PIC18 <b>C</b> XX8  | —            | 25                  | ns       |            |

|              |                       |                                                                       | PIC18 <b>LC</b> XX8 |              | 45                  | ns       |            |

| 76           | TdoF                  | SDO data output fall time                                             |                     | —            | 25                  | ns       |            |

| 77           | TssH2doZ              | S81 to SDO output hi-impedance                                        |                     | 10           | 50                  | ns       |            |

| 78           | TscR                  | SCK output rise time                                                  | PIC18 <b>C</b> XX8  | —            | 25                  | ns       |            |

|              |                       | (Master mode)                                                         | PIC18 <b>LC</b> XX8 |              | 45                  | ns       |            |

| 79           | TscF                  | SCK output fall time (Master mode)                                    |                     | —            | 25                  | ns       |            |

| 80           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | PIC18 <b>C</b> XX8  |              | 50                  | ns       |            |

|              |                       |                                                                       | PIC18 <b>LC</b> XX8 |              | 100                 | ns       |            |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                     | 1.5Tcy + 40  | —                   | ns       |            |

**Note 1:** Requires the use of parameter # 73A.

2: Only if parameter #s 71A and 72A are used.

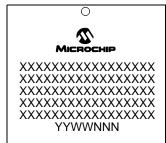

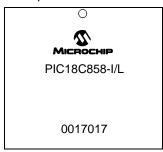

### Package Marking Information (Cont'd)

### 84-Lead PLCC

Example

# APPENDIX E: DEVELOPMENT TOOL VERSION REQUIREMENTS

This lists the minimum requirements (software/firmware) of the specified development tool to support the devices listed in this data sheet.

### MPLAB-ICE 2000:

| PIC18CXX8 Process<br>Part Number -                                                     | sor Module:<br>PCM 18XB0                                                        |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| PIC18CXX8 Device<br>Socket<br>64-pin TQFP<br>68-pin PLCC<br>80-pin TQFP<br>84-pin PLCC | Adapter:<br>Part Number<br>DVD18P2640<br>DVD18XL680<br>DVD18PQ800<br>DVD18XL840 |

| MPLAB-ICD:                                                                             | Not Available                                                                   |

| PROMATE II:                                                                            | version 5.20                                                                    |

| PICSTART Plus:                                                                         | version 2.20                                                                    |

| MPASM:                                                                                 | version 2.50                                                                    |

| MPLAB-C18:                                                                             | version 1.00                                                                    |

| CAN-TOOL:                                                                              | Not available at time printing.                                                 |

| Note: | Please read all associated README.TXT       |  |  |  |

|-------|---------------------------------------------|--|--|--|

|       | files that are supplied with the develop-   |  |  |  |

|       | ment tools. These "read me" files will dis- |  |  |  |

|       | cuss product support and any known          |  |  |  |

|       | limitations.                                |  |  |  |

of