Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 62                                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | -                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0475gk-gak-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.4 Operations of 8-Bit Timer/Event Counters 50, 51, and 52      | 272 |

|------------------------------------------------------------------|-----|

| 7.4.1 Operation as interval timer                                |     |

| 7.4.2 Operation as external event counter                        |     |

| 7.4.3 Square-wave output operation                               |     |

| 7.4.4 PWM output operation                                       |     |

| 7.5 Cautions for 8-Bit Timer/Event Counters 50, 51, and 52       | 279 |

| CHAPTER 8 8-BIT TIMERS H0, H1, AND H2                            |     |

| 8.1 Functions of 8-Bit Timers H0, H1, and H2                     | 282 |

| 8.2 Configuration of 8-Bit Timers H0, H1, and H2                 |     |

| 8.3 Registers Controlling 8-Bit Timers H0, H1, and H2            |     |

| 8.4 Operation of 8-Bit Timers H0, H1 and H2                      |     |

| 8.4.1 Operation as interval timer/square-wave output             |     |

| 8.4.2 Operation as PWM output                                    |     |

| 8.4.3 Carrier generator operation (8-bit timer H1 only)          |     |

| 8.4.4 Control of number of carrier clocks by timer 51 counter    |     |

|                                                                  |     |

| CHAPTER 9 REAL-TIME COUNTER                                      | 311 |

| 9.1 Functions of Real-Time Counter                               |     |

| 9.2 Configuration of Real-Time Counter                           |     |

| 9.3 Registers Controlling Real-Time Counter                      | 313 |

| 9.4 Real-Time Counter Operation                                  | 327 |

| 9.4.1 Starting operation of real-time counter                    |     |

| 9.4.2 Shifting to STOP mode after starting operation             |     |

| 9.4.3 Reading/writing real-time counter                          |     |

| 9.4.4 Setting alarm of real-time counter                         |     |

| 9.4.5 1 Hz output of real-time counter                           |     |

| 9.4.6 32.768 kHz output of real-time counter                     |     |

| 9.4.7 512 Hz, 16.384 kHz output of real-time counter             |     |

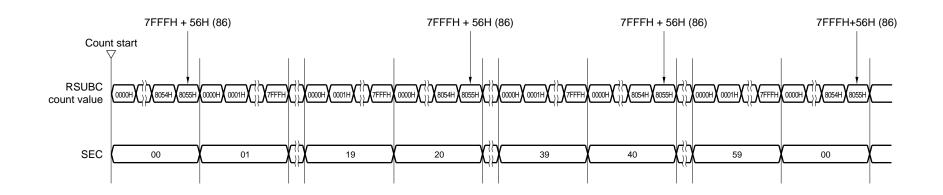

| 9.4.8 Example of watch error correction of real-time counter     |     |

| CHAPTER 10 WATCHDOG TIMER                                        |     |

| 10.1 Functions of Watchdog Timer                                 |     |

| 10.2 Configuration of Watchdog Timer                             |     |

| 10.3 Register Controlling Watchdog Timer                         |     |

| 10.4 Operation of Watchdog Timer                                 |     |

| 10.4.1 Controlling operation of watchdog timer                   |     |

| 10.4.2 Setting overflow time of watchdog timer                   |     |

| 10.4.3 Setting window open period of watchdog timer              |     |

| CHAPTER 11 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER                 |     |

| 11.1 Functions of Clock Output/Buzzer Output Controller          |     |

| 11.2 Configuration of Clock Output/Buzzer Output Controller      |     |

| 11.3 Registers Controlling Clock Output/Buzzer Output Controller |     |

| 11.4 Operations of Clock Output/Buzzer Output Controller         |     |

| 11.4.1 Operation as clock output                                 |     |

| 11.4.2 Operation as buzzer output                                |     |

|                                                                  |     |

| 16.3 Registers Controlling Serial Interface CSI10                         | 462 |

|---------------------------------------------------------------------------|-----|

| 16.4 Operation of Serial Interface CSI10                                  | 466 |

| 16.4.1 Operation stop mode                                                | 466 |

| 16.4.2 3-wire serial I/O mode                                             | 466 |

| CHAPTER 17 SERIAL INTERFACE CSIA0                                         | 476 |

| 17.1 Functions of Serial Interface CSIA0                                  | 476 |

| 17.2 Configuration of Serial Interface CSIA0                              | 477 |

| 17.3 Registers Controlling Serial Interface CSIA0                         | 479 |

| 17.4 Operation of Serial Interface CSIA0                                  | 488 |

| 17.4.1 Operation stop mode                                                | 488 |

| 17.4.2 3-wire serial I/O mode                                             | 489 |

| 17.4.3 3-wire serial I/O mode with automatic transmit/receive function    | 494 |

| CHAPTER 18 LCD CONTROLLER/DRIVER                                          | 509 |

| 18.1 Functions of LCD Controller/Driver                                   | 509 |

| 18.2 Configuration of LCD Controller/Driver                               | 511 |

| 18.3 Registers Controlling LCD Controller/Driver                          | 513 |

| 18.4 Setting LCD Controller/Driver                                        | 521 |

| 18.4.1 Setting method when not using segment key scan function (KSON = 0) | 521 |

| 18.4.2 Setting method when using segment key scan function (KSON = 1)     | 522 |

| 18.5 LCD Display Data Memory                                              | 524 |

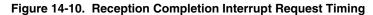

| 18.6 Common and Segment Signals                                           | 525 |

| 18.7 Display Modes                                                        | 535 |

| 18.7.1 Static display example                                             |     |

| 18.7.2 Two-time-slice display example                                     | 538 |

| 18.7.3 Three-time-slice display example                                   |     |

| 18.7.4 Four-time-slice display example                                    |     |

| 18.7.5 Eight-time-slice display example                                   |     |

| 18.8 Operation of Segment Key Scan Function                               | 561 |

| 18.8.1 Circuit configuration example                                      | 561 |

| 18.8.2 Example of procedure for using segment key scan function           |     |

| 18.9 Cautions When Using Segment Key Scan Function                        |     |

| 18.10 Supplying LCD Drive Voltages VLC0, VLC1, VLC2, and VLC3             | 567 |

| 18.10.1 Internal resistance division method                               | 567 |

| 18.10.2 External resistance division method                               | 569 |

| CHAPTER 19 MANCHESTER CODE GENERATOR                                      | 571 |

| 19.1 Functions of Manchester Code Generator                               |     |

| 19.2 Configuration of Manchester Code Generator                           |     |

| 19.3 Registers Controlling Manchester Code Generator                      |     |

| 19.4 Operation of Manchester Code Generator                               |     |

| 19.4.1 Operation stop mode                                                |     |

| 19.4.2 Manchester code generator mode                                     |     |

| 19.4.3 Bit sequential buffer mode                                         | 587 |

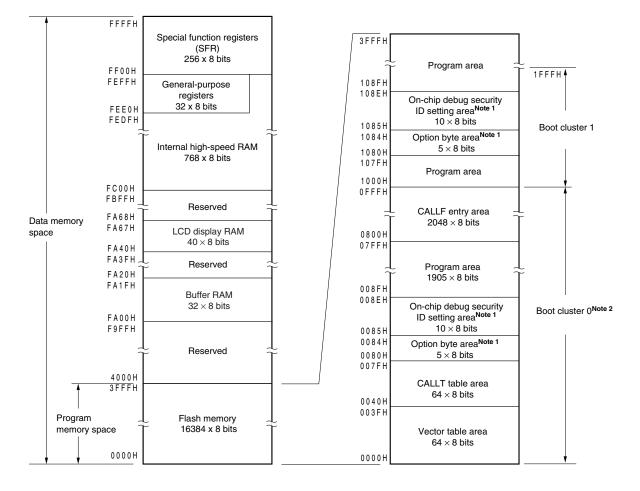

Figure 3-1. Memory Map (µPD78F0471, 78F0481)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 28.8 Security Setting).

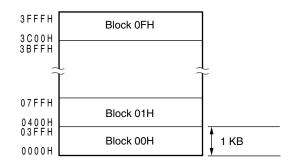

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

# 5.4 System Clock Oscillator

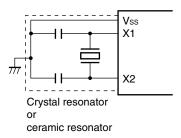

### 5.4.1 X1 oscillator

The X1 oscillator oscillates with a crystal resonator or ceramic resonator (2 to 10 MHz) connected to the X1 and X2 pins.

An external clock can also be input. In this case, input the clock signal to the EXCLK pin. Figure 5-10 shows an example of the external circuit of the X1 oscillator.

### Figure 5-10. Example of External Circuit of X1 Oscillator

### (a) Crystal or ceramic oscillation

(b) External clock

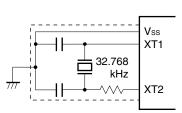

#### 5.4.2 XT1 oscillator

The XT1 oscillator oscillates with a crystal resonator (standard: 32.768 kHz) connected to the XT1 and XT2 pins. Figure 5-11 shows an example of the external circuit of the XT1 oscillator.

## Figure 5-11. Example of External Circuit of XT1 Oscillator

#### (a) Crystal oscillation

- Caution 1. When using the X1 oscillator and XT1 oscillator, wire as follows in the area enclosed by the broken lines in the Figures 5-10 and 5-11 to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss. Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

Note that the XT1 oscillator is designed as a low-amplitude circuit for reducing power consumption.

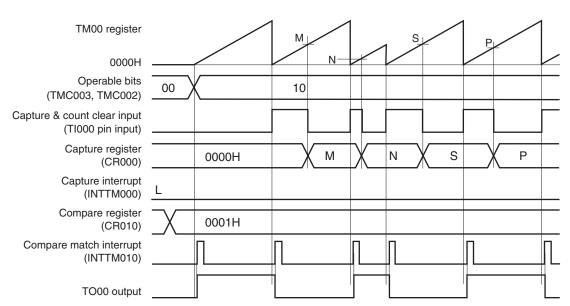

# Figure 6-28. Timing Example of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Capture Register, CR010: Compare Register) (1/2)

#### (a) TOC00 = 13H, PRM00 = 10H, CRC00, = 03H, TMC00 = 08H, CR010 = 0001H

This is an application example where the TO00 output level is to be inverted when the count value has been captured & cleared.

TM00 is cleared at the rising edge detection of the TI000 pin and it is captured to CR000 at the falling edge detection of the TI000 pin.

When bit 1 (CRC001) of capture/compare control register 00 (CRC00) is set to 1, the count value of TM00 is captured to CR000 in the phase reverse to that of the signal input to the TI000 pin, but the capture interrupt signal (INTTM000) is not generated. However, the INTTM000 signal is generated when the valid edge of the TI010 pin is detected. Mask the INTTM000 signal when it is not used.

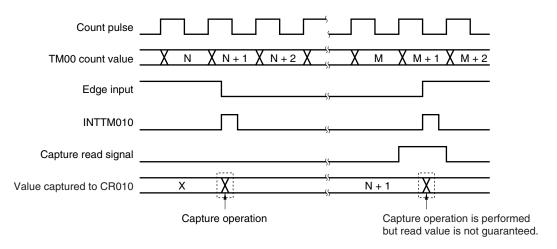

# (4) Timing of holding data by capture register

(a) When the valid edge is input to the TI000/TI010 pin and the reverse phase of the TI000 pin is detected while CR000/CR010 is read, CR010 performs a capture operation but the read value of CR000/CR010 is not guaranteed. At this time, an interrupt signal (INTTM000/INTTM010) is generated when the valid edge of the TI000/TI010 pin is detected (the interrupt signal is not generated when the reverse-phase edge of the TI000 pin is detected).

When the count value is captured because the valid edge of the TI000/TI010 pin was detected, read the value of CR000/CR010 after INTTM000/INTTM010 is generated.

(b) The values of CR000 and CR010 are not guaranteed after 16-bit timer/event counter 00 stops.

### (5) Setting valid edge

Set the valid edge of the TI000 pin while the timer operation is stopped (TMC003 and TMC002 = 00). Set the valid edge by using ES000 and ES001.

# (6) Re-triggering one-shot pulse

Make sure that the trigger is not generated while an active level is being output in the one-shot pulse output mode. Be sure to input the next trigger after the current active level is output.

CHAPTER 9 REAL-TIME COUNTER

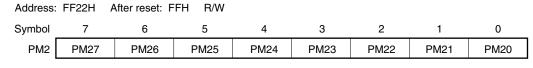

# (6) Port mode register 2 (PM2)

When using the ANI0/P20 to ANI7/P27 pins for analog input port, set PM20 to PM27 to 1. The output latches of P20 to P27 at this time may be 0 or 1.

If PM20 to PM27 are set to 0, they cannot be used as analog input port pins.

PM2 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to FFH.

### Figure 12-10. Format of Port Mode Register 2 (PM2)

| PM2n | P2n pin I/O mode selection (n = 0 to 7) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

ANI0/P20 to ANI7/P27 pins are as shown below depending on the settings of PF2, ADPC0, PM2, ADS, and ADDCTL0.

# Table 12-3. Setting Functions of P20/ANI0 to P27/ANI7 Pins

#### (a) *µ*PD78F048x

| PF2                  | ADPC0                  | PM2            | ADS                  | P20/SEG39/ANI0 to P27/SEG32/ANI7 Pins                                         |

|----------------------|------------------------|----------------|----------------------|-------------------------------------------------------------------------------|

| Digital/Analog       | Analog input selection | Input mode     | Does not select ANI. | Analog input (not to be converted)                                            |

| selection            |                        |                | Selects ANI.         | Analog input (to be converted by successive approximation type A/D converter) |

|                      |                        | Output<br>mode | _                    | Setting prohibited                                                            |

|                      | Digital I/O selection  | Input mode     | -                    | Digital input                                                                 |

|                      |                        | Output<br>mode | -                    | Digital output                                                                |

| SEG output selection | -                      | _              | -                    | Segment output                                                                |

### (b) *µ*PD78F049x

| ADPC0        | PM2         | ADS                  | ADDCTL0               | P20/ANI0/DS0- to P27/ANI7/REF+ Pins                                           |

|--------------|-------------|----------------------|-----------------------|-------------------------------------------------------------------------------|

| Analog input | Input mode  | Does not select ANI. | Does not select DSn±. | Analog input (not to be converted)                                            |

| selection    |             | Selects ANI.         | Does not select DSn±. | Analog input (to be converted by successive approximation type A/D converter) |

|              |             | Does not select ANI. | Selects DSn±.         | Analog input (to be converted by $\Delta\Sigma$ type A/D converter)           |

|              |             | Selects ANI.         | Selects DSn±.         | Setting prohibited                                                            |

|              | Output mode |                      | _                     | Setting prohibited                                                            |

| Digital I/O  | Input mode  | _                    |                       | Digital input                                                                 |

| selection    | Output mode |                      | _                     | Digital output                                                                |

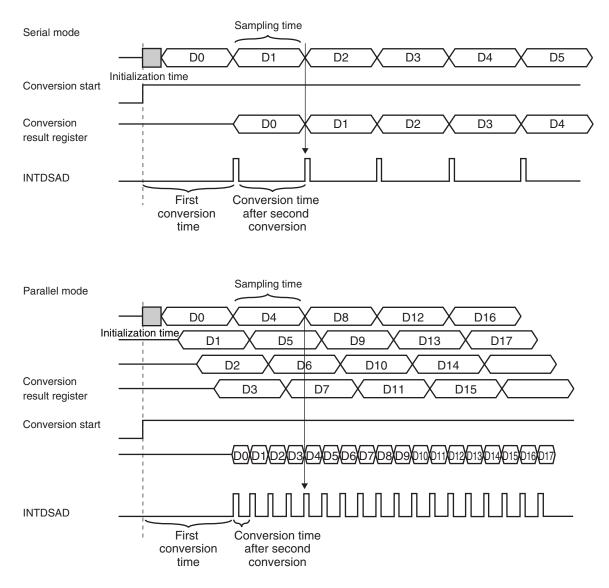

# (3) Serial mode/parallel mode

Serial or parallel mode can be selected as the input mode for the 16-bit  $\Delta\Sigma$  type A/D converter. The parallel mode can reduce the conversion time to a fourth of that in the serial mode. The conversion time of the first conversion, however, is the same as that in the serial mode. Also, the sampling time itself is the same as in the serial mode.

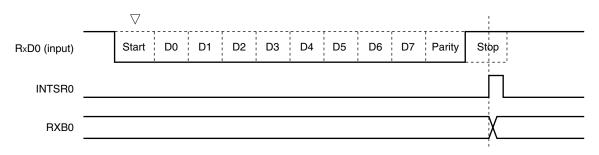

# (d) Reception

Reception is enabled and the RxD0 pin input is sampled when bit 7 (POWER0) of asynchronous serial interface operation mode register 0 (ASIM0) is set to 1 and then bit 5 (RXE0) of ASIM0 is set to 1.

The 5-bit counter of the baud rate generator starts counting when the falling edge of the RxD0 pin input is detected. When the set value of baud rate generator control register 0 (BRGC0) has been counted, the RxD0 pin input is sampled again ( $\bigtriangledown$ in Figure 14-10). If the RxD0 pin is low level at this time, it is recognized as a start bit.

When the start bit is detected, reception is started, and serial data is sequentially stored in receive shift register 0 (RXS0) at the set baud rate. When the stop bit has been received, the reception completion interrupt (INTSR0) is generated and the data of RXS0 is written to receive buffer register 0 (RXB0). If an overrun error (OVE0) occurs, however, the receive data is not written to RXB0.

Even if a parity error (PE0) occurs while reception is in progress, reception continues to the reception position of the stop bit, and an reception error interrupt (INTSR0) is generated after completion of reception. INTSR0 occurs upon completion of reception and in case of a reception error.

- Cautions 1. If a reception error occurs, read asynchronous serial interface reception error status register 0 (ASIS0) and then read receive buffer register 0 (RXB0) to clear the error flag. Otherwise, an overrun error will occur when the next data is received, and the reception error status will persist.

- 2. Reception is always performed with the "number of stop bits = 1". The second stop bit is ignored.

#### 18.7.3 Three-time-slice display example

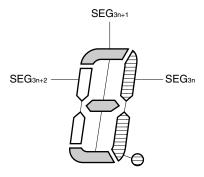

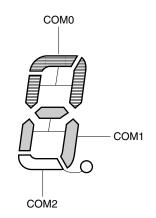

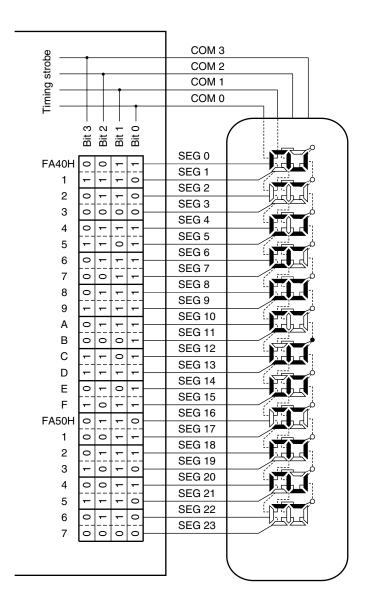

Figure 18-24 shows how the 8-digit LCD panel having the display pattern shown in Figure 18-23 is connected to the segment signals (SEG0 to SEG23) and the common signals (COM0 to COM2) of the 78K0/LF3 chip. This example displays data "123456.78" in the LCD panel. The contents of the display data memory (addresses FA40H to FA57H) correspond to this display.

The following description focuses on numeral "6." ( 5. ) displayed in the third digit. To display "6." in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG6 to SEG8 pins according to Table 18-8 at the timing of the common signals COM0 to COM2; see Figure 18-23 for the relationship between the segment signals and LCD segments.

| Segment | SEG6     | SEG7   | SEG8   |

|---------|----------|--------|--------|

| Common  |          |        |        |

| COM0    | Deselect | Select | Select |

| COM1    | Select   | Select | Select |

| COM2    | Select   | Select | -      |

Table 18-8. Select and Deselect Voltages (COM0 to COM2)

According to Table 18-8, it is determined that the display data memory location (FA46H) that corresponds to SEG6 must contain x110.

Figures 18-25 and 18-26 show examples of LCD drive waveforms between the SEG6 signal and each common signal in the 1/2 and 1/3 bias methods, respectively. When the select voltage is applied to SEG6 at the timing of COM1 or COM2, an alternate rectangle waveform, +VLCD/-VLCD, is generated to turn on the corresponding LCD segment.

**Remark** n = 0 to 7

LCD panel

Figure 18-28. Example of Connecting Four-Time-Slice LCD Panel

Data memory address

### 19.4.2 Manchester code generator mode

This mode is used to transmit data in Manchester code format using the MCGO pin.

## (1) Register description

MCG control register 0 (MC0CTL0), MCG control register 1 (MC0CTL1), and MCG control register 2 (MC0CTL2) are used to set the Manchester code generator mode.

# (a) MCG control register 0 (MC0CTL0)

This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 10H.

Address: FF4CH After reset: 10H R/W

| Symbol  | <7>    | 6 | 5 | <4>    | 3 | 2 | <1>    | <0>    |

|---------|--------|---|---|--------|---|---|--------|--------|

| MC0CTL0 | MC0PWR | 0 | 0 | MC0DIR | 0 | 0 | MC0OSL | MC0OLV |

| MC0PWR | Operation control |

|--------|-------------------|

| 0      | Operation stopped |

| 1      | Operation enabled |

| MC0DIR | First bit specification |

|--------|-------------------------|

| 0      | MSB                     |

| 1      | LSB                     |

| MC0OSL | Data format         |

|--------|---------------------|

| 0      | Manchester code     |

| 1      | Bit sequential data |

| MC00LV | Output level when transmission suspended |

|--------|------------------------------------------|

| 0      | Low level                                |

| 1      | High level                               |

Caution Clear (0) the MC0PWR bit before rewriting the MC0DIR, MC0OSL, and MC0OLV bits (it is possible to rewrite these bits by an 8-bit memory manipulation instruction at the same time when the MC0PWR bit is set (1)).

| Interrupt | Default                    |                         | Interrupt Source                                                                                                                                | Internal/ | Vector           | Basic                                   |

|-----------|----------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----------------------------------------|

| Туре      | Priority <sup>Note 1</sup> | Name                    | Trigger                                                                                                                                         | External  | Table<br>Address | Configuration<br>Type <sup>Note 2</sup> |

| Maskable  | 0                          | INTLVI                  | Low-voltage detection <sup>Note 3</sup>                                                                                                         | Internal  | 0004H            | (A)                                     |

|           | 1                          | INTP0                   | Pin input edge detection                                                                                                                        | External  | 0006H            | (B)                                     |

|           | 2                          | INTP1                   |                                                                                                                                                 |           | 0008H            |                                         |

|           | 3                          | INTP2                   |                                                                                                                                                 |           | 000AH            |                                         |

|           | 4                          | INTP3                   |                                                                                                                                                 |           | 000CH            |                                         |

|           | 5                          | INTP4                   |                                                                                                                                                 |           | 000EH            |                                         |

|           | 6                          | INTP5                   |                                                                                                                                                 |           | 0010H            |                                         |

|           | 7                          | INTSRE6                 | UART6 reception error generation                                                                                                                | Internal  | 0012H            | (A)                                     |

|           | 8                          | INTSR6                  | End of UART6 reception                                                                                                                          |           | 0014H            |                                         |

|           | 9                          | INTST6                  | End of UART6 transmission                                                                                                                       |           | 0016H            |                                         |

|           | 10                         | INTCSI10/<br>INTST0     | End of CSI10 communication/end of UART0 transmission                                                                                            |           | 0018H            |                                         |

|           | 11                         | INTTMH1                 | Match between TMH1 and CMP01<br>(when compare register is specified)                                                                            |           | 001AH            |                                         |

|           | 12                         | INTTMH0                 | Match between TMH0 and CMP00<br>(when compare register is specified)                                                                            |           | 001CH            |                                         |

|           | 13                         | INTTM50                 | Match between TM50 and CR50<br>(when compare register is specified)                                                                             |           | 001EH            |                                         |

|           | 14                         | INTTM000                | Match between TM00 and CR000<br>(when compare register is specified),<br>TI010 pin valid edge detection<br>(when capture register is specified) |           | 0020H            |                                         |

|           | 15                         | INTTM010                | Match between TM00 and CR010<br>(when compare register is specified),<br>TI000 pin valid edge detection<br>(when capture register is specified) |           | 0022H            |                                         |

|           | 16                         | INTAD <sup>Note 5</sup> | End of 10-bit successive approximation type<br>A/D conversion                                                                                   |           | 0024H            |                                         |

|           | 17                         | INTSR0                  | End of UART0 reception or reception error generation                                                                                            |           | 0026H            |                                         |

|           | 18                         | INTRTC                  | Fixed-cycle signal of real-time counter/alarm match detection                                                                                   |           | 0028H            |                                         |

|           | 19                         | INTTM51<br>Note 4       | Match between TM51 and CR51<br>(when compare register is specified)                                                                             |           | 002AH            |                                         |

|           | 20                         | INTKR                   | Key interrupt detection                                                                                                                         | External  | 002CH            | (C)                                     |

|           | 21                         | INTRTCI                 | Interval signal detection of real-time counter                                                                                                  | Internal  | 002EH            | (A)                                     |

| Table 21-1. | Interrupt Source List (1 | /2)  |

|-------------|--------------------------|------|

|             | Interrupt obtaile Elet ( | ··~/ |

**Notes 1.** The default priority determines the sequence of processing vectored interrupts if two or more maskable interrupts occur simultaneously. Zero indicates the highest priority and 28 indicates the lowest priority.

2. Basic configuration types (A) to (D) correspond to (A) to (D) in Figure 21-1.

3. When bit 1 (LVIMD) of the low-voltage detection register (LVIM) is cleared to 0.

4. When 8-bit timer/event counter 51 and 8-bit timer H1 are used in the carrier generator mode, an interrupt is generated upon the timing when the INTTM5H1 signal is generated (see Figure 8-15 Transfer Timing).

**5.**  $\mu$ PD78F048x and 78F049x only.

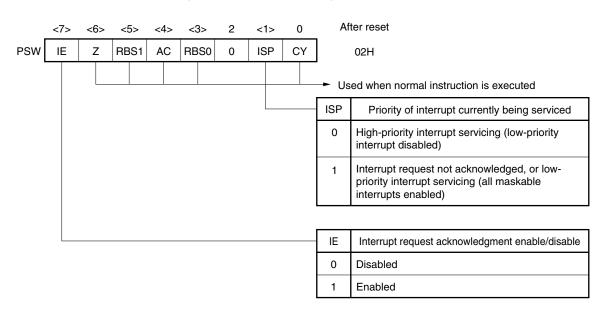

# (5) Program status word (PSW)

The program status word is a register used to hold the instruction execution result and the current status for an interrupt request. The IE flag that sets maskable interrupt enable/disable and the ISP flag that controls multiple interrupt servicing are mapped to the PSW.

Besides 8-bit read/write, this register can carry out operations using bit manipulation instructions and dedicated instructions (EI and DI). When a vectored interrupt request is acknowledged, if the BRK instruction is executed, the contents of the PSW are automatically saved into a stack and the IE flag is reset to 0. If a maskable interrupt request is acknowledged, the contents of the priority specification flag of the acknowledged interrupt are transferred to the ISP flag. The PSW contents are also saved into the stack with the PUSH PSW instruction. They are restored from the stack with the RETI, RETB, and POP PSW instructions.

Reset signal generation sets PSW to 02H.

Figure 21-6. Format of Program Status Word

# CHAPTER 25 POWER-ON-CLEAR CIRCUIT

# 25.1 Functions of Power-on-Clear Circuit

The power-on-clear circuit (POC) has the following functions.

- Generates internal reset signal at power on.

In the 1.59 V POC mode (option byte: POCMODE = 0), the reset signal is released when the supply voltage (V<sub>DD</sub>) exceeds 1.59 V ±0.15 V.

In the 2.7 V/1.59 V POC mode (option byte: POCMODE = 1), the reset signal is released when the supply voltage (V<sub>DD</sub>) exceeds 2.7 V ±0.2 V.

- Compares supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC</sub> = 1.59 V ±0.15 V), generates internal reset signal when V<sub>DD</sub> < V<sub>POC</sub>.

- Caution If an internal reset signal is generated in the POC circuit, the reset control flag register (RESF) is cleared to 00H.

- **Remark** 78K0/LF3 incorporates multiple hardware functions that generate an internal reset signal. A flag that indicates the reset source is located in the reset control flag register (RESF) for when an internal reset signal is generated by the watchdog timer (WDT) or low-voltage-detector (LVI). RESF is not cleared to 00H and the flag is set to 1 when an internal reset signal is generated by WDT or LVI. For details of RESF, see **CHAPTER 24 RESET FUNCTION**.

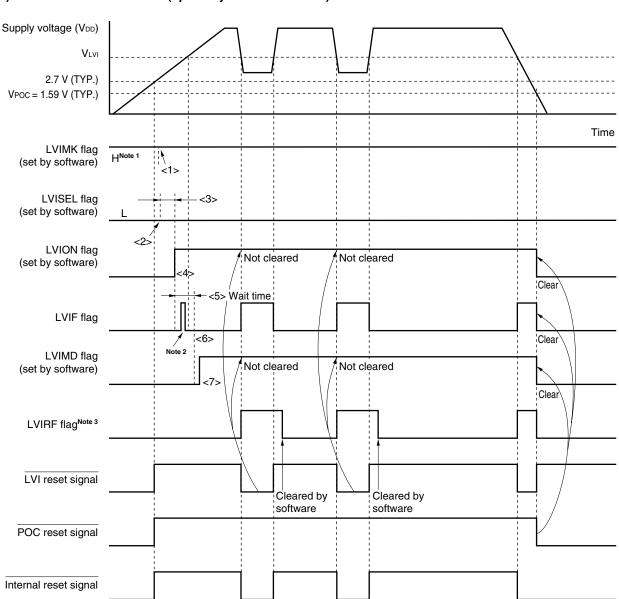

# Figure 26-5. Timing of Low-Voltage Detector Internal Reset Signal Generation (Detects Level of Supply Voltage (VDD)) (2/2)

**Notes 1.** The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIF flag may be set (1).

- 3. LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, see CHAPTER 24 RESET FUNCTION.

- **Remark** <1> to <7> in Figure 26-5 above correspond to <1> to <7> in the description of "When starting operation" in **26.4.1 (1) When detecting level of supply voltage (V**<sub>DD</sub>).

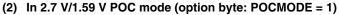

# Figure 26-9. Example of Software Processing After Reset Release (2/2)

Checking reset source

<R>

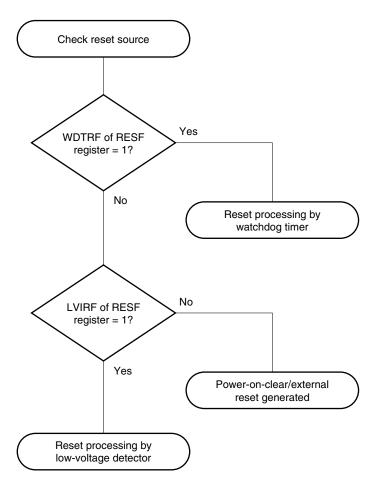

Figure 28-4. Example of Wiring Adapter for Flash Memory Writing in UART (UART6) Mode