Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 62                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0481gc-gad-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.5 78K0/Lx3 Microcontroller Series Lineup

| ROM   | RAM   | 78K0/LC3                         | 78K0/LD3                 | 78K0/LE3                               | 78K0/LF3                               |

|-------|-------|----------------------------------|--------------------------|----------------------------------------|----------------------------------------|

|       |       | 48 Pins                          | 52 Pins                  | 64 Pins                                | 80 Pins                                |

| 60 KB | 2 KB  | 1                                | -                        | µPD78F0465<br>µPD78F0455<br>µPD78F0455 | µPD78F0495<br>µPD78F0485<br>µPD78F0475 |

| 48 KB | 2 KB  | I                                | -                        | µPD78F0464<br>µPD78F0454<br>µPD78F0444 | µPD78F0494<br>µPD78F0484<br>µPD78F0474 |

| 32 KB | 1 KB  | μΡD78F0413<br>μΡD78F0403         | µPD78F0433<br>µPD78F0423 | µPD78F0463<br>µPD78F0453<br>µPD78F0443 | μΡD78F0493<br>μΡD78F0483<br>μΡD78F0473 |

| 24 KB | 1 KB  | μΡD78F0412<br>μΡD78F0402         | µPD78F0432<br>µPD78F0422 | µPD78F0462<br>µPD78F0452<br>µPD78F0442 | µPD78F0492<br>µPD78F0482<br>µPD78F0472 |

| 16 KB | 768 B | μ⁄PD78F0411<br>μ⁄PD78F0401       | µPD78F0431<br>µPD78F0421 | µPD78F0461<br>µPD78F0451<br>µPD78F0441 | μΡD78F0491<br>μΡD78F0481<br>μΡD78F0471 |

| 8 KB  | 512 B | <i>µ</i> PD78F0410<br>µPD78F0400 | μPD78F0430<br>μPD78F0420 | -                                      | -                                      |

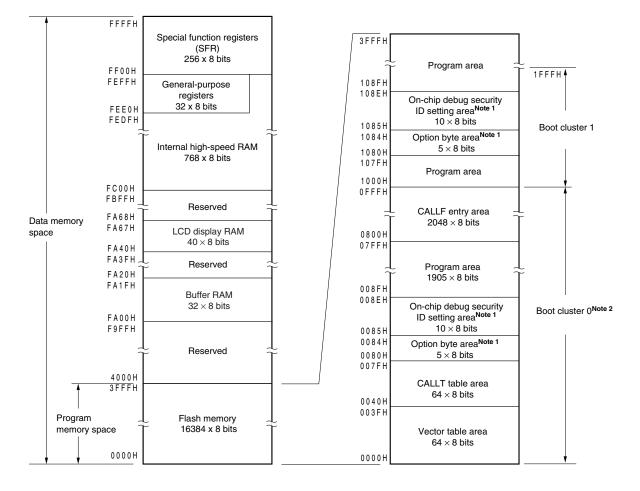

Figure 3-1. Memory Map (µPD78F0471, 78F0481)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 28.8 Security Setting).

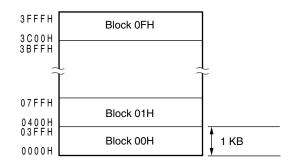

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

| Address | Special Function Register (SFR) Name |                                                        | Symbol | R/W   | Mani         | pulatable Bi | it Unit      | After |

|---------|--------------------------------------|--------------------------------------------------------|--------|-------|--------------|--------------|--------------|-------|

|         |                                      |                                                        |        | 1 Bit | 8 Bits       | 16 Bits      | Reset        |       |

| FF00H   | Receive buffer reg                   | ister 6                                                | RXB6   | R     | _            | $\checkmark$ | -            | FFH   |

| FF01H   | Port register 1                      |                                                        | P1     | R/W   |              | $\checkmark$ | -            | 00H   |

| FF02H   | Port register 2                      |                                                        | P2     | R/W   | $\checkmark$ |              | -            | 00H   |

| FF03H   | Port register 3                      |                                                        | P3     | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF04H   | Port register 4                      |                                                        | P4     | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF05H   | Transmit buffer reg                  | gister 6                                               | TXB6   | R/W   | _            | $\checkmark$ | -            | FFH   |

| FF06H   | 10-bit A/D convers                   | sion result register <sup>Note</sup>                   | ADCR   | R     | _            | _            | $\checkmark$ | 0000H |

| FF07H   |                                      | 8-bit A/D conversion result register H <sup>Note</sup> | ADCRH  | R     | _            | $\checkmark$ | _            | 00H   |

| FF08H   | Port register 8                      |                                                        | P8     | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF09H   | Port register 9                      |                                                        | P9     | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0AH   | Port register 10                     |                                                        | P10    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0BH   | Port register 11                     |                                                        | P11    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0CH   | Port register 12                     |                                                        | P12    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0DH   | Port register 13                     |                                                        | P13    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0EH   | Port register 14                     |                                                        | P14    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF0FH   | Port register 15                     |                                                        | P15    | R/W   | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF10H   | 16-bit timer counte                  | er 00                                                  | TM00   | R     | -            | -            | $\checkmark$ | 0000H |

| FF11H   |                                      |                                                        |        |       |              |              |              |       |

| FF12H   | 16-bit timer captur                  | CR000                                                  | R/W    | _     | -            | $\checkmark$ | 0000H        |       |

| FF13H   |                                      |                                                        |        |       |              |              |              |       |

| FF14H   | 16-bit timer captur                  | e/compare register 010                                 | CR010  | R/W   | _            | -            | $\checkmark$ | 0000H |

| FF15H   |                                      |                                                        |        |       |              |              |              |       |

| FF16H   | 8-bit timer counter                  | 50                                                     | TM50   | R     | -            |              | -            | 00H   |

| FF17H   | 8-bit timer compar                   | e register 50                                          | CR50   | R/W   | -            |              | -            | 00H   |

| FF18H   | 8-bit timer H comp                   | are register 00                                        | CMP00  | R/W   | -            |              | -            | 00H   |

| FF19H   | 8-bit timer H comp                   | are register 10                                        | CMP10  | R/W   | -            |              | -            | 00H   |

| FF1AH   | 8-bit timer H comp                   | are register 01                                        | CMP01  | R/W   | _            | $\checkmark$ | -            | 00H   |

| FF1BH   | 8-bit timer H comp                   |                                                        | CMP11  | R/W   | _            | $\checkmark$ | -            | 00H   |

| FF1FH   | Serial I/O shift regi                | ister 10                                               | SIO10  | R     | -            |              | -            | 00H   |

| FF20H   | Port function regis                  |                                                        | PF1    | R/W   |              | V            | -            | 00H   |

| FF21H   | Port mode register                   |                                                        | PM1    | R/W   | $\checkmark$ | $\checkmark$ | -            | FFH   |

| FF22H   | Port mode register                   |                                                        | PM2    | R/W   | V            | √            | -            | FFH   |

| FF23H   | Port mode register                   |                                                        | PM3    | R/W   | √            | √            | _            | FFH   |

| FF24H   | Port mode register                   |                                                        | PM4    | R/W   | V            | √            | _            | FFH   |

| FF28H   | Port mode register 8                 |                                                        | PM8    | R/W   | √            | √            | _            | FFH   |

| FF29H   | Port mode register 9                 |                                                        | PM9    | R/W   | √            | √            | -            | FFH   |

| FF2AH   | Port mode register                   | PM10                                                   | R/W    | √     | √            | -            | FFH          |       |

| FF2BH   | Port mode register                   |                                                        | PM11   | R/W   | /            | √            | -            | FFH   |

| FF2CH   | Port mode register                   | PM12                                                   | R/W    | √     | √            | -            | FFH          |       |

| FF2DH   | Port mode register                   |                                                        | PM13   | R/W   | √            | √            | -            | FFH   |

| FF2EH   | Port mode register                   |                                                        | PM14   | R/W   | √            | √            | -            | FFH   |

| FF2FH   | Port mode register                   | r 15                                                   | PM15   | R/W   |              |              | -            | FFH   |

| Table 3-8. | Special | Function | Register | List | (1/5) | ) |

|------------|---------|----------|----------|------|-------|---|

|------------|---------|----------|----------|------|-------|---|

**Note**  $\mu$ PD78F048x and 78F049x only.

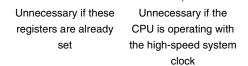

# Table 5-5. CPU Clock Transition and SFR Register Setting Examples (4/4)

#### (9) CPU clock changing from subsystem clock (D) to high-speed system clock (C)

| EXCLK | OSCSEL          | MSTOP                                                            | OSTC                | XSEL <sup>Note</sup>                | MCM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-----------------|------------------------------------------------------------------|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                 |                                                                  | Register            |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0     | 1               | 0                                                                | Must be<br>checked  | 1                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1     | 1               | 0                                                                | Must not be checked | 1                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | EXCLK<br>0<br>1 | EXCLK         OSCSEL           0         1           1         1 | 0 1 0               | 010Must be<br>checked110Must not be | Image: Second | Image: Second |

(Setting sequence of SFR registers)

- **Note** The value of this flag can be changed only once after a reset release. This setting is not necessary if it has already been set.

- Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (see CHAPTER 31 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS)).

- (10) HALT mode (E) set while CPU is operating with internal high-speed oscillation clock (B)

- HALT mode (F) set while CPU is operating with high-speed system clock (C)

- HALT mode (G) set while CPU is operating with subsystem clock (D)

| Status Transition                                         | Setting                    |

|-----------------------------------------------------------|----------------------------|

| $\begin{array}{l} (B) \to (E) \\ (C) \to (F) \end{array}$ | Executing HALT instruction |

| $(D) \rightarrow (G)$                                     |                            |

- (11) STOP mode (H) set while CPU is operating with internal high-speed oscillation clock (B)

- STOP mode (I) set while CPU is operating with high-speed system clock (C)

| (Setting sequence)                                                        |                                                                | <b>&gt;</b>                |

|---------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------|

| Status Transition                                                         | Set                                                            | ting                       |

| $\begin{array}{l} (B) \rightarrow (H) \\ (C) \rightarrow (I) \end{array}$ | Stopping peripheral functions that cannot operate in STOP mode | Executing STOP instruction |

**Remarks 1.** (A) to (I) in Table 5-5 correspond to (A) to (I) in Figure 5-15.

| 2. EXCLK, OSCSEL: | Bits 7 and 6 of the clock operation mode select register (OSCCTL) |

|-------------------|-------------------------------------------------------------------|

| MSTOP:            | Bit 7 of the main OSC control register (MOC)                      |

| XSEL, MCM0:       | Bits 2 and 0 of the main clock mode register (MCM)                |

| CSS:              | Bit 4 of the processor clock control register (PCC)               |

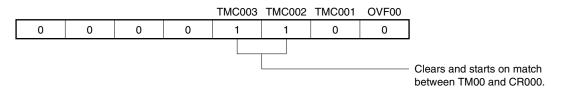

#### Figure 6-42. Example of Register Settings for PPG Output Operation

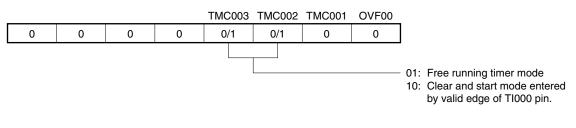

# (a) 16-bit timer mode control register 00 (TMC00)

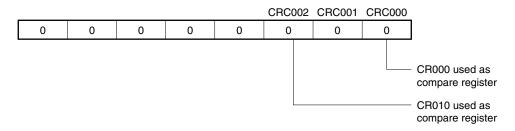

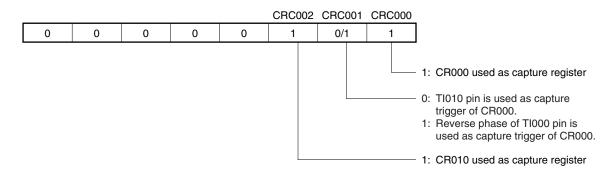

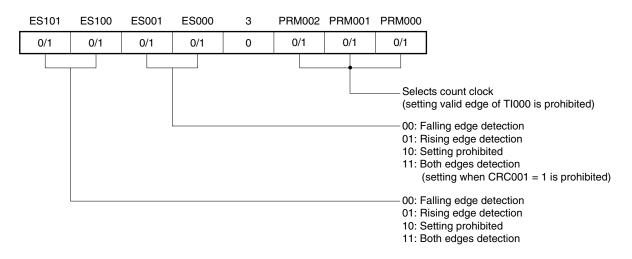

#### (b) Capture/compare control register 00 (CRC00)

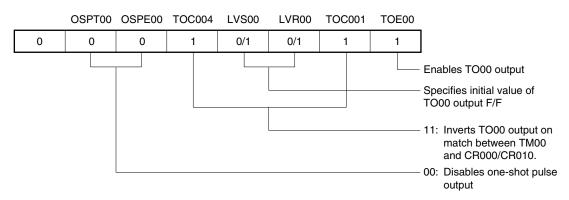

#### (c) 16-bit timer output control register 00 (TOC00)

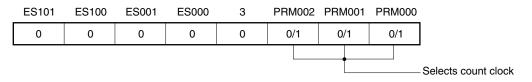

#### (d) Prescaler mode register 00 (PRM00)

# (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

#### (f) 16-bit capture/compare register 000 (CR000)

<R>

An interrupt signal (INTTM000) is generated when the value of this register matches the count value of TM00. The count value of TM00 is cleared.

# (g) 16-bit capture/compare register 010 (CR010)

An interrupt signal (INTTM010) is generated when the value of this register matches the count value of TM00. The count value of TM00 is not cleared.

# Caution Set values to CR000 and CR010 such that the condition $0000H \le CR010 < CR000 \le FFFFH$ is satisfied.

#### Figure 6-52. Example of Register Settings for Pulse Width Measurement (1/2)

# (a) 16-bit timer mode control register 00 (TMC00)

#### (b) Capture/compare control register 00 (CRC00)

## (c) 16-bit timer output control register 00 (TOC00)

| _ |   | OSPT00 | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

|---|---|--------|--------|--------|-------|-------|--------|-------|

|   | 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

#### (d) Prescaler mode register 00 (PRM00)

# (3) Real-time counter control register 1 (RTCC1)

The RTCC1 register is an 8-bit register that is used to control the alarm interrupt function and the wait time of the counter.

RTCC1 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

## Figure 9-4. Format of Real-Time Counter Control Register 1 (RTCC1) (1/2)

|                | After reacts OOL |     |

|----------------|------------------|-----|

| Address: FF8AH | After reset: 00H | R/W |

| Symbol | <7>  | <6>   | 5 | <4>  | <3>  | 2 | <1>  | <0>   |

|--------|------|-------|---|------|------|---|------|-------|

| RTCC1  | WALE | WALIE | 0 | WAFG | RIFG | 0 | RWST | RWAIT |

| WALE                                                                                                                                           | Alarm operation control     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|

| 0                                                                                                                                              | Match operation is invalid. |  |  |  |  |

| 1                                                                                                                                              | Match operation is valid.   |  |  |  |  |

| To set the registers of alarm (WALIE flag of RTCC1, ALARMWM register, ALARMWH register, and ALARMWW register), disable WALE (clear it to "0"). |                             |  |  |  |  |

| WALIE | Control of alarm interrupt (INTRTC) function operation |

|-------|--------------------------------------------------------|

| 0     | Does not generate interrupt on matching of alarm.      |

| 1     | Generates interrupt on matching of alarm.              |

| WAFG                                                                                                                    | Alarm detection status flag    |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| 0                                                                                                                       | Alarm mismatch                 |  |

| 1                                                                                                                       | Detection of matching of alarm |  |

| This is a status flag that indicates detection of matching with the alarm. It is valid only when WALE = 1 and is set to |                                |  |

"1" one clock (32.768 kHz) after matching of the alarm is detected. This flag is cleared when "0" is written to it. Writing "1" to it is invalid.

| RIFG                                                                                                                                              | Constant-period interrupt status flag       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| 0                                                                                                                                                 | Constant-period interrupt is not generated. |  |  |

| 1                                                                                                                                                 | Constant-period interrupt is generated.     |  |  |

| This flag indicates the status of generation of the constant-period interrupt. When the constant-period interrupt is generated, it is set to "1". |                                             |  |  |

This flag is cleared when "0" is written to it. Writing "1" to it is invalid.

| RWST                                                                                                                                                        | Wait status flag of real-time counter |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| 0                                                                                                                                                           | Counter is operating.                 |  |

| 1                                                                                                                                                           | Mode to read or write counter value   |  |

| This status flag indicates whether the setting of RWAIT is valid.<br>Before reading or writing the counter value, confirm that the value of this flag is 1. |                                       |  |

# CHAPTER 10 WATCHDOG TIMER

# 10.1 Functions of Watchdog Timer

The watchdog timer operates on the internal low-speed oscillation clock.

The watchdog timer is used to detect an inadvertent program loop. If a program loop is detected, an internal reset signal is generated.

Program loop is detected in the following cases.

- If the watchdog timer counter overflows

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to WDTE

- If data is written to WDTE during a window close period

- If the instruction is fetched from an area not set by the IMS and IXS registers (detection of an invalid check while the CPU hangs up)

- If the CPU accesses an area that is not set by the IMS and IXS registers (excluding FB00H to FFFFH) by executing a read/write instruction (detection of an abnormal access during a CPU program loop)

When a reset occurs due to the watchdog timer, bit 4 (WDTRF) of the reset control flag register (RESF) is set to 1. For details of RESF, see **CHAPTER 24 RESET FUNCTION**.

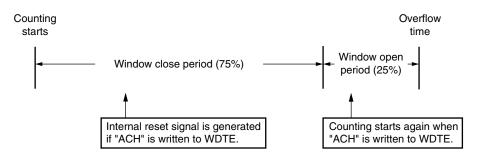

#### 10.4.3 Setting window open period of watchdog timer

Set the window open period of the watchdog timer by using bits 6 and 5 (WINDOW1, WINDOW0) of the option byte (0080H). The outline of the window is as follows.

- If "ACH" is written to WDTE during the window open period, the watchdog timer is cleared and starts counting again.

- Even if "ACH" is written to WDTE during the window close period, an abnormality is detected and an internal reset signal is generated.

Example: If the window open period is 25%

Caution The first writing to WDTE after a reset release clears the watchdog timer, if it is made before the overflow time regardless of the timing of the writing, and the watchdog timer starts counting again.

The window open period to be set is as follows.

| WINDOW1 | WINDOW0 | Window Open Period of Watchdog Timer |

|---------|---------|--------------------------------------|

| 0       | 0       | 25%                                  |

| 0       | 1       | 50%                                  |

| 1       | 0       | 75%                                  |

| 1       | 1       | 100%                                 |

Table 10-4. Setting Window Open Period of Watchdog Timer

Cautions 1. The combination of WDCS2 = WDCS1 = WDCS0 = 0 and WINDOW1 = WINDOW0 = 0 is prohibited.

2. The watchdog timer continues its operation during self-programming and EEPROM emulation of the flash memory. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.

# 12.4 10-Bit Successive Approximation Type A/D Converter Operations

#### 12.4.1 Basic operations of A/D converter

- <1> Set bit 0 (ADCE) of the A/D converter mode register (ADM) to 1 to start the operation of the comparator.

- <2> Set channels for A/D conversion to analog input by using the A/D port configuration register (ADPC0) and set to input mode by using port mode register 2 (PM2).

- <3> Set A/D conversion time by using bits 6 to 1 (FR3 to FR0, LV1, and LV0) of ADM.

- <4> Select one channel for A/D conversion using the analog input channel specification register (ADS).

- <5> Start the conversion operation by setting bit 7 (ADCS) of ADM to 1. (<6> to <12> are operations performed by hardware.)

- <6> The voltage input to the selected analog input channel is sampled by the sample & hold circuit.

- <7> When sampling has been done for a certain time, the sample & hold circuit is placed in the hold state and the sampled voltage is held until the A/D conversion operation has ended.

- <8> Bit 9 of the successive approximation register (SAR) is set. The series resistor string voltage tap is set to (1/2) AVREF by the tap selector.

- <9> The voltage difference between the series resistor string voltage tap and sampled voltage is compared by the voltage comparator. If the analog input is greater than (1/2) AVREF, the MSB of SAR remains set to 1. If the analog input is smaller than (1/2) AVREF, the MSB is reset to 0.

- <10> Next, bit 8 of SAR is automatically set to 1, and the operation proceeds to the next comparison. The series resistor string voltage tap is selected according to the preset value of bit 9, as described below.

- Bit 9 = 1: (3/4) AVREF

- Bit 9 = 0: (1/4) AVREF

The voltage tap and sampled voltage are compared and bit 8 of SAR is manipulated as follows.

- Analog input voltage  $\geq$  Voltage tap: Bit 8 = 1

- Analog input voltage < Voltage tap: Bit 8 = 0

- <11> Comparison is continued in this way up to bit 0 of SAR.

- <12> Upon completion of the comparison of 10 bits, an effective digital result value remains in SAR, and the result value is transferred to the A/D conversion result register (ADCR, ADCRH) and then latched.

At the same time, the A/D conversion end interrupt request (INTAD) can also be generated.

<13> Repeat steps <6> to <12>, until ADCS is cleared to 0.

To stop the A/D converter, clear ADCS to 0.

To restart A/D conversion from the status of ADCE = 1, start from <5>. To start A/D conversion again when ADCE = 0, set ADCE to 1, wait for 1  $\mu$ s or longer, and start <5>. To change a channel of A/D conversion, start from <4>.

# Caution Make sure the period of <1> to <5> is 1 $\mu$ s or more.

- **Remark** Two types of A/D conversion result registers are available.

- ADCR (16 bits): Store 10-bit A/D conversion value

- ADCRH (8 bits): Store 8-bit A/D conversion value

The conversion time can be derived from the sampling clock ( $f_{VP}$ ) and sampling count (N) via the following calculations.

Sampling time =  $1/f_{VP} \times N$ Initialization time = 1/operation clock +  $1/f_{VP} \times 256$ **Operation clock** ADDFS1-0 selected as 1, 1: fsub ADDFS1-0 selected as other than the above: fprs In serial mode <First conversion> Conversion time = Initialization time + sampling time =  $(1/\text{operation clock} + 1/\text{fvP} \times 256) + (1/\text{fvP} \times N)$ <After second conversion> Conversion time = Sampling time  $= 1/f_{VP} \times N$ In parallel mode <First conversion> Conversion time = Initialization time + sampling time =  $(1/\text{operation clock} + 1/\text{fvP} \times 256) + (1/\text{fvP} \times N)$ <After second conversion> Conversion time = Sampling time/4  $= 1/f_{VP} \times N/4$ fvp: sampling clock, N: 16-bit  $\Delta\Sigma$  type A/D sampling count

Caution If ADDCTL0 is rewritten (including the same values), conversion is assumed to have been restarted from that point and the conversion time of the first conversion is applied.

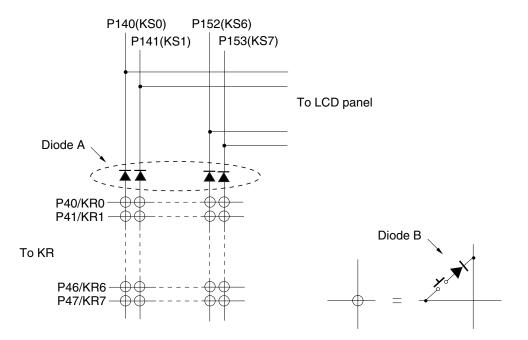

#### 18.9 Cautions When Using Segment Key Scan Function

#### (1) Conditions for use

Use the segment key scan function if  $V_{DD}$  is equal to  $V_{LCO}$ .

#### (2) Segment key scan input pins

Only the KR0 to KR7 pins can be used as input pins for the segment key scan function. Other pins cannot be used as input pins for the segment key scan function.

#### (3) Allowable input range of KR0 to KR7 pins

Due to a delay caused by a pull-up resistor, segment key scan input cannot be performed for the KR pin for a period of two fLCD clocks from the start of the segment key scan output period.

Similarly, due to input end processing, segment key scan input cannot be performed for the KR pin for the period of the last fLCD clock of the segment key scan output period.

# (4) Key return mode register (KRM) setting

When the segment key scan function is used (KSON = 1), set KRMn to 1 or 0 to use or not use the KRn pin as a segment key scan input pin.

#### (5) Circuit configuration

When using the segment key scan function, at least diode A or diode B shown in Figure 18-38 is required. The following problems will occur when diodes A and B are missing.

#### Figure 18-38. Key Matrix Configuration Example

## (2) Transmit operation

In bit sequential buffer mode, data is transmitted in 1- to 8-bit units. Transmission is enabled if bit 7 (MC0PWR) of MCG control register 0 (MC0CTL0) is set to 1.

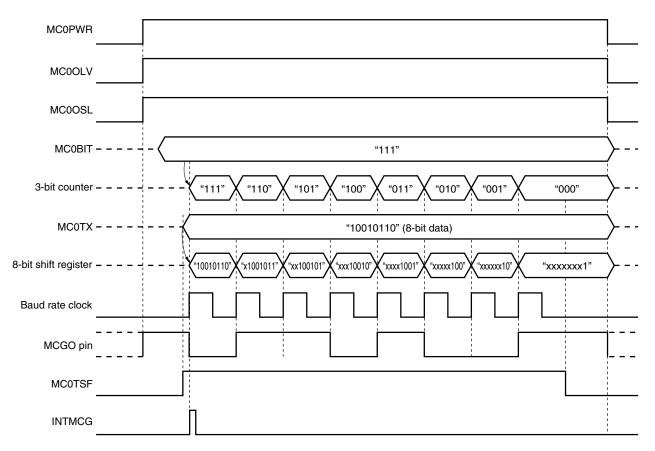

The output value while transmission is suspended can be set by using bit 0 (MC0OLV) of the MC0CTL0 register. A transmission starts by writing a value to the MCG transmit buffer register (MC0TX) after setting the transmit data bit length to the MCG transmit bit count specification register (MC0BIT). At the transmission start timing, the MC0BIT value is transferred to the 3-bit counter and data of MC0TX is transferred to the 8-bit shift register. An interrupt request signal (INTMCG) occurs at the timing that the MC0TX value is transferred to the 8-bit shift register. The 8-bit shift register is continuously shifted by the baud rate clock and is output from the MCGO pin. When continuous transmission is executed, the next data is set to MC0BIT and MC0TX during data transmission after INTMCG occurs.

To transmit continuously, writing the next transfer data to MC0TX must be complete within the period (3) and (4) in Figure 19-9. Rewrite MC0BIT before writing to MC0TX during continuous transmission.

#### Figure 19-9. Timing of Bit Sequential Buffer Mode (LSB First) (1/4)

#### (1) Transmit timing (MC0OLV = 1, total transmit bit length = 8 bits)

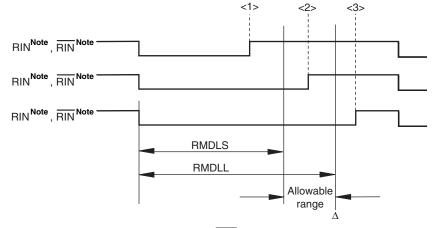

## (3) Data low level width determination

**Note** RIN is generated in type A reception mode, and RIN is generated in type B and type C reception modes.

| Relationship Between RMDLS/RMDLL/Counter | Position of Waveform  | Corresponding Operation                                                                                      |

|------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|

| Counter < RMDLS                          | <1>: Short            | Error interrupt INTRERR is generated <sup>note</sup> .<br>Measuring guide pulse high-level width is started. |

| $RMDLS \leq counter < RMDLL$             | <2>: Within the range | Measuring data high-level width is started.                                                                  |

| RMDLL ≤ counter                          | <3>: Long             | (Type A reception mode)                                                                                      |

|                                          |                       | Measuring the end width is started from the $\Delta$ point.                                                  |

|                                          |                       | (Type B, Type C reception modes)                                                                             |

|                                          |                       | Error interrupt INTRERR is generated at the $\Delta$ point. <sup>note</sup> .                                |

**Note** In type C reception mode, before the first INTDFULL interrupt is generated, INTRERR will not be generated. However, RMSR and RMSCR will be cleared.

| Interrupt                   | Default                    |                                            | Interrupt Source                                                                         | Internal/ | Vector           | Basic                                   |  |

|-----------------------------|----------------------------|--------------------------------------------|------------------------------------------------------------------------------------------|-----------|------------------|-----------------------------------------|--|

| Туре                        | Priority <sup>Note 1</sup> | Name                                       | Trigger                                                                                  | External  | Table<br>Address | Configuration<br>Type <sup>Note 2</sup> |  |

| Maskable                    | 22                         | INTDSAD <sup>Note 4</sup>                  | End of 16-bit $\Delta\Sigma$ type A/D conversion                                         | Internal  | 0030H            | (A)                                     |  |

|                             | 23                         | INTTM52                                    | Match between TM52 and CR52<br>(when compare register is specified)                      |           | 0032H            |                                         |  |

|                             | 24                         | INTTMH2                                    | Match between TMH2 and CRH2<br>(when compare register is specified)                      |           | 0034H            |                                         |  |

|                             | 25                         | INTMCG                                     | End of Manchester code reception                                                         |           | 0036H            |                                         |  |

|                             | 26                         | INTRIN                                     | Remote controller reception edge detection                                               |           | 0038H            |                                         |  |

|                             | 27                         | INTRERR/<br>INTGP/<br>INTREND/<br>INTDFULL | Remote controller guide pulse detection<br>/ Remote controller data reception completion |           | 003AH            |                                         |  |

| 28 INTACSI End of CSIA0 com |                            | End of CSIA0 communication                 | -                                                                                        | 003CH     |                  |                                         |  |

| Software                    | _                          | BRK                                        | BRK instruction execution                                                                | -         | 003EH            | (D)                                     |  |

| Reset                       | -                          | RESET                                      | Reset input                                                                              | -         | 0000H            | _                                       |  |

|                             |                            |                                            | Power-on clear<br>Low-voltage detection <sup>Note 3</sup>                                |           |                  |                                         |  |

| WDT WDT overflow            |                            | WDT overflow                               |                                                                                          |           |                  |                                         |  |

| Table 21-1 | Interrupt Source | 1 ict (2/2) |

|------------|------------------|-------------|

|            | interrupt Source | LISL (2/2)  |

**Notes 1.** The default priority determines the sequence of processing vectored interrupts if two or more maskable interrupts occur simultaneously. Zero indicates the highest priority and 28 indicates the lowest priority.

2. Basic configuration types (A) to (D) correspond to (A) to (D) in Figure 21-1.

3. When bit 1 (LVIMD) of the low-voltage detection register (LVIM) is set to 1.

**4.** *μ*PD78F049x only.

#### 21.4.3 Multiple interrupt servicing

Multiple interrupt servicing occurs when another interrupt request is acknowledged during execution of an interrupt. Multiple interrupt servicing does not occur unless the interrupt request acknowledgment enabled state is selected (IE = 1). When an interrupt request is acknowledged, interrupt request acknowledgment becomes disabled (IE = 0). Therefore, to enable multiple interrupt servicing, it is necessary to set (1) the IE flag with the EI instruction during interrupt servicing to enable interrupt acknowledgment.

Moreover, even if interrupts are enabled, multiple interrupt servicing may not be enabled, this being subject to interrupt priority control. Two types of priority control are available: default priority control and programmable priority control is used for multiple interrupt servicing.

In the interrupt enabled state, if an interrupt request with a priority equal to or higher than that of the interrupt currently being serviced is generated, it is acknowledged for multiple interrupt servicing. If an interrupt with a priority lower than that of the interrupt currently being serviced is generated during interrupt servicing, it is not acknowledged for multiple interrupt servicing. Interrupt requests that are not enabled because interrupts are in the interrupt disabled state or because they have a lower priority are held pending. When servicing of the current interrupt ends, the pending interrupt request is acknowledged following execution of at least one main processing instruction execution.

Table 21-5 shows relationship between interrupt requests enabled for multiple interrupt servicing and Figure 21-10 shows multiple interrupt servicing examples.

Table 21-5. Relationship Between Interrupt Requests Enabled for Multiple Interrupt Servicing

During Interrupt Servicing

| Multiple Interrupt Request |         | Maskable Interrupt Request |        |        |        | Software  |  |

|----------------------------|---------|----------------------------|--------|--------|--------|-----------|--|

|                            |         | PR = 0                     |        | PR = 1 |        | Interrupt |  |

| Interrupt Being Serviced   |         | IE = 1                     | IE = 0 | IE = 1 | IE = 0 | Request   |  |

| Maskable interrupt         | ISP = 0 | 0                          | ×      | ×      | ×      | 0         |  |

|                            | ISP = 1 | 0                          | ×      | 0      | ×      | 0         |  |

| Software interrupt         |         | 0                          | ×      | 0      | ×      | 0         |  |

Remarks 1. O: Multiple interrupt servicing enabled

- 2. x: Multiple interrupt servicing disabled

- 3. ISP and IE are flags contained in the PSW.

- ISP = 0: An interrupt with higher priority is being serviced.

- ISP = 1: No interrupt request has been acknowledged, or an interrupt with a lower priority is being serviced.

- IE = 0: Interrupt request acknowledgment is disabled.

- IE = 1: Interrupt request acknowledgment is enabled.

- 4. PR is a flag contained in PR0L, PR0H, PR1L, and PR1H.

- PR = 0: Higher priority level

- PR = 1: Lower priority level

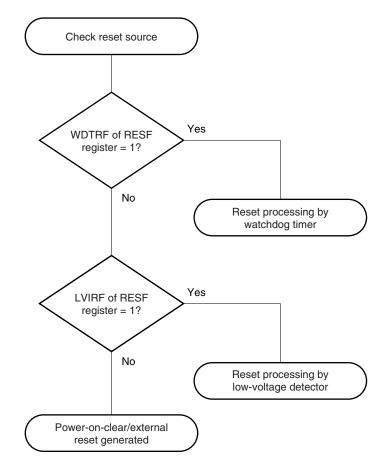

Figure 25-3. Example of Software Processing After Reset Release (2/2)

Checking reset source

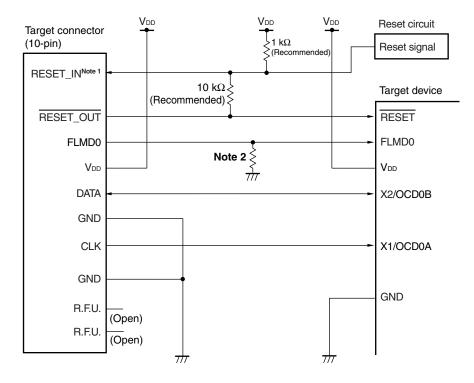

# 29.1 Connecting QB-MINI2 to 78K0/LF3

The 78K0/LF3 uses the V<sub>DD</sub>, FLMD0, RESET, OCD0A/X1, OCD0B/X2, and V<sub>ss</sub> pins to communicate with the host machine via an on-chip debug emulator (QB-MINI2).

Caution The 78K0/LF3 has an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. NEC Electronics is not liable for problems occurring when the on-chip debug function is used.

Figure 29-1. Connection Example of QB-MINI2 and 78K0/LF3

- **Notes 1.** This connection is designed assuming that the reset signal is output from the N-ch open-drain buffer (output resistance: 100  $\Omega$  or less). For details, refer to **QB-MINI2 User's Manual (U18371E)**.

- **2.** Make pull-down resistor 470  $\Omega$  or more (10 k $\Omega$ : recommended).

Caution Input the clock from the OCD0A/X1 pin during on-chip debugging.

#### <R> Recommended Oscillator Constants

| (1) X1 Oscillator: C | eramic resonator (T | ▲ = –40 to +85°C) |

|----------------------|---------------------|-------------------|

|                      |                     |                   |

| Manufacturer     | Part Number     | SMD/ Lead | Frequency<br>(MHz) | Recommended circuit<br>invariable |               | Oscillation<br>Voltage Range |         |

|------------------|-----------------|-----------|--------------------|-----------------------------------|---------------|------------------------------|---------|

|                  |                 |           |                    | C1 (pF)                           | C2 (pF)       | MIN.(V)                      | MAX.(V) |

| Murata Mfg.      | CSTCC2M00G56-R0 | SMD       | 2.00               | Internal (47)                     | Internal (47) | 1.8                          | 5.5     |

|                  | CSTLS4M00G56-B0 | Lead      | 4.00               | Internal (47)                     | Internal (47) |                              |         |

|                  | CSTCR4M00G55-R0 | SMD       |                    | Internal (39)                     | Internal (39) |                              |         |

|                  | CSTLS4M19G56-B0 | Lead      | 4.194              | Internal (47)                     | Internal (47) |                              |         |

|                  | CSTCR4M19G55-R0 | SMD       |                    | Internal (39)                     | Internal (39) |                              |         |

|                  | CSTLS4M91G56-B0 | Lead      | 4.915              | Internal (47)                     | Internal (47) | 2.0                          |         |

|                  | CSTCR4M91G55-R0 | SMD       |                    | Internal (39)                     | Internal (39) | 1.8                          |         |

|                  | CSTLS5M00G56-B0 | Lead      | 5.00               | Internal (47)                     | Internal (47) | 2.0                          |         |

|                  | CSTCR5M00G55-R0 | SMD       |                    | Internal (39)                     | Internal (39) | 1.8                          |         |

|                  | CSTLS6M00G56-B0 | Lead      | 6.00               | Internal (47)                     | Internal (47) | 2.2                          |         |

|                  | CSTCR6M00G55-R0 | SMD       |                    | Internal (39)                     | Internal (39) | 1.9                          |         |

|                  | CSTLS8M00G56-B0 | Lead      | 8.00               | Internal (47)                     | Internal (47) | 2.2                          |         |

|                  | CSTCE8M00G55-R0 | SMD       |                    | Internal (33)                     | Internal (33) | 1.8                          |         |

|                  | CSTLS8M38G56-B0 | Lead      | 8.388              | Internal (47)                     | Internal (47) | 2.2                          |         |

|                  | CSTCE8M38G55-R0 | SMD       |                    | Internal (33)                     | Internal (33) | 1.8                          |         |

|                  | CSTLS10M0G53-B0 | SMD       | 10.0               | Internal (15)                     | Internal (15) | 1.8                          |         |

|                  | CSTCE10M0G55-R0 | SMD       |                    | Internal (33)                     | Internal (33) | 2.1                          |         |

| Murata Mfg.      | CSTLS4M91G53-B0 | Lead      | 4.915              | Internal (15)                     | Internal (15) | 1.8                          | 5.5     |

| (low-capacitance | CSTLS5M00G53-B0 | Lead      | 5.00               | Internal (15)                     | Internal (15) | 1.8                          |         |

| products)        | CSTCR6M00G53-R0 | SMD       | 6.00               | Internal (15)                     | Internal (15) | 1.8                          | 1       |

|                  | CSTLS6M00G53-B0 | Lead      |                    | Internal (15)                     | Internal (15) | 1.8                          | 1       |

|                  | CSTLS8M00G53-B0 | Lead      | 8.00               | Internal (15)                     | Internal (15) | 1.8                          | 1       |

|                  | CSTLS8M38G53-B0 | Lead      | 8.388              | Internal (15)                     | Internal (15) | 1.8                          | 1       |

|                  | CSTCE10M0G52-R0 | SMD       | 10.0               | Internal (10)                     | Internal (10) | 1.8                          | ĺ       |

Caution The oscillator constants shown above are reference values based on evaluation in a specific environment by the resonator manufacturer. If it is necessary to optimize the oscillator characteristics in the actual application, apply to the resonator manufacturer for evaluation on the implementation circuit. The oscillation voltage and oscillation frequency only indicate the oscillator characteristic. Use the 78K0/LF3 so that the internal operation conditions are within the specifications of the DC and AC characteristics.

| QB-MINI2<br>On-chip debug emulator with<br>programming function | This on-chip debug emulator serves to debug hardware and software when developing application systems using the 78K0/Lx3. It is available also as flash memory programmer dedicated to microcontrollers with on-chip flash memory. When using this as on-chip debug emulator, it should be used in combination with a connection cable (10-pin cable or 16-pin cable), a USB interface cable that is used to connect the host machine, and the 78K0-OCD board. |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target connector specifications                                 | 10-pin general-purpose connector (2.54 mm pitch) or 16-pin general-purpose connector (2.54 mm pitch)                                                                                                                                                                                                                                                                                                                                                           |

#### A.5.2 When using on-chip debug emulator with programming function QB-MINI2

- **Remarks 1.** The QB-MINI2 is supplied with a USB interface cable, connection cables (10-pin and 16-pin cables), and the 78K0-OCD board. The connection cable (10-pin cable) and the 78K0-OCD board are used only when using the on-chip debug function.

- 2. Download the software for operating the QB-MINI2 from the download site for development tools (http://www.necel.com/micro/ods/eng/index.html).

# A.6 Debugging Tools (Software)

| ID78K0-QB<br>Integrated debugger | This debugger supports the in-circuit emulators for the 78K0 microcontrollers. The ID78K0-QB is a Windows-based software.<br>It has improved C-compatible debugging functions and can display the results of tracing with the source program using an integrating window function that associates the source program, disassemble display, and memory display with the trace result. It should be |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | used in combination with the device file (sold separately).                                                                                                                                                                                                                                                                                                                                       |

|                                  | Part number: µS××××ID78K0-QB                                                                                                                                                                                                                                                                                                                                                                      |

**Remark** ×××× in the part number differs depending on the host machine and OS used.

# $\mu S_{\underline{\times \times \times \times}}$ ID78K0-QB

| <br>×××× | Host Machine          | OS                         | Supply Medium |

|----------|-----------------------|----------------------------|---------------|

| AB17     | PC-9800 series,       | Windows (Japanese version) | CD-ROM        |

| BB17     | IBM PC/AT compatibles | Windows (English version)  |               |