Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 62                                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0484gk-gak-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CHAPTER 20 REMOTE CONTROLLER RECEIVER                | 596 |

|------------------------------------------------------|-----|

| 20.1 Remote Controller Receiver Functions            |     |

| 20.2 Remote Controller Receiver Configuration        |     |

| 20.3 Registers to Control Remote Controller Receiver |     |

| 20.4 Operation of Remote Controller Receiver         | 607 |

| 20.4.1 Format of type A reception mode               | 607 |

| 20.4.2 Operation flow of type A reception mode       | 607 |

| 20.4.3 Format of type B reception mode               | 609 |

| 20.4.4 Operation flow of type B reception mode       | 609 |

| 20.4.5 Format of type C reception mode               | 611 |

| 20.4.6 Operation flow of type C reception mode       | 611 |

| 20.4.7 Timing                                        | 613 |

| 20.4.8 Compare register setting                      | 617 |

| 20.4.9 Error interrupt generation timing             | 619 |

| 20.4.10 Noise elimination                            | 625 |

| CHAPTER 21 INTERRUPT FUNCTIONS                       | 628 |

| 21.1 Interrupt Function Types                        |     |

| 21.2 Interrupt Sources and Configuration             | 628 |

| 21.3 Registers Controlling Interrupt Functions       | 633 |

| 21.4 Interrupt Servicing Operations                  | 641 |

| 21.4.1 Maskable interrupt acknowledgment             | 641 |

| 21.4.2 Software interrupt request acknowledgment     | 643 |

| 21.4.3 Multiple interrupt servicing                  | 644 |

| 21.4.4 Interrupt request hold                        | 647 |

| CHAPTER 22 KEY INTERRUPT FUNCTION                    | 648 |

| 22.1 Functions of Key Interrupt                      |     |

| 22.2 Configuration of Key Interrupt                  |     |

| 22.3 Register Controlling Key Interrupt              | 649 |

| CHAPTER 23 STANDBY FUNCTION                          | 650 |

| 23.1 Standby Function and Configuration              | 650 |

| 23.1.1 Standby function                              | 650 |

| 23.1.2 Registers controlling standby function        | 651 |

| 23.2 Standby Function Operation                      | 653 |

| 23.2.1 HALT mode                                     | 653 |

| 23.2.2 STOP mode                                     | 658 |

| CHAPTER 24 RESET FUNCTION                            | 664 |

| 24.1 Register for Confirming Reset Source            | 673 |

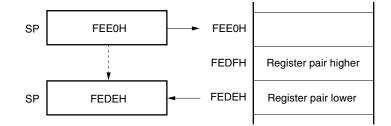

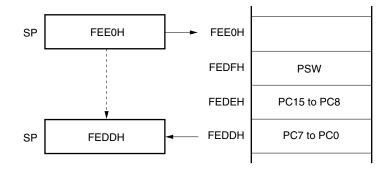

# Figure 3-24. Data to Be Saved to Stack Memory

# (a) PUSH rp instruction (when SP = FEE0H)

(b) CALL, CALLF, CALLT instructions (when SP = FEE0H)

(c) Interrupt, BRK instructions (when SP = FEE0H)

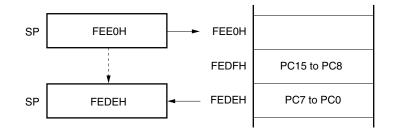

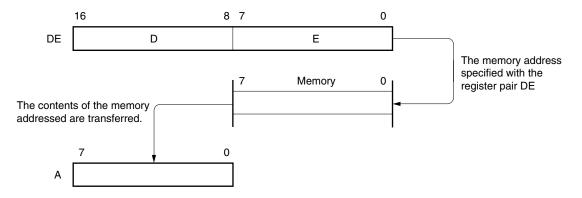

## 3.4.6 Register indirect addressing

# [Function]

Register pair contents specified by a register pair specify code in an instruction word and by a register bank select flag (RBS0 and RBS1) serve as an operand address for addressing the memory. This addressing can be carried out for all of the memory spaces.

# [Operand format]

| Identifier | Description |

|------------|-------------|

| -          | [DE], [HL]  |

1

## [Description example]

MOV A, [DE]; when selecting [DE] as register pair

Operation code

0 0 0 0 1 0 1

# [Illustration]

# 4.2 Port Configuration

Ports include the following hardware.

# Table 4-3. Port Configuration

| Item              | Configuration                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Control registers | Port mode register (PM1 to PM4, PM8 to PM15)<br>Port register (P1 to P4, P8 to P15)<br>Pull-up resistor option register (PU1, PU3, PU4, PU8 to PU15)<br>Port function register 1 (PF1)<br>Port function register 2 (PF2) <sup>Note 1</sup><br>Port function register ALL (PFALL)<br>A/D port configuration register 0 (ADPC0) <sup>Note 2</sup> |  |

| Port              | Total: 62                                                                                                                                                                                                                                                                                                                                       |  |

| Pull-up resistor  | Total: 50                                                                                                                                                                                                                                                                                                                                       |  |

**Notes 1.**  $\mu$ PD78F047x and 78F048x only

**2.** *μ*PD78F048x and 78F049x only

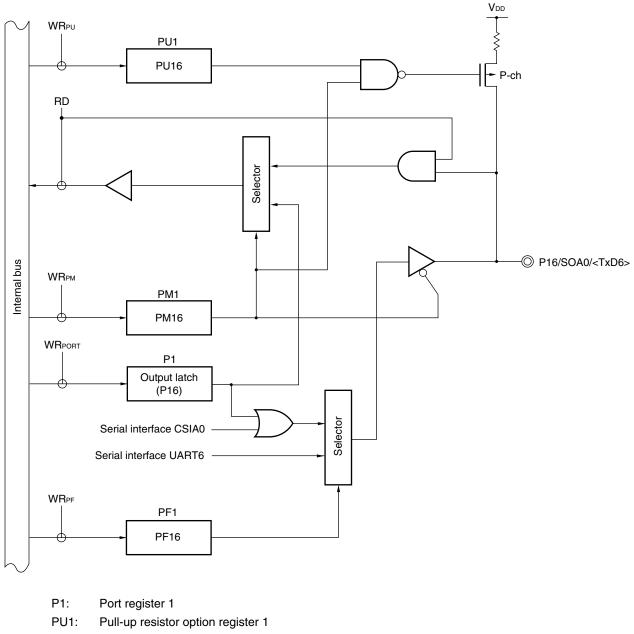

Figure 4-6. Block Diagram of P16

PM1: Port mode register 1

PF1: Port function register 1

- RD: Read signal

- WR××: Write signal

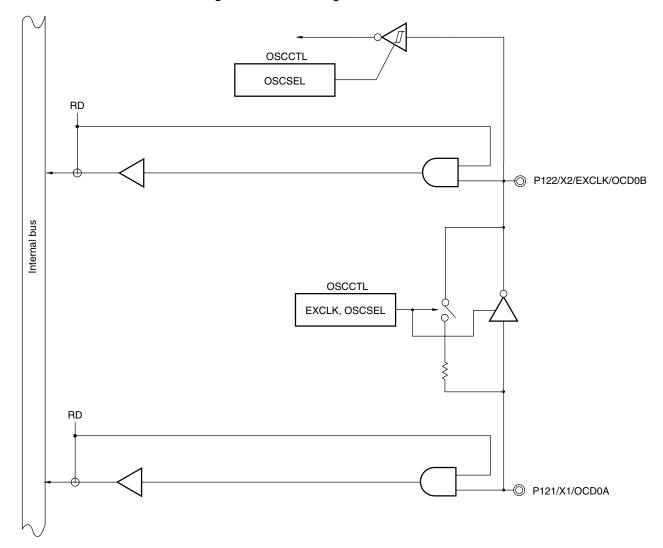

Figure 4-22. Block Diagram of P121 and P122

OSCCTL: Clock operation mode select register RD: Read signal

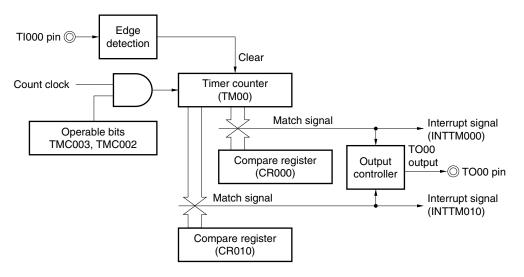

### 6.4.4 Operation in clear & start mode entered by TI000 pin valid edge input

When bits 3 and 2 (TMC003 and TMC002) of 16-bit timer mode control register 00 (TMC00) are set to 10 (clear & start mode entered by the TI000 pin valid edge input) and the count clock (set by PRM00) is supplied to the timer/event counter, TM00 starts counting up. When the valid edge of the TI000 pin is detected during the counting operation, TM00 is cleared to 0000H and starts counting up again. If the valid edge of the TI000 pin is not detected, TM00 overflows and continues counting.

The valid edge of the TI000 pin is a cause to clear TM00. Starting the counter is not controlled immediately after the start of the operation.

CR000 and CR010 are used as compare registers and capture registers.

## (a) When CR000 and CR010 are used as compare registers

Signals INTTM000 and INTTM010 are generated when the value of TM00 matches the value of CR000 and CR010.

#### (b) When CR000 and CR010 are used as capture registers

The count value of TM00 is captured to CR000 and the INTTM000 signal is generated when the valid edge is input to the TI010 pin (or when the phase reverse to that of the valid edge is input to the TI000 pin). When the valid edge is input to the TI000 pin, the count value of TM00 is captured to CR010 and the INTTM010 signal is generated. As soon as the count value has been captured, the counter is cleared to 0000H.

# Caution Do not set the count clock as the valid edge of the TI000 pin (PRM002, PRM001, and PRM000 = 110). When PRM002, PRM001, and PRM000 = 110, TM00 is cleared.

- Remarks 1. For the setting of the I/O pins, see 6.3 (6) Port mode register 3 (PM3).

- 2. For how to enable the INTTM000 signal interrupt, see CHAPTER 21 INTERRUPT FUNCTIONS.

# (1) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: compare register, CR010: compare register)

# Figure 6-23. Block Diagram of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Compare Register, CR010: Compare Register)

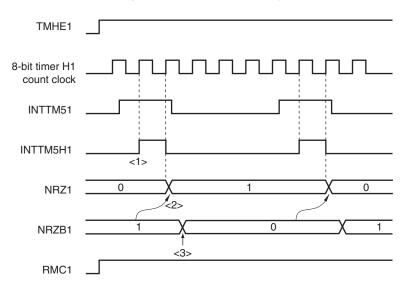

To control the carrier pulse output during a count operation, the NRZ1 and NRZB1 bits of the TMCYC1 register have a master and slave bit configuration. The NRZ1 bit is read-only but the NRZB1 bit can be read and written. The INTTM51 signal is synchronized with the 8-bit timer H1 count clock and is output as the INTTM5H1 signal. The INTTM5H1 signal becomes the data transfer signal of the NRZ1 bit, and the NRZB1 bit value is transferred to the NRZ1 bit. The timing for transfer from the NRZB1 bit to the NRZ1 bit is as shown below.

Figure 8-15. Transfer Timing

- <1> The INTTM51 signal is synchronized with the count clock of the 8-bit timer H1 and is output as the INTTM5H1 signal.

- <2> The value of the NRZB1 bit is transferred to the NRZ1 bit at the second clock from the rising edge of the INTTM5H1 signal.

- <3> Write the next value to the NRZB1 bit in the interrupt servicing program that has been started by the INTTM5H1 interrupt or after timing has been checked by polling the interrupt request flag. Write data to count the next time to the CR51 register.

- Cautions 1. Do not rewrite the NRZB1 bit again until at least the second clock after it has been rewritten, or else the transfer from the NRZB1 bit to the NRZ1 bit is not guaranteed.

- 2. When the 8-bit timer/event counter 51 is used in the carrier generator mode, an interrupt is generated at the timing of <1>. When the 8-bit timer/event counter 51 is used in a mode other than the carrier generator mode, the timing of the interrupt generation differs.

- **Remark** INTTM5H1 is an internal signal and not an interrupt source.

## (2) Asynchronous serial interface reception error status register 0 (ASIS0)

This register indicates an error status on completion of reception by serial interface UART0. It includes three error flag bits (PE0, FE0, OVE0).

This register is read-only by an 8-bit memory manipulation instruction.

Reset signal generation, or clearing bit 7 (POWER0) or bit 5 (RXE0) of ASIM0 to 0 clears this register to 00H. 00H is read when this register is read. If a reception error occurs, read ASIS0 and then read receive buffer register 0 (RXB0) to clear the error flag.

# Figure 14-3. Format of Asynchronous Serial Interface Reception Error Status Register 0 (ASIS0)

Address: FF73H After reset: 00H R

| 0, |    | 100 |   |

|----|----|-----|---|

| A  | SI | S   | כ |

| Symbol | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    |

|--------|---|---|---|---|---|-----|-----|------|

| ASIS0  | 0 | 0 | 0 | 0 | 0 | PE0 | FE0 | OVE0 |

| PE0 | Status flag indicating parity error                                                      |

|-----|------------------------------------------------------------------------------------------|

| 0   | If POWER0 = 0 or RXE0 = 0, or if ASIS0 register is read.                                 |

| 1   | If the parity of transmit data does not match the parity bit on completion of reception. |

| FE0 | Status flag indicating framing error                        |

|-----|-------------------------------------------------------------|

| 0   | If POWER0 = 0 or RXE0 = 0, or if ASIS0 register is read.    |

| 1   | If the stop bit is not detected on completion of reception. |

| OVE0 | Status flag indicating overrun error                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------|

| 0    | If POWER0 = 0 and RXE0 = 0, or if ASIS0 register is read.                                                          |

| 1    | If receive data is set to the RXB0 register and the next reception operation is completed before the data is read. |

- Cautions 1. The operation of the PE0 bit differs depending on the set values of the PS01 and PS00 bits of asynchronous serial interface operation mode register 0 (ASIM0).

- 2. Only the first bit of the receive data is checked as the stop bit, regardless of the number of stop bits.

- 3. If an overrun error occurs, the next receive data is not written to receive buffer register 0 (RXB0) but discarded.

- 4. If data is read from ASIS0, a wait cycle is generated. Do not read data from ASIS0 when the CPU is operating on the subsystem clock and the peripheral hardware clock is stopped. For details, see CHAPTER 34 CAUTIONS FOR WAIT.

## (2) Error of baud rate

The baud rate error can be calculated by the following expression.

- Error (%) =  $\left(\frac{\text{Actual baud rate (baud rate with error)}}{\text{Desired baud rate (correct baud rate)}} 1\right) \times 100 [\%]$

- Cautions 1. Keep the baud rate error during transmission to within the permissible error range at the reception destination.

- 2. Make sure that the baud rate error during reception satisfies the range shown in (4) Permissible baud rate range during reception.

- Example: Frequency of base clock = 10 MHz = 10,000,000 Hz Set value of MDL67 to MDL60 bits of BRGC6 register = 00100001B (k = 33) Target baud rate = 153600 bps

Baud rate = 10 M / (2 × 33) = 10000000 / (2 × 33) = 151,515 [bps]

Error = (151515/153600 - 1) × 100 = -1.357 [%]

# 16.3 Registers Controlling Serial Interface CSI10

Serial interface CSI10 is controlled by the following five registers.

- Serial operation mode register 10 (CSIM10)

- Serial clock selection register 10 (CSIC10)

- Port function register 1 (PF1)

- Port mode register 1 (PM1)

- Port register 1 (P1)

## (1) Serial operation mode register 10 (CSIM10)

CSIM10 is used to select the operation mode and enable or disable operation. CSIM10 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

## Figure 16-2. Format of Serial Operation Mode Register 10 (CSIM10)

Address: FF80H After reset: 00H R/WNote 1

| Symbol | <7>    | 6      | 5 | 4     | 3 | 2 | 1 | 0      |

|--------|--------|--------|---|-------|---|---|---|--------|

| CSIM10 | CSIE10 | TRMD10 | 0 | DIR10 | 0 | 0 | 0 | CSOT10 |

| CSIE10 <sup>Note 2</sup> | Operation control in 3-wire serial I/O mode                                           |

|--------------------------|---------------------------------------------------------------------------------------|

| 0                        | Disables operation and asynchronously resets the internal circuit <sup>Note 3</sup> . |

| 1                        | Enables operation                                                                     |

| TRMD10 <sup>Note 4</sup> | Transmit/receive mode control         |

|--------------------------|---------------------------------------|

| 0 <sup>Note 5</sup>      | Receive mode (transmission disabled). |

| 1                        | Transmit/receive mode                 |

| DIR10 <sup>Note 6</sup> | First bit specification |

|-------------------------|-------------------------|

| 0                       | MSB                     |

| 1                       | LSB                     |

| CSOT10 | Communication status flag     |

|--------|-------------------------------|

| 0      | Communication is stopped.     |

| 1      | Communication is in progress. |

## Notes 1. Bit 0 is a read-only bit.

- 2. To use P11/SCK10, P12/SI10/RxD0, and P13/SO10/TxD0 as general-purpose port, clear CSIE10 to 0.

- 3. Bit 0 (CSOT10) of CSIM10 and serial I/O shift register 10 (SIO10) are reset.

- 4. Do not rewrite TRMD10 when CSOT10 = 1 (during serial communication).

- 5. The SO10 output (see Figure 16-1) is fixed to the low level when TRMD10 is 0. Reception is started when data is read from SIO10.

- **6.** Do not rewrite DIR10 when CSOT10 = 1 (during serial communication).

# Cautions 1. When resuming operation from standby status, do so after having cleared (0) bit 2 (CSIIF10) of interrupt request flag register 0H (IF0H).

2. Be sure to clear bit 5 to 0.

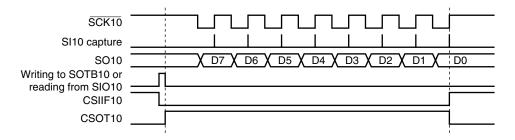

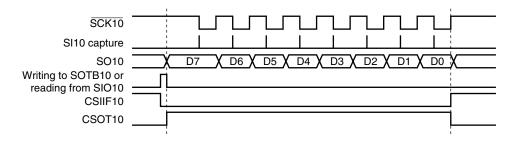

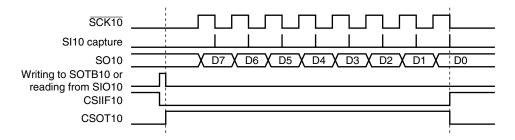

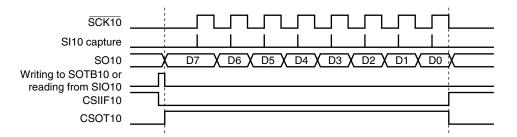

### Figure 16-7. Timing of Clock/Data Phase

# (a) Type 1: CKP10 = 0, DAP10 = 0, DIR10 = 0

### (b) Type 2: CKP10 = 0, DAP10 = 1, DIR10 = 0

## (c) Type 3: CKP10 = 1, DAP10 = 0, DIR10 = 0

#### (d) Type 4: CKP10 = 1, DAP10 = 1, DIR10 = 0

## 18.7.5 Eight-time-slice display example

Figure 18-31 shows how the  $15 \times 8$  dots LCD panel having the display pattern shown in Figure 18-30 is connected to the segment signals (SEG4 to SEG18) and the common signals (COM0 to COM7) of the 78K0/LF3 chip. This example displays data "123" in the LCD panel. The contents of the display data memory (addresses FA44H to FA52H) correspond to this display.

The following description focuses on numeral "3." ( $\exists$ ) displayed in the first digit. To display "3." in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG4 and SEG8 pins according to Table 18-10 at the timing of the common signals COM0 to COM7; see Figure 18-30 for the relationship between the segment signals and LCD segments.

| Segment | SEG4     | SEG5     | SEG6     | SEG7     | SEG8     |

|---------|----------|----------|----------|----------|----------|

| Common  |          |          |          |          |          |

| COM0    | Select   | Select   | Select   | Select   | Select   |

| COM1    | Deselect | Select   | Deselect | Deselect | Deselect |

| COM2    | Deselect | Deselect | Select   | Deselect | Deselect |

| СОМЗ    | Deselect | Select   | Deselect | Deselect | Deselect |

| COM4    | Select   | Deselect | Deselect | Deselect | Deselect |

| COM5    | Select   | Deselect | Deselect | Deselect | Select   |

| COM6    | Deselect | Select   | Select   | Select   | Deselect |

| COM7    | Deselect | Deselect | Deselect | Deselect | Deselect |

Table 18-10. Select and Deselect Voltages (COM0 to COM7)

According to Table 18-10, it is determined that the display data memory location (FA44H) that corresponds to SEG4 must contain 00110001.

Figure 18-32 shows examples of LCD drive waveforms between the SEG4 signal and each common signal. When the select voltage is applied to SEG4 at the timing of COM0, a waveform is generated to turn on the corresponding LCD segment.

### Figure 18-30. Eight-Time-Slice LCD Display Pattern and Electrode Connections

## <2> Error of baud rate

The baud rate error can be calculated by the following expression.

- Error (%) =  $\left(\frac{\text{Actual baud rate (baud rate with error)}}{\text{Desired baud rate (correct baud rate)}} 1\right) \times 100 [\%]$

- Caution Keep the baud rate error during transmission to within the permissible error range at the reception destination.

- Example: Frequency of base clock = 2.5 MHz = 2,500,000 Hz Set value of MC0BRS4 to MC0BRS0 bits of MC0CTL2 register = 10000B (k = 16) Target baud rate = 76,800 bps

Baud rate = 2.5 M/(2  $\times$  16) = 2,500,000/(2  $\times$  16) = 78125 [bps]

Error = (78,125/76,800 - 1) × 100 = 1.725 [%]

## <3> Example of setting baud rate

| Baud          | fpr           | s = 1 | 0.0 MHz             |            | fpp           | is = 8 | .38 MHz             |            | fP            | rs = 8 | 3.0 MHz             |            | fP            | rs = 6 | 6.0 MHz             |            |

|---------------|---------------|-------|---------------------|------------|---------------|--------|---------------------|------------|---------------|--------|---------------------|------------|---------------|--------|---------------------|------------|

| Rate<br>[bps] | MC0CKS2<br>to | k     | Calculated<br>Value | ERR<br>[%] | MC0CKS2<br>to | k      | Calculated<br>Value | ERR<br>[%] | MC0CKS2<br>to | k      | Calculated<br>Value | ERR<br>[%] | MC0CKS2<br>to | k      | Calculated<br>Value | ERR<br>[%] |

|               | MC0CKS0       |       |                     |            | MC0CKS0       |        |                     |            | MC0CKS0       |        |                     |            | MC0CKS0       |        |                     |            |

| 4800          | _             | -     | -                   | -          | 5, 6, or 7    | 27     | 4850                | 1.03       | 5, 6, or 7    | 26     | 4808                | 0.16       | 5, 6, or 7    | 20     | 4688                | -2.34      |

| 9600          | 5, 6, or 7    | 16    | 9766                | 1.73       | 4             | 27     | 9699                | 1.03       | 5, 6, or 7    | 13     | 9615                | 0.16       | 4             | 20     | 9375                | -2.34      |

| 19200         | 5             | 8     | 19531               | 1.73       | 3             | 27     | 19398               | 1.03       | 4             | 13     | 19231               | 0.16       | 4             | 10     | 18750               | -2.34      |

| 31250         | 4             | 10    | 31250               | 0          | 2             | 17     | 30809               | -1.41      | 4             | 8      | 31250               | 0          | 2             | 24     | 31250               | 0          |

| 38400         | 4             | 8     | 39063               | 1.73       | 2             | 27     | 38796               | 1.03       | 3             | 13     | 38462               | 0.16       | 2             | 20     | 37500               | -2.34      |

| 56000         | 3             | 11    | 56818               | 1.46       | 2             | 19     | 55132               | -1.55      | 3             | 9      | 55556               | -0.79      | 1             | 27     | 55556               | -0.79      |

| 62500         | 2             | 20    | 62500               | 0          | 2             | 17     | 61618               | -1.41      | 3             | 8      | 62500               | 0          | 2             | 12     | 62500               | 0          |

| 76800         | 2             | 16    | 78125               | 1.73       | 1             | 27     | 77592               | 1.03       | 2             | 13     | 76923               | 0.16       | 2             | 10     | 75000               | -2.34      |

| 115200        | 1             | 22    | 113636              | -1.36      | 2             | 9      | 116389              | 1.03       | 1             | 17     | 117647              | 2.12       | 1             | 13     | 115385              | 0.16       |

| 125000        | 1             | 20    | 125000              | 0          | 1             | 17     | 123235              | -1.41      | 1             | 16     | 125000              | 0          | 1             | 12     | 125000              | 0          |

| 153600        | 1             | 16    | 156250              | 1.73       | 2             | 7      | 149643              | -2.58      | 1             | 13     | 153846              | 0.16       | 1             | 10     | 150000              | -2.34      |

| 250000        | 1             | 10    | 250000              | 0          | 1             | 8      | 261875              | 4.75       | 1             | 8      | 250000              | 0          | 1             | 6      | 250000              | 0          |

|               |               |       |                     |            | 0             | 17     | 246471              | -1.41      |               |        |                     |            |               |        |                     |            |

Remark MC0CKS2 to MC0CKS0: Bits 2 to 0 of MCG control register 1 (MC0CTL1) (setting of base clock (fxcLK))

k: Value set by bits 4 to 0 (MC0BRS4 to MC0BRS0) of MCG control register 2 (MC0CTL2) (k = 4, 5, 6, ..., 31)

fPRS: Peripheral hardware clock frequency

ERR: Baud rate error

## <2> Error of baud rate

The baud rate error can be calculated by the following expression.

• Error (%) =  $\left(\frac{\text{Actual baud rate (baud rate with error)}}{\text{Desired baud rate (correct baud rate)}} - 1\right) \times 100 [\%]$

- Caution Keep the baud rate error during transmission to within the permissible error range at the reception destination.

- Example: Frequency of base clock = 2.5 MHz = 2,500,000 Hz Set value of MC0BRS4 to MC0BRS0 bits of MC0CTL2 register = 10000B (k = 16) Target baud rate = 76,800 bps

Baud rate = 2.5 M/(2 × 16) = 2,500,000/(2 × 16) = 78125 [bps]

Error = (78,125/76,800 - 1) × 100 = 1.725 [%]

### <3> Example of setting baud rate

| Baud          | fer           | s = 1 | 0.0 MHz    |       | fpr           | is = 8 | .38 MHz    |       | fP            | rs = 8 | 3.0 MHz    |       | fP            | rs = 6 | 6.0 MHz    |       |

|---------------|---------------|-------|------------|-------|---------------|--------|------------|-------|---------------|--------|------------|-------|---------------|--------|------------|-------|

| Rate<br>[bps] | MC0CKS2       | k     | Calculated | ERR   | MC0CKS2       | k      | Calculated | ERR   |               | k      | Calculated | ERR   | MC0CKS2       | k      | Calculated |       |

| [000]         | to<br>MC0CKS0 |       | Value      | [%]   | to<br>MC0CKS0 |        | Value      | [%]   | to<br>MC0CKS0 |        | Value      | [%]   | to<br>MC0CKS0 |        | Value      | [%]   |

|               | NCUCKSU       |       |            |       | NICUCKSU      |        |            |       | NICUCKSU      |        |            |       | NCOCKSU       |        |            |       |

| 4800          | -             | -     | -          | -     | 5, 6, or 7    | 27     | 4850       | 1.03  | 5, 6, or 7    | 26     | 4808       | 0.16  | 5, 6, or 7    | 20     | 4688       | -2.34 |

| 9600          | 5, 6, or 7    | 16    | 9766       | 1.73  | 4             | 27     | 9699       | 1.03  | 5, 6, or 7    | 13     | 9615       | 0.16  | 4             | 20     | 9375       | -2.34 |

| 19200         | 5             | 8     | 19531      | 1.73  | 3             | 27     | 19398      | 1.03  | 4             | 13     | 19231      | 0.16  | 4             | 10     | 18750      | -2.34 |

| 31250         | 4             | 10    | 31250      | 0     | 2             | 17     | 30809      | -1.41 | 4             | 8      | 31250      | 0     | 2             | 24     | 31250      | 0     |

| 38400         | 4             | 8     | 39063      | 1.73  | 2             | 27     | 38796      | 1.03  | 3             | 13     | 38462      | 0.16  | 2             | 20     | 37500      | -2.34 |

| 56000         | 3             | 11    | 56818      | 1.46  | 2             | 19     | 55132      | -1.55 | 3             | 9      | 55556      | -0.79 | 1             | 27     | 55556      | -0.79 |

| 62500         | 2             | 20    | 62500      | 0     | 2             | 17     | 61618      | -1.41 | 3             | 8      | 62500      | 0     | 2             | 12     | 62500      | 0     |

| 76800         | 2             | 16    | 78125      | 1.73  | 1             | 27     | 77592      | 1.03  | 2             | 13     | 76923      | 0.16  | 2             | 10     | 75000      | -2.34 |

| 115200        | 1             | 22    | 113636     | -1.36 | 2             | 9      | 116389     | 1.03  | 1             | 17     | 117647     | 2.12  | 1             | 13     | 115385     | 0.16  |

| 125000        | 1             | 20    | 125000     | 0     | 1             | 17     | 123235     | -1.41 | 1             | 16     | 125000     | 0     | 1             | 12     | 125000     | 0     |

| 153600        | 1             | 16    | 156250     | 1.73  | 2             | 7      | 149643     | -2.58 | 1             | 13     | 153846     | 0.16  | 1             | 10     | 150000     | -2.34 |

| 250000        | 1             | 10    | 250000     | 0     | 1             | 8      | 261875     | 4.75  | 1             | 8      | 250000     | 0     | 1             | 6      | 250000     | 0     |

|               |               |       |            |       | 0             | 17     | 246471     | -1.41 |               |        |            |       |               |        |            |       |

Remark MC0CKS2 to MC0CKS0: Bits 2 to 0 of MCG control register 1 (MC0CTL1) (setting of base clock (fxcLK))

k:

Value set by bits 4 to 0 (MC0BRS4 to MC0BRS0) of MCG control register 2 (MC0CTL2) (k = 4, 5, 6, ..., 31)

fPRS:

Peripheral hardware clock frequency

ERR:

Baud rate error

| HALT                                    | Iode Setting                                                        | When HALT Instruction Is Executed While CPU Is Operating on Subsystem Clock                                                           |  |  |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Item                                    |                                                                     | When CPU Is Operating on XT1 Clock (fxr)                                                                                              |  |  |  |  |  |  |

| System clock                            |                                                                     | Clock supply to the CPU is stopped                                                                                                    |  |  |  |  |  |  |

| Main system clo                         | ck fвн                                                              | Status before HALT mode was set is retained                                                                                           |  |  |  |  |  |  |

|                                         | fx                                                                  |                                                                                                                                       |  |  |  |  |  |  |

|                                         | fexclk                                                              | Operates or stops by external clock input                                                                                             |  |  |  |  |  |  |

| Subsystem cloc                          | <fxт< td=""><td>Operation continues (cannot be stopped)</td></fxт<> | Operation continues (cannot be stopped)                                                                                               |  |  |  |  |  |  |

| fri                                     |                                                                     | Status before HALT mode was set is retained                                                                                           |  |  |  |  |  |  |

| CPU                                     |                                                                     | Operation stopped                                                                                                                     |  |  |  |  |  |  |

| Flash memory                            |                                                                     | Operation stopped                                                                                                                     |  |  |  |  |  |  |

| RAM                                     |                                                                     | Status before HALT mode was set is retained                                                                                           |  |  |  |  |  |  |

| Port (latch)                            |                                                                     | Status before HALT mode was set is retained                                                                                           |  |  |  |  |  |  |

| 16-bit timer/event co                   | ounter 00 <sup>Note</sup>                                           | Operable                                                                                                                              |  |  |  |  |  |  |

| 8-bit timer/event                       | 50 <sup>Note</sup>                                                  |                                                                                                                                       |  |  |  |  |  |  |

| counter                                 | 51 <sup>Note</sup>                                                  |                                                                                                                                       |  |  |  |  |  |  |

|                                         | 52 <sup>Note</sup>                                                  |                                                                                                                                       |  |  |  |  |  |  |

| 8-bit timer                             | HO                                                                  |                                                                                                                                       |  |  |  |  |  |  |

|                                         | H1                                                                  |                                                                                                                                       |  |  |  |  |  |  |

|                                         | H2                                                                  |                                                                                                                                       |  |  |  |  |  |  |

| Real-time counter                       |                                                                     |                                                                                                                                       |  |  |  |  |  |  |

| Watchdog timer                          |                                                                     | Operable. Clock supply to watchdog timer stops when "internal low-speed oscillator can be stopped by software" is set by option byte. |  |  |  |  |  |  |

| Clock output                            |                                                                     | Operable                                                                                                                              |  |  |  |  |  |  |

| Buzzer output                           |                                                                     | Operable. However, operation disabled when peripheral hardware clock (fPRs) is stopped.                                               |  |  |  |  |  |  |

| 10-bit successive ap type A/D converter | proximation                                                         |                                                                                                                                       |  |  |  |  |  |  |

| 16-bit $\Delta\Sigma$ type A/D c        | onverter                                                            | Operable                                                                                                                              |  |  |  |  |  |  |

| Serial interface                        | UART0                                                               |                                                                                                                                       |  |  |  |  |  |  |

|                                         | UART6                                                               |                                                                                                                                       |  |  |  |  |  |  |

|                                         | CSI10 <sup>Note</sup>                                               |                                                                                                                                       |  |  |  |  |  |  |

|                                         | CSIA0 <sup>Note</sup>                                               |                                                                                                                                       |  |  |  |  |  |  |

| LCD controller/drive                    | r                                                                   |                                                                                                                                       |  |  |  |  |  |  |

| Manchester code ge                      | enerator                                                            |                                                                                                                                       |  |  |  |  |  |  |

| Remote controller re                    | ceiver                                                              |                                                                                                                                       |  |  |  |  |  |  |

| Power-on-clear func                     | tion                                                                |                                                                                                                                       |  |  |  |  |  |  |

| Low-voltage detection                   | on function                                                         |                                                                                                                                       |  |  |  |  |  |  |

| External interrupt                      |                                                                     |                                                                                                                                       |  |  |  |  |  |  |

# Table 23-1. Operating Statuses in HALT Mode (2/2)

Note When the CPU is operating on the subsystem clock and the internal high-speed oscillation clock has been stopped, do not start operation of these functions on the external clock input from peripheral hardware pins.

| Remark | fвн: | Internal high-speed oscillation clock |

|--------|------|---------------------------------------|

|        | fx:  | X1 clock                              |

fexclk: External main system clock

- XT1 clock fx<sub>T</sub>:

- Internal low-speed oscillation clock frl:

#### (b) Release by reset signal generation

When the reset signal is generated, HALT mode is released, and then, as in the case with a normal reset operation, the program is executed after branching to the reset vector address.

# <R>

#### Figure 23-4. HALT Mode Release by Reset

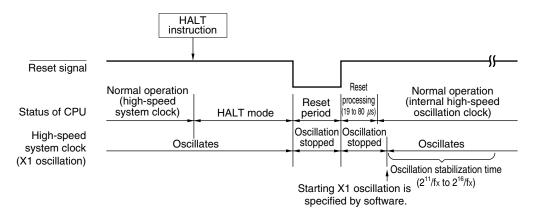

#### (1) When high-speed system clock is used as CPU clock

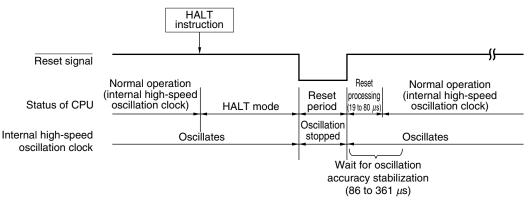

## (2) When internal high-speed oscillation clock is used as CPU clock

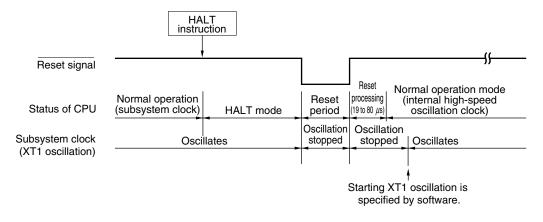

## (3) When subsystem clock is used as CPU clock

# 28.3 Writing with Flash memory programmer

Data can be written to the flash memory on-board or off-board, by using a dedicated flash memory programmer.

## (1) On-board programming

The contents of the flash memory can be rewritten after the 78K0/LF3 has been mounted on the target system. The connectors that connect the dedicated flash memory programmer must be mounted on the target system.

# (2) Off-board programming

Data can be written to the flash memory with a dedicated program adapter (FA series) before the 78K0/LF3 is mounted on the target system.

**Remark** The FA series is a product of Naito Densei Machida Mfg. Co., Ltd.

## Table 28-3. Wiring Between 78K0/LF3 and Dedicated Flash memory programmer

| Pin Configuratior | n of Dedicate | ed Flash memory programmer | With CSI10              | )       | With UART               | 6       |

|-------------------|---------------|----------------------------|-------------------------|---------|-------------------------|---------|

| Signal Name       | I/O           | Pin Function               | Pin Name                | Pin No. | Pin Name                | Pin No. |

| SI/RxD            | Input         | Receive signal             | SO10/TxD0/P13           | 78      | TxD6/SEG18/P112         | 36      |

| SO/TxD            | Output        | Transmit signal            | SI10/RxD0/P12           | 79      | RxD6/SEG19/P113         | 35      |

| SCK               | Output        | Transfer clock             | SCK10/P11               | 80      | -                       | -       |

| CLK               | Output        | Clock to 78K0/LF3          | _Note 1                 | -       | Note 2                  | Note 2  |

| /RESET            | Output        | Reset signal               | RESET                   | 14      | RESET                   | 14      |

| FLMD0             | Output        | Mode signal                | FLMD0                   | 17      | FLMD0                   | 17      |

| VDD               | I/O           | VDD voltage generation/    | VDD                     | 22      | VDD                     | 22      |

|                   |               | power monitoring           | VDD <sup>Note 3</sup>   | 59      | VDD <sup>Note 3</sup>   | 59      |

|                   |               |                            | AVREF <sup>Note 4</sup> |         | AVREF <sup>Note 4</sup> |         |

| GND               | -             | Ground                     | Vss                     | 21      | Vss                     | 21      |

|                   |               |                            | Vss <sup>Note 3</sup>   | 60      | Vss <sup>Note 3</sup>   | 60      |

|                   |               |                            | AVss <sup>Note 4</sup>  |         | AVss <sup>Note 4</sup>  |         |

Notes 1. Only the internal high-speed oscillation clock (fRH) can be used when CSI10 is used.

<R>

Only the X1 clock (fx), external main system clock (fEXCLK), or internal high-speed oscillation clock (fRH) can be used when UART6 is used. When using the clock output of the dedicated flash memory programmer, connect CLK of the PG-FP5 or FL-PR5 to EXCLK/X2/P122 (pin number 18).

- **3.** μPD78F047x only.

- **4.** *μ*PD78F048x and 78F049x only.

<R> Caution Only the bottom side pins (pin numbers 35 and 36) correspond to the UART6 pins (RxD6 and TxD6) when writing by a flash memory programmer. Writing cannot be performed by the top side pins (pin numbers 76 and 75).

| Instruction | Mnemonic  | Operands            | Bytes            | Clo    | ocks   | Operation                                    | F | -lag |    |

|-------------|-----------|---------------------|------------------|--------|--------|----------------------------------------------|---|------|----|

| Group       | Winemonie | Operandas           | Dyte             | Note 1 | Note 2 |                                              | Z | AC ( | CY |

| 16-bit data | MOVW      | rp, #word           | 3                | 6      | -      | $rp \leftarrow word$                         |   |      |    |

| transfer    |           | saddrp, #word       | 4                | 8      | 10     | $(saddrp) \leftarrow word$                   |   |      |    |

|             |           | sfrp, #word         | 4                | -      | 10     | $sfrp \leftarrow word$                       |   |      |    |

|             |           | AX, saddrp          | 2                | 6      | 8      | $AX \leftarrow (saddrp)$                     |   |      |    |

|             |           | saddrp, AX          | 2                | 6      | 8      | $(saddrp) \leftarrow AX$                     |   |      |    |

|             |           | AX, sfrp            | 2                | -      | 8      | $AX \leftarrow sfrp$                         |   |      |    |

|             |           | sfrp, AX            | 2                | -      | 8      | sfrp $\leftarrow AX$                         |   |      |    |

|             |           | AX, rp <sup>№</sup> | <sup>e 3</sup> 1 | 4      | -      | AX ← rp                                      |   |      |    |

|             |           | rp, AX <sup>№</sup> | <sup>e 3</sup> 1 | 4      | -      | $rp \leftarrow AX$                           |   |      |    |

|             |           | AX, !addr16         | 3                | 10     | 12     | $AX \leftarrow (addr16)$                     |   |      |    |

|             |           | !addr16, AX         | 3                | 10     | 12     | (addr16) ← AX                                |   |      |    |

|             | XCHW      | AX, rp <sup>№</sup> | <sup>e 3</sup> 1 | 4      | -      | $AX \leftrightarrow rp$                      |   |      |    |

| 8-bit       | ADD       | A, #byte            | 2                | 4      | _      | A, CY $\leftarrow$ A + byte                  | × | ×    | ×  |

| operation   |           | saddr, #byte        | 3                | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte      | × | ×    | ×  |

|             |           | A, r                | <sup>e 4</sup> 2 | 4      | -      | A, CY ← A + r                                | × | ×    | ×  |

|             |           | r, A                | 2                | 4      | _      | $r, CY \leftarrow r + A$                     | × | ×    | ×  |

|             |           | A, saddr            | 2                | 4      | 5      | A, CY $\leftarrow$ A + (saddr)               | × | ×    | ×  |

|             |           | A, !addr16          | 3                | 8      | 9      | A, CY $\leftarrow$ A + (addr16)              | × | ×    | ×  |

|             |           | A, [HL]             | 1                | 4      | 5      | A, CY $\leftarrow$ A + (HL)                  | × | ×    | ×  |

|             |           | A, [HL + byte]      | 2                | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte)           | × | ×    | ×  |

|             |           | A, [HL + B]         | 2                | 8      | 9      | A, CY $\leftarrow$ A + (HL + B)              | × | ×    | ×  |

|             |           | A, [HL + C]         | 2                | 8      | 9      | A, CY $\leftarrow$ A + (HL + C)              | × | ×    | ×  |

|             | ADDC      | A, #byte            | 2                | 4      | -      | A, CY $\leftarrow$ A + byte + CY             | × | ×    | ×  |

|             |           | saddr, #byte        | 3                | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte + CY | × | ×    | ×  |

|             |           | A, r                | <sup>e 4</sup> 2 | 4      | _      | $A, CY \leftarrow A + r + CY$                | × | ×    | ×  |

|             |           | r, A                | 2                | 4      | _      | $r, CY \leftarrow r + A + CY$                | × | ×    | ×  |

|             |           | A, saddr            | 2                | 4      | 5      | A, CY $\leftarrow$ A + (saddr) + CY          | × | ×    | ×  |

|             |           | A, !addr16          | 3                | 8      | 9      | A, CY $\leftarrow$ A + (addr16) + C          | × | ×    | ×  |

|             |           | A, [HL]             | 1                | 4      | 5      | $A,CY \leftarrow A + (HL) + CY$              | × | ×    | ×  |

|             |           | A, [HL + byte]      | 2                | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte) + CY      | × | ×    | ×  |

|             |           | A, [HL + B]         | 2                | 8      | 9      | $A, CY \leftarrow A + (HL + B) + CY$         | × | ×    | ×  |

|             |           | A, [HL + C]         | 2                | 8      | 9      | A, CY $\leftarrow$ A + (HL + C) + CY         | × | ×    | ×  |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **3.** Only when rp = BC, DE or HL

- **4.** Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

# Standard products

# (c) CSI10 (Master mode, SCK10... internal clock output)

| Parameter                                                   | Symbol        | Conditions                                               | MIN.                              | TYP. | MAX. | Unit |

|-------------------------------------------------------------|---------------|----------------------------------------------------------|-----------------------------------|------|------|------|

| SCK10 cycle time                                            | tксүı         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                    | 250                               |      |      | ns   |

|                                                             |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$                       | 500                               |      |      | ns   |

| SCK10 high-/low-level width                                 | tкн1,<br>tк∟1 | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                    | tксү1/2 –<br>25 <sup>Note 1</sup> |      |      | ns   |

|                                                             |               | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ | tkcy1/2 –<br>50 <sup>Note 1</sup> |      |      | ns   |

| SI10 setup time (to SCK10↑)                                 | tsik1         | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                    | 80                                |      |      | ns   |

|                                                             |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$                       | 170                               |      |      | ns   |

| SI10 hold time (from SCK10↑)                                | tksi1         |                                                          | 30                                |      |      | ns   |

| Delay time from $\overline{SCK10}\downarrow$ to SO10 output | tkso1         | $C = 50 \text{ pF}^{Note 2}$                             |                                   |      | 40   | ns   |

**Notes 1.** This value is when high-speed system clock (fxH) is used.

**2.** C is the load capacitance of the  $\overline{\text{SCK10}}$  and SO10 output lines.

# (d) CSI10 (Slave mode, SCK10... external clock input)

| Parameter                                              | Symbol        | C         | Conditions                            | MIN.    | TYP. | MAX. | Unit |

|--------------------------------------------------------|---------------|-----------|---------------------------------------|---------|------|------|------|

| SCK10 cycle time                                       | <b>t</b> ксү2 |           |                                       | 400     |      |      | ns   |

| SCK10 high-/low-level width                            | tкн2,         |           |                                       | tксү2/2 |      |      | ns   |

|                                                        | tĸl2          |           |                                       |         |      |      |      |

| SI10 setup time (to SCK10↑)                            | tsik2         |           |                                       | 80      |      |      | ns   |

| SI10 hold time (from SCK10↑)                           | tksi2         |           |                                       | 50      |      |      | ns   |

| Delay time from $\overline{\text{SCK10}}\downarrow$ to | tkso2         | C = 50 pF | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ |         |      | 120  | ns   |

| SO10 output                                            |               | Note      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |         |      | 165  | ns   |

**Note** C is the load capacitance of the SO10 output line.