Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 62                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b, 3x16b                                                                     |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0492gc-gad-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (a) KR0 to KR7

<R>

These are the key interrupt input or segment key scan input pins.

## (b) TO50, TO51

These are the timer output pin from 8-bit timer/event counter 50 and 51.

## (c) TI50, TI51

These are the pins for inputting an external count clock to 8-bit timer/event counter 50 and 51.

## (d) RIN

This is the data input pin of the remote controller receiver.

#### (e) VLC3

This is the power supply voltage pins for driving the LCD.

#### 2.2.5 P80 to P83 (port 8)

P80 to P83 function as a 4-bit I/O port. These pins also function as segment signal output pins for the LCD controller/driver. Either I/O port function or segment signal output function can be selected using port function register ALL (PFALL).

#### (1) Port mode

P80 to P83 function as a 4-bit I/O port. P80 to P83 can be set to input or output port in 1-bit units using port mode register 8 (PM8). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 8 (PU8).

### (2) Control mode

P80 to P83 function as segment signal output for the LCD controller/driver.

#### (a) SEG4 to SEG7

These pins are the segment signal output pins for the LCD controller/driver.

#### 2.2.6 P90 to P93 (port 9)

P90 to P93 function as a 4-bit I/O port. These pins also function as segment signal output pins for the LCD controller/driver. Either I/O port function or segment signal output function can be selected using port function register ALL (PFALL).

#### (1) Port mode

P90 to P93 function as a 4-bit I/O port. P90 to P93 can be set to input or output port in 1-bit units using port mode register 9 (PM9). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 9 (PU9).

## (2) Control mode

P90 to P93 function as segment signal output for the LCD controller/driver.

## (a) SEG8 to SEG11

These pins are the segment signal output pins for the LCD controller/driver.

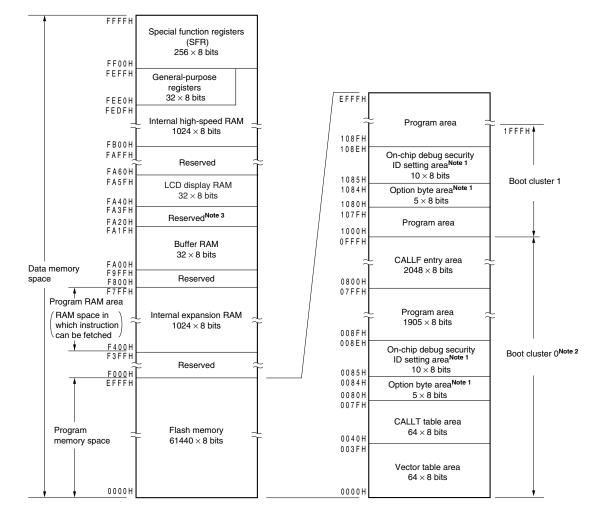

Figure 3-10. Memory Map (*µ*PD78F0495)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used: Set t

ed: Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- Writing boot cluster 0 can be prohibited depending on the setting of security (see 28.8 Security Setting).

- 3. However, FA26H and FA27H can be used (See 13.3 Registers Used in 16-Bit  $\Delta\Sigma$  Type A/D Converter).

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

<R>

| Table 4 | 4-2. | Port | Functions | (2/2) |

|---------|------|------|-----------|-------|

|---------|------|------|-----------|-------|

| Function Name | I/O   | Function                                                                                                                                                      | After Reset | Alternate Function            |

|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------|

| P80 to P83    | 1/0   | Port 8.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.  | Input port  | SEG4 to SEG7                  |

| P90 to P93    | I/O   | Port 9.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.  | Input port  | SEG8 to SEG11                 |

| P100 to P103  | I/O   | Port 10.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port  | SEG12 to SEG15                |

| P110, P111    | I/O   | Port 11.                                                                                                                                                      | Input port  | SEG16, SEG17                  |

| P112          |       | 4-bit I/O port.                                                                                                                                               |             | SEG18/TxD6                    |

| P113          |       | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                |             | SEG19/RxD6                    |

| P120          | I/O   | Port 12.                                                                                                                                                      | Input port  | INTP0/EXLVI                   |

| P121          | Input | 1-bit I/O port and 4-bit input port.                                                                                                                          |             | X1/OCD0A                      |

| P122          |       | Only for P120, use of an on-chip pull-up resistor can be specified by a software setting.                                                                     |             | X2/EXCLK/OCD0B                |

| P123          |       | specifica by a software setting.                                                                                                                              |             | XT1                           |

| P124          |       |                                                                                                                                                               |             | XT2                           |

| P130 to P133  | I/O   | Port 13.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port  | SEG20 to SEG23                |

| P140 to P143  | I/O   | Port 14.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port  | SEG24 (KS0) to<br>SEG27 (KS3) |

| P150 to P153  | I/O   | Port 15.<br>4-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. | Input port  | SEG28 (KS4) to<br>SEG31 (KS7) |

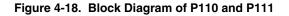

## 4.2.8 Port 11

Port 11 is a 4-bit I/O port with an output latch. Port 11 can be set to the input mode or output mode in 1-bit units using port mode register 11 (PM11). When the P110 to P113 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 11 (PU11).

This port can also be used for segment output and serial interface data I/O.

Reset signal generation sets port 11 to input mode.

Figures 4-18 to 4-20 show a block diagram of port 11.

- P11: Port register 11

- PU11: Pull-up resistor option register 11

- PM11: Port mode register 11

- PFALL: Port function register ALL

- RD: Read signal

- WR××: Write signal

- **Remarks 1.** fx: X1 clock oscillation frequency

- 2. free Internal high-speed oscillation clock frequency

- 3. fexclk: External main system clock frequency

- **4.** fxH: High-speed system clock frequency

- 5. fxp: Main system clock frequency

- 6. fprs: Peripheral hardware clock frequency

- 7. fcpu: CPU clock frequency

- 8. fxr: XT1 clock oscillation frequency

- 9. fsub: Subsystem clock frequency

- **10.** fr.: Internal low-speed oscillation clock frequency

## 5.3 Registers Controlling Clock Generator

The following eight registers are used to control the clock generator.

- Clock operation mode select register (OSCCTL)

- Processor clock control register (PCC)

- Internal oscillation mode register (RCM)

- Main OSC control register (MOC)

- Main clock mode register (MCM)

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

- Internal high-speed oscillation trimming register (HIOTRM)

## (1) Clock operation mode select register (OSCCTL)

This register selects the operation modes of the high-speed system and subsystem clocks, and the gain of the on-chip oscillator.

OSCCTL can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### 5.6.8 Time required for switchover of CPU clock and main system clock

By setting bits 0 to 2 (PCC0 to PCC2) and bit 4 (CSS) of the processor clock control register (PCC), the CPU clock can be switched (between the main system clock and the subsystem clock) and the division ratio of the main system clock can be changed.

The actual switchover operation is not performed immediately after rewriting to PCC; operation continues on the pre-switchover clock for several clocks (see **Table 5-7**).

Whether the CPU is operating on the main system clock or the subsystem clock can be ascertained using bit 5 (CLS) of the PCC register.

|     | Set Value Before<br>Switchover |      |      |                                                                      |                 |      |   | Set Value After Switchover |       |           |          |           |       |          |           |          |          |                  |          |                 |                  |                  |   |   |   |   |   |

|-----|--------------------------------|------|------|----------------------------------------------------------------------|-----------------|------|---|----------------------------|-------|-----------|----------|-----------|-------|----------|-----------|----------|----------|------------------|----------|-----------------|------------------|------------------|---|---|---|---|---|

| CSS | PCC2                           | PCC1 | PCC0 | CSS PCC2 PCC1 PCC0 CSS PCC2 PCC1 PCC0 CSS PCC2 PCC1 PCC0 CSS PCC2 PC |                 |      |   | PCC1                       | PCC0  | CSS       | PCC2     | PCC1      | PCC0  | CSS      | PCC2      | PCC1     | PCC0     |                  |          |                 |                  |                  |   |   |   |   |   |

|     |                                |      |      | 0                                                                    | 0               | 0    | 0 | 0                          | 0     | 0         | 1        | 0         | 0     | 1        | 0         | 0        | 0        | 1                | 1        | 0               | 1                | 0                | 0 | 1 | × | × | × |

| 0   | 0                              | 0    | 0    | /                                                                    |                 |      |   | 16 clocks                  |       | 16 clocks |          | 16 clocks |       |          | 16 clocks |          |          | 2fxp/fsuв clocks |          |                 |                  |                  |   |   |   |   |   |

|     | 0                              | 0    | 1    |                                                                      | 8 clo           | ocks |   |                            |       |           | 8 clocks |           |       | 8 clocks |           |          | 8 clocks |                  |          | fxp/fsuв clocks |                  |                  |   |   |   |   |   |

|     | 0                              | 1    | 0    |                                                                      | 4 clo           | ocks |   |                            | 4 clo | ocks      |          |           |       |          | 4 clocks  |          |          | 4 clocks         |          |                 | fxp/2fsub clocks |                  |   |   |   |   |   |

|     | 0                              | 1    | 1    |                                                                      | 2 clo           | ocks |   |                            | 2 clo | ocks      |          |           | 2 clo | ocks     |           |          |          |                  | 2 clocks |                 |                  | fxp/4fsuв clocks |   |   |   |   |   |

|     | 1                              | 0    | 0    |                                                                      | 1 clock 1 clock |      |   | 1 cl                       | ock   |           |          | 1 cl      | ock   |          |           | /        | /        | /                | fхр      | / <b>8f</b> su  | в cloo           | cks              |   |   |   |   |   |

| 1   | ×                              | ×    | ×    |                                                                      | 2 clo           | ocks |   |                            | 2 clo | ocks      |          |           | 2 clo | ocks     |           | 2 clocks |          |                  |          |                 | 2 clo            | ocks             |   | / | / | / | _ |

Table 5-7. Time Required for Switchover of CPU Clock and Main System Clock Cycle Division Factor

Caution Selection of the main system clock cycle division factor (PCC0 to PCC2) and switchover from the main system clock to the subsystem clock (changing CSS from 0 to 1) should not be set simultaneously.

Simultaneous setting is possible, however, for selection of the main system clock cycle division factor (PCC0 to PCC2) and switchover from the subsystem clock to the main system clock (changing CSS from 1 to 0).

Remarks 1. The number of clocks listed in Table 5-7 is the number of CPU clocks before switchover.

When switching the CPU clock from the main system clock to the subsystem clock, calculate the number of clocks by rounding up to the next clock and discarding the decimal portion, as shown below.

**Example** When switching CPU clock from fxp/2 to fsub/2 (@ oscillation with fxp = 10 MHz, fsub = 32.768 kHz)

$f_{XP}/f_{SUB} = 10000/32.768 \cong 305.1 \rightarrow 306 \text{ clocks}$

By setting bit 0 (MCM0) of the main clock mode register (MCM), the main system clock can be switched (between the internal high-speed oscillation clock and the high-speed system clock).

The actual switchover operation is not performed immediately after rewriting to MCM0; operation continues on the pre-switchover clock for several clocks (see **Table 5-8**).

Whether the CPU is operating on the internal high-speed oscillation clock or the high-speed system clock can be ascertained using bit 1 (MCS) of MCM.

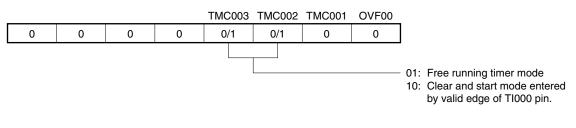

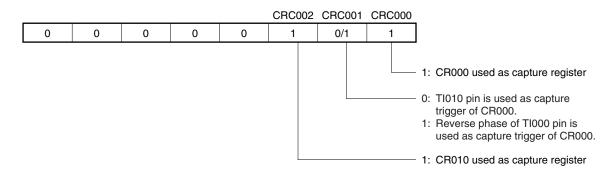

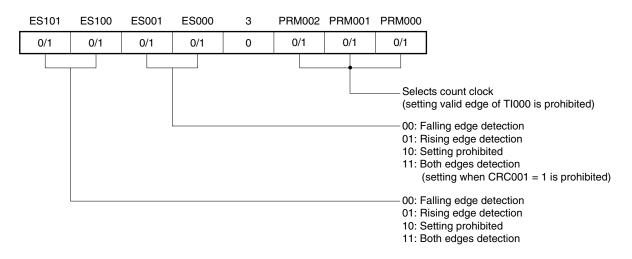

## Figure 6-52. Example of Register Settings for Pulse Width Measurement (1/2)

## (a) 16-bit timer mode control register 00 (TMC00)

## (b) Capture/compare control register 00 (CRC00)

## (c) 16-bit timer output control register 00 (TOC00)

| _ |   | OSPT00 | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

|---|---|--------|--------|--------|-------|-------|--------|-------|

|   | 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

## (d) Prescaler mode register 00 (PRM00)

## 6.5 Special Use of TM00

## 6.5.1 Rewriting CR010 during TM00 operation

In principle, rewriting CR000 and CR010 of the 78K0/LF3 when they are used as compare registers is prohibited while TM00 is operating (TMC003 and TMC002 = other than 00).

However, the value of CR010 can be changed, even while TM00 is operating, using the following procedure if CR010 is used for PPG output and the duty factor is changed (when setting CR010 to a smaller or larger value than the current value, rewrite the CR010 value immediately after a match between CR010 and TM00 or between CR000 and TM00. When CR010 is rewritten immediately before a match between CR010 and TM00 or between CR000 and TM00, an unexpected operation may be performed).

#### Procedure for changing value of CR010

- <1> Disable interrupt INTTM010 (TMMK010 = 1).

- <2> Disable reversal of the timer output when the value of TM00 matches that of CR010 (TOC004 = 0).

- <3> Change the value of CR010.

- <4> Wait for one cycle of the count clock of TM00.

- <5> Enable reversal of the timer output when the value of TM00 matches that of CR010 (TOC004 = 1).

- <6> Clear the interrupt flag of INTTM010 (TMIF010 = 0) to 0.

- <7> Enable interrupt INTTM010 (TMMK010 = 0).

## Remark For TMIF010 and TMMK010, see CHAPTER 21 INTERRUPT FUNCTIONS.

#### 6.5.2 Setting LVS00 and LVR00

## (1) Usage of LVS00 and LVR00

LVS00 and LVR00 are used to set the default value of the TO00 output and to invert the timer output without enabling the timer operation (TMC003 and TMC002 = 00). Clear LVS00 and LVR00 to 00 (default value: low-level output) when software control is unnecessary.

| LVS00 | LVR00 | Timer Output Status            |  |  |  |  |  |

|-------|-------|--------------------------------|--|--|--|--|--|

| 0     | 0     | Not changed (low-level output) |  |  |  |  |  |

| 0     | 1     | Cleared (low-level output)     |  |  |  |  |  |

| 1     | 0     | Set (high-level output)        |  |  |  |  |  |

| 1     | 1     | Setting prohibited             |  |  |  |  |  |

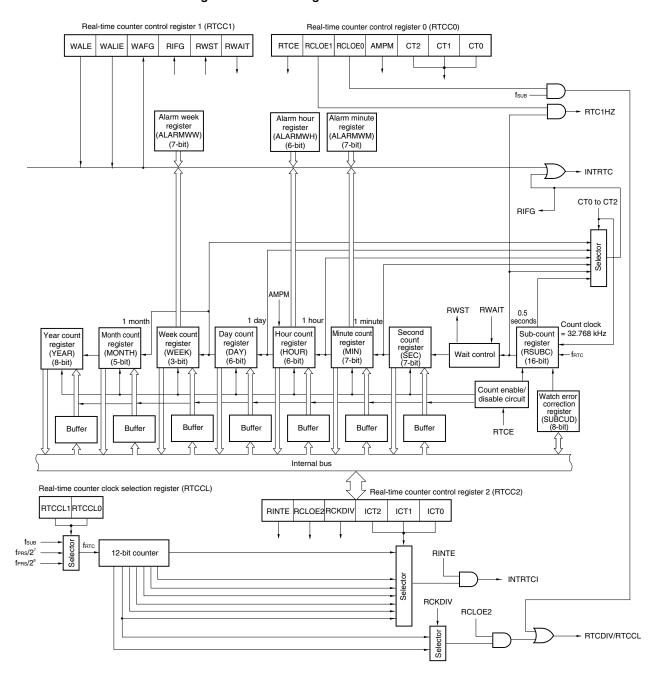

## Figure 9-1. Block Diagram of Real-Time Counter

## 10.4 Operation of Watchdog Timer

## 10.4.1 Controlling operation of watchdog timer

- 1. When the watchdog timer is used, its operation is specified by the option byte (0080H).

- Enable counting operation of the watchdog timer by setting bit 4 (WDTON) of the option byte (0080H) to 1 (the counter starts operating after a reset release) (for details, see **CHAPTER 27**).

| WDTON | Operation Control of Watchdog Timer Counter/Illegal Access Detection                                   |

|-------|--------------------------------------------------------------------------------------------------------|

| 0     | Counter operation disabled (counting stopped after reset), illegal access detection operation disabled |

| 1     | Counter operation enabled (counting started after reset), illegal access detection operation enabled   |

- Set an overflow time by using bits 3 to 1 (WDCS2 to WDCS0) of the option byte (0080H) (for details, see 10.4.2 and CHAPTER 27).

- Set a window open period by using bits 6 and 5 (WINDOW1 and WINDOW0) of the option byte (0080H) (for details, see 10.4.3 and CHAPTER 27).

- 2. After a reset release, the watchdog timer starts counting.

- 3. By writing "ACH" to WDTE after the watchdog timer starts counting and before the overflow time set by the option byte, the watchdog timer is cleared and starts counting again.

- 4. After that, write WDTE the second time or later after a reset release during the window open period. If WDTE is written during a window close period, an internal reset signal is generated.

- 5. If the overflow time expires without "ACH" written to WDTE, an internal reset signal is generated. A internal reset signal is generated in the following cases.

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to WDTE

- If the instruction is fetched from an area not set by the IMS and IXS registers (detection of an invalid check during a CPU program loop)

- If the CPU accesses an area not set by the IMS and IXS registers (excluding FB00H to FFFFH) by executing a read/write instruction (detection of an abnormal access during a CPU program loop)

- Cautions 1. The first writing to WDTE after a reset release clears the watchdog timer, if it is made before the overflow time regardless of the timing of the writing, and the watchdog timer starts counting again.

- 2. If the watchdog timer is cleared by writing "ACH" to WDTE, the actual overflow time may be different from the overflow time set by the option byte by up to 2/f<sub>RL</sub> seconds.

- 3. The watchdog timer can be cleared immediately before the count value overflows (FFFFH).

## 15.4 Operation of Serial Interface UART6

Serial interface UART6 has the following two modes.

- Operation stop mode

- Asynchronous serial interface (UART) mode

## 15.4.1 Operation stop mode

In this mode, serial communication cannot be executed; therefore, the power consumption can be reduced. In addition, the pins can be used as ordinary port pins in this mode. To set the operation stop mode, clear bits 7, 6, and 5 (POWER6, TXE6, and RXE6) of ASIM6 to 0.

## (1) Register used

The operation stop mode is set by asynchronous serial interface operation mode register 6 (ASIM6). ASIM6 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 01H.

Address: FF50H After reset: 01H R/W

| Symbol | <7>    | <6>  | <5>  | 4    | 3    | 2   | 1   | 0     |

|--------|--------|------|------|------|------|-----|-----|-------|

| ASIM6  | POWER6 | TXE6 | RXE6 | PS61 | PS60 | CL6 | SL6 | ISRM6 |

| POWER6              | Enables/disables operation of internal operation clock                                                                                               |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| O <sup>Note 1</sup> | Disables operation of the internal operation clock (fixes the clock to low level) and asynchronously resets the internal circuit <sup>Note 2</sup> . |

| TXE6 | Enables/disables transmission                                                    |

|------|----------------------------------------------------------------------------------|

| 0    | Disables transmission operation (synchronously resets the transmission circuit). |

| RXE6 | Enables/disables reception                                       |

|------|------------------------------------------------------------------|

| 0    | Disables reception (synchronously resets the reception circuit). |

- **Notes 1.** The output of the TxD6 pin goes high and the input from the RxD6 pin is fixed to high level when POWER6 = 0 during transmission.

- 2. Asynchronous serial interface reception error status register 6 (ASIS6), asynchronous serial interface transmission status register 6 (ASIF6), bit 7 (SBRF6) and bit 6 (SBRT6) of asynchronous serial interface control register 6 (ASICL6), and receive buffer register 6 (RXB6) are reset.

- Caution Clear POWER6 to 0 after clearing TXE6 and RXE6 to 0 to stop the operation. To start the communication, set POWER6 to 1, and then set TXE6 or RXE6 to 1.

- **Remark** To use the RxD6/P15 and TxD6/P16 or RxD6/P113 and TxD6/P112 pins as general-purpose port pins, see **CHAPTER 4 PORT FUNCTIONS**.

#### (2) 1-byte transmission/reception communication operation

#### (a) 1-byte transmission/reception

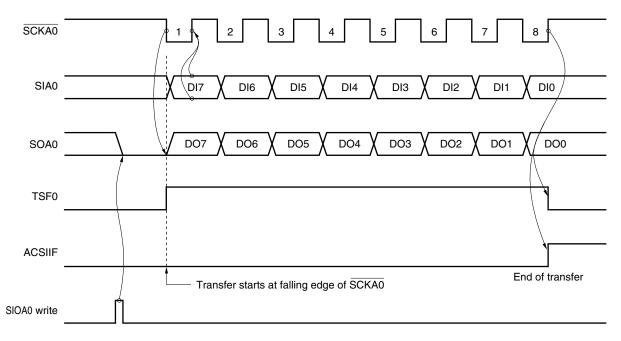

When bit 7 (CSIAE0) and bit 6 (ATE0) of serial operation mode specification register 0 (CSIMA0) = 1, 0, respectively, if communication data is written to serial I/O shift register 0 (SIOA0), the data is output via the SOA0 pin in synchronization with the  $\overline{SCKA0}$  falling edge, and stored in the SIOA0 register in synchronization with the rising edge 1 clock later.

Data transmission and data reception can be performed simultaneously.

If only reception is to be performed, communication can only be started by writing a dummy value to the SIOA0 register.

When communication of 1 byte is complete, an interrupt request signal (INTACSI) is generated.

In 1-byte transmission/reception, the setting of bit 5 (ATM0) of CSIMA0 is invalid.

Be sure to read data after confirming that bit 0 (TSF0) of serial status register 0 (CSIS0) = 0.

Figure 17-11. 3-Wire Serial I/O Mode Timing

Caution The SOA0 pin becomes low level by an SIOA0 write.

## (3) Automatic transmission/reception communication operation

## (a) Automatic transmission/reception mode

Automatic transmission/reception can be performed using buffer RAM.

The data stored in the buffer RAM is output from the SOA0 pin via the SIOA0 register in synchronization with the  $\overline{SCKA0}$  falling edge by performing (2) Automatic transmit/receive data setting.

The receive data is stored in the buffer RAM via the SIOA0 register in synchronization with the SCKA0 rising edge.

Data transfer ends if bit 0 (TSF0) of serial status register 0 (CSIS0) is set to 1 when any of the following conditions is met.

- Communication stop: Reset by clearing bit 7 (CSIAE0) of the CSIMA0 register to 0

- Communication suspension: Transfer of 1 byte is complete by setting bit 1 (ATSTP0) of the CSIT0 register to 1

- Transfer of the range specified by the ADTP0 register is complete

At this time, an interrupt request signal (INTACSI) is generated except when the CSIAE0 bit = 0. If a transfer is terminated in the middle, transfer starting from the remaining data is not possible. Read automatic data transfer address count register 0 (ADTC0) to confirm how much of the data has already been transferred and re-execute transfer by performing (2) Automatic transmit/receive data setting. Figure 17-14 shows the example of the operation timing in automatic transmission/reception mode and Figure 17-15 shows the operation flowchart. Figures 17-16 and 17-17 show the operation of internal buffer RAM when 6 bytes of data are transmitted/received.

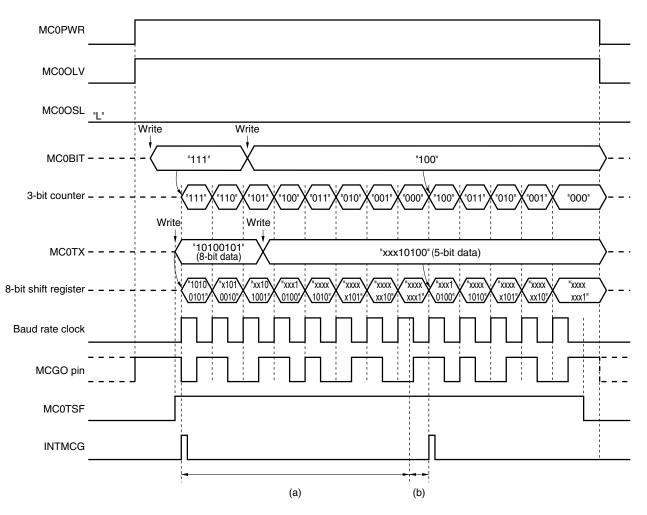

(3) Transmit timing (MC0OLV = 1, total transmit bit length = 13 bits)

- (a): "8-bit transfer period" (b)

- (b): "1/2 cycle of baud rate" + 1 clock (fxcLk) before the last bit of transmit data

- fxclk: Frequency of the operation base clock selected by using the MC0CKS2 to MC0CKS0 bits of the MC0CTL1 register

Last bit: Transfer bit when 3-bit counter = 000

Caution Writing the next transmit data to MC0TX must be complete within the period (a) during continuous transmission. If writing the next transmit data to MC0TX is executed in the period (b), the next data transmission starts 2 clocks (fxcLk) after the last bit has been transmitted. Rewrite the MC0BIT before writing to MC0TX during continuous transmission.

## (2) Remote controller receive data register (RMDR)

This register holds the remote controller reception data. When the remote controller receive shift register (RMSR) overflows, the data in RMSR is transferred to RMDR. Bit 7 stores the last data, and bit 0 stores the first data. INTDFULL is generated at the same time as data is transferred from RMSR to RMDR.

RMDR is read with an 8-bit memory manipulation instruction.

Reset signal generation sets RMDR to 00H.

When the remote controller operation is disabled (RMEN = 0), RMDR is cleared to 00H.

# Caution When INTDFULL has been generated, read RMDR before the next 8-bit data is received. If the next INTDFULL is generated before the read operation is complete, RMDR is overwritten.

## (3) Remote controller shift register receive counter register (RMSCR)

This is a 3-bit counter register used to indicate the number of valid bits remaining in the remote controller receive shift register (RMSR) when remote controller reception is complete (INTREND is generated). Reading the values of this register allows confirmation of the number of bits, even if the received data is in a format other than an integral multiple of 8 bits.

RMSCR is read with an 8-bit memory manipulation instruction.

Reset signal generation sets RMSCR to 00H.

It is cleared to 00H under any of the following conditions.

- Remote controller stops operation (RMEN = 0).

- Error is detected (INTRERR is generated).

- RMSR is read after INTREND has been generated.

Caution When INTREND has been generated, immediately read RMSCR before reading RMSR. If reading occurs at another timing, the value is not guaranteed.

|                   |              |              |              | RM           | ISR          |              |              |              | RMSCR        | RMDR         |

|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|                   | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            |              |              |

| After reset       | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 00H          | 0000000B     |

| Receiving 1 bit   | 1            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 01H          | 0000000B     |

| Receiving 2 bits  | 0            | 1            | 0            | 0            | 0            | 0            | 0            | 0            | 02H          | 0000000B     |

| Receiving 3 bits  | 1            | 0            | 1            | 0            | 0            | 0            | 0            | 0            | 03H          | 0000000B     |

|                   |              |              |              |              |              |              |              |              |              |              |

| Receiving 7 bits  | 1            | 0            | 1            | 0            | 1            | 0            | 1            | 0            | 07H          | 0000000B     |

| Receiving 8 bits  | 0            | 1            | 0            | 1            | 0            | 1            | 0            | 1            | 00H          | 0000000B     |

| $\downarrow$      | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ |

| RMDR transfer     | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 00H          | 01010101B    |

| Receiving 9 bits  | 1            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 01H          | 01010101B    |

| Receiving 10 bits | 1            | 1            | 0            | 0            | 0            | 0            | 0            | 0            | 02H          | 01010101B    |

|                   |              |              |              |              |              |              |              |              |              |              |

| Receiving 16 bits | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 00H          | 01010101B    |

| $\downarrow$      | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ |

| RMDR transfer     | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 00H          | 11111111B    |

## Figure 20-2. Operation Examples of RMSR, RMSCR, and RMDR Registers When Receiving 1010101011111111B (16 Bits)

## (1) Interrupt request flag registers (IF0L, IF0H, IF1L, IF1H)

The interrupt request flags are set to 1 when the corresponding interrupt request is generated or an instruction is executed. They are cleared to 0 when an instruction is executed upon acknowledgment of an interrupt request or upon reset signal generation.

When an interrupt is acknowledged, the interrupt request flag is automatically cleared and then the interrupt routine is entered.

IF0L, IF0H, IF1L, and IF1H are set by a 1-bit or 8-bit memory manipulation instruction. When IF0L and IF0H, and IF1L and IF1H are combined to form 16-bit registers IF0 and IF1, they are set by a 16-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

## Figure 21-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H)

| Address: FFI | Address: FFE0H After reset: 00H R/W |                          |                        |        |         |         |       |                        |  |

|--------------|-------------------------------------|--------------------------|------------------------|--------|---------|---------|-------|------------------------|--|

| Symbol       | <7>                                 | <6>                      | <5>                    | <4>    | <3>     | <2>     | <1>   | <0>                    |  |

| IF0L         | SREIF6                              | PIF5                     | PIF4                   | PIF3   | PIF2    | PIF1    | PIF0  | LVIIF                  |  |

|              |                                     |                          |                        |        |         |         |       |                        |  |

| Address: FFI | E1H After r                         | eset: 00H F              | R/W                    |        |         |         |       |                        |  |

| Symbol       | <7>                                 | <6>                      | <5>                    | <4>    | <3>     | <2>     | <1>   | <0>                    |  |

| IF0H         | TMIF010                             | TMIF000                  | TMIF50                 | TMIFH0 | TMIFH1  | CSIIF10 | STIF6 | SRIF6                  |  |

|              |                                     |                          |                        |        |         | STIF0   |       |                        |  |

|              |                                     |                          |                        |        |         |         |       |                        |  |

| Address: FFI | E2H After r                         | eset: 00H F              | R/W                    |        |         |         |       |                        |  |

| Symbol       | <7>                                 | <6>                      | <5>                    | <4>    | <3>     | <2>     | <1>   | <0>                    |  |

| IF1L         | TMIF52                              | DSADIF <sup>Note 2</sup> | RTCIIF                 | KRIF   | TMIF51  | RTCIF   | SRIF0 | ADIF <sup>Note 1</sup> |  |

|              |                                     |                          |                        |        |         |         |       |                        |  |

| Address: FFI | E3H After r                         | eset: 00H F              | R/W                    |        |         |         |       |                        |  |

| Symbol       | 7                                   | 6                        | 5                      | <4>    | <3>     | <2>     | <1>   | <0>                    |  |

| IF1H         | 0                                   | 0                        | 0                      | ACSIIF | RERRIF  | RINIF   | MCGIF | TMHIF2                 |  |

|              |                                     |                          |                        |        | GPIF    |         |       |                        |  |

|              |                                     |                          |                        |        | RENIF   |         |       |                        |  |

|              |                                     |                          |                        |        | DFULLIF |         |       |                        |  |

|              |                                     |                          |                        |        |         |         |       |                        |  |

|              | XXIFX                               |                          | Interrupt request flag |        |         |         |       |                        |  |

| XXIFX                                                      | Interrupt request flag                   |  |  |  |

|------------------------------------------------------------|------------------------------------------|--|--|--|

| 0                                                          | No interrupt request signal is generated |  |  |  |

| 1 Interrupt request is generated, interrupt request status |                                          |  |  |  |

**Notes 1.** *μ*PD78F048x and 78F049x only.

**2.** μPD78F049x only.

Cautions 1. Be sure to clear bits 5 to 7 of IF1H to 0.

2. When operating a timer, serial interface, or A/D converter after standby release, operate it once after clearing the interrupt request flag. An interrupt request flag may be set by noise.

(4) External interrupt rising edge enable register (EGP), external interrupt falling edge enable register (EGN) These registers specify the valid edge for INTP0 to INTP5.

EGP and EGN are set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

# Figure 21-5. Format of External Interrupt Rising Edge Enable Register (EGP) and External Interrupt Falling Edge Enable Register (EGN)

| Address: FF | 48H After | reset: 00H | R/W  |      |      |      |      |      |

|-------------|-----------|------------|------|------|------|------|------|------|

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1    | 0    |

| EGP         | 0         | 0          | EGP5 | EGP4 | EGP3 | EGP2 | EGP1 | EGP0 |

|             |           |            |      |      |      |      |      |      |

| Address: FF | 49H After | reset: 00H | R/W  |      |      |      |      |      |

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1    | 0    |

| EGN         | 0         | 0          | EGN5 | EGN4 | EGN3 | EGN2 | EGN1 | EGN0 |

|             |           |            |      |      |      |      |      |      |

| EGPn | EGNn | INTPn pin valid edge selection $(n = 0 \text{ to } 5)$ |  |  |  |

|------|------|--------------------------------------------------------|--|--|--|

| 0    | 0    | dge detection disabled                                 |  |  |  |

| 0    | 1    | alling edge                                            |  |  |  |

| 1    | 0    | Rising edge                                            |  |  |  |

| 1    | 1    | Both rising and falling edges                          |  |  |  |

Table 21-3 shows the ports corresponding to EGPn and EGNn.

| Detection En | able Register | Edge Detection Port        | Interrupt Request Signal |

|--------------|---------------|----------------------------|--------------------------|

| EGP0         | EGN0          | P120/EXLVI                 | INTP0                    |

| EGP1         | EGN1          | P34/TI52/TI010/TO00/RTC1HZ | INTP1                    |

| EGP2         | EGN2          | P33/TI000/RTCDIV/RTCCL/BUZ | INTP2                    |

| EGP3         | EGN3          | P31/TOH1                   | INTP3                    |

| EGP4         | EGN4          | P14/SCKA0                  | INTP4                    |

| EGP5         | EGN5          | P30                        | INTP5                    |

Table 21-3. Ports Corresponding to EGPn and EGNn

Caution Select the port mode by clearing EGPn and EGNn to 0 because an edge may be detected when the external interrupt function is switched to the port function.

**Remark** n = 0 to 5

## **CHAPTER 30 INSTRUCTION SET**

This chapter lists each instruction set of the 78K0/LF3 in table form. For details of each operation and operation code, refer to the separate document **78K/0 Series Instructions User's Manual (U12326E)**.

## **30.1 Conventions Used in Operation List**

#### 30.1.1 Operand identifiers and specification methods

Operands are written in the "Operand" column of each instruction in accordance with the specification method of the instruction operand identifier (refer to the assembler specifications for details). When there are two or more methods, select one of them. Uppercase letters and the symbols #, !, \$ and [] are keywords and must be written as they are. Each symbol has the following meaning.

- #: Immediate data specification

- !: Absolute address specification

- \$: Relative address specification

- []: Indirect address specification

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, be sure to write the #, !, \$, and [] symbols.

For operand register identifiers r and rp, either function names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be used for specification.

| Identifier | Specification Method                                                                     |

|------------|------------------------------------------------------------------------------------------|

| r          | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7)                           |

| rp         | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                                                   |

| sfr        | Special function register symbol <sup>Note</sup>                                         |

| sfrp       | Special function register symbol (16-bit manipulatable register even addresses only)Note |

| saddr      | FE20H to FF1FH Immediate data or labels                                                  |

| saddrp     | FE20H to FF1FH Immediate data or labels (even address only)                              |

| addr16     | 0000H to FFFFH Immediate data or labels                                                  |

|            | (Only even addresses for 16-bit data transfer instructions)                              |

| addr11     | 0800H to 0FFFH Immediate data or labels                                                  |

| addr5      | 0040H to 007FH Immediate data or labels (even address only)                              |

| word       | 16-bit immediate data or label                                                           |

| byte       | 8-bit immediate data or label                                                            |

| bit        | 3-bit immediate data or label                                                            |

| RBn        | RB0 to RB3                                                                               |

Table 30-1. Operand Identifiers and Specification Methods

**Note** Addresses from FFD0H to FFDFH cannot be accessed with these operands.

Remark For special function register symbols, see Table 3-6 Special Function Register List.

## 30.2 Operation List

| Instruction | Maamania | Oporopdo       | Dutes | Clocks |        | Oneration                       |   | Flag |    |

|-------------|----------|----------------|-------|--------|--------|---------------------------------|---|------|----|

| Group       | Mnemonic | Operands       | Bytes | Note 1 | Note 2 | Operation                       | Z | AC 0 | CY |

| 8-bit data  | MOV      | r, #byte       | 2     | 4      | -      | r ← byte                        |   |      |    |

| transfer    |          | saddr, #byte   | 3     | 6      | 7      | $(saddr) \leftarrow byte$       |   |      |    |

|             |          | sfr, #byte     | 3     | -      | 7      | sfr $\leftarrow$ byte           |   |      |    |

|             |          | A, r           | 1     | 2      | -      | A ← r                           |   |      |    |

|             |          | r, A Note 3    | 1     | 2      | -      | $r \leftarrow A$                |   |      |    |

|             |          | A, saddr       | 2     | 4      | 5      | $A \leftarrow (saddr)$          |   |      |    |

|             |          | saddr, A       | 2     | 4      | 5      | $(saddr) \leftarrow A$          |   |      |    |

|             |          | A, sfr         | 2     | -      | 5      | A ← sfr                         |   |      |    |

|             |          | sfr, A         | 2     | -      | 5      | sfr ← A                         |   |      |    |

|             |          | A, !addr16     | 3     | 8      | 9      | $A \leftarrow (addr16)$         |   |      |    |

|             |          | !addr16, A     | 3     | 8      | 9      | $(addr16) \leftarrow A$         |   |      |    |

|             |          | PSW, #byte     | 3     | -      | 7      | PSW ← byte                      | × | ×    | ×  |

|             |          | A, PSW         | 2     | -      | 5      | A ← PSW                         |   |      |    |

|             |          | PSW, A         | 2     | -      | 5      | $PSW \leftarrow A$              | × | ×    | ×  |

|             |          | A, [DE]        | 1     | 4      | 5      | $A \leftarrow (DE)$             |   |      |    |

|             |          | [DE], A        | 1     | 4      | 5      | $(DE) \leftarrow A$             |   |      |    |

|             |          | A, [HL]        | 1     | 4      | 5      | $A \leftarrow (HL)$             |   |      |    |

|             |          | [HL], A        | 1     | 4      | 5      | $(HL) \leftarrow A$             |   |      |    |

|             |          | A, [HL + byte] | 2     | 8      | 9      | $A \leftarrow (HL + byte)$      |   |      |    |

|             |          | [HL + byte], A | 2     | 8      | 9      | (HL + byte) ← A                 |   |      |    |

|             |          | A, [HL + B]    | 1     | 6      | 7      | $A \leftarrow (HL + B)$         |   |      |    |

|             |          | [HL + B], A    | 1     | 6      | 7      | $(HL + B) \leftarrow A$         |   |      |    |

|             |          | A, [HL + C]    | 1     | 6      | 7      | $A \leftarrow (HL + C)$         |   |      |    |

|             |          | [HL + C], A    | 1     | 6      | 7      | $(HL + C) \leftarrow A$         |   |      |    |

|             | хсн      | A, r Note 3    | 1     | 2      | -      | $A \leftrightarrow r$           |   |      |    |

|             |          | A, saddr       | 2     | 4      | 6      | $A \leftrightarrow (saddr)$     |   |      |    |

|             |          | A, sfr         | 2     | -      | 6      | $A \leftrightarrow (sfr)$       |   |      |    |

|             |          | A, !addr16     | 3     | 8      | 10     | $A \leftrightarrow (addr16)$    |   |      |    |

|             |          | A, [DE]        | 1     | 4      | 6      | $A \leftrightarrow (DE)$        |   |      |    |

|             |          | A, [HL]        | 1     | 4      | 6      | $A \leftrightarrow (HL)$        |   |      |    |

|             |          | A, [HL + byte] | 2     | 8      | 10     | $A \leftrightarrow (HL + byte)$ |   |      |    |

|             |          | A, [HL + B]    | 2     | 8      | 10     | $A \leftrightarrow (HL + B)$    |   |      |    |

|             |          | A, [HL + C]    | 2     | 8      | 10     | $A \leftrightarrow (HL + C)$    |   |      |    |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- 3. Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

**Remark** ×××× in the part number differs depending on the host machine and OS used.

# μS××××RA78K0 μS××××CC78K0 μS××××CC78K0-L

| <br>×××× | Host Machine                   | Host Machine OS                   |        |

|----------|--------------------------------|-----------------------------------|--------|

| AB17     | PC-9800 series,                | Windows (Japanese version)        | CD-ROM |

| BB17     | IBM PC/AT compatibles          | Windows (English version)         |        |

| 3P17     | HP9000 series 700 <sup>™</sup> | HP-UX <sup>™</sup> (Rel. 10.10)   |        |

| 3K17     | SPARCstation <sup>™</sup>      | SunOS™ (Rel. 4.1.4)               |        |

|          |                                | Solaris <sup>™</sup> (Rel. 2.5.1) |        |

# μS<u>××××</u>DF780495

|                         | ×××× | Host Machine          | OS                         | Supply Medium   |

|-------------------------|------|-----------------------|----------------------------|-----------------|

|                         | AB13 | PC-9800 series,       | Windows (Japanese version) | 3.5-inch 2HD FD |

| BB13 IBM PC/AT compatib |      | IBM PC/AT compatibles | Windows (English version)  |                 |

# A.3 Control Software

| This is control software designed to enable efficient user program development in the Windows environment. All operations used in development of a user program, such as starting the editor, building, and starting the debugger, can be performed from the project manager. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The project manager is included in the assembler package (RA78K0).<br>It can only be used in Windows.                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                               |