Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 62                                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b, 3x16b                                                                     |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 80-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0495gk-gak-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CHAPTER 1 OUTLINE

### 1.1 Features

- O Minimum instruction execution time can be changed from high speed (0.2 μs: @ 10 MHz operation with high-speed system clock) to ultra low-speed (122 μs: @ 32.768 kHz operation with subsystem clock)

- O General-purpose register: 8 bits  $\times$  32 registers (8 bits  $\times$  8 registers  $\times$  4 banks)

- O ROM, RAM capacities

| Item                         | Program Memory<br>(ROM)  |       | Data Memory                                   |                                             |                                                                      |  |  |

|------------------------------|--------------------------|-------|-----------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|--|--|

| Part Number                  |                          |       | Internal High-<br>Speed RAM <sup>Note 1</sup> | Internal Expansion<br>RAM <sup>Note 1</sup> | LCD Display RAM                                                      |  |  |

| μPD78F0471, 78F0481, 78F0491 | Flash                    | 16 KB | 768 bytes                                     | -                                           | <µPD78F047x, 78F048x>                                                |  |  |

| μPD78F0472, 78F0482, 78F0492 | memory <sup>Note 1</sup> | 24 KB | 1 KB                                          |                                             | $40\times4$ bits (36 $\times$ 8 bits)                                |  |  |

| μPD78F0473, 78F0483, 78F0493 |                          | 32 KB |                                               |                                             | $[36\times4\mbox{ bits }(32\times8\mbox{ bits })]^{\mbox{Note 2}}$   |  |  |

| μPD78F0474, 78F0484, 78F0494 |                          | 48 KB |                                               | 1 KB                                        | <µPD78F049x>                                                         |  |  |

| μPD78F0475, 78F0485, 78F0495 |                          | 60 KB |                                               |                                             | $32\times4$ bits (28 $\times$ 8 bits)                                |  |  |

|                              |                          |       |                                               |                                             | $[28\times4 \text{ bits }(24\times8 \text{ bits })]^{\text{Note 2}}$ |  |  |

- **Notes 1.** The internal flash memory, internal high-speed RAM capacities, and internal expansion RAM capacities can be changed using the internal memory size switching register (IMS) and the internal expansion RAM size switching register (IXS).

- The items in parentheses are applicable when 8com is used. The items in square brackets are applicable when using the UART6 pins (RxD6, TxD6) on the bottom side.

- O On-chip single-power-supply flash memory

- O Self-programming (with boot swap function)

- O On-chip debug function

<R>

- O On-chip power-on-clear (POC) circuit and low-voltage detector (LVI)

- O On-chip watchdog timer (operable with internal low-speed oscillation clock)

- O LCD controller/driver (external resistance division and internal resistance division are switchable)

- µPD78F047x: Segment signals: 36, Common signals: 8 (1/4 bias)

- : Segment signals: 40, Common signals: 4 (1/3 bias)

- : Segment signals: 40, Common signals: 3 (1/3, 1/2 bias)

- : Segment signals: 40, Common signals: 2 (1/2 bias)

- : Segment signals: 40, Common signals: 1 (Static)

- $\mu$ PD78F048x: Segment signals: 36, Common signals: 8 (1/4 bias)

- : Segment signals: 40, Common signals: 4 (1/3 bias)

- : Segment signals: 40, Common signals: 3 (1/3, 1/2 bias)

- : Segment signals: 40, Common signals: 2 (1/2 bias)

- : Segment signals: 40, Common signals: 1 (Static)

- µPD78F049x: Segment signals: 28, Common signals: 8 (1/4 bias)

- : Segment signals: 32, Common signals: 4 (1/3 bias)

- : Segment signals: 32, Common signals: 3 (1/3, 1/2 bias)

- : Segment signals: 32, Common signals: 2 (1/2 bias)

- : Segment signals: 32, Common signals: 1 (Static)

An outline of the timer is shown below.

|           |                         | 16-Bit Timer/<br>Event<br>Counters 00 | 8-Bit Timer/<br>Event Counters 50, 51, and 52 |           |                     | 8-Bit Tim | ners H0, H1        | Real-time<br>Counter | Watchdog<br>Timer   |           |

|-----------|-------------------------|---------------------------------------|-----------------------------------------------|-----------|---------------------|-----------|--------------------|----------------------|---------------------|-----------|

|           |                         | TM00                                  | TM50                                          | TM51      | TM52                | TMH0      | TMH1               | TMH2                 |                     |           |

| Function  | Interval timer          | 1 channel                             | 1 channel                                     | 1 channel | 1 channel           | 1 channel | 1 channel          | 1 channel            | 1 channel           | _         |

|           | External event counter  | 1 channel<br>Note 2                   | 1 channel                                     | 1 channel | 1 channel<br>Note 2 | -         | -                  | Note 2               | -                   | -         |

|           | PPG output              | 1 output                              | -                                             | -         | -                   | -         | -                  | -                    | -                   | -         |

|           | PWM output              | -                                     | 1 output                                      | 1 output  | -                   | 1 output  | 1 output           | -                    | -                   | -         |

|           | Pulse width measurement | 2 inputs                              | -                                             | -         | _                   | -         | -                  | -                    | -                   | _         |

|           | Square-wave output      | 1 output                              | 1 output                                      | 1 output  | -                   | 1 output  | 1 output           | -                    | -                   | -         |

|           | Carrier<br>generator    | -                                     | -                                             | _Note 3   | _                   | _         | 1 output<br>Note 3 | _                    | -                   | _         |

|           | calendar<br>function    | -                                     | -                                             | -         | -                   | -         | -                  | -                    | 1 channel           |           |

|           | RTC output              | -                                     | _                                             | -         | _                   | _         | -                  | _                    | 2 outputs<br>Note 4 | _         |

|           | Watchdog timer          | -                                     | _                                             | -         | -                   | -         | _                  | -                    | -                   | 1 channel |

| Interrupt | source                  | 2                                     | 1                                             | 1         | 1                   | 1         | 1                  | 1                    | 1                   | -         |

**Notes 1.** In the real-time counter, the Interval timer function and calendar function can be used simultaneously.

**2.** TM52 and TM00 can be connected in cascade to be used as a 24-bit counter. Also, the external event input of TM52 can be input enable-controlled via TMH2.

**3.** TM51 and TMH1 can be used in combination as a carrier generator mode.

4. A 1 Hz output can be used as one output and a 512 Hz, 16.384 kHz, or 32.768 kHz output can be used as one output.

# **CHAPTER 4 PORT FUNCTIONS**

#### 4.1 Port Functions

There are two types of pin I/O buffer power supplies:  $AV_{REF}^{Note}$  and  $V_{DD}$ . The relationship between these power supplies and the pins is shown below.

| Power Supply                                 | Corresponding Pins              |  |  |  |

|----------------------------------------------|---------------------------------|--|--|--|

| AV <sub>REF</sub> <sup>Note</sup> P20 to P27 |                                 |  |  |  |

| VDD                                          | Port pins other than P20 to P27 |  |  |  |

| Table 4-1. | Pin I/C | Buffer Powe | r Supplies |

|------------|---------|-------------|------------|

|------------|---------|-------------|------------|

**Note**  $\mu$ PD78F048x and 78F049x only. The power supply is VDD with  $\mu$ PD78F047x.

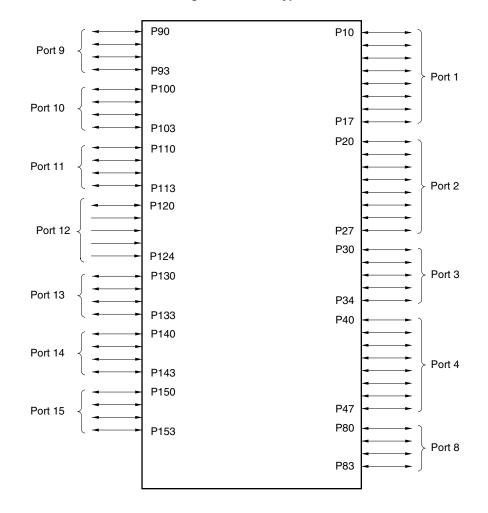

78K0/LF3 products are provided with the ports shown in Figure 4-1, which enable variety of control operations. The functions of each port are shown in Table 4-2.

In addition to the function as digital I/O ports, these ports have several alternate functions. For details of the alternate functions, see CHAPTER 2 PIN FUNCTIONS.

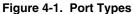

# (3) Measuring the pulse width by using one input signal of the TI000 pin (clear & start mode entered by the TI000 pin valid edge input)

Set the clear & start mode entered by the TI000 pin valid edge (TMC003 and TMC002 = 10). The count value of TM00 is captured to CR000 in the phase reverse to the valid edge of the TI000 pin, and the count value of TM00 is captured to CR010 and TM00 is cleared (0000H) when the valid edge of the TI000 pin is detected. Therefore, a cycle is stored in CR010 if TM00 does not overflow.

If an overflow occurs, take the value that results from adding 10000H to the value stored in CR010 as a cycle. Clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

## Figure 6-51. Timing Example of Pulse Width Measurement (3)

#### • TMC00 = 08H, PRM00 = 10H, CRC00 = 07H

#### (2) 8-bit timer H carrier control register 1 (TMCYC1)

This register controls the remote control output and carrier pulse output status of 8-bit timer H1. This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

#### Figure 8-9. Format of 8-Bit Timer H Carrier Control Register 1 (TMCYC1)

| Address: FF | F6DH Af | ter reset: 0 | 0H R/W | R/W <sup>Note</sup> |   |      |       |      |

|-------------|---------|--------------|--------|---------------------|---|------|-------|------|

| Symbol      | 7       | 6            | 5      | 4                   | 3 | 2    | 1     | <0>  |

| TMCYC1      | 0       | 0            | 0      | 0                   | 0 | RMC1 | NRZB1 | NRZ1 |

| RMC1 | NRZB1 | Remote control output                                       |

|------|-------|-------------------------------------------------------------|

| 0    | 0     | Low-level output                                            |

| 0    | 1     | High-level output at rising edge of INTTM51 signal input    |

| 1    | 0     | Low-level output                                            |

| 1    | 1     | Carrier pulse output at rising edge of INTTM51 signal input |

| NRZ1 | Carrier pulse output status flag                                                               |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | Carrier output disabled status (low-level status)                                              |  |  |  |  |  |

| 1    | Carrier output enabled status<br>(RMC1 = 1: Carrier pulse output, RMC1 = 0: High-level status) |  |  |  |  |  |

Note Bit 0 is read-only.

# Caution Do not rewrite RMC1 when TMHE1 = 1. However, TMCYC1 can be refreshed (the same value is written).

#### (3) Port mode register 3 (PM3)

This register sets port 3 input/output in 1-bit units.

When using the P32/TOH0/MCGO and P31/TOH1/INTP3 pins for timer output, clear PM32 and PM31 and the output latches of P32 and P31 to 0.

PM3 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to FFH.

## Figure 8-10. Format of Port Mode Register 3 (PM3)

| Address: I | F23H A | fter reset: FF | H R/W |      |      |      |      |      |

|------------|--------|----------------|-------|------|------|------|------|------|

| Symbol     | 7      | 6              | 5     | 4    | 3    | 2    | 1    | 0    |

| PM3        | 1      | 1              | 1     | PM34 | PM33 | PM32 | PM31 | PM30 |

| PM3n | P3n pin I/O mode selection $(n = 0 \text{ to } 4)$ |  |  |  |  |  |

|------|----------------------------------------------------|--|--|--|--|--|

| 0    | Dutput mode (output buffer on)                     |  |  |  |  |  |

| 1    | Input mode (output buffer off)                     |  |  |  |  |  |

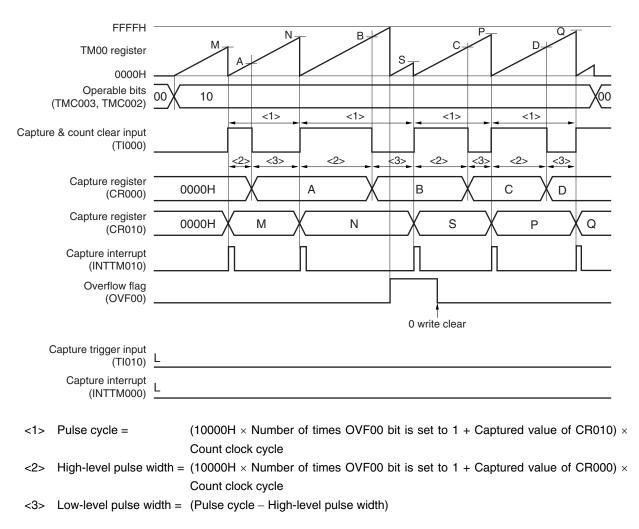

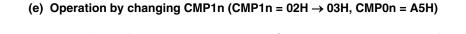

### Figure 8-14. Operation Timing in PWM Output Mode (4/4)

- <1> The count operation is enabled by setting TMHEn = 1. Start 8-bit timer counter Hn by masking one count clock to count up. At this time, PWM output outputs an inactive level.

- <2> The CMP1n register value can be changed during timer counter operation. This operation is asynchronous to the count clock.

- <3> When the values of 8-bit timer counter Hn and the CMP0n register match, the value of 8-bit timer counter Hn is cleared, an active level is output, and the INTTMHn signal is output.

<4> If the CMP1n register value is changed, the value is latched and not transferred to the register. When the values of the 8-bit timer counter Hn and the CMP1n register before the change match, the value is transferred to the CMP1n register and the CMP1n register value is changed (<2>'). However, three count clocks or more are required from when the CMP1n register value is changed to when the value is transferred to the register. If a match signal is generated within three count clocks, the changed

- <5> When the values of 8-bit timer counter Hn and the CMP1n register after the change match, an inactive level is output. 8-bit timer counter Hn is not cleared and the INTTMHn signal is not generated.

- <6> Clearing the TMHEn bit to 0 during timer Hn operation sets the INTTMHn signal to the default and PWM output to an inactive level.

**Remark** n = 0 to 2, however, TOH0 and TOH1 only for TOHn

value cannot be transferred to the register.

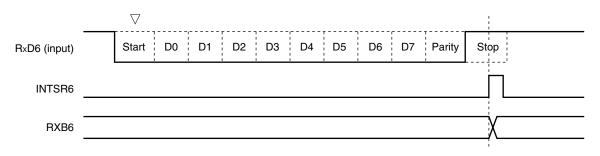

### (e) Normal reception

Reception is enabled and the RxD6 pin input is sampled when bit 7 (POWER6) of asynchronous serial interface operation mode register 6 (ASIM6) is set to 1 and then bit 5 (RXE6) of ASIM6 is set to 1.

The 8-bit counter of the baud rate generator starts counting when the falling edge of the RxD6 pin input is detected. When the set value of baud rate generator control register 6 (BRGC6) has been counted, the RxD6 pin input is sampled again ( $\bigtriangledown$  in Figure 15-21). If the RxD6 pin is low level at this time, it is recognized as a start bit.

When the start bit is detected, reception is started, and serial data is sequentially stored in the receive shift register (RXS6) at the set baud rate. When the stop bit has been received, the reception completion interrupt (INTSR6) is generated and the data of RXS6 is written to receive buffer register 6 (RXB6). If an overrun error (OVE6) occurs, however, the receive data is not written to RXB6.

Even if a parity error (PE6) occurs while reception is in progress, reception continues to the reception position of the stop bit, and a reception error interrupt (INTSR6/INTSRE6) is generated on completion of reception.

- Cautions 1. If a reception error occurs, read ASIS6 and then RXB6 to clear the error flag. Otherwise, an overrun error will occur when the next data is received, and the reception error status will persist.

- 2. Reception is always performed with the "number of stop bits = 1". The second stop bit is ignored.

- 3. Be sure to read asynchronous serial interface reception error status register 6 (ASIS6) before reading RXB6.

### (4) Port mode register 1 (PM1)

This register sets port 1 input/output in 1-bit units.

When using P11/SCK10 as the clock output pin of the serial interface, clear PM11 to 0, and set the output latches of P11 to 1.

When using P13/SO10/TxD0 as the data output pin of the serial interface, clear PM13 and the output latches of P13 to 0.

When using P11/SCK10 as the clock input pin of the serial interface and P12/SI10/RxD0 as the data input pin, set PM11 and PM12 to 1. At this time, the output latches of P11 and P12 may be 0 or 1.

PM1 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

####

| PM1n                             | P1n pin I/O mode selection (n = 0 to 7) |  |  |  |  |

|----------------------------------|-----------------------------------------|--|--|--|--|

| 0 Output mode (output buffer on) |                                         |  |  |  |  |

| 1                                | Input mode (output buffer off)          |  |  |  |  |

# Figure 16-5. Format of Port Mode Register 1 (PM1)

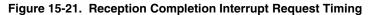

Figure 16-9. Output Value of SO10 Pin (Last Bit) (2/2)

#### User's Manual U18329EJ4V0UD

#### (1) Serial operation mode specification register 0 (CSIMA0)

This is an 8-bit register used to control the serial communication operation. This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 17-2. Format of Serial Operation Mode Specification Register 0 (CSIMA0)

Address: FF90H After reset: 00H R/W

| Symbol | <7>    | 6    | 5    | 4       | <3>   | <2>   | 1    | 0 |

|--------|--------|------|------|---------|-------|-------|------|---|

| CSIMA0 | CSIAE0 | ATE0 | ATM0 | MASTER0 | TXEA0 | RXEA0 | DIR0 | 0 |

| CSIAE0 | E0 Control of CSIA0 operation enable/disable                                                                                   |  |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0      | CSIA0 operation disabled (SOA0: Low level, SCKA0: High level) and asynchronously resets the internal circuit <sup>Note</sup> . |  |  |  |  |  |  |

| 1      | CSIA0 operation enabled                                                                                                        |  |  |  |  |  |  |

| ATE0 | Control of automatic communication operation enable/disable |

|------|-------------------------------------------------------------|

| 0    | 1-byte communication mode                                   |

| 1    | Automatic communication mode                                |

| ATM0 | Automatic communication mode specification                                                            |

|------|-------------------------------------------------------------------------------------------------------|

| 0    | Single transfer mode (stops at the address specified by the ADTP0 register)                           |

| 1    | Repeat transfer mode (after transfer is complete, clear the ADTC0 register to 00H to resume transfer) |

| MASTER0 | CSIA0 master/slave mode specification           |  |  |  |  |  |

|---------|-------------------------------------------------|--|--|--|--|--|

| 0       | Slave mode (synchronous with SCKA0 input clock) |  |  |  |  |  |

| 1       | Master mode (synchronous with internal clock)   |  |  |  |  |  |

| TXEA0 | Control of transmit operation enable/disable  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

| 0     | Transmit operation disabled (SOA0: Low level) |  |  |  |  |  |

| 1     | Transmit operation enabled                    |  |  |  |  |  |

| RXEA0 | Control of receive operation enable/disable |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

| 0     | Receive operation disabled                  |  |  |  |  |  |

| 1     | Receive operation enabled                   |  |  |  |  |  |

| DIR0 | First bit specification |

|------|-------------------------|

| 0    | MSB                     |

| 1    | LSB                     |

Note Automatic data transfer address count register 0 (ADTC0), serial trigger register 0 (CSIT0), serial I/O shift register 0 (SIOA0), and bit 0 (TSF0) of serial status register 0 (CSIS0) are reset.

#### Cautions 1. When CSIAE0 = 0, the buffer RAM cannot be accessed.

- 2. When CSIAE0 is changed from 1 to 0, the registers and bits mentioned in Note above are asynchronously initialized. To set CSIAE0 = 1 again, be sure to re-set the initialized registers.

- 3. When CSIAE0 is re-set to 1 after CSIAE0 is changed from 1 to 0, it is not guaranteed that the value of the buffer RAM will be retained.

# Figure 18-25. Three-Time-Slice LCD Drive Waveform Examples (1/2 Bias Method)

User's Manual U18329EJ4V0UD

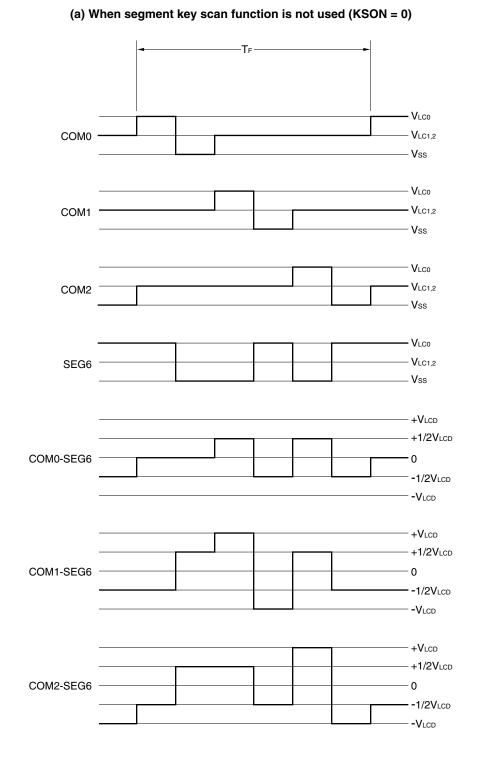

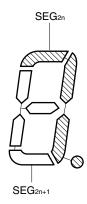

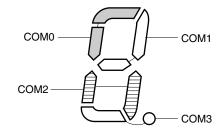

#### 18.7.4 Four-time-slice display example

Figure 18-28 shows how the 12-digit LCD panel having the display pattern shown in Figure 18-27 is connected to the segment signals (SEG0 to SEG23) and the common signals (COM0 to COM3) of the 78K0/LF3 chip. This example displays data "123456.789012" in the LCD panel. The contents of the display data memory (addresses FA40H to FA57H) correspond to this display.

The following description focuses on numeral "6." (5.) displayed in the seventh digit. To display "6." in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG12 and SEG13 pins according to Table 18-9 at the timing of the common signals COM0 to COM3; see Figure 18-27 for the relationship between the segment signals and LCD segments.

| Segment | SEG12    | SEG13  |

|---------|----------|--------|

| Common  |          |        |

| COM0    | Select   | Select |

| COM1    | Deselect | Select |

| COM2    | Select   | Select |

| СОМЗ    | Select   | Select |

Table 18-9. Select and Deselect Voltages (COM0 to COM3)

According to Table 18-9, it is determined that the display data memory location (FA4CH) that corresponds to SEG12 must contain 1101.

Figure 18-29 shows examples of LCD drive waveforms between the SEG12 signal and each common signal. When the select voltage is applied to SEG12 at the timing of COM0, an alternate rectangle waveform,  $+V_{LCD}/-V_{LCD}$ , is generated to turn on the corresponding LCD segment.

**Remark** n = 0 to 11

#### (b) MCG control register 1 (MC0CTL1)

This register is used to set the base clock of the Manchester code generator. This register can be set by an 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

| Symbol  | 7 | 6 | 5 | 4 | 3 | 2       | 1       | 0       |

|---------|---|---|---|---|---|---------|---------|---------|

| MC0CTL1 | 0 | 0 | 0 | 0 | 0 | MC0CKS2 | MC0CKS1 | MC0CKS0 |

| Address: FF4DH | After reset: 00H | R/W |

|----------------|------------------|-----|

|----------------|------------------|-----|

| MC0CKS2 | MC0CKS1 | MC0CKS0 | Base clock (fxcLk) selection <sup>Note 1</sup> |

|---------|---------|---------|------------------------------------------------|

| 0       | 0       | 0       | fprs <sup>Note 2</sup> (10 MHz)                |

| 0       | 0       | 1       | fprs/2 (5 MHz)                                 |

| 0       | 1       | 0       | fprss/2 <sup>2</sup> (2.5 MHz)                 |

| 0       | 1       | 1       | fprs/2 <sup>3</sup> (1.25 MHz)                 |

| 1       | 0       | 0       | fprs/2⁴ (625 kHz)                              |

| 1       | 0       | 1       | fprs/2 <sup>5</sup> (312.5 kHz)                |

| 1       | 1       | 0       |                                                |

| 1       | 1       | 1       |                                                |

# **Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fPRs  $\leq$  5 MHz

- 2. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V  $\leq$  VDD < 2.7 V, the setting of MC0CKS2 = MC0CKS1 = MC0CKS0 = 0 (base clock: fPRs) is prohibited.

# Caution Clear bit 7 (MC0PWR) of the MC0CTL0 register to 0 before rewriting the MC0CKS2 to MC0CKS0 bits.

- Remarks 1. fprs: Peripheral hardware clock frequency

- 2. Figures in parentheses are for operation with fPRs = 10 MHz.

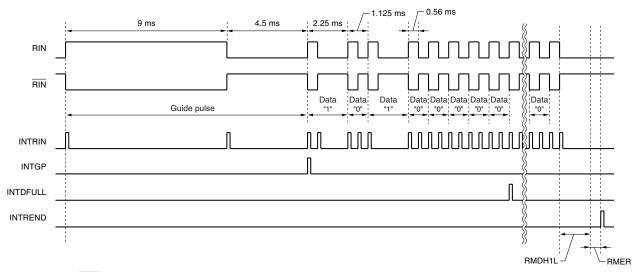

#### 20.4.3 Format of type B reception mode

Figure 20-8 shows the data format for type B.

#### Figure 20-8. Example of Type B Data Format

**Remark** RIN is the internally inverted signal of RIN.

#### 20.4.4 Operation flow of type B reception mode

Figure 20-9 shows the operation flow.

#### Cautions 1. When INTRERR is generated, RMSR and RMSCR are automatically cleared immediately.

- 2. When data has been set to all the bits of RMSR, the following processing is automatically performed.

- The value of RMSR is transferred to RMDR.

- INTDFULL is generated.

- RMSR is cleared.

RMDR must then be read before the next data is set to all the bits of RMSR.

- When INTREND has been generated, read RMSCR first followed by RMSR.

When RMSR has been read, RMSCR and RMSR are automatically cleared.

If INTREND is generated, the next data cannot be received until RMSR is read.

- 4. RMSR, RMSCR, and RMDR are cleared simultaneously to operation termination (RMEN = 0).

# 21.3 Registers Controlling Interrupt Functions

The following 6 types of registers are used to control the interrupt functions.

- Interrupt request flag register (IF0L, IF0H, IF1L, IF1H)

- Interrupt mask flag register (MK0L, MK0H, MK1L, MK1H)

- Priority specification flag register (PR0L, PR0H, PR1L, PR1H)

- External interrupt rising edge enable register (EGP)

- External interrupt falling edge enable register (EGN)

- Program status word (PSW)

Table 21-2 shows a list of interrupt request flags, interrupt mask flags, and priority specification flags corresponding to interrupt request sources.

| Interrupt | Interrupt Request | Interrupt Request Flag |                | lag      | Priority Specification Flag |          |

|-----------|-------------------|------------------------|----------------|----------|-----------------------------|----------|

| Source    |                   | Register               |                | Register |                             | Register |

| INTLVI    | LVIIF             | IF0L                   | LVIMK          | MKOL     | LVIPR                       | PROL     |

| INTP0     | PIF0              |                        | PMK0           |          | PPR0                        |          |

| INTP1     | PIF1              |                        | PMK1           |          | PPR1                        |          |

| INTP2     | PIF2              |                        | PMK2           |          | PPR2                        |          |

| INTP3     | PIF3              |                        | РМКЗ           |          | PPR3                        |          |

| INTP4     | PIF4              |                        | PMK4           |          | PPR4                        |          |

| INTP5     | PIF5              |                        | PMK5           |          | PPR5                        |          |

| INTSRE6   | SREIF6            |                        | SREMK6         | -        | SREPR6                      |          |

| INTSR6    | SRIF6             | IF0H                   | SRMK6          | МКОН     | SRPR6                       | PR0H     |

| INTST6    | STIF6             |                        | STMK6          |          | STPR6                       |          |

| INTCSI10  | CSIIF10 Note 1    |                        | CSIMK10 Note 2 |          | CSIPR10 Note 3              |          |

| INTST0    | STIF0 Note 1      |                        | STMK0 Note 2   |          | STPR0 Note 3                |          |

| INTTMH1   | TMIFH1            |                        | TMMKH1         |          | TMPRH1                      |          |

| INTTMH0   | TMIFH0            |                        | ТММКНО         | -        | TMPRH0                      |          |

| INTTM50   | TMIF50            | ]                      | TMMK50         |          | TMPR50                      | ]        |

| INTTM000  | TMIF000           |                        | ТММК000        |          | TMPR000                     |          |

| INTTM010  | TMIF010           |                        | TMMK010        |          | TMPR010                     |          |

Table 21-2. Flags Corresponding to Interrupt Request Sources (1/2)

Notes 1. If either interrupt source INTCSI10 or INTST0 is generated, bit 2 of IF0H is set (1).

- 2. Bit 2 of MK0H supports both interrupt sources INTCSI10 and INTST0.

- 3. Bit 2 of PR0H supports both interrupt sources INTCSI10 and INTST0.

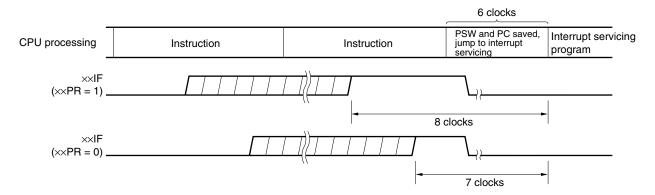

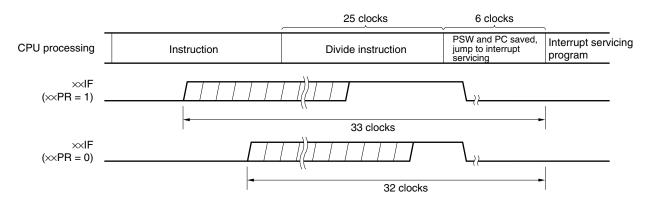

#### Figure 21-8. Interrupt Request Acknowledgment Timing (Minimum Time)

Remark 1 clock: 1/fcpu (fcpu: CPU clock)

#### 21.4.2 Software interrupt request acknowledgment

A software interrupt acknowledge is acknowledged by BRK instruction execution. Software interrupts cannot be disabled.

If a software interrupt request is acknowledged, the contents are saved into the stacks in the order of the program status word (PSW), then program counter (PC), the IE flag is reset (0), and the contents of the vector table (003EH, 003FH) are loaded into the PC and branched.

Restoring from a software interrupt is possible by using the RETB instruction.

#### Caution Do not use the RETI instruction for restoring from the software interrupt.

|                                                                | Hardware                                                         | After Reset<br>Acknowledgment <sup>№te 1</sup>                 |

|----------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|

| Program counter (PC)                                           |                                                                  | The contents of the reset vector table (0000H, 0001H) are set. |

| Stack pointer (SP)                                             |                                                                  | Undefined                                                      |

| Program status wor                                             | rd (PSW)                                                         | 02H                                                            |

| RAM                                                            | Data memory                                                      | Undefined <sup>Note 2</sup>                                    |

|                                                                | General-purpose registers                                        | Undefined <sup>Note 2</sup>                                    |

| Port registers (P1 to P4, P8 to P15) (output latches)          |                                                                  | 00H                                                            |

| Port mode registers (PM1 to PM4, PM8 to PM15)                  |                                                                  | FFH                                                            |

| Pull-up resistor option registers (PU1, PU3, PU4, PU8 to PU15) |                                                                  | 00H                                                            |

| Port function register 1 (PF1)                                 |                                                                  | 00H                                                            |

| Port function register 2 (PF2)                                 |                                                                  | 00H                                                            |

| Port function register ALL (PFALL)                             |                                                                  | 00H                                                            |

| Internal expansion RAM size switching register (IXS)           |                                                                  | 0CH <sup>Note 3</sup>                                          |

| Internal memory size switching register (IMS)                  |                                                                  | CFH <sup>Note 3</sup>                                          |

| Clock operation mode select register (OSCCTL)                  |                                                                  | 00H                                                            |

| Processor clock control register (PCC)                         |                                                                  | 01H                                                            |

| Internal oscillation r                                         | node register (RCM)                                              | 80H                                                            |

| Main OSC control register (MOC)                                |                                                                  | 80H                                                            |

| Main clock mode register (MCM)                                 |                                                                  | 00H                                                            |

| Oscillation stabilization time counter status register (OSTC)  |                                                                  | 00H                                                            |

| Oscillation stabilization time select register (OSTS)          |                                                                  | 05H                                                            |

| Internal high-speed                                            | oscillation trimming register (HIOTRM)                           | 10H                                                            |

| 16-bit timer/event                                             | Timer counters 00 (TM00)                                         | 0000H                                                          |

| counters 00                                                    | Capture/compare registers 000, 010 (CR000, CR010)                | 0000H                                                          |

|                                                                | Mode control registers 00 (TMC00)                                | 00H                                                            |

|                                                                | Prescaler mode registers 00 (PRM00)                              | 00H                                                            |

|                                                                | Capture/compare control registers 00 (CRC00)                     | 00H                                                            |

|                                                                | Timer output control registers 00 (TOC00)                        | 00H                                                            |

| 8-bit timer/event<br>counters 50, 51, 52                       | Timer counters 50, 51, 52 (TM50, TM51, TM52)                     | 00H                                                            |

|                                                                | Compare registers 50, 51, 52 (CR50, CR51, CR52)                  | 00H                                                            |

|                                                                | Timer clock selection registers 50, 51, 52 (TCL50, TCL51, TCL52) | 00H                                                            |

|                                                                | Mode control registers 50, 51, 52 (TMC50, TMC51, TMC52)          | 00H                                                            |

#### Table 24-2. Hardware Statuses After Reset Acknowledgment (1/4)

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

- 2. When a reset is executed in the standby mode, the pre-reset status is held even after reset.

- **3.** The initial values of the internal memory size switching register (IMS) and internal expansion RAM size switching register (IXS) after a reset release are constant (IMS = CFH, IXS = 0CH) in all the 78K0/LF3 products, regardless of the internal memory capacity. Therefore, after a reset is released, be sure to set the following values for each product.

| Flash Memory Version<br>(78K0/LF3) | IMS | IXS |

|------------------------------------|-----|-----|

| μPD78F0471, 78F0481, 78F0491       | 04H | 0CH |

| μPD78F0472, 78F0482, 78F0492       | C6H |     |

| μPD78F0473, 78F0483, 78F0493       | C8H |     |

| µPD78F0474, 78F0484, 78F0494       | ССН | 0AH |

| μPD78F0475, 78F0485, 78F0495       | CFH |     |

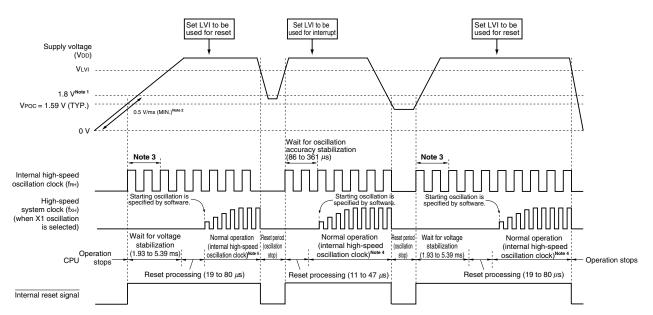

# Figure 25-2. Timing of Generation of Internal Reset Signal by Power-on-Clear Circuit and Low-Voltage Detector (1/2)

# (1) In 1.59 V POC mode (option byte: POCMODE = 0)

- **Notes 1.** The operation guaranteed range is  $1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}$ . To make the state at lower than 1.8 V reset state when the supply voltage falls, use the reset function of the low-voltage detector, or input the low level to the  $\overline{\text{RESET}}$  pin.

- 2. If the voltage rises to 1.8 V at a rate slower than 0.5 V/ms (MIN.) on power application, input a low level to the RESET pin after power application and before the voltage reaches 1.8 V, or set the 2.7 V/1.59 V POC mode by using an option byte (POCMODE = 1).

- **3.** The internal voltage stabilization time includes the oscillation accuracy stabilization time of the internal high-speed oscillation clock.

- 4. The internal high-speed oscillation clock and a high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the OSTC register to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

- Caution Set the low-voltage detector by software after the reset status is released (see CHAPTER 26 LOW-VOLTAGE DETECTOR).

- Remark

VLVI:

LVI detection voltage

VPOC:

POC detection voltage

<R>

# **CHAPTER 30 INSTRUCTION SET**

This chapter lists each instruction set of the 78K0/LF3 in table form. For details of each operation and operation code, refer to the separate document **78K/0 Series Instructions User's Manual (U12326E)**.

#### **30.1 Conventions Used in Operation List**

#### 30.1.1 Operand identifiers and specification methods

Operands are written in the "Operand" column of each instruction in accordance with the specification method of the instruction operand identifier (refer to the assembler specifications for details). When there are two or more methods, select one of them. Uppercase letters and the symbols #, !, \$ and [] are keywords and must be written as they are. Each symbol has the following meaning.

- #: Immediate data specification

- !: Absolute address specification

- \$: Relative address specification

- []: Indirect address specification

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, be sure to write the #, !, \$, and [] symbols.

For operand register identifiers r and rp, either function names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be used for specification.

| Identifier | Specification Method                                                                     |

|------------|------------------------------------------------------------------------------------------|

| r          | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7)                           |

| rp         | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                                                   |

| sfr        | Special function register symbol <sup>Note</sup>                                         |

| sfrp       | Special function register symbol (16-bit manipulatable register even addresses only)Note |

| saddr      | FE20H to FF1FH Immediate data or labels                                                  |

| saddrp     | FE20H to FF1FH Immediate data or labels (even address only)                              |

| addr16     | 0000H to FFFFH Immediate data or labels                                                  |

|            | (Only even addresses for 16-bit data transfer instructions)                              |

| addr11     | 0800H to 0FFFH Immediate data or labels                                                  |

| addr5      | 0040H to 007FH Immediate data or labels (even address only)                              |

| word       | 16-bit immediate data or label                                                           |

| byte       | 8-bit immediate data or label                                                            |

| bit        | 3-bit immediate data or label                                                            |

| RBn        | RB0 to RB3                                                                               |

Table 30-1. Operand Identifiers and Specification Methods

**Note** Addresses from FFD0H to FFDFH cannot be accessed with these operands.

Remark For special function register symbols, see Table 3-6 Special Function Register List.

|                   |                                                                                                                                              | (3/3           |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Page              | Description                                                                                                                                  | Classification |

| -                 |                                                                                                                                              | 1              |

| p. 666            | Change of Figure 24-2. Timing of Reset by RESET Input                                                                                        | (c)            |

| p. 666            | Change of Figure 24-3. Timing of Reset Due to Watchdog Timer Overflow                                                                        | (c)            |

| p. 667            | Change of Figure 24-4. Timing of Reset in STOP Mode by RESET Input                                                                           | (c)            |

| CHAPTER 25        | POWER-ON-CLEAR CIRCUIT                                                                                                                       | 1              |

| p. 676            | Change of Figure 25-2. Timing of Generation of Internal Reset Signal by Power-on-Clear<br>Circuit and Low-Voltage Detector (1)               | (b)            |

| p. 677            | Change of Caution 2 in Figure 25-2. Timing of Generation of Internal Reset Signal by Power-<br>on-Clear Circuit and Low-Voltage Detector (2) | (b, c)         |

| CHAPTER 26        | COW-VOLTAGE DETECTOR                                                                                                                         |                |

| p. 697            | Change of Figure 26-9. Example of Software Processing After Reset Release (2/2)                                                              | (c)            |

| CHAPTER 28        | B FLASH MEMORY                                                                                                                               |                |

| p. 705            | Change of Note 2 in and addition of Caution to Table 28-3. Wiring Between 78K0/LF3 and Dedicated Flash memory programmer                     | (c)            |

| р. 709            | Change of Note 1 in Table 28-4. Pin Connection                                                                                               | (c)            |

| p. 712            | Change of Caution 2 in 28.6.6 Other signal pins                                                                                              | (c)            |

| p. 713            | Change of Figure 28-12. Flash Memory Manipulation Procedure                                                                                  | (b)            |

| p. 714            | Change of Table 28-7. Communication Modes                                                                                                    | (b)            |

| pp. 718 to<br>720 | Addition of 28.9 Processing Time for Each Command When PG-FP5 Is Used (Reference)                                                            | (b, c)         |

| pp. 721 to<br>730 | Revision of 28.10 Flash Memory Programming by Self-Programming                                                                               | (b, c)         |

| CHAPTER 29        | ON-CHIP DEBUG FUNCTION                                                                                                                       |                |

| pp. 731, 732      | Full-scale revision of chapter                                                                                                               | (C)            |

| CHAPTER 31        | ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS)                                                                                                |                |

| р. 746            | Addition of Caution                                                                                                                          | (C)            |

| р. 750            | Addition of Recommended Oscillator Constants                                                                                                 | (b)            |

| p. 754            | Change of Supply current value and Notes 1, 6 in and addition of Note 5 to DC Characteristics                                                | (b)            |

| p. 755            | Change of $\Delta\Sigma$ type A/D converter operating current value in <b>DC Characteristics</b>                                             | (b)            |

| p. 765            | Change of 16-bit ΔΣ type A/D Converter Characteristics                                                                                       | (b)            |

| p. 766            | Change of Note 3 in LCD Characteristics                                                                                                      | (b)            |

| p. 769            | Change of <b>Basic characteristics</b> in <b>Flash Memory Programming Characteristics</b> and addition of <b>Notes 1</b> , 4                 | (b, c)         |

| CHAPTER 33        |                                                                                                                                              | u              |

| p. 772            | Addition of chapter                                                                                                                          | (b, c)         |

| APPENDIX A        | DEVELOPMENT TOOLS                                                                                                                            |                |

| pp. 775 to<br>782 | Addition of appendix A                                                                                                                       | (c)            |

**Remark** "Classification" in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,(d): Addition/change of package, part number, or management division, (e): Addition/change of related documents