#### Welcome to E-XFL.COM

**Renesas Electronics America Inc - DF2633F25IV Datasheet**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 73                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b; D/A 4x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 128-BFQFP                                                                    |

| Supplier Device Package    | 128-QFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2633f25iv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# H8S/2633 Group Manuals:

| Document Title                                   | Document No. |

|--------------------------------------------------|--------------|

| H8S/2633 Group Hardware Manual                   | This manual  |

| H8S/2600 Series, H8S/2000 Series Software Manual | REJ09B0139   |

Users Manuals for Development Tools:

| Document Title                                                                          | Document No. |

|-----------------------------------------------------------------------------------------|--------------|

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimized Linkage<br>Editor User's Manual | REJ10J2039   |

| H8S, H8/300 Series Simulator/Debugger User's Manual                                     | REJ10B0211   |

| High-performance Embedded Workshop User's Manual                                        | REJ10J2169   |

# Application Notes:

| Document Title             | Document No. |

|----------------------------|--------------|

| H8S Family Technical Q & A | REJ05B0397   |

| Item                                                                    | Page | Revision (See M                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Manu                                           | al foi                                           | r Deta                                                      | ails)                          |                             |                                           |                                            |                                              |                                        |                                      |

|-------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|--------------------------------|-----------------------------|-------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------|--------------------------------------|

| 18.4 Usage Notes                                                        | 893  | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

| Table 18.8 I <sup>2</sup> C Bus                                         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |                                                  |                                                             | lication (                     | at Maxim                    | um Trans                                  | ier Rate)                                  | [ns]                                         |                                        |                                      |

| Timing (with Maximum Influence of $t_{\rm S}/t_{\rm Si}$ )              |      | $\begin{array}{c} t_{cyc} \\ \textbf{Item Indication} \\ t_{\text{SOAGO}} & 1t_{\text{SOLIO}} \overset{\text{*}}{=} -3t_{cyc} \\ (\text{master}) & (-t_{sr}) & \text{mode} \end{array}$                                                                                                                                                                                                                                                                                       | l<br>(<br>ndard -                              | s/t <sub>sr</sub><br>nfluence<br>(Max.)<br>-1000 | I <sup>2</sup> C Bus<br>Specifi-<br>cation<br>(Min.)<br>250 | φ =<br>5 MHz<br>3100           | φ =<br>8 MHz<br>3325        | ¢ =<br><b>10 MHz</b><br>3400              | ¢ =<br>16 MHz<br>3513                      | ¢ =<br><b>20 MHz</b><br>3550                 | ¢ =<br><b>25 MHz</b><br>3580           | φ =<br>28 MHz<br>3593                |

|                                                                         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n-speed -                                      | -300                                             | 100                                                         | 400                            | 625                         | 700                                       | 813                                        | 850                                          | 880                                    | 893                                  |

|                                                                         |      | $t_{SDASO}$ $1t_{SCLL}^{*3}-12t_{cyc}^{*2}$ Stand<br>(slave) $(-t_{sr})$ mode                                                                                                                                                                                                                                                                                                                                                                                                 | ndard -                                        | -1000                                            | 250                                                         | 3100                           | 3325                        | 3400                                      | 3513                                       | 3550                                         | 3580                                   | 3593                                 |

|                                                                         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n-speed -                                      | -300                                             | 100                                                         | 400                            | 625                         | 700                                       | 813                                        | 850                                          | 880                                    | 893                                  |

|                                                                         |      | Notes amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

|                                                                         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                | on the                                           |                                                             | ( hit i                        | s sat                       | to 1                                      | Whe                                        | n the                                        | IICX                                   | hit is                               |

|                                                                         |      | Notes 2. Value when the IICX bit is set to 1. When the IICX bit is cleared to 0, the value is $(1t_{scll} - 6t_{orc})$ .                                                                                                                                                                                                                                                                                                                                                      |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

|                                                                         |      | <ol> <li>Calculated using the l<sup>2</sup>C bus specification values<br/>(standard mode: 4700 ns min.; high-speed mode: 1300<br/>ns min.).</li> </ol>                                                                                                                                                                                                                                                                                                                        |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

|                                                                         | 902  | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

|                                                                         |      | Notes on Wait Operation in Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

|                                                                         |      | During master mode operation using the wait function, when<br>the interrupt flag IRIC bit is cleared from 1 to 0 between the<br>falling edge of the 7th clock cycle and the falling edge of the<br>8th clock cycle, in some cases no wait is inserted after the<br>falling edge of the 8th clock cycle and the clock pulse of the 9th<br>clock cycle is output continuously.<br>Observe the following with regard to clearing the IRIC flag<br>while using the wait function. |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              | e<br>ie                                |                                      |

|                                                                         |      | At the rising<br>and then clea<br>cycle (while t<br>greater).<br>If clearing of<br>the like and t<br>the SCL pin s                                                                                                                                                                                                                                                                                                                                                            | ar it to<br>the va<br>the II<br>the B<br>state | o zero<br>alue c<br>RIC fl<br>C cou<br>is lov    | o befo<br>of the<br>ag is<br>unter<br>v-leve                | bre th<br>BC2<br>dela<br>value | to B<br>yed b<br>reader the | ong eo<br>C0 cc<br>by inte<br>ches<br>BC2 | lge o<br>ounte<br>errupt<br>1 or 0<br>to B | f the<br>r valu<br>t proc<br>), cor<br>C0 cc | 1st cl<br>ie is 2<br>cessir<br>nfirm t | ock<br>2 or<br>ng or<br>hat<br>r has |

|                                                                         |      | reached 0 ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nd the                                         | en cle                                           | ar the                                                      | e IRI                          | C flag                      | g. (Se                                    | e figu                                     | ure 18                                       | 8.28.)                                 |                                      |

| Figure 18.28<br>Timing of IRIC Flag<br>Clearing During Wai<br>Operation | t    | Figure added                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                |                                                  |                                                             |                                |                             |                                           |                                            |                                              |                                        |                                      |

| Bit 3 | Bit 2 | Bit 1 | Bit 0 |                                                                                 |

|-------|-------|-------|-------|---------------------------------------------------------------------------------|

| AE3   | AE2   | AE1   | AE0   | <br>Description                                                                 |

| 0     | 0     | 0     | 0     | A8–A23 address output disabled (Initial value*)                                 |

|       |       |       | 1     | A8 address output enabled; A9–A23 address output disabled                       |

|       |       | 1     | 0     | A8, A9 address output enabled; A10–A23 address output disabled                  |

|       |       |       | 1     | A8–A10 address output enabled; A11–A23 address output disabled                  |

|       | 1     | 0     | 0     | A8–A11 address output enabled; A12–A23 address output disabled                  |

|       |       |       | 1     | A8–A12 address output enabled; A13–A23 address output disabled                  |

|       |       | 1     | 0     | A8–A13 address output enabled; A14–A23 address output disabled                  |

|       |       |       | 1     | A8–A14 address output enabled; A15–A23 address output disabled                  |

| 1     | 0     | 0     | 0     | A8–A15 address output enabled; A16–A23 address output disabled                  |

|       |       |       | 1     | A8–A16 address output enabled; A17–A23 address output disabled                  |

|       |       | 1     | 0     | A8–A17 address output enabled; A18–A23 address output disabled                  |

|       |       |       | 1     | A8–A18 address output enabled; A19–A23 address output disabled                  |

|       | 1     | 0     | 0     | A8–A19 address output enabled; A20–A23 address output disabled                  |

|       |       |       | 1     | A8–A20 address output enabled; A21–A23 address output disabled (Initial value*) |

|       |       | 1     | 0     | A8–A21 address output enabled; A22, A23 address output disabled                 |

|       |       |       | 1     | A8–A23 address output enabled                                                   |

Note: \* In expanded mode with ROM, bits AE3 to AE0 are initialized to B'0000. In ROMIess expanded mode, bits AE3 to AE0 are initialized to B'1101. Address pins A0 to A7 are made address outputs by setting the corresponding DDR bits to 1.

| Name                                | Symbol | I/O    | Function                                                                                                         |

|-------------------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------|

| Lower column<br>strobe <sup>*</sup> | LCAS*  | Output | DRAM lower column address strobe signal*                                                                         |

| Wait                                | WAIT   | Input  | Wait request signal when accessing external 3-state access space.                                                |

| Bus request                         | BREQ   | Input  | Request signal that releases bus to external device.                                                             |

| Bus request<br>acknowledge          | BACK   | Output | Acknowledge signal indicating that bus has been released.                                                        |

| Bus request output                  | BREQO  | Output | External bus request signal used when internal bus master accesses external space when external bus is released. |

Note: \* This function is not available in the H8S/2695.

#### 7.1.4 Register Configuration

Table 7.2 summarizes the registers of the bus controller.

### Table 7.2 Bus Controller Registers

|                                |                     |     | Initial           |                 |                       |

|--------------------------------|---------------------|-----|-------------------|-----------------|-----------------------|

| Name                           | Abbreviation        | R/W | Power-On<br>Reset | Manual<br>Reset | Address <sup>*1</sup> |

| Bus width control register     | ABWCR               | R/W | H'FF/H'00*2       | Retained        | H'FED0                |

| Access state control register  | ASTCR               | R/W | H'FF              | Retained        | H'FED1                |

| Wait control register H        | WCRH                | R/W | H'FF              | Retained        | H'FED2                |

| Wait control register L        | WCRL                | R/W | H'FF              | Retained        | H'FED3                |

| Bus control register H         | BCRH                | R/W | H'D0              | Retained        | H'FED4                |

| Bus control register L         | BCRL                | R/W | H'08              | Retained        | H'FED5                |

| Pin function control register  | PFCR                | R/W | H'0D/H'00         | Retained        | H'FDEB                |

| Memory control register        | MCR <sup>*3</sup>   | R/W | H'00              | Retained        | H'FED6                |

| DRAM control register          | DRAMCR*3            | R/W | H'00              | Retained        | H'FED7                |

| Refresh timer counter          | RTCNT <sup>*3</sup> | R/W | H'00              | Retained        | H'FED8                |

| Refresh time constant register | RTCOR*3             | R/W | H'FF              | Retained        | H'FED9                |

|                                |                     |     |                   |                 |                       |

Notes: 1. Lower 16 bits of the address.

- 2. Determined by the MCU operating mode.

- 3. This function is not available in the H8S/2695.

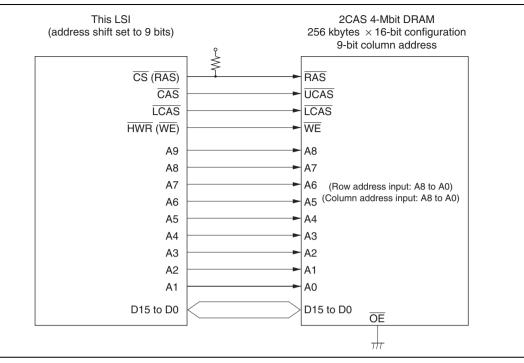

Figure 7.20 High-speed Page Mode DRAM

| Port   | Description                                | Pins                    | Mode 4                        | Mode 5                                     | Mode 6     | Mode 7                                  |  |  |  |

|--------|--------------------------------------------|-------------------------|-------------------------------|--------------------------------------------|------------|-----------------------------------------|--|--|--|

| Port E | • 8-bit I/O                                | PE7/D7                  | In 8-bit-bus mod              | I/O port                                   |            |                                         |  |  |  |

|        | port                                       | PE6/D6                  | In 16-bit-bus mo              |                                            |            |                                         |  |  |  |

|        | <ul> <li>Built-in<br/>MOS input</li> </ul> | PE5/D5                  |                               |                                            |            |                                         |  |  |  |

|        | pull-up                                    | PE4/D4                  |                               |                                            |            |                                         |  |  |  |

|        |                                            | PE3/D3                  |                               |                                            |            |                                         |  |  |  |

|        |                                            | PE2/D2                  |                               |                                            |            |                                         |  |  |  |

|        |                                            | PE1/D1                  |                               |                                            |            |                                         |  |  |  |

|        |                                            | PE0 /D0                 |                               |                                            |            |                                         |  |  |  |

| Port F | • 8-bit I/O                                | PF7/ø                   | When DDR = 0:                 | input port                                 |            | When                                    |  |  |  |

|        | port                                       |                         | When DDR = 1                  | (after reset): $\phi$ or                   | utput      | DDR = 0 (after<br>reset): input<br>port |  |  |  |

|        |                                            |                         |                               |                                            |            | When<br>DDR = 1: φ<br>output            |  |  |  |

|        |                                            | PF6 /AS/LCAS            | RD, HWR, LWF                  | ₹ outputs                                  |            | I/O port                                |  |  |  |

|        |                                            | PF5 /RD                 | ADTRG, IRQ3 i                 | nput                                       |            | ADTRG, IRQ3                             |  |  |  |

|        |                                            | PF4 / <del>HWR</del>    | When LCASS =                  | 0: AS output                               |            | input                                   |  |  |  |

|        |                                            | PF3/LWR/ADTRG/<br>IRQ3  |                               | O RMTS0 = B'00<br>CASS = 1: LCAS           |            |                                         |  |  |  |

|        |                                            | PF2/LCAS/WAIT/<br>BREQO | When WAITE = reset): I/O port | 0 and BREQOE                               | = 0 (after | I/O port                                |  |  |  |

|        |                                            |                         | When WAITE =<br>input         | 1 and BREQOE                               | = 0: WAIT  |                                         |  |  |  |

|        |                                            |                         | When WAITE =<br>input         | 0 and BREQOE                               | = 1: BREQO |                                         |  |  |  |

|        |                                            |                         |                               | o RMTS0 = $B'00$<br>CASS = 0: LCAS         |            |                                         |  |  |  |

|        |                                            | PF1/BACK/BUZZ           | When BRLE = 0                 | ) (after reset): I/C                       | ) port     | BUZZ output                             |  |  |  |

|        |                                            | PF0/BREQ/IRQ2           | When BRLE = 1                 | I: $\overline{BREQ}$ input, $\overline{B}$ | ACK output | IRQ2 input                              |  |  |  |

|        |                                            |                         | BUZZ output, IF               | RQ2 input                                  |            | I/O port                                |  |  |  |

# 10A.8 Port B

# 10A.8.1 Overview

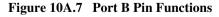

Port B is an 8-bit I/O port. Port B pins also function as TPU I/O pins (TIOCA3, TIOCB3, TIOCC3, TIOCD3, TIOCA4, TIOCB4, TIOCA5, and TIOCB5) and as address outputs; the pin functions change according to the operating mode.

Port B has a built-in MOS input pull-up function that can be controlled by software.

Figure 10A.7 shows the port B pin configuration.

|        | Port B pins                                                                                                | Pin functions in modes 4 to 6                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>PB7/A15/TIOCB5</li> <li>PB6/A14/TIOCA5</li> <li>PB5/A13/TIOCB4</li> <li>PB4/A12/TIOCA4</li> </ul> | PB7 (I/O) / A15 (output) / TIOCB5 (I/O)<br>PB6 (I/O) / A14 (output) / TIOCA5 (I/O)<br>PB5 (I/O) / A13 (output) / TIOCB4 (I/O)<br>PB4 (I/O) / A12 (output) / TIOCA4 (I/O) |

| Port B | <ul> <li>PB3/A11/TIOCD3</li> <li>PB2/A10/TIOCC3</li> <li>PB1/A9 /TIOCB3</li> <li>PB0/A8 /TIOCA3</li> </ul> | PB3 (I/O) / A11 (output) / TIOCD3 (I/O)<br>PB2 (I/O) / A10 (output) / TIOCC3 (I/O)<br>PB1 (I/O) / A9 (output) / TIOCB3 (I/O)<br>PB0 (I/O) / A8 (output) / TIOCA3 (I/O)   |

|        |                                                                                                            | Pin functions in mode 7                                                                                                                                                  |

|        |                                                                                                            | PB7 (I/O) / TIOCB5 (I/O)<br>PB6 (I/O) / TIOCA5 (I/O)                                                                                                                     |

|        |                                                                                                            | PB5 (I/O) / TIOCB4 (I/O)<br>PB4 (I/O) / TIOCA4 (I/O)                                                                                                                     |

|        |                                                                                                            | PB3 (I/O) / TIOCD3 (I/O)<br>PB2 (I/O) / TIOCC3 (I/O)                                                                                                                     |

|        |                                                                                                            | PB1 (I/O) / TIOCB3 (I/O)<br>PB0 (I/O) / TIOCA3 (I/O)                                                                                                                     |

# 10A.8.4 MOS Input Pull-Up Function

Port B has a built-in MOS input pull-up function that can be controlled by software. MOS input pull-up can be specified as on or off on an individual bit basis.

In modes 4 to 6, if a pin is in the input state in accordance with the settings in PFCR, in the TPU's TIOR, and in DDR, setting the corresponding PBPCR bit to 1 turns on the MOS input pull-up for that pin.

In mode 7, if a pin is in the input state in accordance with the settings in the TPU's TIOR and in DDR, setting the corresponding PBPCR bit to 1 turns on the MOS input pull-up for that pin.

The MOS input pull-up function is in the off state after a power-on reset, and in hardware standby mode. The prior state is retained by a manual reset or in software standby mode.

Table 10A.15 summarizes the MOS input pull-up states.

### Table 10A.15 MOS Input Pull-Up States (Port B)

| Pin States                      | Power-On<br>Reset | Hardware<br>Standby Mode | Manual<br>Reset | Software<br>Standby Mode | In Other<br>Operations |

|---------------------------------|-------------------|--------------------------|-----------------|--------------------------|------------------------|

| Address output or<br>TPU output | OFF               | OFF                      | OFF             | OFF                      | OFF                    |

| Other than above                |                   |                          | ON/OFF          | ON/OFF                   | ON/OFF                 |

Legend:

OFF: MOS input pull-up is always off.

ON/OFF: On when PBDDR = 0 and PBPCR = 1; otherwise off.

# 10B.2.3 Pin Functions

Port 1 pins also function as TPU I/O pins (TCLKA, TCLKB, TCLKC, TCLKD, TIOCA0, TIOCB0, TIOCC0, TIOCD0, TIOCA1, TIOCB1, TIOCA2, and TIOCB2), external interrupt input pins (IRQ0 and IRQ1), and address bus output pins (A23 to A20). Port 1 pin functions are shown in table 10B.3.

#### Table 10B.3 Port 1 Pin Functions

| Pin                                                                                                                                                                                                                                                                                   | Selection Meth           | od and Pi                        | n Functior                                 | IS         |                     |                         |          |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|--------------------------------------------|------------|---------------------|-------------------------|----------|--|--|

| P17/TIOCB2/<br>TCLKD The pin function is switched as shown below according to the combination o<br>the TPU channel 2 setting (by bits MD3 to MD0 in TMDR2, bits IOB3 to IOB0<br>in TIOR2, and bits CCLR1 and CCLR0 in TCR2), bits TPSC2 to TPSC0 in<br>TCR0 and TCR5, and bit P17DDR. |                          |                                  |                                            |            |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | TPU Channel<br>2 Setting |                                  |                                            |            |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | P17DDR — 0 1             |                                  |                                            |            |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | Pin function             | TIOCB2 output P17 input P17 outp |                                            |            |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | TIOCB2 input*1           |                                  |                                            |            |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       |                          |                                  |                                            | TCLKD      | input <sup>*2</sup> |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | Notes: 1. TIOC           | B2 input v                       | when MD3                                   | to MD0 = I | 3'0000 or l         | B'01xx, and             | I IOB3 = |  |  |

|                                                                                                                                                                                                                                                                                       | to TF<br>TCLI<br>mode    | PSC0 = B'<br>KD input w          | /hen the se<br>111.<br>/hen chann          | •          |                     |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | TPU Channel<br>2 Setting | (2)                              | (1)                                        | (2)        | (2)                 | (1)                     | (2)      |  |  |

|                                                                                                                                                                                                                                                                                       | MD3 to MD0               | B'0000                           | , B'01xx                                   | B'0010     | B'0011              |                         |          |  |  |

|                                                                                                                                                                                                                                                                                       | IOB3 to IOB0             | B'0000<br>B'0100<br>B'1xxx       | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 |            | B'xx00              | Other tha               | n B'xx00 |  |  |

|                                                                                                                                                                                                                                                                                       | CCLR1,<br>CCLR0          | —                                | _                                          | _          |                     | Other<br>than B'10      | B'10     |  |  |

|                                                                                                                                                                                                                                                                                       | Output<br>function       | —                                | Output<br>compare<br>output                |            |                     | PWM<br>mode 2<br>output | _        |  |  |

| x: Don't care                                                                                                                                                                                                                                                                         |                          |                                  |                                            |            |                     |                         |          |  |  |

# Port C Data Register (PCDR)

| Bit :      |        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|            |        | PC7DR | PC6DR | PC5DR | PC4DR | PC3DR | PC2DR | PC1DR | PC0DR |

| Initial va | alue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W        | :      | R/W   |

PCDR is an 8-bit readable/writable register that stores output data for the port C pins (PC7 to PC0).

PCDR is initialized to H'00 by a power-on reset, and in hardware standby mode. It retains its prior state by a manual reset or in software standby mode.

## Port C Register (PORTC)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            | Ī     | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

| Initial va | lue : | *   | *   | *   | *   | *   | *   | *   | *   |

| R/W        | :     | R   | R   | R   | R   | R   | R   | R   | R   |

Note: \* Determined by state of pins PC7 to PC0.

PORTC is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port C pins (PC7 to PC0) must always be performed on PCDR.

If a PORTC read is performed while PCDDR bits are set to 1, the PCDR values are read. If a PORTC read is performed while PCDDR bits are cleared to 0, the pin states are read.

After a power-on reset and in hardware standby mode, PORTC contents are determined by the pin states, as PCDDR and PCDR are initialized. PORTC retains its prior state by a manual reset or in software standby mode.

# 13.4 Interrupts

# 13.4.1 Interrupt Sources and DTC Activation

(The H8S/2695 does not have a DTC function or an 8-bit timer)

There are three 8-bit timer interrupt sources: CMIA, CMIB, and OVI. Their relative priorities are shown in table 13.3. Each interrupt source is set as enabled or disabled by the corresponding interrupt enable bit in TCR, and independent interrupt requests are sent for each to the interrupt controller. It is also possible to activate the DTC by means of CMIA and CMIB interrupts.

| Channel | nel Interrupt Source Description |                   | <b>DTC Activation</b> | Priority |

|---------|----------------------------------|-------------------|-----------------------|----------|

| 0       | CMIA0                            | Interrupt by CMFA | Possible              | High     |

|         | CMIB0                            | Interrupt by CMFB | Possible              | <b>†</b> |

|         | OVI0                             | Interrupt by OVF  | Not possible          |          |

| 1       | CMIA1                            | Interrupt by CMFA | Possible              |          |

|         | CMIB1                            | Interrupt by CMFB | Possible              |          |

|         | OVI1                             | Interrupt by OVF  | Not possible          |          |

| 2       | CMIA2                            | Interrupt by CMFA | Possible              |          |

|         | CMIB2                            | Interrupt by CMFB | Possible              |          |

|         | OVI2                             | Interrupt by OVF  | Not possible          |          |

| 3       | CMIA3                            | Interrupt by CMFA | Possible              |          |

|         | CMIB3                            | Interrupt by CMFB | Possible              |          |

|         | OVI3                             | Interrupt by OVF  | Not possible          | Low      |

Table 13.3

8-Bit Timer Interrupt Sources

Note: This table shows the initial state immediately after a reset. The relative channel priorities can be changed by the interrupt controller.

# 13.4.2 A/D Converter Activation

The A/D converter can be activated only by channel 0 compare match A.

If the ADTE bit in TCSR0 is set to 1 when the CMFA flag is set to 1 by the occurrence of channel 0 compare match A, a request to start A/D conversion is sent to the A/D converter. If the 8-bit timer conversion start trigger has been selected on the A/D converter side at this time, A/D conversion is started.

The FSX bit also specifies whether or not SARX slave address recognition is performed in slave mode. For details, see the description of the FS bit in SAR.

| Bit :           |   | 7    | 6    | _  | 5  |    | 4   |    | 3   |   | 2  | 1   | 0   |  |

|-----------------|---|------|------|----|----|----|-----|----|-----|---|----|-----|-----|--|

|                 | N | /ILS | WAIT | Cł | S2 | Cł | KS1 | C۲ | (SO | В | C2 | BC1 | BC0 |  |

| Initial value : |   | 0    | 0    |    | 0  |    | 0   |    | 0   |   | 0  | 0   | 0   |  |

| R/W :           | F | R/W  | R/W  | R  | /W | R  | /W  | R  | /W  | F | /W | R/W | R/W |  |

### **18.2.4** I<sup>2</sup>C Bus Mode Register (ICMR)

ICMR is an 8-bit readable/writable register that selects whether the MSB or LSB is transferred first, performs master mode wait control, and selects the master mode transfer clock frequency and the transfer bit count. ICMR is assigned to the same address as SAR. ICMR can be written and read only when the ICE bit is set to 1 in ICCR.

ICMR is initialized to H'00 by a reset and in hardware standby mode.

**Bit 7—MSB-First/LSB-First Select (MLS):** Selects whether data is transferred MSB-first or LSB-first.

If the number of bits in a frame, excluding the acknowledge bit, is less than 8, transmit data and receive data are stored differently. Transmit data should be written justified toward the MSB side when MLS = 0, and toward the LSB side when MLS = 1. Receive data bits read from the LSB side should be treated as valid when MLS = 0, and bits read from the MSB side when MLS = 1.

Do not set this bit to 1 when the  $I^2C$  bus format is used.

| MLS | Description |                 |

|-----|-------------|-----------------|

| 0   | MSB-first   | (Initial value) |

| 1   | LSB-first   |                 |

**Bit 6—Wait Insertion Bit (WAIT):** Selects whether to insert a wait between the transfer of data and the acknowledge bit, in master mode with the I<sup>2</sup>C bus format. When WAIT is set to 1, after the fall of the clock for the final data bit, the IRIC flag is set to 1 in ICCR, and a wait state begins (with SCL at the low level). When the IRIC flag is cleared to 0 in ICCR, the wait ends and the acknowledge bit is transferred. If WAIT is cleared to 0, data and acknowledge bits are transferred consecutively with no wait inserted.

Bit 7

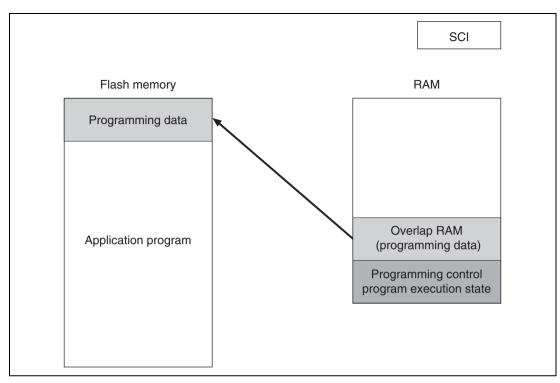

Figure 22.5 Writing Overlap RAM Data in User Program Mode

### 22.4.6 Differences between Boot Mode and User Program Mode

| <b>Table 22.4</b> | Differences between | <b>Boot Mode and</b> | User Program Mode |

|-------------------|---------------------|----------------------|-------------------|

|-------------------|---------------------|----------------------|-------------------|

|                              | Boot Mode              | User Program Mode      |

|------------------------------|------------------------|------------------------|

| Total erase                  | Yes                    | Yes                    |

| Block erase                  | No                     | Yes                    |

| Programming control program* | Program/program-verify | Erase/erase-verify     |

|                              |                        | Program/program-verify |

|                              |                        | Emulation              |

Note: \* To be provided by the user, in accordance with the recommended algorithm.

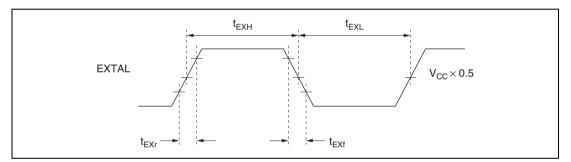

External Clock: Table 23A.4 and figure 23A.7 show the input conditions for the external clock.

## Table 23A.4 External Clock Input Conditions

|                                          |                  | $V_{cc} = 3.0 V$<br>to 3.6 V,<br>$PV_{cc} = 3.0 V$<br>to 5.5 V |     | $V_{cc} = 3.0 V$<br>to 3.6 V,<br>$PV_{cc} = 5.0 V$<br>±10% |     |      |                 |

|------------------------------------------|------------------|----------------------------------------------------------------|-----|------------------------------------------------------------|-----|------|-----------------|

| Item                                     | Symbol           | Min                                                            | Max | Min                                                        | Max | Unit | Test Conditions |

| External clock input low<br>pulse width  | $t_{\text{EXL}}$ | 20                                                             | _   | 15                                                         | _   | ns   | Figure 23A.7    |

| External clock input<br>high pulse width | t <sub>exh</sub> | 20                                                             | —   | 15                                                         | —   | ns   | _               |

| External clock rise time                 | t <sub>EXr</sub> | _                                                              | 10  | _                                                          | 5   | ns   | _               |

| External clock fall time                 | t <sub>EXf</sub> | _                                                              | 10  | _                                                          | 5   | ns   | _               |

Figure 23A.7 External Clock Input Timing

# 23B.2 Register Descriptions

### 23B.2.1 System Clock Control Register (SCKCR)

| Bit       | :     | 7     | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|-----------|-------|-------|---|---|---|------|------|------|------|

|           |       | PSTOP | — | — | — | STCS | SCK2 | SCK1 | SCK0 |

| Initial v | alue: | 0     | 0 | 0 | 0 | 0    | 0    | 0    | 0    |

| R/W       | :     | R/W   | _ | _ | _ | R/W  | R/W  | R/W  | R/W  |

SCKCR is an 8-bit readable/writable register that performs  $\phi$  clock output control, selection of operation when the PLL circuit frequency multiplication factor is changed, and medium-speed mode control.

SCKCR is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

#### Bit 7— Clock Output Disable (PSTOP): Controls $\phi$ output.

|       | Description                          |                             |                                                              |                          |  |  |  |  |  |  |

|-------|--------------------------------------|-----------------------------|--------------------------------------------------------------|--------------------------|--|--|--|--|--|--|

| Bit 7 | High-Speed Mode,                     | Sleen Mede                  | Software<br>Standby Mode,                                    | Hardware<br>Standby Mode |  |  |  |  |  |  |

| PSTOP | Medium-Speed Mode,<br>Subactive Mode | Sleep Mode<br>Subsleep Mode | Watch Mode <sup>*</sup> ,<br>Direct Transitions <sup>*</sup> |                          |  |  |  |  |  |  |

| 0     | $\phi$ output (initial value)        | φ output                    | Fixed high                                                   | High impedance           |  |  |  |  |  |  |

| 1     | Fixed high                           | Fixed high                  | Fixed high                                                   | High impedance           |  |  |  |  |  |  |

Note: \* This function is not available in the H8S/2695.

Bits 6 to 4—Reserved: These bits are always read as 0 and cannot be modified.

**Bit 3—Frequency Multiplication Factor Switching Mode Select (STCS):** Selects the operation when the PLL circuit frequency multiplication factor is changed.

#### Bit 3

| STCS | Description                                                                                                                           |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0    | Specified multiplication factor is valid after transition to software standby mode,<br>watch mode, and subactive mode (Initial value) |  |  |  |  |  |  |

| 1    | Specified multiplication factor is valid immediately after STC bits are rewritten                                                     |  |  |  |  |  |  |

# 24.11 Direct Transitions (This function is not available in the H8S/2695)

# 24.11.1 Overview of Direct Transitions

There are three modes, high-speed, medium-speed, and subactive, in which the CPU executes programs. When a direct transition is made, there is no interruption of program execution when shifting between high-speed and subactive modes. Direct transitions are enabled by setting the LPWRCR DTON bit to 1, then executing the SLEEP instruction. After a transition, direct transition interrupt exception processing starts.

## (1) Direct Transitions from High-Speed Mode to Subactive Mode

Execute the SLEEP instruction in high-speed mode when the SBYCR SSBY bit = 1, LPWRCR LSON bit = 1, and DTON bit = 1, and TSCR (WDT1) PSS bit = 1 to make a transition to subactive mode.

### (2) Direct Transitions from Subactive Mode to High-Speed Mode

Execute the SLEEP instruction in subactive mode when the SBYCR SSBY bit = 1, LPWRCR LSON bit = 0, and DTON bit = 1, and TSCR (WDT1) PSS bit = 1 to make a direct transition to high-speed mode after the time set in SBYCR STS2 to STS0 has elapsed.

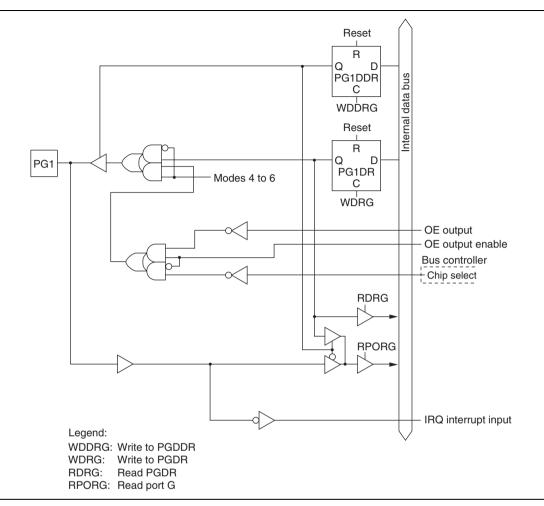

Figure C.12 (b) Port G Block Diagram (Pin PG1)

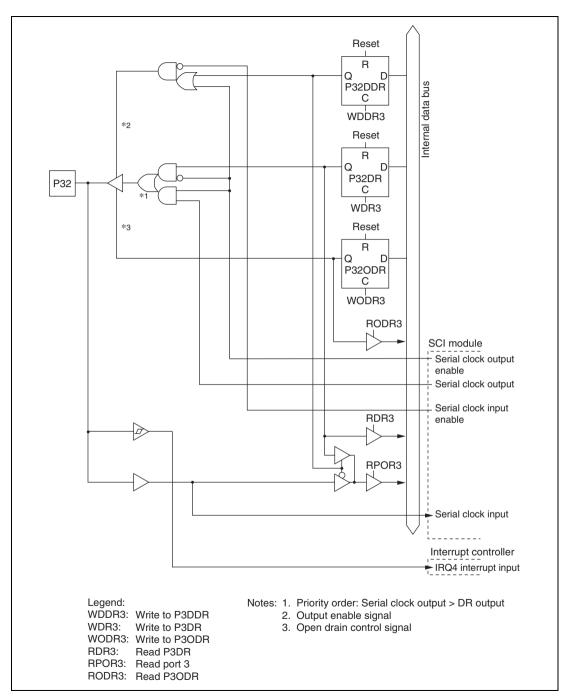

#### Figure C.14 (c) Port 3 Block Diagram (Pin P32)

# RENESAS

| Port Name<br>Pin Name | MCU<br>Operating<br>Mode | Power-<br>On<br>Reset | Manual<br>Reset | Hardware<br>Standby<br>Mode | Software<br>Standby<br>Mode                                                           | Bus<br>Release<br>State | Program<br>Execution<br>State<br>Sleep Mode                                                         |

|-----------------------|--------------------------|-----------------------|-----------------|-----------------------------|---------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|

| PG3/CS1<br>PG2/CS2    | 4 to 6                   | Т                     | kept            | Т                           | [DDR = 1,<br>OPE = 0]<br>T<br>[DDR = 1,<br>OPE = 1]<br>H<br>[DDR = 0]<br>T            | Τ                       | $[DDR = 0]$ Input port $[DDR = 1]$ $\overline{CS2} \text{ to } \overline{CS1}$                      |

|                       | 7                        | Т                     | kept            | Т                           | kept                                                                                  | kept                    | I/O port                                                                                            |

| PG1/CS3/<br>OE/IRQ7   | 4 to 6                   | Т                     | kept            | Т                           | [DDR = 1,<br>OPE = 0]<br>T<br>[DDR = 1,<br>OPE = 1]<br>H<br>[DDR = 0]<br>T            | Т                       | $[DDR = 0]$ Input port $[OE = 0,$ $DDR = 1]$ $\overline{CS3}$ $[OE = 1,$ $DDR = 1]$ $\overline{OE}$ |

|                       | 7                        | Т                     | kept            | Т                           | kept                                                                                  | kept                    | I/O port                                                                                            |

| PG0/CAS/<br>IRQ6      | 4 to 6                   | Т                     | kept            | Т                           | [DRAME = 0]<br>kept<br>[DRAME = 1,<br>OPE = 1]<br>CAS<br>[DRAME = 1,<br>OPE = 1]<br>T | Т                       | [DRAME = 0]<br>I/O port<br>[DRAME = 1]<br>CAS                                                       |

| Logond:               | 7                        | Т                     | kept            | Т                           | kept                                                                                  | kept                    | I/O port                                                                                            |

Legend:

H: High level

L: Low level

T: High impedance

kept: Input port becomes high-impedance, output port retains state

DDR: Data direction register

OPE: Output port enable

WAITE: Wait input enable

BRLE: Bus release enable

BREQOE: BREQO pin enable

DRAME: DRAM space setting

LCASE: DRAM space setting, CW2 = LCASS = 0

Note: \* Indicates the state after completion of the executing bus cycle.