Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 28MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 73                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | •                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b; D/A 4x8b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 120-TQFP                                                                      |

| Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2633rte28v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.6.3 Table of Instructions Classified by Function

Table 2.3 summarizes the instructions in each functional category. The notation used in table 2.3 is defined below.

#### **Operation Notation**

| General register (destination)*                |

|------------------------------------------------|

| General register (source)*                     |

| General register*                              |

| General register (32-bit register)             |

| Multiply-accumulate register (32-bit register) |

| Destination operand                            |

| Source operand                                 |

| Extended control register                      |

| Condition-code register                        |

| N (negative) flag in CCR                       |

| Z (zero) flag in CCR                           |

| V (overflow) flag in CCR                       |

| C (carry) flag in CCR                          |

| Program counter                                |

| Stack pointer                                  |

| Immediate data                                 |

| Displacement                                   |

| Addition                                       |

| Subtraction                                    |

| Multiplication                                 |

| Division                                       |

| Logical AND                                    |

| Logical OR                                     |

| Logical exclusive OR                           |

| Move                                           |

| NOT (logical complement)                       |

| 8-, 16-, 24-, or 32-bit length                 |

|                                                |

Note: \* General registers include 8-bit registers (R0H to R7H, R0L to R7L), 16-bit registers (R0 to R7, E0 to E7), and 32-bit registers (ER0 to ER7).

# 4.5 Trap Instruction

Trap instruction exception handling starts when a TRAPA instruction is executed. Trap instruction exception handling can be executed at all times in the program execution state.

The TRAPA instruction fetches a start address from a vector table entry corresponding to a vector number from 0 to 3, as specified in the instruction code.

Table 4.5 shows the status of CCR and EXR after execution of trap instruction exception handling.

| Table 4.5 | Status of CCR and EXR after | Trap Instruction | <b>Exception Handling</b> |

|-----------|-----------------------------|------------------|---------------------------|

|           |                             |                  |                           |

|                        | CCR |    | EXR      |   |  |

|------------------------|-----|----|----------|---|--|

| Interrupt Control Mode | I   | UI | l2 to l0 | т |  |

| 0                      | 1   | —  | —        |   |  |

| 2                      | 1   | —  | —        | 0 |  |

Legend:

1: Set to 1

0: Cleared to 0

-: Retains value prior to execution

## 5.4.3 Interrupt Control Mode 2

Eight-level masking is implemented for IRQ interrupts and on-chip supporting module interrupts by comparing the interrupt mask level set by bits I2 to I0 of EXR in the CPU with IPR.

Figure 5.6 shows a flowchart of the interrupt acceptance operation in this case.

- [1] If an interrupt source occurs when the corresponding interrupt enable bit is set to 1, an interrupt request is sent to the interrupt controller.

- [2] When interrupt requests are sent to the interrupt controller, the interrupt with the highest priority according to the interrupt priority levels set in IPR is selected, and lower-priority interrupt requests are held pending. If a number of interrupt requests with the same priority are generated at the same time, the interrupt request with the highest priority according to the priority system shown in table 5.4 is selected.

- [3] Next, the priority of the selected interrupt request is compared with the interrupt mask level set in EXR. An interrupt request with a priority no higher than the mask level set at that time is held pending, and only an interrupt request with a priority higher than the interrupt mask level is accepted.

- [4] When an interrupt request is accepted, interrupt exception handling starts after execution of the current instruction has been completed.

- [5] The PC, CCR, and EXR are saved to the stack area by interrupt exception handling. The PC saved on the stack shows the address of the first instruction to be executed after returning from the interrupt handling routine.

- [6] The T bit in EXR is cleared to 0. The interrupt mask level is rewritten with the priority level of the accepted interrupt.If the accepted interrupt is NMI, the interrupt mask level is set to H'7.

[7] A vector address is generated for the accepted interrupt, and execution of the interrupt handling routine starts at the address indicated by the contents of that vector address.

| Bit 5  | Bit 4  | Bit 3  |                                                                                |

|--------|--------|--------|--------------------------------------------------------------------------------|

| BAMRA2 | BAMRA1 | BAMRA0 | _<br>Description                                                               |

| 0      | 0      | 0      | All BARA bits are unmasked and included in break conditions (Initial value)    |

|        |        | 1      | BAA0 (lowest bit) is masked, and not included in break conditions              |

|        | 1      | 0      | BAA1 to BAA0 (lower 2 bits) are masked, and not included in break conditions   |

|        |        | 1      | BAA2 to BAA0 (lower 3 bits) are masked, and not included in break conditions   |

| 1      | 0      | 0      | BAA3 to BAA0 (lower 4 bits) are masked, and not included in break conditions   |

|        |        | 1      | BAA7 to BAA0 (lower 8 bits) are masked, and not included in break conditions   |

|        | 1      | 0      | BAA11 to BAA0 (lower 12 bits) are masked, and not included in break conditions |

|        |        | 1      | BAA15 to BAA0 (lower 16 bits) are masked, and not included in break conditions |

#### Bits 2 and 1-Break Condition Select A (CSELA1, CSELA0): These bits selection an

instruction fetch, data read, data write, or data read/write cycle as the channel A break condition.

| Bit 2  | Bit 1  |                                                  |                 |

|--------|--------|--------------------------------------------------|-----------------|

| CSELA1 | CSELA0 | Description                                      |                 |

| 0      | 0      | Instruction fetch is used as break condition     | (Initial value) |

|        | 1      | Data read cycle is used as break condition       |                 |

| 1      | 0      | Data write cycle is used as break condition      |                 |

|        | 1      | Data read/write cycle is used as break condition |                 |

Bit 0-Break Interrupt Enable A (BIEA): Enables or disables channel A PC break interrupts.

Bit 0

Description

0

PC break interrupts are disabled (Initial value)

1

PC break interrupts are enabled

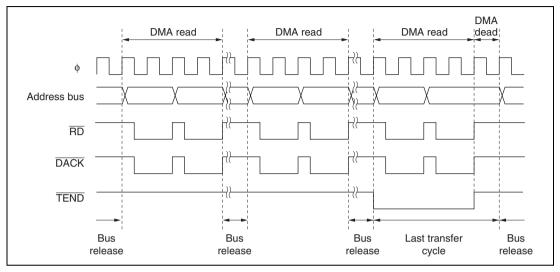

Figure 8.28 shows a transfer example in which  $\overline{\text{TEND}}$  output is enabled and word-size single address mode transfer (read) is performed from external 8-bit, 2-state access space to an external device.

Figure 8.28 Example of Single Address Mode (Word Read) Transfer

A one-byte or one-word transfer is performed for one transfer request, and after the transfer the bus is released. While the bus is released, one or more bus cycles are inserted by the CPU or DTC.

In the transfer end cycle (the cycle in which the transfer counter reaches 0), a one-state DMA dead cycle is inserted after the DMA write cycle.

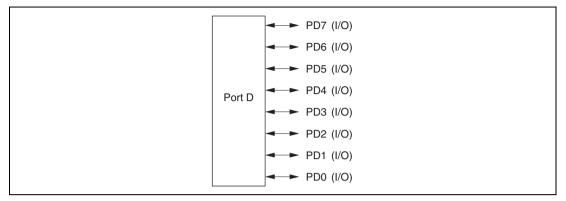

Port D pin functions in mode 7 are shown in figure 10A.14.

### Figure 10A.14 Port D Pin Functions (Mode 7)

### **10A.10.4 MOS Input Pull-Up Function**

Port D has a built-in MOS input pull-up function that can be controlled by software. This MOS input pull-up function can be used in mode 7, and can be specified as on or off on an individual bit basis.

When a PDDDR bit is cleared to 0 in mode 7, setting the corresponding PDPCR bit to 1 turns on the MOS input pull-up for that pin.

The MOS input pull-up function is in the off state after a power-on reset, and in hardware standby mode. The prior state is retained by a manual reset or in software standby mode.

Table 10A.19 summarizes the MOS input pull-up states.

## Table 10A.19 MOS Input Pull-Up States (Port D)

| Modes  | Power-On<br>Reset | Hardware<br>Standby Mode | Manual<br>Reset | Software<br>Standby Mode | In Other<br>Operations |

|--------|-------------------|--------------------------|-----------------|--------------------------|------------------------|

| 4 to 6 | OFF               | OFF                      | OFF             | OFF                      | OFF                    |

| 7      |                   |                          | ON/OFF          | ON/OFF                   | ON/OFF                 |

Legend:

OFF: MOS input pull-up is always off.

ON/OFF: On when PDDDR = 0 and PDPCR = 1; otherwise off.

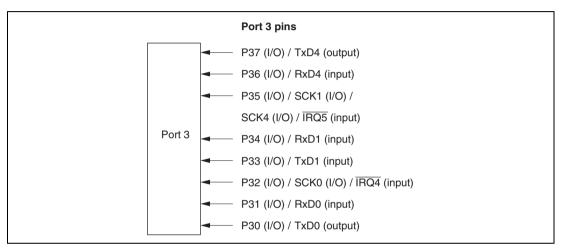

# 10B.3 Port 3

# 10B.3.1 Overview

Port 3 is an 8-bit I/O port. Port 3 is a multi-purpose port for SCI I/O pins (TxD0, RxD0, SCK0, TxD1, RxD1, SCK1, TxD4, RxD4, and SCK4) and external interrupt input pins ( $\overline{IRQ4}$  and  $\overline{IRQ5}$ ). All of the port 3 pin functions have the same operating mode. The configuration for each of the port 3 pins is shown in figure 10B.2.

Figure 10B.2 Port 3 Pin Functions

# 10B.3.2 Register Configuration

Table 10B.4 shows the configuration of port 3 registers.

# Table 10B.4 Port 3 Register Configuration

| Name                               | Abbreviation | R/W | Initial Value | Address* |

|------------------------------------|--------------|-----|---------------|----------|

| Port 3 data direction register     | P3DDR        | W   | H'00          | H'FE32   |

| Port 3 data register               | P3DR         | R/W | H'00          | H'FF02   |

| Port 3 register                    | PORT3        | R   | Undefined     | H'FFB2   |

| Port 3 open drain control register | P3ODR        | R/W | H'00          | H'FE46   |

|                                    |              |     |               |          |

Note: \* Lower 16 bits of the address.

## Address H'FE2D

| Bit :           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------|------|------|------|------|------|------|------|------|

|                 | NDR7 | NDR6 | NDR5 | NDR4 | NDR3 | NDR2 | NDR1 | NDR0 |

| Initial value : | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W :           | R/W  |

|                 |      |      |      |      |      |      |      |      |

| Address H'FE    | 2F   |      |      |      |      |      |      |      |

| Bit :           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|                 | —    | _    |      | —    | _    | _    | _    | —    |

| Initial value : | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| R/W :           | _    | _    | _    | _    | _    | _    | _    | _    |

**Different Triggers for Pulse Output Groups:** If pulse output groups 2 and 3 are triggered by different compare match events, the address of the upper 4 bits in NDRH (group 3) is H'FE2C and the address of the lower 4 bits (group 2) is H'FE2E. Bits 3 to 0 of address H'FE2C and bits 7 to 4 of address H'FE2E are reserved bits that cannot be modified and are always read as 1.

#### Address H'FE2C

| Bit :           | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|-----------------|-------|-------|-------|-------|-------|-------|------|------|

|                 | NDR15 | NDR14 | NDR13 | NDR12 | —     | —     | _    | —    |

| Initial value : | 0     | 0     | 0     | 0     | 1     | 1     | 1    | 1    |

| R/W :           | R/W   | R/W   | R/W   | R/W   | —     | —     | —    |      |

|                 |       |       |       |       |       |       |      |      |

| Address H'FE    | 2E    |       |       |       |       |       |      |      |

| Bit :           | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|                 | —     | —     | —     | —     | NDR11 | NDR10 | NDR9 | NDR8 |

| Initial value : | 1     | 1     | 1     | 1     | 0     | 0     | 0    | 0    |

| R/W :           | —     | —     | —     | —     | R/W   | R/W   | R/W  | R/W  |

If pulse output groups 0 and 1 are triggered by different compare match event, the address of the upper 4 bits in NDRL (group 1) is H'FE2D and the address of the lower 4 bits (group 0) is H'FE2F. Bits 3 to 0 of address H'FE2D and bits 7 to 4 of address H'FE2F are reserved bits that cannot be modified and are always read as 1. However, the H8S/2633 Group has no output pins corresponding to pulse output groups 0 and 1.

## 15.5.6 OVF Flag Clearing in Interval Timer Mode

When the OVF Flag setting conflicts with the OVF flag reading in interval timer mode, writing 0 to the OVF bit may not clear the flag even though the OVF bit has been read while it is 1. If there is a possibility that the OVF flag setting and reading will conflict, such as when the OVF flag is polled with the interval timer interrupt disabled, read the OVF bit while it is 1 at least twice before writing 0 to the OVF bit to clear the flag.

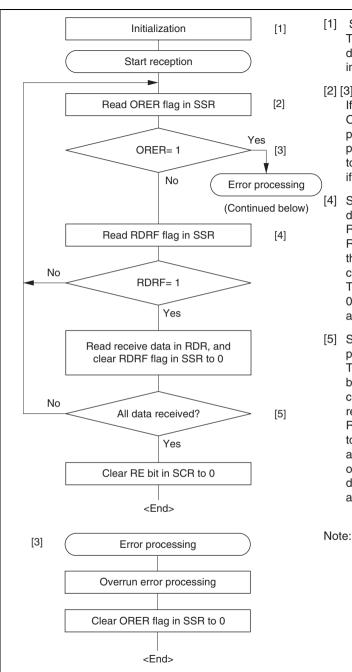

- [1] SCI initialization: The RxD pin is automatically designated as the receive data input pin.

- [2] [3] Receive error processing: If a receive error occurs, read the ORER flag in SSR, and after performing the appropriate error processing, clear the ORER flag to 0. Transfer cannot be resumed if the ORER flag is set to 1.

- SCI status check and receive data read: Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR and clear the RDRF flag to 0. Transition of the RDRF flag from 0 to 1 can also be identified by an RXI interrupt.

- [5] Serial reception continuation procedure:

To continue serial reception, before the MSB (bit 7) of the current frame is received, finish reading the RDRF flag, reading RDR, and clearing the RDRF flag to 0. The RDRF flag is cleared automatically when the DMAC\* or DTC\* is activated by a receive data full interrupt (RXI) request and the RDR value is read.

Note: \* DMAC and DTC functions are not available in the H8S/2695.

## Figure 16.18 Sample Serial Reception Flowchart

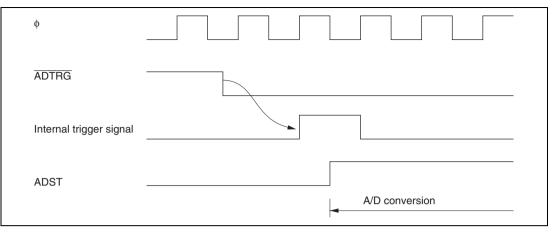

Figure 19.6 External Trigger Input Timing

# **19.5** Interrupts

The A/D converter generates an A/D conversion end interrupt (ADI) at the end of A/D conversion. ADI interrupt requests can be enabled or disabled by means of the ADIE bit in ADCSR.

The DTC<sup>\*</sup> and DMAC<sup>\*</sup> can be activated by an ADI interrupt. Having the converted data read by the DTC<sup>\*</sup> or DMAC<sup>\*</sup> in response to an ADI interrupt enables continuous conversion to be achieved without imposing a load on software.

The A/D converter interrupt source is shown in table 19.6.

Note: \* This function is not available in the H8S/2695.

#### Table 19.6 A/D Converter Interrupt Source

| Interrupt Source                                       | Description                        | DTC*, DMAC* Activation |  |  |  |  |

|--------------------------------------------------------|------------------------------------|------------------------|--|--|--|--|

| ADI                                                    | Interrupt due to end of conversion | Possible               |  |  |  |  |

| Note: * This function is not available in the USC/2005 |                                    |                        |  |  |  |  |

Note: \* This function is not available in the H8S/2695.

# Section 23A Clock Pulse Generator (H8S/2633, H8S/2632, H8S/2631, H8S/2633F)

# 23A.1 Overview

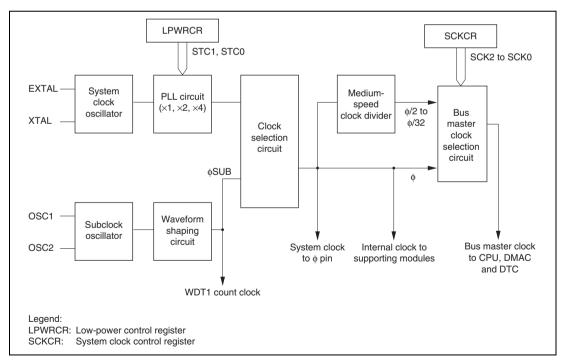

The H8S/2633 Group has a built-in clock pulse generator (CPG) that generates the system clock  $(\phi)$ , the bus master clock, and internal clocks.

The clock pulse generator consists of an oscillator, PLL (phase-locked loop) circuit, clock selection circuit, medium-speed clock divider, bus master clock selection circuit, subclock oscillator, and waveform shaping circuit. The frequency can be changed by means of the PLL circuit in the CPG. Frequency changes are performed by software by means of settings in the system clock control register (SCKCR) and low-power control register (LPWRCR).

## 23A.1.1 Block Diagram

Figure 23A.1 shows a block diagram of the clock pulse generator.

Figure 23A.1 Block Diagram of Clock Pulse Generator

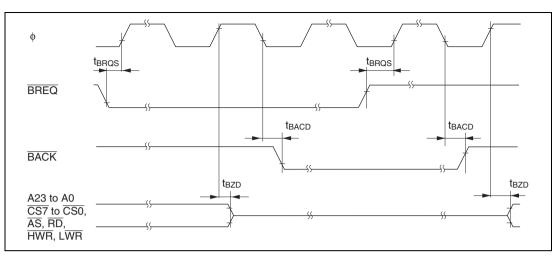

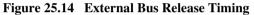

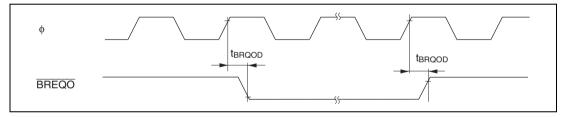

Figure 25.15 External Bus Request Output Timing

## 26.3.2 Control Signal Timing

Table 26.6 lists the control signal timing.

### Table 26.6 Control Signal Timing

Conditions:  $PV_{cc} = 4.5 \text{ V}$  to 5.5 V,  $AV_{cc} = 4.5 \text{ V}$  to 5.5 V,  $V_{ref} = 4.5 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = PLLV_{ss} = 0 \text{ V}$ , 2 to 28 MHz,  $T_a = -20^{\circ}\text{C}$  to +75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to +85°C (wide-range specifications)

| Item                                               | Symbol             | Min | Max | Unit             | Test Conditions |

|----------------------------------------------------|--------------------|-----|-----|------------------|-----------------|

| RES setup time                                     | t <sub>ress</sub>  | 200 | _   | ns               | Figure 26.4     |

| RES pulse width                                    | t <sub>resw</sub>  | 20  | _   | t <sub>cyc</sub> |                 |

| MRES setup time                                    | t <sub>mress</sub> | 250 | _   | ns               |                 |

| MRES pulse width                                   | t <sub>mresw</sub> | 20  | _   | t <sub>cyc</sub> |                 |

| NMI setup time                                     | t <sub>nmis</sub>  | 150 | _   | ns               | Figure 26.5     |

| NMI hold time                                      | t <sub>nmin</sub>  | 10  | _   |                  |                 |

| NMI pulse width<br>(exiting software standby mode) | t <sub>nmiw</sub>  | 200 | _   | ns               |                 |

| IRQ setup time                                     | t <sub>irqs</sub>  | 150 | _   | ns               |                 |

| IRQ hold time                                      | t <sub>irqh</sub>  | 10  | _   | ns               |                 |

| IRQ pulse width<br>(exiting software standby mode) | t <sub>irqw</sub>  | 200 | —   | ns               |                 |

|             |                  |                  |                                                                                                         | _       |                                                       | _       | _                                                     | _       | _               | _               |              | _               | _           |                  |                |                 | _             |            |            |                                     |         | _             | _            |                 | _           |                  |                | _              |                |

|-------------|------------------|------------------|---------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------|---------|-------------------------------------------------------|---------|-----------------|-----------------|--------------|-----------------|-------------|------------------|----------------|-----------------|---------------|------------|------------|-------------------------------------|---------|---------------|--------------|-----------------|-------------|------------------|----------------|----------------|----------------|

| 6           |                  |                  |                                                                                                         |         |                                                       |         |                                                       |         |                 |                 |              |                 |             |                  |                |                 |               |            |            | R:W*7                               |         |               |              |                 |             |                  |                |                |                |

| 8           |                  |                  |                                                                                                         |         |                                                       |         |                                                       |         |                 |                 |              |                 |             |                  |                |                 |               |            |            | Internal operation, R:W*7           | 1 state |               |              |                 |             |                  |                |                |                |

| 7           |                  |                  |                                                                                                         |         |                                                       |         |                                                       |         |                 |                 |              |                 |             |                  |                |                 |               |            |            | R:W VEC+2                           |         |               |              |                 |             |                  |                |                |                |

| 9           |                  |                  |                                                                                                         |         |                                                       |         |                                                       |         |                 |                 |              |                 |             |                  |                |                 |               |            |            | R:W:M VEC                           |         |               |              |                 |             |                  |                |                |                |

| 5           | W:W EA           | W:W EA           | W:W stack (L)*3                                                                                         |         | W:W stack (L)*3                                       |         | W:W stack (L)*3                                       |         |                 |                 |              |                 |             |                  |                |                 |               |            |            | W:W stack (EXR) R:W:M VEC R:W VEC+2 |         |               |              |                 |             |                  |                |                |                |

| 4           | R:W NEXT         | R:W NEXT         | Internal operation, W:W:M stack (H) <sup><math>*3</math></sup> W:W stack (L) <sup><math>*3</math></sup> |         | Internal operation, W:W:M stack (H)*3 W:W stack (L)*3 |         | Internal operation, W:W:M stack (H)*3 W:W stack (L)*3 |         |                 |                 |              |                 |             |                  |                |                 |               |            | W:B EA     | W:W stack (H)                       |         |               |              |                 |             |                  |                |                |                |

| e           | R:W 4th          | R:W 4th          | Internal operation,                                                                                     | 1 state | Internal operation,                                   | 1 state | Internal operation,                                   | 1 state |                 |                 |              |                 |             | R:W NEXT         |                |                 |               |            | R:B:M EA   |                                     |         |               |              |                 |             | R:W NEXT         |                |                |                |

| 2           | R:W 3rd          | R:W 3rd          | R:W:M NEXT                                                                                              |         | R:W:M NEXT                                            |         | R:W:M NEXT                                            |         |                 |                 |              | R:W NEXT        |             | R:W 3rd          |                |                 |               |            | R:W NEXT   | Internal operation, W:W stack (L)   | 1 state |               |              | R:W NEXT        |             | R:W 3rd          | R:W NEXT       |                | R:W NEXT       |

| 1           | R:W 2nd          | R:W 2nd          | R:W 2nd                                                                                                 |         | R:W 2nd                                               |         | R:W 2nd                                               |         | R:W NEXT        | R:W NEXT        | R:W NEXT     | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W NEXT       | R:W NEXT        | R:W NEXT      | R:W NEXT   | R:W 2nd    | R:W NEXT                            |         | R:W NEXT      | R:W NEXT     | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W 2nd        | R:W NEXT       | R:W 2nd        |

| Instruction | STC CCR, @ aa:32 | STC EXR, @ aa:32 | STM.L(ERn-ERn+1), @-SP*9 R:W 2nd                                                                        |         | STM.L(ERn-ERn+2), @-SP*9 R:W 2nd                      |         | STM.L(ERn-ERn+3), @-SP*9                              |         | STMAC MACH, ERd | STMAC MACL, ERd | SUB.B Rs, Rd | SUB.W #xx:16,Rd | SUB.W Rs,Rd | SUB.L #xx:32,ERd | SUB.L ERS, ERd | SUBS #1/2/4,ERd | SUBX #xx:8,Rd | SUBX Rs,Rd | TAS @ERd*8 | TRAPA #x:2                          |         | XOR.B #xx8,Rd | XOR.B Rs, Rd | XOR.W #xx:16,Rd | XOR.W Rs,Rd | XOR.L #xx:32,ERd | XOR.L ERS, ERd | XORC #xx:8,CCR | XORC #xx:8,EXR |

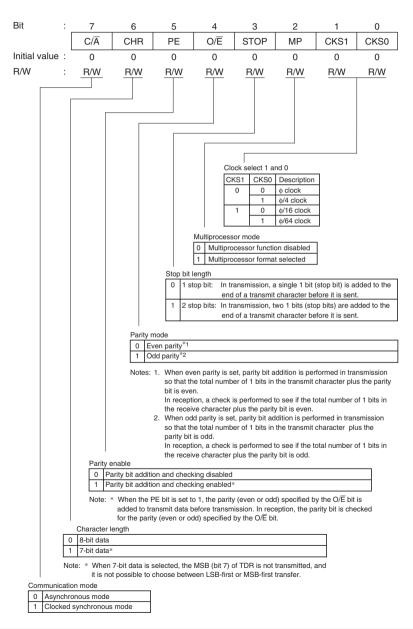

| SMR3—Serial Mode Register 3 | H'FDD0 | SCI3 |

|-----------------------------|--------|------|

| SMR4—Serial Mode Register 4 | H'FDD8 | SCI4 |

| SMR0—Serial Mode Register 0 | H'FF78 | SCI0 |

| SMR1—Serial Mode Register 1 | H'FF80 | SCI1 |

| SMR2—Serial Mode Register 2 | H'FF88 | SCI2 |

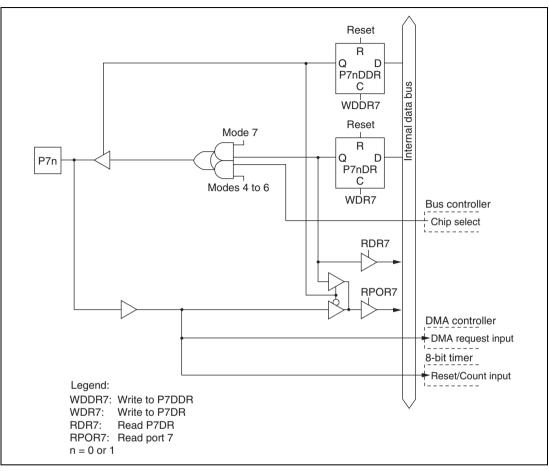

# C.4 Port 7 Block Diagram

Figure C.4 (a) Port 7 Block Diagram (Pins P70 and P71)

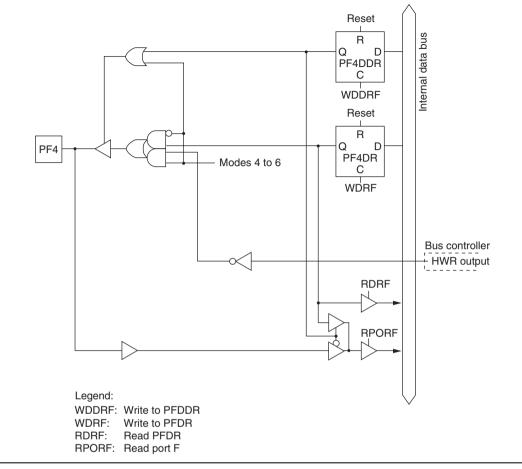

Appendix C I/O Port Block Diagrams

Figure C.23 (e) Port F Block Diagram (Pin PF4)

| Port Name<br>Pin Name                   | MCU<br>Operating<br>Mode | Power-<br>On<br>Reset | Manual<br>Reset | Hardware<br>Standby<br>Mode | Software<br>Standby<br>Mode                                                | Bus<br>Release<br>State                   | Program<br>Execution<br>State<br>Sleep Mode     |  |  |

|-----------------------------------------|--------------------------|-----------------------|-----------------|-----------------------------|----------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------|--|--|

| PF5/RD<br>PF4/HWR<br>PF3/LWR/<br>ADTRG/ | 4 to 6                   | Н                     | Н               | Т                           | [OPE = 0]<br>T<br>[OPE = 1]<br>H                                           | Т                                         | rd, hwr,<br>Lwr                                 |  |  |

| IRQ3                                    | 7                        | Т                     | kept            | Т                           | kept                                                                       | kept                                      | I/O port                                        |  |  |

| PF2/WAIT/<br>BREQO                      | 4 to 6                   | Т                     | kept            | Т                           | kept                                                                       | [BREQOE = 1]<br>BREQO<br>[WAITE = 1]<br>T | [BREQOE =<br>1]<br>BREQO<br>[WAITE = 1]<br>WAIT |  |  |

|                                         | 7                        | Т                     | kept            | Т                           | kept                                                                       | kept                                      | I/O port                                        |  |  |

| PF1/BACK                                | 4 to 6                   | Т                     | kept            | Т                           | [BRLE = 0]<br>I/O port<br>[BRLE = 1]<br>H                                  | [BRLE = 0]<br>I/O port<br>[BRLE = 1]<br>L | [BRLE = 0]<br>I/O port<br>[BRLE = 1]<br>BACK    |  |  |

|                                         | 7                        | Т                     | kept            | Т                           | kept                                                                       | kept                                      | I/O port                                        |  |  |

| PF0/BREQ/<br>IRQ2                       | 4 to 6                   | Т                     | kept            | Т                           | [BRLE = 0]<br>kept<br>[BRLE = 1]<br>T                                      | Т                                         | [BRLE = 0]<br>I/O port<br>[BRLE = 1]<br>BREQO   |  |  |

|                                         | 7                        | Т                     | kept            | Т                           | kept                                                                       | kept                                      | I/O port                                        |  |  |

| PG4/CS0                                 | 4, 5<br>6                | H<br>T                | kept            | Т                           | [DDR = 1,<br>OPE = 0]<br>T<br>[DDR = 1,<br>OPE = 1]<br>H<br>[DDR = 0]<br>T | Т                                         | [DDR = 0]<br>Input port<br>[DDR = 1]<br>CS0     |  |  |

|                                         | 7                        | Т                     | kept            | Т                           | kept                                                                       | kept                                      | I/O port                                        |  |  |