Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 16MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 73                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b; D/A 4x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 120-TQFP                                                                     |

| Supplier Device Package    | 120-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2633te16v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                      |                                                                                         | H8S/2633 | Group    | H8S/2633R Group                                                          |                                                                 |                                                                |  |

|--------------------------------------|-----------------------------------------------------------------------------------------|----------|----------|--------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|--|

|                                      | H8S/2633F-ZTAT                                                                          | H8S/2633 | H8S/2632 | H8S/2631                                                                 | H8S/2633RF-ZTAT                                                 | H8S/2695                                                       |  |

| 32 kHz oscillator                    | See section 23A, C<br>H8S/2632, H8S/26                                                  |          | •        | See section 23B,<br>Clock Pulse<br>Generator<br>(H8S/2633R,<br>H8S/2695) | _                                                               |                                                                |  |

| Clock Pulse<br>Generator             | See section 23A, C<br>H8S/2632, H8S/26                                                  |          | · ·      | See section 23B, Clock Pulse Generator<br>(H8S/2633R, H8S/2695)          |                                                                 |                                                                |  |

| EXTAL input level                    | See section 25, Electrical Characteristics (H8S/2633,<br>H8S/2632, H8S/2631, H8S/2633F) |          |          |                                                                          | See section 26,<br>Electrical<br>Characteristics<br>(H8S/2633R) | See section 27,<br>Electrical<br>Characteristics<br>(H8S/2695) |  |

| Recommended<br>external PLL circuit  |                                                                                         |          |          | See section 23B, Clock Pulse Generator<br>(H8S/2633R, H8S/2695)          |                                                                 |                                                                |  |

| Interrupt processing<br>vector table | See section 5, Interrupt Controller<br>See table 5.4 (a)                                |          |          |                                                                          |                                                                 | See section 5,<br>Interrupt Controller<br>See table 5.4 (b)    |  |

| Name                                | Symbol | I/O    | Function                                                                                                         |

|-------------------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------|

| Lower column<br>strobe <sup>*</sup> | LCAS*  | Output | DRAM lower column address strobe signal*                                                                         |

| Wait                                | WAIT   | Input  | Wait request signal when accessing external 3-state access space.                                                |

| Bus request                         | BREQ   | Input  | Request signal that releases bus to external device.                                                             |

| Bus request<br>acknowledge          | BACK   | Output | Acknowledge signal indicating that bus has been released.                                                        |

| Bus request output                  | BREQO  | Output | External bus request signal used when internal bus master accesses external space when external bus is released. |

Note: \* This function is not available in the H8S/2695.

#### 7.1.4 Register Configuration

Table 7.2 summarizes the registers of the bus controller.

#### Table 7.2 Bus Controller Registers

|                                |                     |     | Initial           |                 |                       |

|--------------------------------|---------------------|-----|-------------------|-----------------|-----------------------|

| Name                           | Abbreviation        | R/W | Power-On<br>Reset | Manual<br>Reset | Address <sup>*1</sup> |

| Bus width control register     | ABWCR               | R/W | H'FF/H'00*2       | Retained        | H'FED0                |

| Access state control register  | ASTCR               | R/W | H'FF              | Retained        | H'FED1                |

| Wait control register H        | WCRH                | R/W | H'FF              | Retained        | H'FED2                |

| Wait control register L        | WCRL                | R/W | H'FF              | Retained        | H'FED3                |

| Bus control register H         | BCRH                | R/W | H'D0              | Retained        | H'FED4                |

| Bus control register L         | BCRL                | R/W | H'08              | Retained        | H'FED5                |

| Pin function control register  | PFCR                | R/W | H'0D/H'00         | Retained        | H'FDEB                |

| Memory control register        | MCR <sup>*3</sup>   | R/W | H'00              | Retained        | H'FED6                |

| DRAM control register          | DRAMCR*3            | R/W | H'00              | Retained        | H'FED7                |

| Refresh timer counter          | RTCNT <sup>*3</sup> | R/W | H'00              | Retained        | H'FED8                |

| Refresh time constant register | RTCOR*3             | R/W | H'FF              | Retained        | H'FED9                |

|                                |                     |     |                   |                 |                       |

Notes: 1. Lower 16 bits of the address.

- 2. Determined by the MCU operating mode.

- 3. This function is not available in the H8S/2695.

### 8.5.4 Repeat Mode

Repeat mode can be specified by setting the RPE bit in DMACR to 1, and clearing the DTIE bit to 0. In repeat mode, MAR is updated after each byte or word transfer in response to a single transfer request, and this is executed the number of times specified in ETCR. On completion of the specified number of transfers, MAR and ETCRL are automatically restored to their original settings and operation continues.

One address is specified by MAR, and the other by IOAR. The transfer direction can be specified by the DTDIR bit in DMACR.

Table 8.8 summarizes register functions in repeat mode.

|                      | Fun                                |                                    |                                                                |                                                                                                               |

|----------------------|------------------------------------|------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Register             | DTDIR = 0                          | DTDIR = 1                          | Initial Setting                                                | Operation                                                                                                     |

| 23 0                 | Source<br>address<br>register      | Destination<br>address<br>register | Start address of<br>transfer destination<br>or transfer source | Incremented/<br>decremented every<br>transfer. Initial<br>setting is restored<br>when value reaches<br>H'0000 |

| 23 15 0<br>H'FF IOAR | Destination<br>address<br>register | Source<br>address<br>register      | Start address of<br>transfer source or<br>transfer destination | Fixed                                                                                                         |

| 7 0<br>ETCRH         | Holds numb<br>transfers            | per of                             | Number of transfers                                            | Fixed                                                                                                         |

| 7 ▼ 0<br>ETCRL       | Transfer co                        | unter                              | Number of transfers                                            | Decremented every<br>transfer. Loaded with<br>ETCRH value when<br>count reaches H'00                          |

### Table 8.8 Register Functions in Repeat Mode

Legend:

- MAR: Memory address register

- IOAR: I/O address register

- ETCR: Transfer count register

- DTDIR: Data transfer direction bit

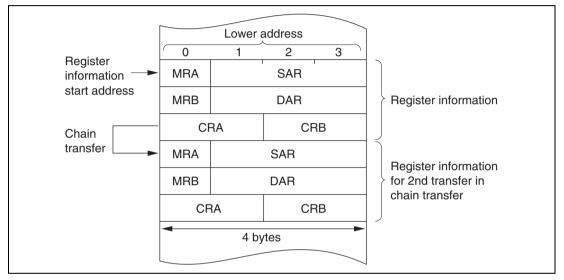

### 9.3.4 Location of Register Information in Address Space

Figure 9.5 shows how the register information should be located in the address space.

Locate the MRA, SAR, MRB, DAR, CRA, and CRB registers, in that order, from the start address of the register information (contents of the vector address). In the case of chain transfer, register information should be located in consecutive areas.

Locate the register information in the on-chip RAM (addresses: H'FFEBC0 to H'FFEFBF).

Figure 9.5 Location of Register Information in Address Space

#### Selection Method and Pin Functions

P16/PO14/ The p TIOCA2/PWM2/ the T IRQ1 in TIO

Pin

The pin function is switched as shown below according to the combination of the TPU channel 2 setting (by bits MD3 to MD0 in TMDR2, bits IOA3 to IOA0 in TIOR2, and bits CCLR1 and CCLR0 in TCR2), OEA bit in DACR3, bit NDER14 in NDERH, and bit P16DDR.

| TPU Channel<br>2 Setting | Table Below (1) | Table Below (2) |               |                |                |  |  |

|--------------------------|-----------------|-----------------|---------------|----------------|----------------|--|--|

| OEA                      | _               | 0               | 0             | 0              | 1              |  |  |

| P16DDR                   | _               | 0               | 1             | 1              | —              |  |  |

| NDER14                   | _               | _               | 0             | 1              | —              |  |  |

| Pin function             | TIOCA2 output   | P16<br>input    | P16<br>output | PO14<br>output | PWM2<br>output |  |  |

|                          |                 | TIOCA2 input*1  |               |                |                |  |  |

| IRQ1 input               |                 |                 |               |                |                |  |  |

| TPU Channel<br>2 Setting | (2)                        | (1)                                        | (2)    | (1)                                   | (1)                     | (2)  |  |

|--------------------------|----------------------------|--------------------------------------------|--------|---------------------------------------|-------------------------|------|--|

| MD3 to MD0               | B'0000,                    | , B'01xx                                   | B'001x | B'0010                                | B'0011                  |      |  |

| IOA3 to IOA0             | B'0000<br>B'0100<br>B'1xxx | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | B'xx00 | Other than B'xx00                     |                         |      |  |

| CCLR1,<br>CCLR0          | —                          | —                                          | _      |                                       | Other<br>than B'01      | B'01 |  |

| Output<br>function       |                            | Output<br>compare<br>output                |        | PWM<br>mode 1<br>output <sup>*2</sup> | PWM<br>mode 2<br>output | —    |  |

x: Don't care

- Notes: 1. TIOCA2 input when MD3 to MD0 = B'0000 or B'01xx, and IOA3 = 1.

- 2. TIOCB2 output is disabled.

# Port B Data Register (PBDR)

| Bit        | :     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|            |       | PB7DR | PB6DR | PB5DR | PB4DR | PB3DR | PB2DR | PB1DR | PB0DR |

| Initial va | lue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W        | :     | R/W   |

PBDR is an 8-bit readable/writable register that stores output data for the port B pins (PB7 to PB0). PBDR is initialized to H'00 by a power-on reset, and in hardware standby mode. It retains its prior state by a manual reset or in software standby mode.

## Port B Register (PORTB)

| Bit                                             | :      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|--|

|                                                 |        | PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 |  |

| Initial va                                      | alue : | *   | *   | *   | *   | *   | *   | *   | *   |  |

| R/W                                             | :      | R   | R   | R   | R   | R   | R   | R   | R   |  |

| Note: * Determined by state of pins PB7 to PB0. |        |     |     |     |     |     |     |     |     |  |

Note: \* Determined by state of pins PB7 to PB0.

PORTB is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port B pins (PB7 to PB0) must always be performed on PBDR.

If a PORTB read is performed while PBDDR bits are set to 1, the PBDR values are read. If a PORTB read is performed while PBDDR bits are cleared to 0, the pin states are read.

After a power-on reset and in hardware standby mode, PORTB contents are determined by the pin states, as PBDDR and PBDR are initialized. PORTB retains its prior state in software standby mode.

| Port   | Description                                                                                                                      | Pins                                                                                                                                       | Mode 4                                                                   | Mode 5                                                                                                                                                        | Mode 6 | Mode 7                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|

| Port 7 | 8-bit I/O port                                                                                                                   | P77/TxD3<br>P76/RxD3<br>P75/SCK3<br>P74/MRES<br>P73/CS7<br>P72/CS6<br>P71/CS5<br>P70/CS4                                                   | 8-bit I/O port als<br>output pins (CS-<br>RxD3, TxD3), ar<br>(MRES)      | 8-bit I/O port<br>also function-<br>ing as SCI I/O<br>pins (SCK3,<br>RxD3, TxD3)<br>and the<br>manual reset<br>input pin<br>(MRES)                            |        |                                                                                                 |

| Port 9 | 8-bit input     port                                                                                                             | P97/AN15<br>P96/AN14<br>P95/AN13<br>P94/AN12<br>P93/AN11<br>P92/AN10<br>P91/AN9<br>P90/AN8                                                 | 8-bit input port a<br>(AN15 to AN8)                                      | r analog inputs                                                                                                                                               |        |                                                                                                 |

| Port A | <ul> <li>4-bit I/O<br/>port</li> <li>Built-in<br/>MOS input<br/>pull-up</li> <li>Open-drain<br/>output<br/>capability</li> </ul> | PA3/A19/SCK2<br>PA2/A18/RxD2<br>PA1/A17/TxD2<br>PA0/A16                                                                                    | 4-bit I/O port als<br>2) I/O pins (TxD<br>outputs (A19 to                | 2, RxD2, SCK2)                                                                                                                                                |        | 4-bit I/O port<br>also function-<br>ing as SCI<br>(channel 2)<br>I/O pins (TxD2,<br>RxD2, SCK2) |

| Port B | 8-bit I/O port<br>Built-in MOS<br>input pull-up<br>Open-drain<br>output<br>capability                                            | PB7/A15/TIOCB5<br>PB6/A14/TIOCA5<br>PB5/A13/TIOCB4<br>PB4/A12/TIOCA4<br>PB3/A11/TIOCD3<br>PB2/A10/TIOCC3<br>PB1/A9/TIOCB3<br>PB0/A8/TIOCA3 | 8-bit I/O port als<br>(TIOCB5, TIOC/<br>TIOCC3, TIOCE<br>outputs (A15 to | 8-bit I/O port<br>also<br>functioning as<br>TPU I/O pins<br>(TIOCB5,<br>TIOCA5,<br>TIOCB4,<br>TIOCA4,<br>TIOCD3,<br>TIOCC3,<br>TIOCC3,<br>TIOCB3,<br>TIIOCA3) |        |                                                                                                 |

P1DR is initialized to H'00 by a power-on reset, and in hardware standby mode. It retains its prior state by a manual reset or in software standby mode.

### Port 1 Register (PORT1)

| Bit                                            | :      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-----|--|

|                                                |        | P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |  |

| Initial va                                     | alue : | *   | *   | *   | *   | *   | *   | *   | *   |  |

| R/W                                            | :      | R   | R   | R   | R   | R   | R   | R   | R   |  |

| Note: * Determined by state of pine P17 to P10 |        |     |     |     |     |     |     |     |     |  |

Note: \* Determined by state of pins P17 to P10.

PORT1 is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port 1 pins (P17 to P10) must always be performed on P1DR.

If a PORT1 read is performed while P1DDR bits are set to 1, the P1DR values are read. If a PORT1 read is performed while P1DDR bits are cleared to 0, the pin states are read.

After a power-on reset and in hardware standby mode, PORT1 contents are determined by the pin states, as P1DDR and P1DR are initialized. PORT1 retains its prior state by a manual reset or in software standby mode.

| Pin                                                                                                                  | Selection Meth                                                                                                                                   | od and Pin          | Function             | IS   |                   |                    |        |                     |                      |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|-------------------|--------------------|--------|---------------------|----------------------|

| PF3/LWR/ADTRG/<br>IRQ3                                                                                               | The pin function is switched as shown below according to the operating mode, the bus mode, A/D converter bits TRGS1 and TRGS0, and bit PF3DDR.   |                     |                      |      |                   |                    |        |                     |                      |

|                                                                                                                      | Operating mode                                                                                                                                   |                     | Modes 4 to 6         |      |                   |                    |        | Мос                 | le 7                 |

|                                                                                                                      | Bus mode                                                                                                                                         | 16-bit bus<br>mode  | 8-bit bus mode       |      |                   | е                  |        | _                   | -                    |

|                                                                                                                      | PF3DDR                                                                                                                                           | —                   | 0                    |      |                   | 1                  |        | 0                   | 1                    |

|                                                                                                                      | Pin function                                                                                                                                     | LWR output<br>pin   | PF3 inp<br>pin       | out  |                   | output<br>in       |        | 3 input<br>pin      | PF3 output<br>pin    |

|                                                                                                                      |                                                                                                                                                  |                     |                      |      | AD                | TRG i              | nput   | pin*1               |                      |

|                                                                                                                      |                                                                                                                                                  |                     |                      |      | IF                | RQ3 inp            | out pi | in <sup>*2</sup>    |                      |

|                                                                                                                      | Notes: 1. ADT                                                                                                                                    | •                   |                      |      |                   |                    |        |                     |                      |

| <ol> <li>When used as an external interrupt input pin, do not use as an I/O<br/>pin for another function.</li> </ol> |                                                                                                                                                  |                     |                      |      |                   |                    |        |                     |                      |

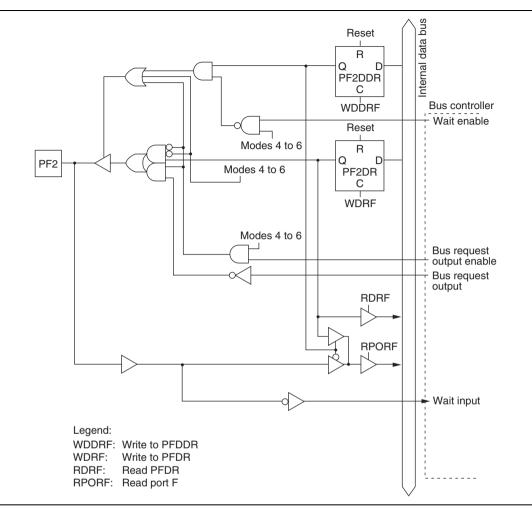

| PF2/ WAIT/<br>BREQO                                                                                                  | The pin function is switched as shown below according to the combination of the operating mode and bits BREQOE, WAITE, ABW5 to ABW2, and PF2DDR. |                     |                      |      |                   |                    |        |                     |                      |

|                                                                                                                      | Operating<br>Mode                                                                                                                                | Modes 4 to 6        |                      |      |                   |                    | Mode 7 |                     |                      |

|                                                                                                                      | BREQOE                                                                                                                                           |                     | 0                    |      |                   | 1                  | —      |                     |                      |

|                                                                                                                      | WAITE                                                                                                                                            | 0                   |                      |      | 1                 |                    |        | —                   |                      |

|                                                                                                                      | PF2DDR                                                                                                                                           | 0                   | 1                    | -    |                   |                    |        | 0                   | 1                    |

|                                                                                                                      | Pin function                                                                                                                                     | PF2<br>input<br>pin | PF2<br>output<br>pin | in   | AIT<br>put<br>pin | BRE<br>outp<br>pir | ut     | PF2<br>input<br>pin | PF2<br>output<br>pin |

| PF1/BACK                                                                                                             | The pin function the operating me                                                                                                                |                     |                      |      |                   |                    | g to t | he coml             | pination of          |

|                                                                                                                      | Operating<br>Mode                                                                                                                                |                     | Modes 4              | to 6 | ;                 |                    |        | Мос                 | le 7                 |

|                                                                                                                      | BRLE                                                                                                                                             |                     | 0                    |      |                   | 1                  |        | _                   | _                    |

|                                                                                                                      | PF1DDR                                                                                                                                           | 0                   | 1                    |      |                   | _                  |        | 0                   | 1                    |

|                                                                                                                      | Pin function                                                                                                                                     | PF1 input<br>pin    | PF1 out<br>pin       | tput |                   | .CK<br>ut pin      |        | 1 input<br>pin      | PF1 output<br>pin    |

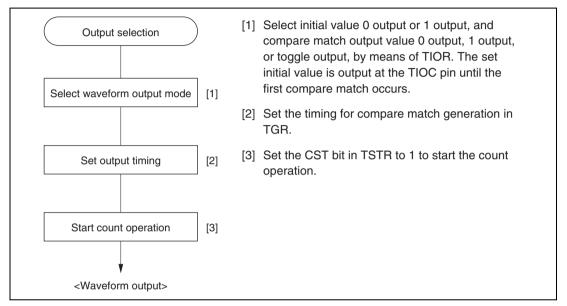

### Waveform Output by Compare Match

The TPU can perform 0, 1, or toggle output from the corresponding output pin using compare match.

**Example of setting procedure for waveform output by compare match:** Figure 11.9 shows an example of the setting procedure for waveform output by compare match

Figure 11.9 Example of Setting Procedure for Waveform Output by Compare Match

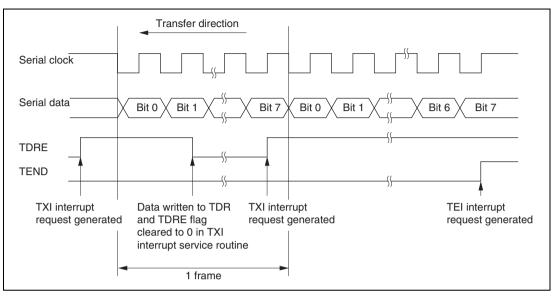

Figure 16.17 shows an example of SCI operation in transmission.

Figure 16.17 Example of SCI Operation in Transmission

Serial data reception (clocked synchronous mode): Figure 16.18 shows a sample flowchart for serial reception.

The following procedure should be used for serial data reception.

When changing the operating mode from asynchronous to clocked synchronous, be sure to check that the ORER, PER, and FER flags are all cleared to 0.

The RDRF flag will not be set if the FER or PER flag is set to 1, and neither transmit nor receive operations will be possible.

# 16.4 SCI Interrupts

The SCI has four interrupt sources: the transmit-end interrupt (TEI) request, receive-error interrupt (ERI) request, receive-data-full interrupt (RXI) request, and transmit-data-empty interrupt (TXI) request. Table 16.13 shows the interrupt sources and their relative priorities. Individual interrupt sources can be enabled or disabled with the TIE, RIE, and TEIE bits in the SCR. Each kind of interrupt request is sent to the interrupt controller independently.

When the TDRE flag in SSR is set to 1, a TXI interrupt request is generated. When the TEND flag in SSR is set to 1, a TEI interrupt request is generated. A TXI interrupt can activate the DMAC<sup>\*</sup> or DTC<sup>\*</sup> to perform data transfer. The TDRE flag is cleared to 0 automatically when data transfer is performed by the DMAC<sup>\*</sup> or DTC<sup>\*</sup>. The DMAC<sup>\*</sup> or DTC<sup>\*</sup> cannot be activated by a TEI interrupt request.

When the RDRF flag in SSR is set to 1, an RXI interrupt request is generated. When the ORER, PER, or FER flag in SSR is set to 1, an ERI interrupt request is generated. An RXI interrupt can activate the DMAC<sup>\*</sup> or DTC<sup>\*</sup> to perform data transfer. The RDRF flag is cleared to 0 automatically when data transfer is performed by the DMAC<sup>\*</sup> or DTC<sup>\*</sup>. The DMAC<sup>\*</sup> or DTC<sup>\*</sup> cannot be activated by an ERI interrupt request.

Note that the  $DMAC^*$  cannot be activated by interrupts of SCI channels 2 to 4.

Note: \* DMAC and DTC functions are not available in the H8S/2695.

| Bit 4 |                                                                                       |                                  |

|-------|---------------------------------------------------------------------------------------|----------------------------------|

| TRS   | Description                                                                           |                                  |

| 0     | Receive mode                                                                          | (Initial value)                  |

|       | [Clearing conditions]                                                                 |                                  |

|       | 1. When 0 is written by software (in cases other than setting c                       | ondition 3)                      |

|       | 2. When 0 is written in TRS after reading TRS = 1 (in case of                         | clearing condition 3)            |

|       | 3. When bus arbitration is lost after transmission is started in I                    | <sup>2</sup> C bus format master |

|       | mode                                                                                  |                                  |

| 1     | Transmit mode                                                                         |                                  |

|       | [Setting conditions]                                                                  |                                  |

|       | 1. When 1 is written by software (in cases other than clearing                        | conditions 3 and 4)              |

|       | <ol> <li>When 1 is written in TRS after reading TRS = 0 (in case of and 4)</li> </ol> | clearing conditions 3            |

|       | 3. When 1 is received as the R/W bit of the first frame in I <sup>2</sup> C bit       | us format slave mode             |

**Bit 3—Acknowledge Bit Judgement Selection (ACKE):** Specifies whether the value of the acknowledge bit returned from the receiving device when using the I<sup>2</sup>C bus format is to be ignored and continuous transfer is performed, or transfer is to be aborted and error handling, etc., performed if the acknowledge bit is 1. When the ACKE bit is 0, the value of the received acknowledge bit is not indicated by the ACKB bit, which is always 0.

In the H8S/2633 Group, the DTC<sup>\*</sup> can be used to perform continuous transfer. The DTC<sup>\*</sup> is activated when the IRTR interrupt flag is set to 1 (IRTR is one of two interrupt flags, the other being IRIC). When the ACKE bit is 0, the TDRE, IRIC, and IRTR flags are set on completion of data transmission, regardless of the value of the acknowledge bit. When the ACKE bit is 1, the TDRE, IRIC, and IRTR flags are set on completion of data transmission when the acknowledge bit is 0, and the IRIC flag alone is set on completion of data transmission when the acknowledge bit is 1.

When the DTC<sup>\*</sup> is activated, the TDRE, IRIC, and IRTR flags are cleared to 0 after the specified number of data transfers have been executed. Consequently, interrupts are not generated during continuous data transfer, but if data transmission is completed with a 1 acknowledge bit when the ACKE bit is set to 1, the DTC<sup>\*</sup> is not activated and an interrupt is generated, if enabled.

Depending on the receiving device, the acknowledge bit may be significant, in indicating completion of processing of the received data, for instance, or may be fixed at 1 and have no significance.

Note: \* The DTC function is not available in the H8S/2695.

# 22.5 Register Descriptions

| Bit:           | 7   | 6    | 5    | 4    | 3   | 2   | 1   | 0   |

|----------------|-----|------|------|------|-----|-----|-----|-----|

|                | FWE | SWE1 | ESU1 | PSU1 | EV1 | PV1 | E1  | P1  |

| Initial value: | *   | 0    | 0    | 0    | 0   | 0   | 0   | 0   |

| R/W:           | R   | R/W  | R/W  | R/W  | R/W | R/W | R/W | R/W |

## 22.5.1 Flash Memory Control Register 1 (FLMCR1)

Note: \* Determined by the state of the FWE pin.

FLMCR1 is an 8-bit register used for flash memory operating mode control. Program-verify mode or erase-verify mode for addresses H'00000 to H'3FFFF is entered by setting SWE1 bit to 1 when FWE = 1, then setting the PV1 or EV1 bit. Program mode for addresses H'00000 to H'3FFFF is entered by setting SWE1 bit to 1 when FWE = 1, then setting the PSU1 bit, and finally setting the P1 bit. Erase mode for addresses H'00000 to H'3FFFF is entered by setting SWE1 bit to 1 when FWE = 1, then setting the ESU1 bit, and finally setting the E1 bit. FLMCR1 is initialized by a power-on reset, and in hardware standby mode and software standby mode. Its initial value is H'80 when a high level is input to the FWE pin, and H'00 when a low level is input. When on-chip flash memory is disabled, a read will return H'00, and writes are invalid.

Writes are enabled only in the following cases: Writes to bit SWE1 of FLMCR1 enabled when FWE = 1, to bits ESU1, PSU1, EV1, and PV1 when FWE = 1 and SWE1 = 1, to bit E1 when FWE = 1, SWE1 = 1 and ESU1 = 1, and to bit P1 when FWE = 1, SWE1 = 1, and PSU1 = 1.

Bit 7—Flash Write Enable Bit (FWE): Sets hardware protection against flash memory programming/erasing.

| FWE | _<br>Description                                                    |

|-----|---------------------------------------------------------------------|

| 0   | When a low level is input to the FWE pin (hardware-protected state) |

| 1   | When a high level is input to the FWE pin                           |

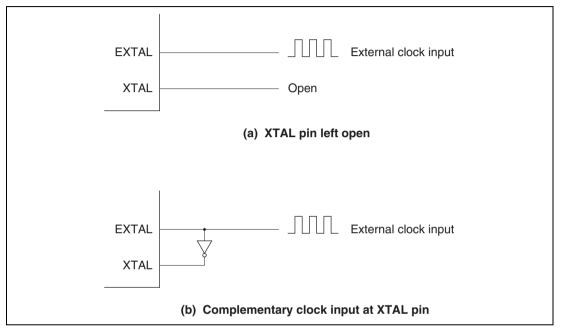

## 23A.3.2 External Clock Input

**Circuit Configuration:** An external clock signal can be input as shown in the examples in figure 23A.6. If the XTAL pin is left open, make sure that stray capacitance is no more than 10 pF.

In example (b), make sure that the external clock is held high in standby mode.

Figure 23A.6 External Clock Input (Examples)

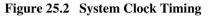

Figure 25.3 Oscillator Settling Timing

| Item                                 |                                         | Symbol           | Min | Тур                          | Max | Unit | Test<br>Conditions                  |

|--------------------------------------|-----------------------------------------|------------------|-----|------------------------------|-----|------|-------------------------------------|

| MOS input<br>pull-up current         | Ports A to E                            | I <sub>P</sub>   | 50  | _                            | 300 | μΑ   | $V_{in} = 0 V$                      |

| Input                                | RES                                     | C <sub>in</sub>  | _   | _                            | 30  | рF   | $V_{in} = 0 V$                      |

| capacitance                          | NMI                                     | -                | _   | _                            | 30  | рF   | f = 1 MHz                           |

|                                      | All input pins<br>except RES<br>and NMI | -                |     | _                            | 15  | pF   | <sup>–</sup> T <sub>a</sub> = 25°C  |

| Current<br>dissipation <sup>*2</sup> | Normal operation                        | I_cc *4          | _   | 70                           | 84  | mA   | f = 28 MHz                          |

|                                      | Sleep mode                              | -                | _   | 55                           | 77  | mA   | f = 28 MHz                          |

|                                      | All modules stopped                     |                  | _   | 40                           | _   | mA   | f = 28 MHz<br>(reference<br>values) |

|                                      | Medium-speed<br>mode (\phi/32)          | -                |     | 54                           | _   | mA   | f = 28 MHz<br>(reference<br>values) |

|                                      | Standby                                 | -                | _   | 0.1                          | 5.0 | μΑ   | $T_a \le 50^\circ C$                |

|                                      | mode                                    |                  | _   | _                            | 20  | _    | 50°C < T <sub>a</sub>               |

| Analog<br>power supply               | During A/D conversion                   | Al <sub>cc</sub> | —   | 0.6                          | 2.0 | mA   | $AV_{cc} = 5.0 V$                   |

| current                              | Idle                                    | -                | —   | 0.1<br>T <sub>a</sub> = 25°C | 5.0 | μΑ   |                                     |

| Reference<br>power supply            | During A/D conversion                   | $AI_{cc}$        | —   | 4.0                          | 5.0 | mA   | $V_{ref} = 5.0 V$                   |

| current                              | Idle                                    | -                | _   | 0.1<br>T <sub>a</sub> = 25°C | 5.0 | μΑ   |                                     |

| RAM standby v                        | voltage*3                               | $V_{\text{RAM}}$ | 2.0 | _                            | _   | V    |                                     |

Notes: 1. If the A/D converter is not used, do not leave the AV<sub>cc</sub>, V<sub>ref</sub>, and AV<sub>ss</sub> pins open. Apply a voltage between 3.3 V and 5.5 V to the AV<sub>cc</sub> and V<sub>ref</sub> pins by connecting them to PV<sub>cc</sub>, for instance. Set V<sub>ref</sub>  $\leq$  AV<sub>cc</sub>.

- 2. Current dissipation values are for  $V_{\mu} = AV_{cc}$  (ports 4 and 9), or  $PV_{cc}$  (other), and  $V_{\mu} = 0$  V, with all output pins unloaded and the on-chip MOS pull-up transistors in the off state.

- 3. The values are for  $V_{_{RAM}} \leq PV_{_{CC}} <$  3.0 V,  $V_{_{IH}}$  min =  $PV_{_{CC}} -$  0.1 V, and  $V_{_{IL}}$  max = 0.1 V.

- 4.  $I_{cc}$  depends on PV<sub>cc</sub> and f as follows:

$I_{cc}$  max = 15 (mA) + 0.45 (mA/(MHz × V)) × PV<sub>cc</sub> × f (normal operation)

$I_{cc}$  max = 15 (mA) + 0.40 (mA/(MHz × V)) × PV<sub>cc</sub> × f (sleep mode)

| Instruction code  |     | 1st byte | 2nd byte | byte | 3rd | 3rd byte | 4th byte      | oyte | 5th byte   | te | 6th byte |    |          |                          |                                                                                                    |                              |                          |

|-------------------|-----|----------|----------|------|-----|----------|---------------|------|------------|----|----------|----|----------|--------------------------|----------------------------------------------------------------------------------------------------|------------------------------|--------------------------|

|                   | AH  | AL       | ВН       | ВГ   | Ю   | СГ       | Н             | Ы    | 표          | Ш  | FH       |    |          |                          |                                                                                                    |                              |                          |

|                   |     |          |          |      |     |          |               |      |            |    | Ţ        |    | Instrue  | ction wher<br>ction wher | Instruction when most significant bit of FH is 0 Instruction when most significant bit of FH is 1. | nificant bit<br>nificant bit | of FH is 0<br>of FH is 1 |

| НАЦВНВІСНСІДНОІЕН | 0   | -        | 0        | e    |     | 4        | 5             | 9    | 2          | 80 | 6        | ۲  | 8        | υ                        |                                                                                                    | ш                            | ш                        |

| 6A10aaa6*         |     |          |          |      | Ļ   |          |               |      |            |    |          |    |          |                          |                                                                                                    |                              |                          |

| 6A10aaa7*         |     |          |          |      |     | Νб       | BXOR<br>BIXOR | BAND | BLD<br>BLD |    |          |    |          |                          |                                                                                                    |                              |                          |

| 6A18aaa6*         |     |          |          |      |     |          |               |      | <u> </u> 2 |    |          |    |          |                          |                                                                                                    |                              |                          |

| 6A18aaa7*         | DOE | DNG      | всги     | r    |     |          |               |      |            |    |          |    |          |                          |                                                                                                    |                              |                          |

|                   |     |          |          |      |     |          |               |      |            |    |          |    |          |                          |                                                                                                    |                              |                          |

| Instruction code  | 18  | 1st byte | 2nd byte | byte | 3rd | 3rd byte | 4th byte      | oyte | 5th byte   | te | 6th byte | 71 | 7th byte | 8th byte                 | /te                                                                                                |                              |                          |

|                   | AH  | AL       | ВН       | BL   | СН  | СГ       | Н             | DL   | H          | E  | FI       | GH | GL       | 포                        | н                                                                                                  |                              |                          |

|                   |     |          |          |      |     |          |               |      |            |    | Ļ        |    |          | ction wher<br>ction wher | Instruction when most significant bit of HH is 0 Instruction when most significant bit of HH is 1  | nificant bit<br>nificant bit | of HH is 0<br>of HH is 1 |

RENESAS

BST BIST BIAND BIXOR BIOR BCLR BNOT BSET 6A38aaaaaaa7\* 6A38aaaaaaa6\*

Mar 02, 2011

ο<del>΄</del> Γ

Page 1187 of 1434

.. <del>.</del>.

ш

ш

C

ш

∢

ი

ω

$\sim$

9

ß

4

ო

N

-

0

GL GL ... FHFLGH 6A30aaaaaaa6\*

6A30aaaaaaa7\*

BLD

BAND

BXOR

BOR

BTST

### NDRH—Next Data Register H

Same trigger for pulse output groups.

| Bit :            | 7            | 6          | 5      | 4     | 3     | 2     | 1    | 0    |

|------------------|--------------|------------|--------|-------|-------|-------|------|------|

|                  | NDR15        | NDR14      | NDR13  | NDR12 | NDR11 | NDR10 | NDR9 | NDR8 |

| Initial value :  | 0            | 0          | 0      | 0     | 0     | 0     | 0    | 0    |

| R/W :            | R/W          | R/W        | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  |

|                  |              |            |        |       |       |       |      |      |

| Bit :            | 7            | 6          | 5      | 4     | 3     | 2     | 1    | 0    |

|                  | —            | —          | —      | —     | —     | —     | —    | _    |

| Initial value :  | 1            | 1          | 1      | 1     | 1     | 1     | 1    | 1    |

| R/W :            | _            | _          | _      | _     | _     | _     | _    | _    |

|                  |              |            |        |       |       |       |      |      |

| Different trigge | ers for puls | e output g | roups. |       |       |       |      |      |

|                  |              |            |        |       |       |       |      |      |

| Bit :            | 7            | 6          | 5      | 4     | 3     | 2     | 1    | 0    |

|                  | NDR15        | NDR14      | NDR13  | NDR12 | _     | _     | _    | _    |

| Initial value :  | 0            | 0          | 0      | 0     | 1     | 1     | 1    | 1    |

| R/W :            | R/W          | R/W        | R/W    | R/W   | _     | _     | _    | _    |

|                  |              |            |        |       |       |       |      |      |

| Bit :            | 7            | 6          | 5      | 4     | 3     | 2     | 1    | 0    |

|                  | —            | —          | —      | —     | NDR11 | NDR10 | NDR9 | NDR8 |

| Initial value :  | 1            | 1          | 1      | 1     | 0     | 0     | 0    | 0    |

| R/W :            |              | _          | _      | _     | R/W   | R/W   | R/W  | R/W  |

Note: For details see section 12.2.4, Notes on NDR Access.

H'FE2C, H'FE2E PPG

Figure C.23 (c) Port F Block Diagram (Pin PF2)