Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 48MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 46                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 12K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x16b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-LQFP                                                                |

| Supplier Device Package    | 80-FQFP (12x12)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08mm128vlk |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Devices in the MC9S08MM128 series

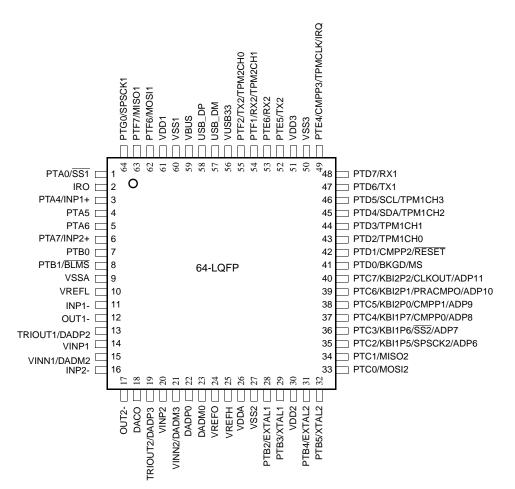

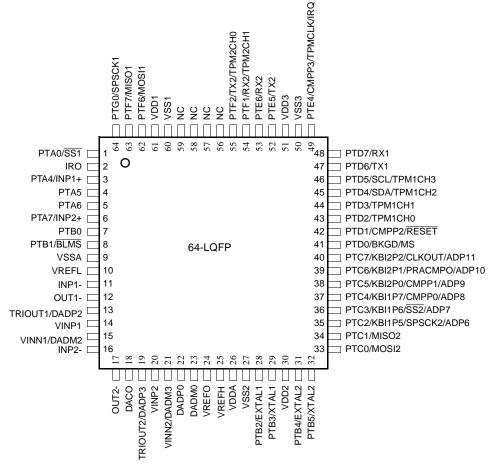

## 1.1 Pin Assignments

This section shows the pin assignments for the MC9S08MM128 series devices.

## 1.1.1 64-Pin LQFP

The following two figures show the 64-pin LQFP pinout configuration. The first illustrates the pinout configuration for MC9S08MM128, MC9S08MM64, and MC9S08MM32 devices.

#### Figure 2. 64-Pin LQFP for MC9S08MM128, MC9S08MM64, and MC9S08MM32 devices

For MC9S08MM32A devices, pins 56, 57, 58, and 59 are no connects (NC) as illustrated in the following figure.

Figure 3. 64-Pin LQFP for MC9S08MM32A devices

Freescale Semiconductor

# 2.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in the following table may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

| # | Rating                                                                                          | Symbol           | Value                         | Unit |

|---|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| 1 | Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| 2 | Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| 3 | Digital input voltage                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| 4 | Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | ۱ <sub>D</sub>   | ± 25                          | mA   |

| 5 | Storage temperature range                                                                       | T <sub>stg</sub> | -55 to 150                    | °C   |

| Table 5. | Absolute | Maximum | Ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}.

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## 2.4 ESD Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) This device was qualified to AEC-Q100 Rev E.

A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                 | Symbol | Value | Unit |

|------------|-----------------------------|--------|-------|------|

| Human Body | Series Resistance           | R1     | 1500  | Ω    |

|            | Storage Capacitance         | С      | 100   | pF   |

|            | Number of Pulse per pin     | —      | 3     |      |

| Machine    | Series Resistance           | R1     | 0     | Ω    |

|            | Storage Capacitance         | С      | 200   | pF   |

|            | Number of Pulse per pin     | —      | 3     | _    |

| Latch-up   | Minimum input voltage limit | —      | -2.5  | V    |

|            | Maximum input voltage limit | —      | 7.5   | V    |

Table 7. ESD and Latch-up Test Conditions

| Table 8 | . ESD | and | Latch-Up | Protection | Characteristics |

|---------|-------|-----|----------|------------|-----------------|

|---------|-------|-----|----------|------------|-----------------|

| # | Rating                                     | Symbol           | Min   | Max | Unit | С |

|---|--------------------------------------------|------------------|-------|-----|------|---|

| 1 | Human Body Model (HBM)                     | V <sub>HBM</sub> | ±2000 |     | V    | Т |

| 2 | Machine Model (MM)                         | V <sub>MM</sub>  | ±200  |     | V    | Т |

| 3 | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ±500  |     | V    | Т |

| 4 | Latch-up Current at T <sub>A</sub> = 125°C | I <sub>LAT</sub> | ±100  |     | mA   | Т |

| # | Symbol             | Parameter                                      | Bus         | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Max  | Unit | Temp          | С |

|---|--------------------|------------------------------------------------|-------------|---------------------|------------------|------|------|---------------|---|

|   | -                  |                                                | Freq        |                     |                  |      |      | (°C)          |   |

| 5 | WI <sub>DD</sub>   | Wait mode FEI mode, supply current             | all modules | OFF <sup>3</sup>    |                  |      |      |               |   |

|   |                    |                                                | 24 MHz      | 3                   | 6.7              | _    | mA   | -40 to<br>105 | С |

|   |                    |                                                | 20 MHz      | 3                   | 5.6              | _    | mA   | -40 to<br>105 | Т |

|   |                    |                                                | 8 MHz       | 3                   | 2.4              | _    | mA   | -40 to<br>105 | Т |

|   |                    |                                                | 1 MHz       | 3                   | 1                | _    | mA   | -40 to<br>105 | Т |

| 6 | LPWI <sub>DD</sub> | Low-Power<br>Wait mode<br>supply current       |             |                     |                  |      |      |               |   |

|   |                    |                                                | 16 KHz      | 3                   | 10               | 40   | μA   | -40 to<br>105 | Т |

| 7 | S2I <sub>DD</sub>  | Stop2 mode<br>supply cur-<br>rent <sup>4</sup> |             |                     |                  |      |      |               |   |

|   |                    |                                                | N/A         | 3                   | 0.39             | 0.8  | μΑ   | -40 to<br>25  | Ρ |

|   |                    |                                                | N/A         | 3                   | 2.4              | 4.5  | μA   | 70            | С |

|   |                    |                                                | N/A         | 3                   | 7                | 11   | μA   | 85            | С |

|   |                    |                                                | N/A         | 3                   | 16               | 22   | μA   | 105           | Р |

|   |                    |                                                | N/A         | 2                   | 0.2              | 0.45 | μA   | -40 to<br>25  | С |

|   |                    |                                                | N/A         | 2                   | 2                | 3.8  | μA   | 70            | С |

|   |                    |                                                | N/A         | 2                   | 8                | 12   | μA   | 85            | С |

|   |                    |                                                | N/A         | 2                   | 10               | 20   | μA   | 105           | С |

## Table 10. Supply Current Characteristics (Continued)

| # | Parameter           | Condition                        |     | Temperature (°C) |     |     |     |         |   |

|---|---------------------|----------------------------------|-----|------------------|-----|-----|-----|---------|---|

| # | Farameter           |                                  | -40 | 25               | 70  | 85  | 105 | - Units | С |

| 7 | DAC <sup>1</sup>    | High-Power mode; no load on DACO | 369 | 377              | 377 | 390 | 410 | μA      | Т |

|   |                     | Low-Power mode                   | 50  | 51               | 51  | 52  | 60  | μΑ      | Т |

| 8 | OPAMP <sup>1</sup>  | High-Power mode                  | 453 | 538              | 538 | 540 | 540 | μA      | Т |

| 0 |                     | Low-Power mode                   | 56  | 67               | 67  | 68  | 70  | μA      | Т |

| 9 | TRIAMP <sup>1</sup> | High-Power mode                  | 430 | 432              | 433 | 438 | 478 | μA      | Т |

| 9 |                     | Low-Power mode                   | 52  | 52               | 52  | 55  | 60  | μA      | Т |

#### Table 11. Typical Stop Mode Adders (Continued)

$\overline{1}$  Not available in stop2 mode.

# 2.7 PRACMP Electricals

|    |                                                |                                       |                     |         | 1               | 1    |   |

|----|------------------------------------------------|---------------------------------------|---------------------|---------|-----------------|------|---|

| #  | Characteristic                                 | Symbol                                | Min                 | Typical | Max             | Unit | С |

| 1  | Supply voltage                                 | V <sub>PWR</sub>                      | 1.8                 |         | 3.6             | V    | Р |

| 2  | Supply current (active) (PRG enabled)          | I <sub>DDACT1</sub>                   | —                   |         | 80              | μA   | D |

| 3  | Supply current (active) (PRG disabled)         | I <sub>DDACT2</sub>                   | —                   |         | 40              | μA   | D |

| 4  | Supply current (ACMP and PRG all disabled)     | I <sub>DDDIS</sub>                    | —                   | _       | 2               | nA   | D |

| 5  | Analog input voltage                           | VAIN                                  | $V_{SS} - 0.3$      |         | V <sub>DD</sub> | V    | D |

| 6  | Analog input offset voltage                    | VAIO                                  | —                   | 5       | 40              | mV   | D |

| 7  | Analog comparator hysteresis                   | V <sub>H</sub>                        | 3.0                 | _       | 20.0            | mV   | D |

| 8  | Analog input leakage current                   | I <sub>ALKG</sub>                     | —                   | _       | 1               | nA   | D |

| 9  | Analog comparator initialization delay         | tAINIT                                | —                   | _       | 1.0             | μS   | D |

| 10 | Programmable reference generator inputs        | V <sub>In2</sub> (V <sub>DD25</sub> ) | 1.8                 | _       | 2.75            | V    | D |

| 11 | Programmable reference generator setup delay   | t <sub>PRGST</sub>                    | —                   | 1       | _               | μs   | D |

| 12 | Programmable reference generator step size     | Vstep                                 | 0.75                | 1       | 1.25            | LSB  | D |

| 13 | Programmable reference generator voltage range | Vprgout                               | V <sub>In</sub> /32 | _       | V <sub>in</sub> | V    | Р |

#### Table 12. PRACMP Electrical Specifications

| #  | Characteristic                                                                    | Symbol               | Min                        | Тур  | Max   | Unit  | С | Notes                                                                                               |

|----|-----------------------------------------------------------------------------------|----------------------|----------------------------|------|-------|-------|---|-----------------------------------------------------------------------------------------------------|

| 9  | DAC output voltage range high<br>(high-power mode, no load, DAC<br>set to 0x0FFF) | V <sub>dacouth</sub> | V <sub>DACR</sub> -<br>100 | _    | _     | mV    | т |                                                                                                     |

| 10 | Integral non-linearity error                                                      | INL                  | —                          | —    | ± 8   | LSB   | Т |                                                                                                     |

| 11 | Differential non-linearity error<br>VDACR is > 2.4 V                              | DNL                  | _                          | _    | ± 1   | LSB   | т |                                                                                                     |

| 12 | Offset error                                                                      | E <sub>O</sub>       | _                          | ±0.4 | ± 3   | %FSR  | т | Calculated by a<br>best fit curve<br>from V <sub>SS</sub> +<br>100mV to<br>V <sub>REFH</sub> -100mV |

| 13 | Gain error, V <sub>REFH</sub> = V <sub>ext</sub> = V <sub>DD</sub>                | E <sub>G</sub>       | _                          | ±0.1 | ± 0.5 | %FSR  | т | Calculated by a<br>best fit curve<br>from V <sub>SS</sub> +<br>100mV to<br>V <sub>REFH</sub> –100mV |

| 14 | Power supply rejection ratio $V_{DD} \ge 2.4 \text{ V}$                           | PSRR                 | 60                         | _    | _     | dB    | т |                                                                                                     |

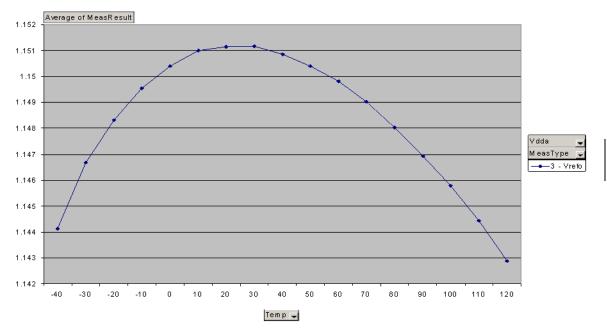

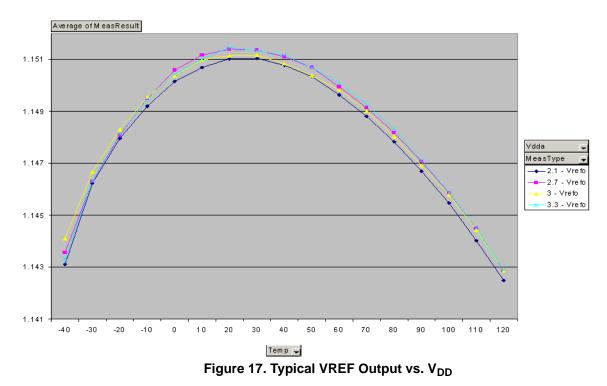

| 15 | Temperature drift of offset voltage (DAC set to 0x0800)                           | T <sub>co</sub>      | _                          |      | 2     | mV    | Т | See Typical<br>Drift figure that<br>follows.                                                        |

| 16 | Offset aging coefficient                                                          | A <sub>c</sub>       | —                          | —    | 8     | μV/yr | Т |                                                                                                     |

Table 14. DAC 12-Bit Operating Behaviors (Continued)

Figure 6. Offset at Half Scale vs Temperature

# 2.9 ADC Characteristics

| # | Symb              | Characteristic              | Conditions                                                                    | Min               | Typ <sup>1</sup> | Max              | Unit | С | Comment                                   |

|---|-------------------|-----------------------------|-------------------------------------------------------------------------------|-------------------|------------------|------------------|------|---|-------------------------------------------|

| 1 | V <sub>DDA</sub>  | Supply voltage              | Absolute                                                                      | 1.8               | —                | 3.6              | V    | D |                                           |

| 2 | $\Delta V_{DDA}$  |                             | Delta to V <sub>DD</sub><br>(V <sub>DD</sub> –V <sub>DDA</sub> ) <sup>2</sup> | -100              | 0                | +100             | mV   | D |                                           |

| 3 | $\Delta V_{SSA}$  | Ground voltage              | Delta to V <sub>SS</sub><br>(V <sub>SS</sub> –V <sub>SSA</sub> ) <sup>2</sup> | -100              | 0                | +100             | mV   | D |                                           |

| 4 | V <sub>REFH</sub> | Ref Voltage High            |                                                                               | 1.15              | V <sub>DDA</sub> | V <sub>DDA</sub> | V    | D |                                           |

| 5 | V <sub>REFL</sub> | Ref Voltage Low             |                                                                               | V <sub>SSA</sub>  | V <sub>SSA</sub> | V <sub>SSA</sub> | V    | D |                                           |

| 6 | V <sub>ADIN</sub> | Input Voltage               |                                                                               | V <sub>REFL</sub> | —                | $V_{REFH}$       | V    | D |                                           |

| 7 | C <sub>ADIN</sub> | Input<br>Capacitance        | 16-bit modes<br>8/10/12-bit modes                                             | _                 | 8<br>4           | 10<br>5          | pF   | Т |                                           |

| 8 | R <sub>ADIN</sub> | Input Resistance            |                                                                               | _                 | 2                | 5                | kΩ   | Т |                                           |

| 9 | R <sub>AS</sub>   | Analog Source<br>Resistance |                                                                               |                   |                  |                  |      |   | External to<br>MCU<br>Assumes<br>ADLSMP=0 |

|   |                   | 16-bit mode                 | f <sub>ADCK</sub> > 8 MHz                                                     | _                 | _                | 0.5              | kΩ   | т |                                           |

|   |                   |                             | 4 MHz < f <sub>ADCK</sub> < 8<br>MHz                                          | —                 | —                | 1                | kΩ   | т |                                           |

|   |                   |                             | f <sub>ADCK</sub> < 4 MHz                                                     |                   | _                | 2                | kΩ   | Т |                                           |

|   |                   | 13/12-bit mode              | f <sub>ADCK</sub> > 8 MHz                                                     | —                 | —                | 1                | kΩ   | т |                                           |

|   |                   |                             | 4 MHz < f <sub>ADCK</sub> < 8<br>MHz                                          | _                 | —                | 2                | kΩ   | Т |                                           |

|   |                   |                             | f <sub>ADCK</sub> < 4 MHz                                                     | _                 | —                | 5                | kΩ   | Т |                                           |

|   |                   | 11/10-bit mode              | f <sub>ADCK</sub> > 8 MHz                                                     | _                 | —                | 2                | kΩ   | Т |                                           |

|   |                   |                             | 4 MHz < f <sub>ADCK</sub> < 8<br>MHz                                          | _                 | _                | 5                | kΩ   | т |                                           |

|   |                   |                             | f <sub>ADCK</sub> < 4 MHz                                                     |                   | —                | 10               | kΩ   | Т |                                           |

|   |                   | 9/8-bit mode                | f <sub>ADCK</sub> > 8 MHz                                                     | _                 | —                | 5                | kΩ   | т |                                           |

|   |                   |                             | f <sub>ADCK</sub> < 8 MHz                                                     | _                 | _                | 10               | kΩ   | Т |                                           |

## Table 15. 16-Bit ADC Operating Conditions

# Table 16. 16-Bit SAR ADC Characteristics full operating range (V<sub>REFH</sub> = V<sub>DDA</sub>, > 1.8, V<sub>REFL</sub> = V<sub>SSA</sub> $\leq$ 8 MHz, –40 to 85 °C) (Continued)

| #  | Characteristic                  | Conditions <sup>1</sup>                                                 | Symb            | Min                                  | Typ <sup>2</sup>                     | Max                  | Unit             | С | Comment                                           |

|----|---------------------------------|-------------------------------------------------------------------------|-----------------|--------------------------------------|--------------------------------------|----------------------|------------------|---|---------------------------------------------------|

| 8  | Integral<br>Non-Linearity       | 16-bit differential mode<br>16-bit single-ended mode                    | INL             |                                      | ±6.0<br>±10.0                        | ±16.0<br>±20.0       | LSB <sup>2</sup> | Т |                                                   |

|    |                                 | 13-bit differential mode<br>12-bit single-ended mode                    |                 | _                                    | ±1.0<br>±1.0                         | ±2.5<br>±2.5         |                  | Т |                                                   |

|    |                                 | 11-bit differential mode<br>10-bit single-ended mode                    |                 | _                                    | ±0.5<br>±0.5                         | ±1.0<br>±1.0         |                  | Т |                                                   |

|    |                                 | 9-bit differential mode<br>8-bit single-ended mode                      |                 | _                                    | ±0.3<br>±0.3                         | ±0.5<br>±0.5         |                  | Т |                                                   |

| 9  | Zero-Scale<br>Error             | 16-bit differential mode<br>16-bit single-ended mode                    | E <sub>ZS</sub> | _                                    | ±4.0<br>±4.0                         | +32/ –24<br>+24/ –16 | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>SSA</sub>           |

|    |                                 | 13-bit differential mode<br>12-bit single-ended mode                    |                 | _                                    | ±0.7<br>±0.7                         | ±2.5<br>±2.0         |                  | Т |                                                   |

|    |                                 | 11-bit differential mode<br>10-bit single-ended mode                    |                 | _                                    | ±0.4<br>±0.4                         | ±1.0<br>±1.0         |                  | Т |                                                   |

|    |                                 | 9-bit differential mode<br>8-bit single-ended mode                      |                 |                                      | ±0.2<br>±0.2                         | ±0.5<br>±0.5         |                  | Т |                                                   |

| 10 | Full-Scale Error                | 16-bit differential mode<br>16-bit single-ended mode                    | E <sub>FS</sub> |                                      | +10/0<br>+14/0                       | +42/–2<br>+46/–2     | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>DDA</sub>           |

|    |                                 | 13-bit differential mode<br>12-bit single-ended mode                    |                 |                                      | ±1.0<br>±1.0                         | ±3.5<br>±3.5         |                  | Т |                                                   |

|    |                                 | 11-bit differential mode<br>10-bit single-ended mode                    |                 | _                                    | ±0.4<br>±0.4                         | ±1.5<br>±1.5         |                  | Т |                                                   |

|    |                                 | 9-bit differential mode<br>8-bit single-ended mode                      |                 | _                                    | ±0.2<br>±0.2                         | ±0.5<br>±0.5         |                  | Т |                                                   |

| 11 | Quantization<br>Error           | 16-bit modes                                                            | EQ              | _                                    | -1 to 0                              | _                    | LSB <sup>2</sup> | D |                                                   |

|    |                                 | ≤13-bit modes                                                           |                 | _                                    | —                                    | ±0.5                 |                  |   |                                                   |

| 12 | Effective<br>Number of Bits     | 16-bit differential mode<br>Avg=32<br>Avg=16<br>Avg=8<br>Avg=4<br>Avg=1 | ENOB            | 12.8<br>12.7<br>12.6<br>12.5<br>11.9 | 14.2<br>13.8<br>13.6<br>13.3<br>12.5 | <br> <br> <br>       | Bits             | С | F <sub>in</sub> =<br>F <sub>sample</sub> /10<br>0 |

| 13 | Signal to Noise plus Distortion | See ENOB                                                                | SINAD           | SINAD                                | $= 6.02 \cdot E$                     | <i>NOB</i> + 1.76    | dB               |   |                                                   |

| Table 17. 16-bit SAR ADC Characteristics full operating range                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|

| (V <sub>REFH</sub> = V <sub>DDA</sub> , $\geq$ 2.7 V, V <sub>REFL</sub> = V <sub>SSA</sub> , f <sub>ADACK</sub> $\leq$ 4 MHz, ADHSC = 1) |

| # | Characteristic                | Conditions <sup>1</sup>                              | Symb            | Min | Typ <sup>2</sup> | Мах                 | Unit             | С | Comment                                                         |

|---|-------------------------------|------------------------------------------------------|-----------------|-----|------------------|---------------------|------------------|---|-----------------------------------------------------------------|

| 1 | Total<br>Unadjusted<br>Error  | 16-bit differential mode<br>16-bit single-ended mode | TUE             |     | ±16<br>±20       | +24/ -24<br>+32/-20 | LSB <sup>3</sup> | Т | 32x<br>Hardware<br>Averaging<br>(AVGE =<br>%1<br>AVGS =<br>%11) |

|   |                               | 13-bit differential mode<br>12-bit single-ended mode |                 | _   | ±1.5<br>±1.75    | ±2.0<br>±2.5        |                  | Т |                                                                 |

|   |                               | 11-bit differential mode<br>10-bit single-ended mode |                 |     | ±0.7<br>±0.8     | ±1.0<br>±1.25       |                  | Т |                                                                 |

|   |                               | 9-bit differential mode<br>8-bit single-ended mode   |                 |     | ±0.5<br>±0.5     | ±1.0<br>±1.0        |                  | Т |                                                                 |

| 2 | Differential<br>Non-Linearity | 16-bit differential mode<br>16-bit single-ended mode | DNL             | _   | ±2.5<br>±2.5     | ±3<br>±3            | LSB <sup>2</sup> | Т |                                                                 |

|   |                               | 13-bit differential mode<br>12-bit single-ended mode |                 | _   | ±0.7<br>±0.7     | ±1<br>±1            |                  | Т |                                                                 |

|   |                               | 11-bit differential mode<br>10-bit single-ended mode |                 |     | ±0.5<br>±0.5     | ±0.75<br>±0.75      |                  | Т |                                                                 |

|   |                               | 9-bit differential mode<br>8-bit single-ended mode   |                 |     | ±0.2<br>±0.2     | ±0.5<br>±0.5        |                  | Т |                                                                 |

| 3 | Integral<br>Non-Linearity     | 16-bit differential mode<br>16-bit single-ended mode | INL             |     | ±6.0<br>±10.0    | ±12.0<br>±16.0      | LSB <sup>2</sup> | Т |                                                                 |

|   |                               | 13-bit differential mode<br>12-bit single-ended mode |                 | _   | ±1.0<br>±1.0     | ±2.0<br>±2.0        |                  | Т |                                                                 |

|   |                               | 11-bit differential mode<br>10-bit single-ended mode |                 |     | ±0.5<br>±0.5     | ±1.0<br>±1.0        |                  | Т |                                                                 |

|   |                               | 9-bit differential mode<br>8-bit single-ended mode   |                 |     | ±0.3<br>±0.3     | ±0.5<br>±0.5        |                  | Т |                                                                 |

| 4 | Zero-Scale<br>Error           | 16-bit differential mode<br>16-bit single-ended mode | E <sub>ZS</sub> | _   | ±4.0<br>±4.0     | +16/0<br>+16/-8     | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>SSA</sub>                         |

|   |                               | 13-bit differential mode<br>12-bit single-ended mode |                 | _   | ±0.7<br>±0.7     | ±2.0 ±2.0           |                  | Т |                                                                 |

|   |                               | 11-bit differential mode<br>10-bit single-ended mode |                 |     | ±0.4<br>±0.4     | ±1.0<br>±1.0        |                  | Т |                                                                 |

|   |                               | 9-bit differential mode<br>8-bit single-ended mode   |                 | _   | ±0.2<br>±0.2     | ±0.5<br>±0.5        |                  | Т |                                                                 |

## Table 17. 16-bit SAR ADC Characteristics full operating range ( $V_{REFH} = V_{DDA}$ , $\ge 2.7$ V, $V_{REFL} = V_{SSA}$ , $f_{ADACK} \le 4$ MHz, ADHSC = 1) (Continued)

| <u> </u> |                                 |                                                                         |                 |                                      |                                      |                |                  |   | 1                                                                                  |

|----------|---------------------------------|-------------------------------------------------------------------------|-----------------|--------------------------------------|--------------------------------------|----------------|------------------|---|------------------------------------------------------------------------------------|

| #        | Characteristic                  | Conditions <sup>1</sup>                                                 | Symb            | Min                                  | Typ <sup>2</sup>                     | Max            | Unit             | С | Comment                                                                            |

| 5        | Full-Scale Error                | 16-bit differential mode<br>16-bit single-ended mode                    | E <sub>FS</sub> |                                      | +8/0<br>+12/0                        | +24/0<br>+24/0 | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>DDA</sub>                                            |

|          |                                 | 13-bit differential mode<br>12-bit single-ended mode                    |                 |                                      | ±0.7<br>±0.7                         | ±2.0<br>±2.5   |                  | Т |                                                                                    |

|          |                                 | 11-bit differential mode<br>10-bit single-ended mode                    |                 |                                      | ±0.4<br>±0.4                         | ±1.0<br>±1.0   |                  | Т |                                                                                    |

|          |                                 | 9-bit differential mode<br>8-bit single-ended mode                      |                 |                                      | ±0.2<br>±0.2                         | ±0.5<br>±0.5   |                  | Т |                                                                                    |

| 6        | Quantization<br>Error           | 16-bit modes                                                            | EQ              |                                      | -1 to 0                              | _              | LSB <sup>2</sup> | D |                                                                                    |

|          |                                 | ≤13-bit modes                                                           |                 |                                      |                                      | ±0.5           |                  |   |                                                                                    |

| 7        | Effective<br>Number of Bits     | 16-bit differential mode<br>Avg=32<br>Avg=16<br>Avg=8<br>Avg=4<br>Avg=1 | ENO<br>B        | 14.3<br>13.8<br>13.4<br>13.1<br>12.4 | 14.5<br>14.0<br>13.7<br>13.4<br>12.6 |                | Bits             | С | F <sub>in</sub> =<br>F <sub>sample</sub> /10<br>0                                  |

| 8        | Signal to Noise plus Distortion | See ENOB                                                                | SINA<br>D       | SINAD                                | $= 6.02 \cdot ENOB + 1.76$           |                | dB               |   |                                                                                    |

| 9        | Total Harmonic<br>Distortion    | 16-bit differential mode<br>Avg=32                                      | THD             | _                                    | -95.8                                | -90.4          | dB               | С | F <sub>in</sub> =<br>F <sub>sample</sub> /10                                       |

|          |                                 | 16-bit single-ended mode<br>Avg=32                                      |                 | _                                    | _                                    | _              |                  | D | 0                                                                                  |

| 10       | Dynamic                         | 16-bit differential mode<br>Avg=32                                      | SFDR            | 91.0                                 | 96.5                                 | _              | dB               | С | F <sub>in</sub> =<br>F <sub>sample</sub> /10<br>0                                  |

|          | Range                           | 16-bit single-ended mode<br>Avg=32                                      |                 | _                                    | _                                    | _              |                  | D | U                                                                                  |

| 11       | Input Leakage<br>Error          | all modes                                                               | E <sub>IL</sub> |                                      | I <sub>In</sub> * R <sub>AS</sub>    | 5              | mV               | D | I <sub>In</sub> =<br>leakage<br>current<br>(refer to<br>DC<br>characteri<br>stics) |

<sup>1</sup> All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

<sup>2</sup> Typical values assume V<sub>DDA</sub> = 3.0V, Temp = 25°C, f<sub>ADCK</sub>=2.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>3</sup> 1 LSB = (V<sub>REFH</sub> - V<sub>REFL</sub>)/2<sup>N</sup>

| # | Characteristic                     |                                                                                | Symbol                    | Min | Typ <sup>1</sup> | Max | Unit | С |

|---|------------------------------------|--------------------------------------------------------------------------------|---------------------------|-----|------------------|-----|------|---|

|   | Crystal start-up time <sup>4</sup> | • Low range, low gain (RANGE = 0, HGO = 0)                                     | t<br>CSTL-LP              | _   | 200              | _   |      | D |

| 6 |                                    | <ul> <li>Low range, high gain<br/>(RANGE = 0, HGO = 1)</li> </ul>              | t<br>CSTL-HG<br>O         | _   | 400              | _   |      | D |

|   |                                    | <ul> <li>High range, low gain<br/>(RANGE = 1, HGO = 0)<sup>5</sup></li> </ul>  | t <sub>CSTH-LP</sub>      | _   | 5                | _   | ms   | D |

|   |                                    | <ul> <li>High range, high gain<br/>(RANGE = 1, HGO = 1)<sup>5</sup></li> </ul> | <sup>t</sup> CSTH-HG<br>О | _   | 15               | _   |      | D |

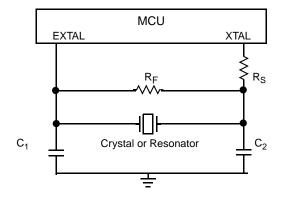

Table 19. XOSC (Temperature Range = -40 to 105°C Ambient)

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

<sup>2</sup> When MCG is configured for FEE or FBE mode, input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> When MCG is configured for PEE or PBE mode, input clock source must be divisible using RDIV to within the range of 1 MHz to 2 MHz.

<sup>4</sup> This parameter is characterized and not tested on each device. Proper PC board layout porcedures must be followed to achieve specifications.

<sup>5</sup> 4 MHz crystal.

| # | Symbol                                | Parameter                                                                               |                                                 | Min | Typical <sup>1</sup> | Max | С | Unit |  |

|---|---------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------|-----|----------------------|-----|---|------|--|

| 9 | t <sub>Rise</sub> , t <sub>Fall</sub> | $t_{Rise}$ , $t_{Fall}$ Port rise and fall time (load = 50 pF) <sup>4</sup> , Low Drive |                                                 |     |                      |     |   |      |  |

|   |                                       |                                                                                         | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 11                   | —   | D |      |  |

|   |                                       |                                                                                         | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  | _   | 35                   | _   | D |      |  |

|   |                                       |                                                                                         | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 40                   | _   | D |      |  |

|   |                                       |                                                                                         | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  |     | 75                   |     | D |      |  |

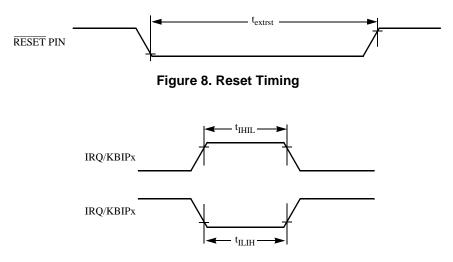

#### Table 20. Control Timing

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40 °C to 105 °C.

Figure 9. IRQ/KBIPx Timing

Freescale Semiconductor

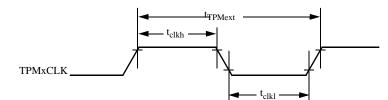

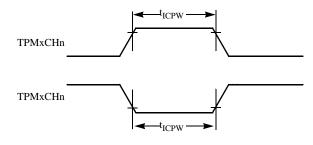

# 2.11.2 TPM Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

Table 21. TPM Input Timing

| # | С | Function                  | Symbol              | Min | Мах                 | Unit             |

|---|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1 | — | External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| 2 | — | External clock period     | t <sub>TPMext</sub> | 4   | —                   | t <sub>cyc</sub> |

| 3 | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 4 | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| 5 | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

Figure 10. Timer External Clock

Figure 11. Timer Input Capture Pulse

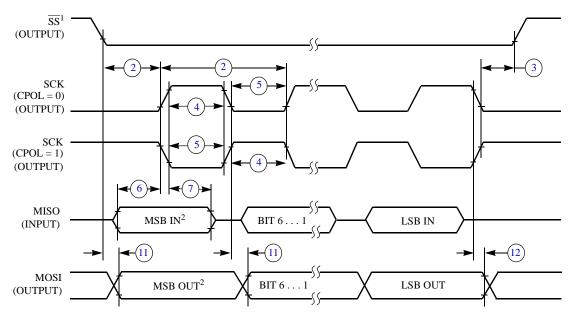

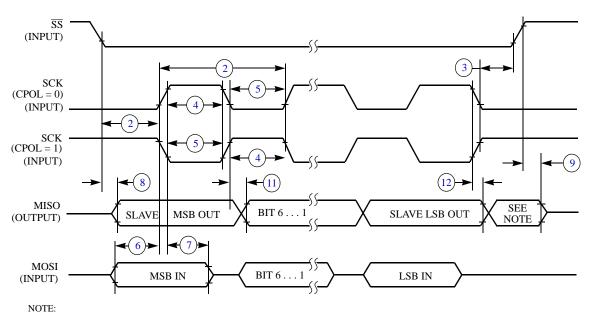

NOTES:

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

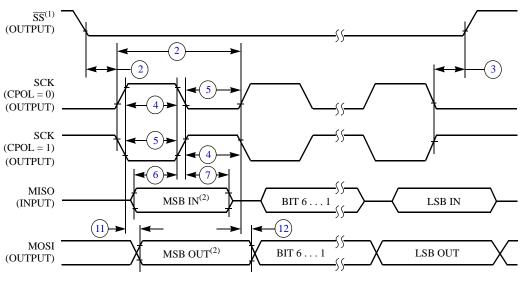

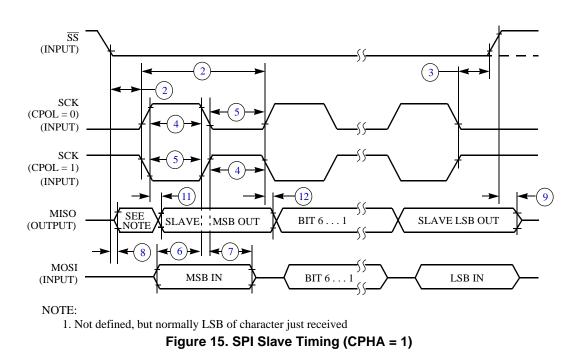

NOTES:

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 13. SPI Master Timing (CPHA = 1)

1. Not defined, but normally MSB of character just received **Figure 14. SPI Slave Timing (CPHA = 0)**

# 2.14 USB Electricals

The USB electricals for the USB On-the-Go module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit http://www.usb.org.

If the Freescale USB On-the-Go implementation has electrical characteristics that deviate from the standard or require additional information, this space would be used to communicate that information.

| # | Characteristic                                       | Symbol               | Min | Тур | Мах  | Unit | С |

|---|------------------------------------------------------|----------------------|-----|-----|------|------|---|

| 1 | Regulator operating voltage                          | V <sub>regin</sub>   | 3.9 | _   | 5.5  | V    | С |

| 2 | VREG output                                          | V <sub>regout</sub>  | 3   | 3.3 | 3.75 | V    | Р |

| 3 | V <sub>USB33</sub> input with internal VREG disabled | V <sub>usb33in</sub> | 3   | 3.3 | 3.6  | V    | С |

| 4 | VREG Quiescent Current                               | I <sub>VRQ</sub>     | _   | 0.5 | _    | mA   | С |

### Table 24. Internal USB 3.3 V Voltage Regulator Characteristics

## 2.16 TRIAMP Electrical Parameters

Table 27. TRIAMP Characteristics 1.8–3.6 V, –40°C~105°C

| #  | Characteristic <sup>1</sup>                                  | Symbol              | Min  | Typ <sup>2</sup> | Max                       | Unit   | С |

|----|--------------------------------------------------------------|---------------------|------|------------------|---------------------------|--------|---|

| 1  | Operating Voltage                                            | V <sub>DD</sub>     | 1.8  | —                | 3.6                       | V      | С |

| 2  | Supply Current (I <sub>OUT</sub> =0mA, CL=0) Low-power mode  | I <sub>SUPPLY</sub> |      | 52               | 60                        | μA     | Т |

| 3  | Supply Current (I <sub>OUT</sub> =0mA, CL=0) High-speed mode | I <sub>SUPPLY</sub> | _    | 432              | 480                       | μΑ     | Т |

| 4  | Input Offset Voltage                                         | V <sub>OS</sub>     |      | ± 1              | ± 5                       | mV     | Т |

| 5  | Input Offset Voltage Temperature Drift                       | α <sub>VOS</sub>    |      | 600              | —                         | μV     | Т |

| 6  | Input Offset Current                                         | I <sub>OS</sub>     |      | ±120             | 500                       | pА     | Т |

| 7  | Input Bias Current (0 ~ 50°C)                                | I <sub>BIAS</sub>   | _    | < 350            | < ±500                    | pА     | Т |

| 8  | Input Bias Current (–40 ~ 105°C)                             | I <sub>BIAS</sub>   |      | 3                | 6.55                      | nA     | Т |

| 9  | Input Common Mode Voltage Low                                | V <sub>CML</sub>    | 0    | —                | —                         | V      | Т |

| 10 | Input Common Mode Voltage High                               | V <sub>CMH</sub>    |      | —                | V <sub>DD</sub> -1.4      | V      | Т |

| 11 | Input Resistance                                             | R <sub>IN</sub>     | 500  | —                | —                         | MΩ     | Т |

| 12 | Input Capacitances                                           | C <sub>IN</sub>     |      | —                | 5                         | pF     | D |

| 13 | AC Input Impedance (f <sub>IN</sub> =100kHz)                 | X <sub>IN</sub>     | _    | 1                | —                         | MΩ     | D |

| 14 | Input Common Mode Rejection Ratio                            | CMRR                | 60   | 70               | —                         | dB     | Т |

| 15 | Power Supply Rejection Ration                                | PSRR                | 60   | 70               | —                         | dB     | Т |

| 16 | Slew Rate ( $\Delta V_{IN}$ =100mV) Low-power mode           | SR                  |      | 0.1              | —                         | V/µs   | Т |

| 17 | Slew Rate ( $\Delta V_{IN}$ =100mV) High-speed mode          | SR                  | _    | 1                | —                         | V/µs   | Т |

| 18 | Unity Gain Bandwidth (Low-power mode) 50pF                   | GBW                 | 0.15 | 0.25             | —                         | MHz    | Т |

| 19 | Unity Gain Bandwidth (High-speed mode) 50pF                  | GBW                 | _    | 1.6              | —                         | MHz    | Т |

| 20 | DC Open Loop Voltage Gain                                    | A <sub>V</sub>      |      | 80               | —                         | dB     | Т |

| 21 | Load Capacitance Driving Capability                          | CL(max)             |      | —                | 100                       | pF     | Т |

| 22 | Output Impedance AC Open Loop (@100 kHz<br>Low-power mode)   | R <sub>OUT</sub>    | _    | 1.4              | —                         | kΩ     | D |

| 23 | Output Impedance AC Open Loop (@100 kHz<br>High-speed mode)  | R <sub>OUT</sub>    | —    | 184              | —                         | Ω      | D |

| 24 | Output Voltage Range                                         | triout              | 0.15 | _                | V <sub>DD</sub> –<br>0.15 | V      | Т |

| 25 | Output Drive Capability                                      | I <sub>OUT</sub>    | _    | ± 1.0            | —                         | mA     | Т |

| 26 | Gain Margin                                                  | GM                  | 20   |                  | —                         | dB     | D |

| 27 | Phase Margin                                                 | PM                  | 45   | 55               | _                         | deg    | Т |

| 28 | Input Voltage Noise Density                                  | f= 1 kHz            | —    | 160              | —                         | nV/√Hz | Т |

<sup>1</sup> All parameters are measured at 3.0 V, CL= 47 pF across temperature -40 to + 105 °C unless specified.

$^2\,$  Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

# 2.17 **OPAMP Electrical Parameters**

| #    | Characteristics <sup>1</sup>                                  | Symbol              | Min  | Typ <sup>2</sup> | Max                       | Unit | С |

|------|---------------------------------------------------------------|---------------------|------|------------------|---------------------------|------|---|

|      |                                                               | _                   |      | тур              |                           |      |   |

| 1    | Operating Voltage                                             | V <sub>DD</sub>     | 1.8  | -                | 3.6                       | V    | C |

| 2    | Supply Current (I <sub>OUT</sub> =0mA, CL=0 Low-Power mode)   | I <sub>SUPPLY</sub> |      | 67               | 80                        | μΑ   | Т |

| 3    | Supply Current (I <sub>OUT</sub> =0mA, CL=0 High-Speed mode)  | I <sub>SUPPLY</sub> | —    | 538              | 550                       | μΑ   | Т |

| 4    | Input Offset Voltage                                          | V <sub>OS</sub>     | —    | ±2               | ±6                        | mV   | Т |

| 5    | Input Offset Voltage Temperature Coefficient                  | $\alpha_{VOS}$      | —    | 10               | —                         | μV/C | Т |

| 6    | Input Offset Current (-40°C to 105°C)                         | I <sub>OS</sub>     | —    | ±2.5             | ±250                      | nA   | Т |

| 7    | Input Offset Current (-40°C to 50°C)                          | I <sub>OS</sub>     | —    | —                | 45                        | nA   | Т |

| 8    | Positive Input Bias Current (-40°C to 105°C)                  | I <sub>BIAS</sub>   | _    | 0.8              | 3.5                       | nA   | Т |

| 9    | Positive Input Bias Current (-40°C to 50°C)                   | I <sub>BIAS</sub>   | —    | —                | ±2                        | nA   | Т |

| 10   | Negative Input Bias Current (-40°C to 105°C)                  | I <sub>BIAS</sub>   | —    | 2.5              | 250                       | nA   | Т |

| 11   | Negative Input Bias Current (-40°C to 50°C)                   | I <sub>BIAS</sub>   | —    | —                | 45                        | nA   | Т |

| 12   | Input Common Mode Voltage Low                                 | V <sub>CML</sub>    | 0.1  | —                | —                         | V    | Т |

| 13   | Input Common Mode Voltage High                                | V <sub>CMH</sub>    | —    | —                | V <sub>DD</sub>           | V    | Т |

| 14   | Input Resistance                                              | R <sub>IN</sub>     | —    | 500              | —                         | MΩ   | Т |

| 15   | Input Capacitances                                            | C <sub>IN</sub>     | —    | —                | 10                        | pF   | D |

| 16   | AC Input Impedance (f <sub>IN</sub> =100kHz Negative Channel) | X <sub>IN</sub>     | —    | 52               | —                         | kΩ   | D |

| 17   | AC Input Impedance (f <sub>IN</sub> =100kHz Positive Channel) | X <sub>IN</sub>     | _    | 132              | —                         | kΩ   | D |

| 18   | Input Common Mode Rejection Ratio                             | CMRR                | 55   | 65               | —                         | dB   | Т |

| 19   | Power Supply Rejection Ratio                                  | PSRR                | 60   | 65               | —                         | dB   | Т |

| 20   | Slew Rate ( $\Delta V_{IN}$ =100mV Low-Power mode)            | SR                  | 0.1  | —                | —                         | V/µs | Т |

| 21   | Slew Rate (△V <sub>IN</sub> =100mV High-Speed mode)           | SR                  | 1    | —                | —                         | V/µs | Т |

| 22   | Unity Gain Bandwidth (Low-Power mode)                         | GBW                 | 0.2  | —                | —                         | MHz  | Т |

| 23   | Unity Gain Bandwidth (High-Speed mode)                        | GBW                 | 1    | —                | —                         | MHz  | Т |

| 24   | DC Open Loop Voltage Gain                                     | A <sub>V</sub>      | 80   | 90               | —                         | dB   | Т |

| 25   | Load Capacitance Driving Capability                           | CL(max)             | _    | —                | 100                       | pF   | Т |

| 26   | Output Impedance AC Open Loop (@100 kHz<br>Low-Power mode)    | R <sub>OUT</sub>    | _    | 4k               | —                         | Ω    | D |

| 27   | Output Impedance AC Open Loop (@100 kHz<br>High-Speed mode)   | R <sub>OUT</sub>    | —    | 220              | —                         | Ω    | D |

| 28   | Output Voltage Range                                          | V <sub>OUT</sub>    | 0.15 | —                | V <sub>DD</sub> -0.1<br>5 | V    | Т |

| 29   | Output Drive Capability                                       | I <sub>OUT</sub>    | ±0.5 | ±1.0             | —                         | mA   | Т |

| - 00 | Gain Margin                                                   | GM                  | 20   |                  | _                         | dB   | D |

| 30   | Gain Margin                                                   | 0.01                | 20   |                  |                           | uр   |   |

Table 28. OPAMP Characteristics 1.8–3.6 V

Freescale Semiconductor