Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 24MHz                                                                                    |

| Connectivity               | UART/USART                                                                               |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                          |

| Number of I/O              | 17                                                                                       |

| Program Memory Size        | 2KB (2K x 8)                                                                             |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | 128 x 8                                                                                  |

| RAM Size                   | 256 x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

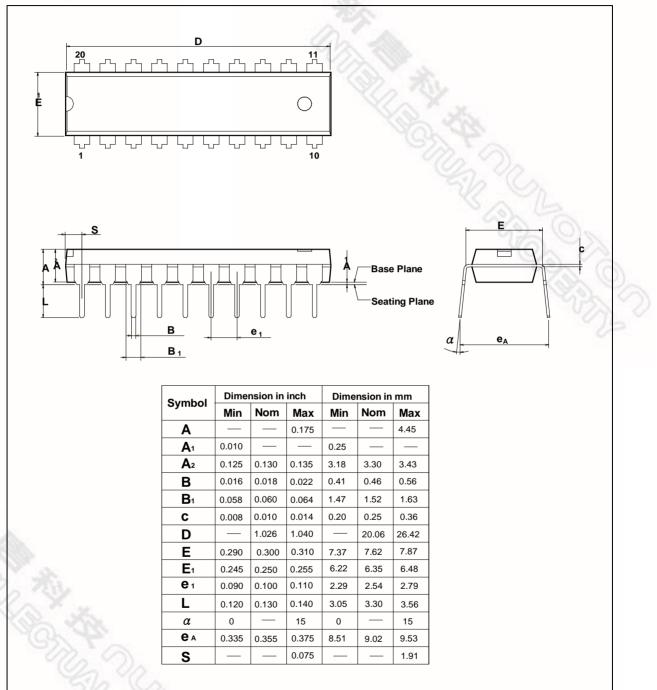

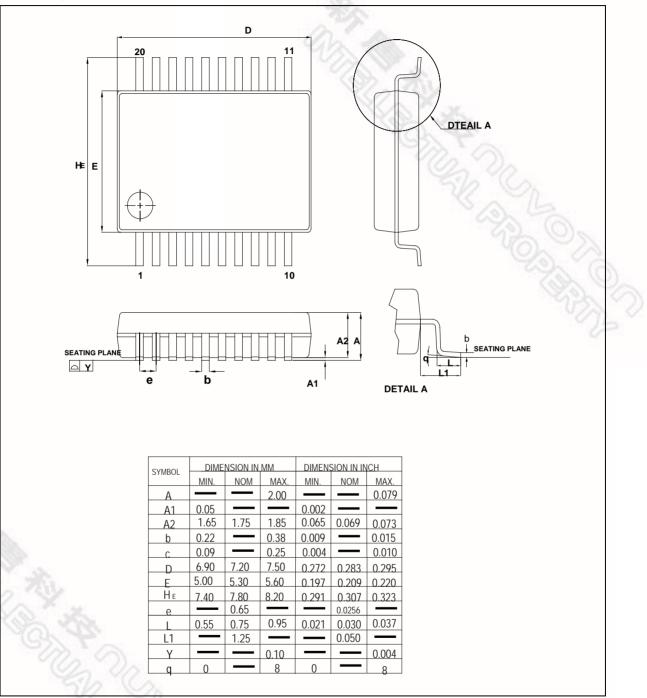

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                           |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e2051rasg |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## nuvoTon

- Lead Free (RoHS) PDIP 20: W79E2051RAKG

- Lead Free (RoHS) SOP 20: W79E2051RASG

- Lead Free (RoHS) SSOP 20: W79E2051RARG

### **3 PARTS INFORMATION LIST**

### 3.1 Lead Free (RoHS) Parts information list

Table 3-1: Lead Free (RoHS) Parts information list

| PART NO.     | PROGRAM<br>FLASH<br>EPROM | RAM  | DATA<br>FLASH<br>EPROM | INTERNAL RC<br>OSCILLATOR<br>ACCURACY <sup>1</sup> | PACKAGE     |

|--------------|---------------------------|------|------------------------|----------------------------------------------------|-------------|

| W79E4051AKG  | 4KB                       | 256B | 128B                   | 22MHz ± 25%                                        | PDIP-20 Pin |

| W79E4051ASG  | 4KB                       | 256B | 128B                   | 22MHz ± 25%                                        | SOP-20 Pin  |

| W79E4051ARG  | 4KB                       | 256B | 128B                   | 22MHz ± 25%                                        | SSOP-20 Pin |

| W79E2051AKG  | 2KB                       | 256B | 128B                   | 22MHz ± 25%                                        | PDIP-20 Pin |

| W79E2051ASG  | 2KB                       | 256B | 128B                   | 22MHz ± 25%                                        | SOP-20 Pin  |

| W79E2051ARG  | 2KB                       | 256B | 128B                   | 22MHz ± 25%                                        | SSOP-20 Pin |

| W79E4051RAKG | 4KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | PDIP-20 Pin |

| W79E4051RASG | 4KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | SOP-20 Pin  |

| W79E4051RARG | 4KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | SSOP-20 Pin |

| W79E2051RAKG | 2KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | PDIP-20 Pin |

| W79E2051RASG | 2KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | SOP-20 Pin  |

| W79E2051RARG | 2KB                       | 256B | 128B                   | 22.1184MHz ± 2%                                    | SSOP-20 Pin |

Note:

1. Factory calibration condition:  $V_{DD}=5.0V$ , TA = 25°C

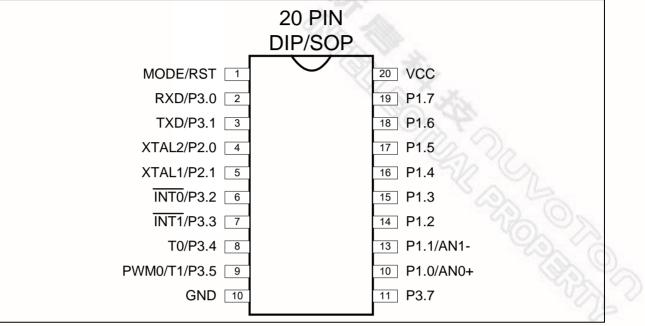

### **4 PIN CONFIGURATION**

Table 4-1: Pin Configuration

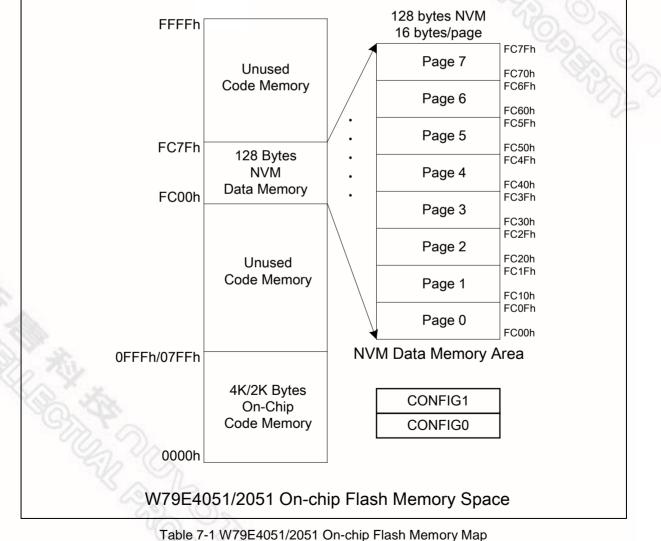

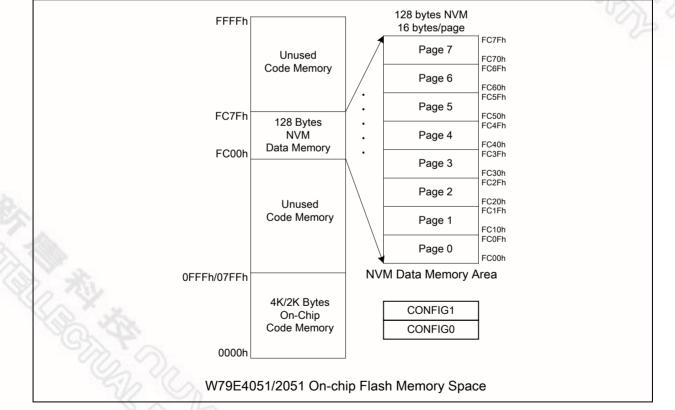

### 7 MEMORY ORGANIZATION

The W79E4051/2051 series separate the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

### 7.1 Program Memory (on-chip Flash)

The Program Memory on the W79E4051/2051 series can be up to **4K/2K** bytes long. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region.

### 7.2 Data Flash Memory

The Data Flash EPROM on the W79E4051/2051 series is **128** bytes long with page size of **16** bytes. The W79E4051/2051 series read the content of data memory by using "MOVC A, @A+DPTR". To write data is by NVMADDRL, NVMDATA and NVMCON SFR's registers.

### 8 SPECIAL FUNCTION REGISTERS

The W79E4051/2051 series uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes. The SFRs reside in the register locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where users wish to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The W79E4051/2051 series contain all the SFRs present in the standard 8052. However some additional SFRs are added. In some cases the unused bits in the original 8052, have been given new functions. The list of the SFRs is as follows.

|    | <u> </u> | -     | 9     |       |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

|----|----------|-------|-------|-------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| F8 | IP1      |       |       |       |         | Carl M | 1. Contraction 1. Con |                                         |

| F0 | В        |       |       |       |         | "(D)"  | PCMPIDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IP1H                                    |

| E8 | EIE      |       |       |       |         |        | OB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |

| E0 | ACC      |       |       |       |         | 51     | 2 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |

| D8 | WDCON    | PWMPL | PWM0L |       | PWMCON1 |        | s a The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) |

| D0 | PSW      | PWMPH | PWM0H |       |         |        | 62 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWMCON3                                 |

| C8 |          |       |       |       |         |        | NVMCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NVMDATA                                 |

| C0 |          |       |       |       |         |        | NVMADDRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ТА                                      |

| B8 | IP0      | SADEN |       |       |         |        | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                       |

| B0 | P3       |       |       | P1M1  |         |        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IP0H                                    |

| A8 | IE       | SADDR |       |       |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Six S                                   |

| A0 | P2       |       | AUXR1 | AUXR2 |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | "mo                                     |

| 98 | SCON     | SBUF  |       |       |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                       |

| 90 | P1       |       |       |       |         |        | ACCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ACSR                                    |

| 88 | TCON     | TMOD  | TL0   | TL1   | TH0     | TH1    | CKCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CLKREG                                  |

| 80 |          | SP    | DPL   | DPH   |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PCON                                    |

Table 8-1: Special Function Register Location Table

Note:

- 1. The SFRs in the column with dark borders are bit-addressable

- 2. The table is condensed with eight locations per row. Empty locations indicate that these are no registers at these addresses.

| 0 | IDL | 1: The CPU goes into the IDLE mode. In this mode, the clocks CPU clock stopped,  |

|---|-----|----------------------------------------------------------------------------------|

|   |     | so program execution is frozen. But the clock to the serial, timer and interrupt |

|   |     | blocks is not stopped, and these blocks continue operating.                      |

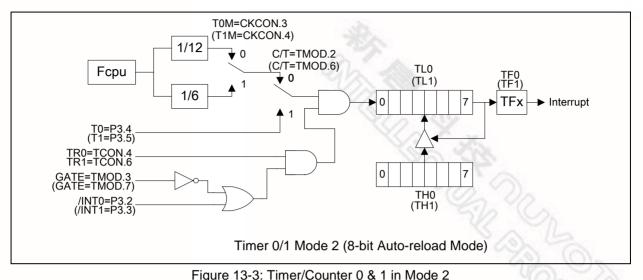

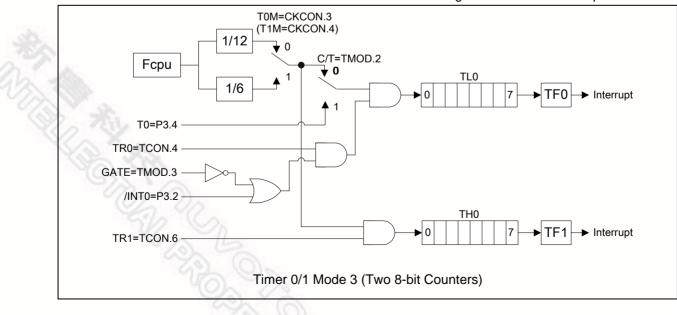

### TIMER CONTROL

|      |           | -                             |                                                                                                                                                                                                                                                                    |               |                                               |              |                |                       |  |  |  |  |  |

|------|-----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------|--------------|----------------|-----------------------|--|--|--|--|--|

| Bit: | 7         | 6                             | 5                                                                                                                                                                                                                                                                  | 4             | 3                                             | 2            | 1              | 0                     |  |  |  |  |  |

|      | TF1       | TR1                           | TF0                                                                                                                                                                                                                                                                | TR0           | IE1                                           | IT1          | IE0            | IT0                   |  |  |  |  |  |

| N    | Inemonic: | TCON                          |                                                                                                                                                                                                                                                                    |               | 4                                             | Ya.          | 22             | Address: 88h          |  |  |  |  |  |

| BIT  | NAME      | FUNCTION                      | FUNCTION                                                                                                                                                                                                                                                           |               |                                               |              |                |                       |  |  |  |  |  |

| 7    | TF1       | automaticall                  | ner 1 Overflow Flag. This bit is set when Timer 1 overflows. It is cleared tomatically when the program does a timer 1 interrupt service routine. Software n also set or clear this bit.                                                                           |               |                                               |              |                |                       |  |  |  |  |  |

| 6    | TR1       | Timer 1 Run<br>or off.        | Control. T                                                                                                                                                                                                                                                         | his bit is se | et or cleared                                 | by software  | e to turn time | er/counter on         |  |  |  |  |  |

| 5    | TF0       |                               | y when the                                                                                                                                                                                                                                                         | program c     | set when Tin<br>loes a timer (                |              |                | eared<br>ne. Software |  |  |  |  |  |

| 4    | TR0       | Timer 0 Rur<br>or off.        | Control. T                                                                                                                                                                                                                                                         | his bit is se | et or cleared                                 | by softwar   | e to turn time | er/counter on         |  |  |  |  |  |

| 3    | IE1       | INT1. This b                  | oit is cleare                                                                                                                                                                                                                                                      | d by hardw    | by hardware<br>are when the<br>Otherwise it f | e service ro | outine is vec  | tored to only if      |  |  |  |  |  |

| 2    | IT1       | Interrupt 1 T<br>triggered ex |                                                                                                                                                                                                                                                                    |               | red by softwa                                 | are to spec  | ify falling ed | ge/ low level         |  |  |  |  |  |

| 1    | IEO       | on INT0 . Th                  | Interrupt 0 Edge Detect Flag. Set by hardware when an edge/level is detected on $\overline{INT0}$ . This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin. |               |                                               |              |                |                       |  |  |  |  |  |

| 0    | IT0       | Interrupt 0 T<br>triggered ex |                                                                                                                                                                                                                                                                    |               | red by softwa                                 | are to spec  | ify falling ed | ge/ low level         |  |  |  |  |  |

| TIME | R MODE C | ONTROL |    |    |        |     |    |    |

|------|----------|--------|----|----|--------|-----|----|----|

| Bit: | 7        | 6      | 5  | 4  | 3      | 2   | 1  | 0  |

|      | GATE     | C/T    | M1 | MO | GATE   | C/T | M1 | MO |

|      | TIMER1   | 1      |    |    | TIMER0 |     | •  |    |

| N   | Inemonic: | TMOD Address: 89h                                                                                                                                                                                                                                            |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | NAME      | FUNCTION                                                                                                                                                                                                                                                     |

| 7   | GATE      | Gating control: When this bit is set, Timer/counter 1 is enabled only while the $\overline{INT1}$ pin is high and the TR1 control bit is set. When cleared, the $\overline{INT1}$ pin has no effect, and Timer 1 is enabled whenever TR1 control bit is set. |

| 6   | C/T       | Timer or Counter Select: When clear, Timer 1 is incremented by the internal clock.<br>When set, the timer counts falling edges on the T1 pin.                                                                                                                |

| 5   | M1        | Timer 1 mode select bit 1. See table below.                                                                                                                                                                                                                  |

## nuvoTon

| 4 | 4 | Drownout voltogo is 4 EV |  |

|---|---|--------------------------|--|

| 1 | I | Brownout voltage is 4.5V |  |

All the bits in this SFR have unrestricted read access. SRST require Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

### **AUX FUNCTION REGISTER 2**

| Bit: | 7            | 6          | 5       | 4             | 3     | 2    | 1            | 0     |

|------|--------------|------------|---------|---------------|-------|------|--------------|-------|

|      | -            | -          | -       | -             | -     |      | 35           | DPS   |

| N    | Inemonic: AL | JXR2       |         |               | Yah   | 22   | Address: A3h |       |

| BIT  | NAME         | FUNCTIO    | N       |               | -47   | 20   |              |       |

| 7-1  | -            | Reserved   |         |               |       | 6    | 27.4         | 2 ~   |

|      |              | Dual Data  | Pointer |               |       | W. S | 2h           |       |

| 0    | DPS          | 0: To sele | ct DPTF | R of standard | 8051. |      |              | LES . |

|      |              | 1: To sele | ct DPTF | R1            |       |      | 2            | 200   |

#### **INTERRUPT ENABLE**

| Bit: | 7  | 6  | 5 | 4  | 3   | 2   | 1   | 0   |

|------|----|----|---|----|-----|-----|-----|-----|

|      | EA | EC | - | ES | ET1 | EX1 | ET0 | EX0 |

| Μ   | Inemonic: IE | Address: A8                                   |

|-----|--------------|-----------------------------------------------|

| BIT | NAME         | FUNCTION                                      |

| 7   | EA           | Global enable. Enable/Disable all interrupts. |

| 6   | EC           | Enable analog comparator interrupt.           |

| 5   | -            | Reserved.                                     |

| 4   | ES           | Enable Serial Port 0 interrupt.               |

| 3   | ET1          | Enable Timer 1 interrupt.                     |

| 2   | EX1          | Enable external interrupt 1.                  |

| 1   | ET0          | Enable Timer 0 interrupt.                     |

| 0   | EX0          | Enable external interrupt 0.                  |

### SLAVE ADDRESS

| Bit: | 7                                                                                                                                      | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

|      | SADDR.7                                                                                                                                | SADDR.6 | SADDR.5 | SADDR.4 | SADDR.3 | SADDR.2 | SADDR.1 | SADDR.0 |  |  |  |  |  |

| N    | Mnemonic: SADDR Address: A9h                                                                                                           |         |         |         |         |         |         |         |  |  |  |  |  |

| BIT  | BIT NAME FUNCTION                                                                                                                      |         |         |         |         |         |         |         |  |  |  |  |  |

| 7~0  | 7~0 SADDR The SADDR should be programmed to the given or broadcast address for serial port to which the slave processor is designated. |         |         |         |         |         |         |         |  |  |  |  |  |

| PORT | PORT 3                                                                                                                                 |         |         |         |         |         |         |         |  |  |  |  |  |

6 Bit: 7 4 3 2 1 0 5

| 1 | _    |       | _    | L _  | _    | -    | _    | _    |  |

|---|------|-------|------|------|------|------|------|------|--|

|   | P3.7 | CMP_O | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3.0 |  |

Mnemonic: P3

Address: B0h

P3.7-0: General purpose Input/Output port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. These alternate functions are described below:

| BIT | NAME  | FUNCTION                                                   |

|-----|-------|------------------------------------------------------------|

| 7   | P3.7  |                                                            |

| 6   | CMP_O | Read only. This bit stores the hardware comparator result. |

| 5   | P3.5  | T1 or PWM output                                           |

| 4   | P3.4  | ТО                                                         |

| 3   | P3.3  | INT1                                                       |

| 2   | P3.2  | INTO                                                       |

| 1   | P3.1  | TX                                                         |

| 0   | P3.0  | RX                                                         |

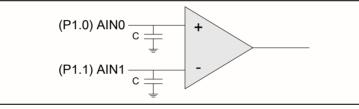

### Port1 Output Mode 1

| Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|------|---|---|---|---|---|---|--------|--------|

|      | - | - | - | - | - | - | P1M1.1 | P1M1.0 |

|      |   |   |   |   |   |   |        |        |

| M   | nemonic: P1 | M1 Address: B3h                          |

|-----|-------------|------------------------------------------|

| BIT | NAME        | FUNCTION                                 |

| 7-2 | Reserved    |                                          |

| 1   | P1M1.1      | 0: P1.1 is in open drain mode. (Default) |

|     |             | 1: P1.1 is in Quasi-bidirection mode     |

| 0   | P1M1.0      | 0: P1.0 is in open drain mode. (Default) |

|     |             | 1: P1.0 is in Quasi-bidirection mode     |

### **Interrupt High Priority 0**

| Bit: | 7 | 6   | 5 | 4   | 3    | 2    | 1    | 0    |

|------|---|-----|---|-----|------|------|------|------|

| S.   | - | PCH | - | PSH | PT1H | PX1H | PT0H | PX0H |

**Mnemonic: IP0H** Address: B7h BIT FUNCTION NAME 7 Reserved \_ 6 PCH 1: To set interrupt high priority of analog comparator is highest priority level. 5 4 Reserved. PSH 4 1: To set interrupt high priority of Serial port 0 is highest priority level. 3 PT1H 1: To set interrupt high priority of Timer 1 is highest priority level. 2 PX1H 1: To set interrupt high priority of External interrupt 1 is highest priority level. PT0H 1: To set interrupt high priority of Timer 0 is highest priority level. 1 PX0H 1: To set interrupt high priority of External interrupt 0 is highest priority level. 0

| Ν   | Inemonic: | PSW Address: D0h                                                                                                                                  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | NAME      | FUNCTION                                                                                                                                          |

| 7   | CY        | Carry flag:                                                                                                                                       |

|     |           | Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations. |

| 6   | AC        | Auxiliary carry:                                                                                                                                  |

|     |           | Set when the previous operation resulted in a carry from the high order nibble.                                                                   |

| 5   | F0        | User flag 0:                                                                                                                                      |

|     |           | The General purpose flag that can be set or cleared by the user.                                                                                  |

| 4   | RS1       | Register bank select bits:                                                                                                                        |

| 3   | RS0       | Register bank select bits:                                                                                                                        |

| 2   | OV        | Overflow flag:                                                                                                                                    |

|     |           | Set when a carry was generated from the seventh bit but not from the 8 <sup>th</sup> bit as a result of the previous operation, or vice-versa.    |

| 1   | F1        | User Flag 1:                                                                                                                                      |

|     |           | The General purpose flag that can be set or cleared by the user by software.                                                                      |

| 0   | Р         | Parity flag:                                                                                                                                      |

|     |           | Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.                                                                    |

| RS1 | RS0 | Register bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00-07h  |

| 0   | 1   | 1             | 08-0Fh  |

| 1   | 0   | 2             | 10-17h  |

| 1   | 1   | 3             | 18-1Fh  |

### DS 1 0. Desister bank calestion bits

#### **PWM COUNTER HIGH BITS REGISTER**

| Bit: | 7                            | 6       | 5                                  | 4 | 3 | 2 | 1      | 0      |  |  |  |

|------|------------------------------|---------|------------------------------------|---|---|---|--------|--------|--|--|--|

|      |                              | -       | -                                  | - | - | - | PWMP.9 | PWMP.8 |  |  |  |

| M    | Mnemonic: PWMPH Address: D1h |         |                                    |   |   |   |        |        |  |  |  |

| BIT  | NAME                         | FUNCT   | UNCTION                            |   |   |   |        |        |  |  |  |

| 7-2  | ¥                            | Reserve | leserved.                          |   |   |   |        |        |  |  |  |

| 1-0  | PWMP.[9:8]                   | The PW  | The PWM Counter Register bits 9~8. |   |   |   |        |        |  |  |  |

### **PWM 0 HIGH BITS REGISTER**

| Bit: | 750        | 6    | 5     | 4 | 3 | 2 | 1      | 0            |

|------|------------|------|-------|---|---|---|--------|--------------|

|      | - 35       | ~11  | 0     | - | - | - | PWM0.9 | PWM0.8       |

| М    | nemonic: P | ₩МОН | 0     |   |   |   | /      | Address: D2h |

| BIT  | NAME       | FUNC | CTION |   |   |   |        |              |

## nuvoTon

| 0 | PCMPIDS.0 | P1.0 digital input disable bit.                              |

|---|-----------|--------------------------------------------------------------|

|   |           | 0: Default (With digital/analog input).                      |

|   |           | 1: Disable Digital Input of Comparator Input 1(Positive end) |

#### **INTERRUPT HIGH PRIORITY 1**

| Bit: | 7           | 6     | 5     | 4     | 3 | 2     | 1 | 0            |

|------|-------------|-------|-------|-------|---|-------|---|--------------|

|      | -           | PBOVH | PPWMH | PWDIH |   | No. S | - | -            |

| Μ    | nemonic: IP | 1H    |       |       |   | Yak   |   | Address: F7h |

| BIT | NAME  | FUNCTION                                                                      |

|-----|-------|-------------------------------------------------------------------------------|

| 7   | -     | Reserved.                                                                     |

| 6   | PBOVH | 1: To set interrupt priority of Brownout interrupt is highest priority level. |

| 5   | PPWMH | 1: To set interrupt priority of PWM underflow is highest priority level.      |

| 4   | PWDIH | 1: To set interrupt high priority of Watchdog is highest priority level.      |

| 3-0 | -     | Reserved.                                                                     |

### **EXTENDED INTERRUPT PRIORITY**

| Bit: | 7 | 6    | 5    | 4    | 3 | 2 | 1 | 0   |

|------|---|------|------|------|---|---|---|-----|

|      | - | PBOV | PPWM | PWDI | - | - | - | - 9 |

| Μ   | nemonic: IP1 | Address: F8h                                                                 |

|-----|--------------|------------------------------------------------------------------------------|

| BIT | NAME         | FUNCTION                                                                     |

| 7   | -            | Reserved.                                                                    |

| 6   | PBOV         | 1: To set interrupt priority of Brownout interrupt is higher priority level. |

| 5   | PPWM         | 1: To set interrupt priority of PWM underflow is higher priority level.      |

| 4   | PWDI         | 1: To set interrupt priority of Watchdog is higher priority level.           |

| 3-0 | -            | Reserved.                                                                    |

## nuvoTon

| Op-code              | HEX Code | Bytes | W79E4051<br>/2051<br>series<br>Machine<br>Cycle | W79E4051<br>/2051<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E4051/205<br>1 series vs.<br>8032 Speed<br>Ratio |

|----------------------|----------|-------|-------------------------------------------------|------------------------------------------------|-------------------------|-----------------------------------------------------|

| CJNE A, direct, rel  | B5       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE A, #data, rel   | B4       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE @R0, #data, rel | B6       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE @R1, #data, rel | B7       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R0, #data, rel  | B8       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R1, #data, rel  | B9       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R2, #data, rel  | BA       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R3, #data, rel  | BB       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R4, #data, rel  | BC       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R5, #data, rel  | BD       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R6, #data, rel  | BE       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R7, #data, rel  | BF       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| DJNZ R0, rel         | D8       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R1, rel         | D9       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R5, rel         | DD       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R2, rel         | DA       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R3, rel         | DB       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R4, rel         | DC       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R6, rel         | DE       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R7, rel         | DF       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ direct, rel     | D5       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

Table 9-1: Instruction Set for W79E4051/2051

- 44 -

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

- 1. An interrupt of equal or higher priority is not currently being serviced.

- 2. The current polling cycle is the last machine cycle of the instruction currently being execute.

- 3. The current instruction does not involve a write to IE, IP and IPH, registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is repeated every machine cycle, with the interrupts sampled in the same machine cycle. If an interrupt flag is active in one cycle but not responded to, and is not active when the above conditions are met, the denied interrupt will not be serviced. This means that active interrupts are not remembered; every polling cycle is new.

The processor responds to a valid interrupt by executing an LCALL instruction to the appropriate service routine. This may or may not clear the flag which caused the interrupt. In case of Timer interrupts, the TF0 or TF1 flags are cleared by hardware whenever the processor vectors to the appropriate timer service routine. In case of external interrupt, INT0 and INT1, the flags are cleared only if they are edge triggered. In case of Serial interrupts, the flags are not cleared by hardware. The hardware LCALL behaves exactly like the software LCALL instruction. This instruction saves the Program Counter contents onto the Stack, but does not save the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the LCALL. These address of vector for the different sources are as follows:

| SOURCE               | VECTOR ADDRESS | SOURCE               | VECTOR ADDRESS |

|----------------------|----------------|----------------------|----------------|

| External Interrupt 0 | 0003h          | Timer 0 Overflow     | 000Bh          |

| External Interrupt 1 | 0013h          | Timer 1 Overflow     | 001Bh          |

| Serial Port          | 0023h          | Brownout Interrupt   | 002Bh          |

| Analog Comparator    | 0033h          | -                    | 003Bh          |

| -                    | 0043h          | -                    | 004Bh          |

| Watchdog Timer       | 0053h          | -                    | 005Bh          |

| -                    | 0063h          | PWM Period Interrupt | 006Bh          |

#### VECTOR LOCATIONS FOR INTERRUPT SOURCES

Table 12-1: Vector locations for interrupt sources

Execution continues from the vectored address till an RETI instruction is executed. On execution of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top of the stack. The user must take care that the status of the stack is restored to what it was after the hardware LCALL, if the execution is return to the interrupted program. The processor does not notice anything if the stack contents are modified and will proceed with execution from the address put back into PC. Note that a RET instruction would perform exactly the same process as a RETI instruction, but it would not inform the Interrupt Controller that the interrupt service routine is completed, and would leave the controller still thinking that the service routine is underway.

### 12.2 Priority Level Structure

The W79E4051/2051 series uses a four priority level interrupt structure (highest, high, low and lowest) and supports up to 9 interrupt sources. The interrupt sources can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as table below. This allows great flexibility in controlling and handling many interrupt sources.

| <b>Priority Bits</b> |     | Interrupt Drievity Lavel   |

|----------------------|-----|----------------------------|

| IPxH                 | IPx | Interrupt Priority Level   |

| 0                    | 0   | Level 0 (lowest priority)  |

| 0                    | 1   | Level 1                    |

| 1                    | 0   | Level 2                    |

| 1                    | 1   | Level 3 (highest priority) |

Table 12-2: Four-level interrupt priority

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the IPx and IPxH registers. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. So, if two requests of different priority levels are received simultaneously, the request of higher priority level is serviced.

If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve simultaneous requests of the same priority level.

As below Table summarizes the interrupt sources, flag bits, vector addresses, enable bits, priority bits, arbitration ranking, and whether each interrupt may wake up the CPU from Power Down mode.

| Source                  | Flag | Vector<br>address | Interrupt<br>Enable Bits | Interrupt<br>Priority | Flag<br>cleared by                                                        | Arbitration<br>Ranking | Power<br>Down<br>Wakeup |

|-------------------------|------|-------------------|--------------------------|-----------------------|---------------------------------------------------------------------------|------------------------|-------------------------|

| External<br>Interrupt 0 | IEO  | 0003Н             | EX0 (IE0.0)              | IP0H.0, IP0.0         | Edge:<br>Hardware,<br>Software;<br>Level:<br>Follow the<br>inverse of pin | 1(highest)             | Yes                     |