Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                                     |

| Core Processor             | 8051                                                                                    |

| Core Size                  | 8-Bit                                                                                   |

| Speed                      | 24MHz                                                                                   |

| Connectivity               | UART/USART                                                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 17                                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 128 x 8                                                                                 |

| RAM Size                   | 256 x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                             |

| Data Converters            | -                                                                                       |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                          |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e4051arg |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### ηυνοτοη

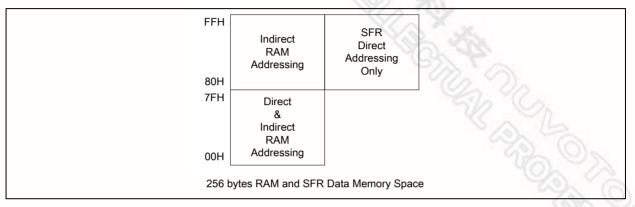

#### 7.3 Scratch-pad RAM and Register Map

As mentioned before the W79E4051/2051 series have separate Program and Data Memory areas. The on-chip **256** bytes scratch pad RAM is built in W79E4051/2051. There are also several Special Function Registers (SFRs) which can be accessed by software. The SFRs can be accessed only by direct addressing, while the on-chip RAM can be accessed by either direct or indirect addressing.

#### Table 7-2 W79E4051/2051 256 bytes RAM and SFR memory map

Since the scratch-pad RAM is **256** bytes it can be used only when data contents are small. There are several other special purpose areas within the scratch-pad RAM. These are illustrated in next figure.

## nuvoTon

#### STACK POINTER 7 6 5 4 2 0 Bit: 3 1 SP.4 SP.7 SP.6 SP.5 SP.3 SP.2 SP.1 SP.0 Mnemonic: SP Address: 81h NAME FUNCTION BIT SP.[7:0] The Stack Pointer stores the Scratch-pad RAM address where the stack begins. In 7-0 other words it always points to the top of the stack. DATA POINTER LOW Bit: 7 6 5 4 3 2 0 1 DPL.7 DPL.6 DPL.5 DPL.4 DPL.3 DPL.2 DPL 1 DPL.0 Mnemonic: DPL Address: 82h BIT NAME **FUNCTION** 7-0 DPL.[7:0] This is the low byte of the standard 8052 16-bit data pointer. DATA POINTER HIGH Bit: 7 6 5 3 2 1 0 4 DPH.7 DPH.6 DPH.5 DPH.4 DPH.3 DPH.2 DPH.1 DPH.0 Mnemonic: DPH Address: 83h NAME FUNCTION BIT 7-0 DPH.[7:0] This is the high byte of the standard 8052 16-bit data pointer. POWER CONTROL Bit: 7 6 5 3 2 1 0 4 POR GF0 PD IDL SMOD SMOD0 \_ GF1 Mnemonic: PCON Address: 87h BIT NAME FUNCTION 7 SMOD 1: This bit doubles the serial port baud rate in mode 1, 2, and 3. 0: Framing Error Detection Disable. SCON.7 (SM0/FE) bit is used as SM0 6 SMOD (standard 8052 function). 0 1: Framing Error Detection Enable. SCON.7 (SM0/FE) bit is used to reflect as Frame Error (FE) status flag. Reserved 5 2 4 POR 0: Cleared by software. 1: Set automatically when a power-on reset has occurred. 3 GF1 General purpose user flags. GF0 2 General purpose user flags. 1 PD 1: The CPU goes into the POWER DOWN mode. In this mode, all the clocks are stopped and program execution is frozen.

| 1 | _    |       | _    | L _  | _    | -    | _    | _    |  |

|---|------|-------|------|------|------|------|------|------|--|

|   | P3.7 | CMP_O | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3.0 |  |

Mnemonic: P3

Address: B0h

P3.7-0: General purpose Input/Output port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. These alternate functions are described below:

| BIT | NAME  | FUNCTION                                                   |

|-----|-------|------------------------------------------------------------|

| 7   | P3.7  |                                                            |

| 6   | CMP_O | Read only. This bit stores the hardware comparator result. |

| 5   | P3.5  | T1 or PWM output                                           |

| 4   | P3.4  | ТО                                                         |

| 3   | P3.3  | INT1                                                       |

| 2   | P3.2  | INTO                                                       |

| 1   | P3.1  | TX                                                         |

| 0   | P3.0  | RX                                                         |

#### Port1 Output Mode 1

| Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|------|---|---|---|---|---|---|--------|--------|

|      | - | - | - | - | - | - | P1M1.1 | P1M1.0 |

|      |   |   |   |   |   |   |        |        |

| M   | Mnemonic: P1M1 |                                          |  |  |  |  |  |

|-----|----------------|------------------------------------------|--|--|--|--|--|

| BIT | NAME           | FUNCTION                                 |  |  |  |  |  |

| 7-2 | Reserved       |                                          |  |  |  |  |  |

| 1   | P1M1.1         | 0: P1.1 is in open drain mode. (Default) |  |  |  |  |  |

|     |                | 1: P1.1 is in Quasi-bidirection mode     |  |  |  |  |  |

| 0   | P1M1.0         | 0: P1.0 is in open drain mode. (Default) |  |  |  |  |  |

|     |                | 1: P1.0 is in Quasi-bidirection mode     |  |  |  |  |  |

#### **Interrupt High Priority 0**

| Bit: | 7 | 6   | 5 | 4   | 3    | 2    | 1    | 0    |

|------|---|-----|---|-----|------|------|------|------|

| S.   | - | PCH | - | PSH | PT1H | PX1H | PT0H | PX0H |

**Mnemonic: IP0H** Address: B7h BIT FUNCTION NAME 7 Reserved \_ 6 PCH 1: To set interrupt high priority of analog comparator is highest priority level. 5 4 Reserved. PSH 4 1: To set interrupt high priority of Serial port 0 is highest priority level. 3 PT1H 1: To set interrupt high priority of Timer 1 is highest priority level. 2 PX1H 1: To set interrupt high priority of External interrupt 1 is highest priority level. PT0H 1: To set interrupt high priority of Timer 0 is highest priority level. 1 PX0H 1: To set interrupt high priority of External interrupt 0 is highest priority level. 0

|     |       | Watchdog Timer Time-out Select bits. These bits determine the time-out period of the watchdog timer. The reset time-out period is 512 clocks longer than the watchdog time-out. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |                                                                                 |            |  |  |  |  |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|------------|--|--|--|--|

| 5~4 |       | WD1                                                                                                                                                                             | WD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Interrupt time-<br>out                              | Reset<br>time-out                                                               |            |  |  |  |  |

| 5~4 |       | 0                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 <sup>17</sup>                                     | 2 <sup>17</sup> + 512                                                           |            |  |  |  |  |

|     |       | 0                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 <sup>20</sup>                                     | 2 <sup>20</sup> + 512                                                           |            |  |  |  |  |

|     |       | 1                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 <sup>23</sup>                                     | 2 <sup>23</sup> + 512                                                           |            |  |  |  |  |

|     |       | 1                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 <sup>26</sup>                                     | 2 <sup>26</sup> + 512                                                           |            |  |  |  |  |

| 3   | WDIF  | elapsed. This<br>1: If the watchdo<br>watchdog inte<br>Watchdog Timer                                                                                                           | bit must be cl<br>g interrupt is o<br>rrupt has occo<br>Reset flag:                                                                                                                                                                                                                                                                                                                                                                                                                 | eared by software.<br>enabled, hardware w<br>urred. | tes that the time-out pe                                                        | e that the |  |  |  |  |

| 2   | WTRF  | 1: Hardware will read it but mu                                                                                                                                                 | set this bit wh<br>st clear it mar                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nually. A power-fail re                             | er causes a reset. Soft<br>set will also clear the b<br>reset. If EWRST = 0, th | oit. This  |  |  |  |  |

|     |       |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | affect on this bit.                                 |                                                                                 | 1          |  |  |  |  |

| 1   | EWRST | 0: Disable Watch<br>1: Enable Watch                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                                                                 | 8          |  |  |  |  |

| 0   | WDCLR | This bit helps in resetting the wat                                                                                                                                             | 1: Enable Watchdog Timer Reset.<br>Reset Watchdog Timer:<br>This bit helps in putting the watchdog timer into a know state. It also helps in<br>resetting the watchdog timer before a time-out occurs. Failing to set the EWRST<br>before time-out will cause an interrupt (if EWDI (EIE.4) is set), and 512 clocks<br>after that a watchdog timer reset will be generated (if EWRST is set). This bit is<br>peter that a watchdog timer reset will be generated (if EWRST is set). |                                                     |                                                                                 |            |  |  |  |  |

The WDCON SFR is set to a 0x000000B on a power-on-reset. WTRF (WDCON.2) is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF (WDCON.2) is not altered by an external reset. EWRST (WDCON.1) is set to 0 on all resets.

All the bits in this SFR have unrestricted read access. WDRUN, EWRST, WDIF and WDCLR require Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

| ТА    | REG      | C7H        |                                 |

|-------|----------|------------|---------------------------------|

| WDCON | REG      | D8H        |                                 |

| MOV   | TA, #AAH |            | ; To access protected bits      |

| MOV   | TA, #55H |            |                                 |

| SETB  | WDCON.0  |            | ; Reset watchdog timer          |

| ORL   | WDCON, # | #00110000B | ; Select 26 bits watchdog timer |

| MOV   | TA, #AAH |            |                                 |

| MOV   | TA, #55H |            |                                 |

| ORL   | WDCON, # | #00000010B | ; Enable watchdog               |

# nuvoTon

#### ACCUMULATOR

| Bit: | 7                         | 6          | 5                                                       | 4     | 3     | 2     | 1     | 0     |  |  |  |

|------|---------------------------|------------|---------------------------------------------------------|-------|-------|-------|-------|-------|--|--|--|

|      | ACC.7                     | ACC.6      | ACC.5                                                   | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |  |  |  |

| N    | Mnemonic: ACC Address: E0 |            |                                                         |       |       |       |       |       |  |  |  |

| Bit  | Name                      | Function   |                                                         |       |       |       |       |       |  |  |  |

| 7-0  | ACC                       | The A or A | The A or ACC register is the standard 8052 accumulator. |       |       |       |       |       |  |  |  |

|      |                           |            |                                                         |       |       | A     |       |       |  |  |  |

#### **INTERRUPT ENABLE REGISTER 1**

| INTER | RUPI ENA    | BLE REGIS  | IER 1                                |              |       |   |      |     |            |  |  |  |

|-------|-------------|------------|--------------------------------------|--------------|-------|---|------|-----|------------|--|--|--|

| Bit:  | 7           | 6          | 5                                    | 4            | 3     | 2 | 1)   | C   | )          |  |  |  |

|       | -           | EBOV EPWN  | EPWM                                 | EWDI         | -     | - | 560  | 6.  |            |  |  |  |

| Μ     | nemonic: El | E          |                                      |              |       |   | NS A | Add | dress: E8h |  |  |  |

| BIT   | NAME        | FUNCTIO    | CTION                                |              |       |   |      |     |            |  |  |  |

| 7     | -           | Reserved   | Reserved.                            |              |       |   |      |     |            |  |  |  |

| 6     | EBOV        | 0: Disable | - No                                 | 2 6          |       |   |      |     |            |  |  |  |

|       |             | 1: Enable  | Brownout ir                          |              |       |   |      | 0 V |            |  |  |  |

| 5     | EPWM        | 0: Disable | 0: Disable PWM underflow interrupt.  |              |       |   |      |     |            |  |  |  |

|       |             | 1: Enable  | PWM unde                             | rflow interr | upt.  |   |      |     | 195        |  |  |  |

| 4     | EWDI        | 0: Disable | 0: Disable Watchdog Timer Interrupt. |              |       |   |      |     |            |  |  |  |

|       |             | 1: Enable  | Watchdog 7                           | Fimer Inter  | rupt. |   |      |     |            |  |  |  |

| 3-0   | -           | Reserved   |                                      |              |       |   |      |     |            |  |  |  |

#### **B REGISTER**

| Bit: | 7                                                                                      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|------|----------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

|      | B.7                                                                                    | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 |  |  |  |

| Μ    | Mnemonic: B Address: F0h                                                               |     |     |     |     |     |     |     |  |  |  |

| Bit  | Bit Name Function                                                                      |     |     |     |     |     |     |     |  |  |  |

| 7-0  | -0 B The B register is the standard 8052 register that serves as a second accumulator. |     |     |     |     |     |     |     |  |  |  |

#### PORT COMPARATOR INPUT DISABLE

| Bit: 7   | 6         | 5 | 4 | 3 | 2 | 1    | 0            |

|----------|-----------|---|---|---|---|------|--------------|

| Sec. as  |           | - | - | - | - | Bit1 | Bit0         |

| Mnemonic | : PCMPIDS | 5 |   |   |   |      | Address: F6h |

| 1   | Unemonic: PCM | 1PIDS                                                        | Address: F6 |

|-----|---------------|--------------------------------------------------------------|-------------|

| Bit | Name          | Function                                                     |             |

| 7-2 | - 50          | Reserved                                                     |             |

| 1   | PCMPIDS.1     | P1.1 digital input disable bit.                              |             |

|     | 63            | 0: Default (With digital/analog input).                      |             |

|     | 6             | 1: Disable Digital Input of Comparator Input 1(Negative end) |             |

|     | 1             |                                                              |             |

#### **11 RESET CONDITIONS**

The user has several hardware related options for placing the W79E4051/2051 series into reset condition. In general, most register bits go to their reset value irrespective of the reset condition, but there are a few flags whose state depends on the source of reset. The user can use these flags to determine the cause of reset using software.

#### 11.1 Sources of reset

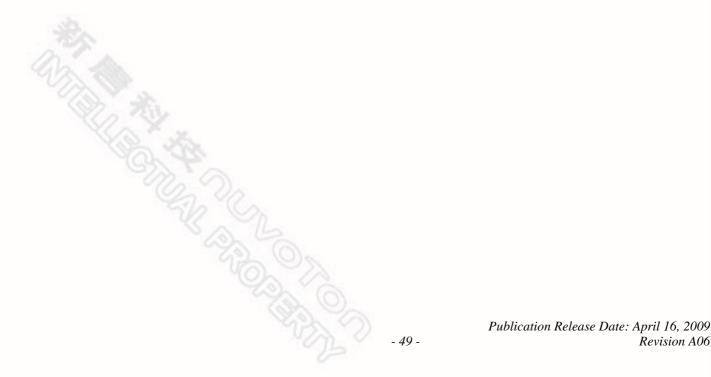

#### 11.1.1 External Reset

The device samples the RST pin every machine cycle during state C4. The RST pin must be held high for at least two machine cycles before the reset circuitry applies an internal reset signal. Thus, this reset is a synchronous operation and requires the clock to be running.

The device remains in the reset state as long as RST pin is high and remains high up to two machine cycles after RST is deactivated. Then, the device begins program execution at 0000h. There are no flags associated with the external reset, but, since the other two reset sources do have flags, the external reset is the cause if those flags are clear.

#### 11.1.2 Power-On Reset (POR)

If the power supply falls below  $V_{RST}$ , the device goes into the reset state. When the power supply returns to proper levels, the device performs a power-on reset and sets the POR flag. The software should clear the POR flag, or it will be difficult to determine the source of future resets.  $V_{RST}$  is about 2.0V.

#### 11.1.3 Brown-Out Reset (BOR)

If the power supply falls below brownout voltage of  $V_{BOV}$ , the device goes into the reset state. When the power supply returns to proper levels, the device performs a brownout reset.

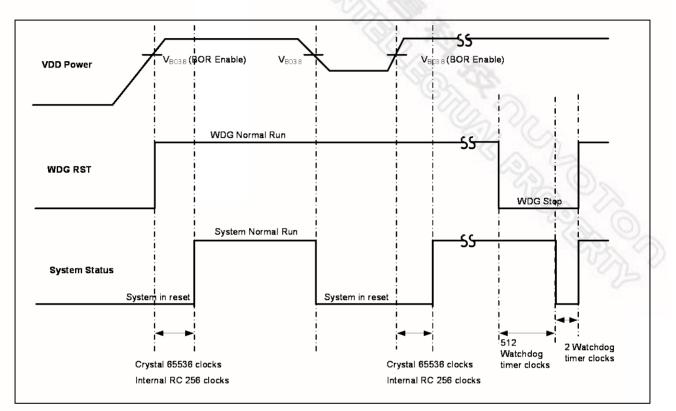

#### 11.1.4 Watchdog Timer Reset

The Watchdog Timer is a free-running timer with programmable time-out intervals. The program must clear the Watchdog Timer before the time-out interval is reached to restart the count. If the time-out interval is reached, an interrupt flag is set. 512 clocks later, if the Watchdog Reset is enabled and the Watchdog Timer has not been cleared, the Watchdog Timer generates a reset. The reset condition is maintained by the hardware for two machine cycles, and the WTRF bit in WDCON is set. Afterwards, the device begins program execution at 0000h.

#### 11.2 Reset State

When the device is reset, most registers return to their initial state. The Watchdog Timer is disabled if the reset source was a power-on reset. The port registers are set to FFh, which puts most of the port pins in a high state. The Program Counter is set to 0000h, and the stack pointer is reset to 07h. After this, the device remains in the reset state as long as the reset conditions are satisfied.

Reset does not affect the on-chip RAM, however, so RAM is preserved as long as VDD remains above approximately 2V, the minimum operating voltage for the RAM. If VDD falls below 2V, the RAM contents are also lost. In either case, the stack pointer is always reset, so the stack contents are lost.

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset. The WDCON SFR is set to a 0x00 0000B on the reset. WTRF (WDCON.2) is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF (WDCON.2) is not altered by external reset. EWRST (WDCON.1) is cleared by any reset. Software or any reset will clear WDIF (WDCON.3) bit.

Some of the bits in the WDCON SFR (WDRUN, WDCLR, EWRST, WDIF, WD0 and WD1) have unrestricted read access which required Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

Figure 11-1: Internal reset and VDD monitor timing diagram

Revision A06

## nuvoTon

Figure 11-2: External reset timing diagram

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

- 1. An interrupt of equal or higher priority is not currently being serviced.

- 2. The current polling cycle is the last machine cycle of the instruction currently being execute.

- 3. The current instruction does not involve a write to IE, IP and IPH, registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is repeated every machine cycle, with the interrupts sampled in the same machine cycle. If an interrupt flag is active in one cycle but not responded to, and is not active when the above conditions are met, the denied interrupt will not be serviced. This means that active interrupts are not remembered; every polling cycle is new.

The processor responds to a valid interrupt by executing an LCALL instruction to the appropriate service routine. This may or may not clear the flag which caused the interrupt. In case of Timer interrupts, the TF0 or TF1 flags are cleared by hardware whenever the processor vectors to the appropriate timer service routine. In case of external interrupt, INT0 and INT1, the flags are cleared only if they are edge triggered. In case of Serial interrupts, the flags are not cleared by hardware. The hardware LCALL behaves exactly like the software LCALL instruction. This instruction saves the Program Counter contents onto the Stack, but does not save the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the LCALL. These address of vector for the different sources are as follows:

| SOURCE               | VECTOR ADDRESS | SOURCE               | VECTOR ADDRESS |

|----------------------|----------------|----------------------|----------------|

| External Interrupt 0 | 0003h          | Timer 0 Overflow     | 000Bh          |

| External Interrupt 1 | 0013h          | Timer 1 Overflow     | 001Bh          |

| Serial Port          | 0023h          | Brownout Interrupt   | 002Bh          |

| Analog Comparator    | 0033h          | -                    | 003Bh          |

| -                    | 0043h          | -                    | 004Bh          |

| Watchdog Timer       | 0053h          | -                    | 005Bh          |

| -                    | 0063h          | PWM Period Interrupt | 006Bh          |

#### VECTOR LOCATIONS FOR INTERRUPT SOURCES

Table 12-1: Vector locations for interrupt sources

Execution continues from the vectored address till an RETI instruction is executed. On execution of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top of the stack. The user must take care that the status of the stack is restored to what it was after the hardware LCALL, if the execution is return to the interrupted program. The processor does not notice anything if the stack contents are modified and will proceed with execution from the address put back into PC. Note that a RET instruction would perform exactly the same process as a RETI instruction, but it would not inform the Interrupt Controller that the interrupt service routine is completed, and would leave the controller still thinking that the service routine is underway.

#### 12.2 Priority Level Structure

| Source                   | Flag    | Vector<br>address | Interrupt<br>Enable Bits | Interrupt<br>Priority | Flag<br>cleared by        | Arbitration<br>Ranking | Power<br>Down<br>Wakeup |

|--------------------------|---------|-------------------|--------------------------|-----------------------|---------------------------|------------------------|-------------------------|

|                          |         |                   |                          | 9b                    | Follow the inverse of pin |                        |                         |

| Timer 1<br>Interrupt     | TF1     | 001BH             | ET1 (IE.3)               | IP0H.3, IP0.3         | Hardware,<br>Software     | 6                      | No                      |

| Serial Port Tx<br>and Rx | TI & RI | 0023H             | ES (IE.4)                | IP0H.4, IP0.4         | Software                  | 7                      | No                      |

| Comparator<br>Interrupt  | CF      | 0033H             | EC (IE.6)                | IP0H.6, IP0.6         | Software                  | 8                      | Yes <sup>(2)</sup>      |

| PWM Period<br>Interrupt  | PWMF    | 006BH             | EPWM (EIE.5)             | IP1H.5, IP1.5         | Software                  | 9(lowest)              | No                      |

Table 12-3: Vector location for Interrupt sources and power down wakeup

Note:

1. The Watchdog Timer can wake up Power Down Mode when its clock source is from internal RC.

2. The comparator can wake up Power Down Mode when bit ACSR.5(CIPE) is set to high.

#### 12.3 Response Time

The response time for each interrupt source depends on several factors, such as the nature of the

interrupt and the instruction underway. In the case of external interrupts INT0 to RI+TI, they are sampled at C3 of every machine cycle and then their corresponding interrupt flags IEx will be set or reset. The Timer 0 and 1 overflow flags are set at C3 of the machine cycle in which overflow has occurred. These flag values are polled only in the next machine cycle. If a request is active and all three conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes four machine cycles to be completed. Thus there is a minimum time of five machine cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the service routine currently being executed. If the polling cycle is not the last machine cycle of the instruction being executed, then an additional delay is introduced. The maximum response time (if no other interrupt is in service) occurs if the W79E4051/2051 series are performing a write to IE, IP and IPH and then executes a MUL or DIV instruction. From the time an interrupt source is activated, the longest reaction time is 12 machine cycles. This includes 1 machine cycle to detect the interrupt, 2 machine cycles to complete the IE, IP or IPH access, 5 machine cycles to complete the MUL or DIV instruction.

Thus in a single-interrupt system the interrupt response time will always be more than 5 machine cycles and not more than 12 machine cycles. The maximum latency of 12 machine cycles is 48 clock cycles. Note that in the standard 8051 the maximum latency is 8 machine cycles which equals 96 machine cycles. This is a 50% reduction in terms of clock periods.

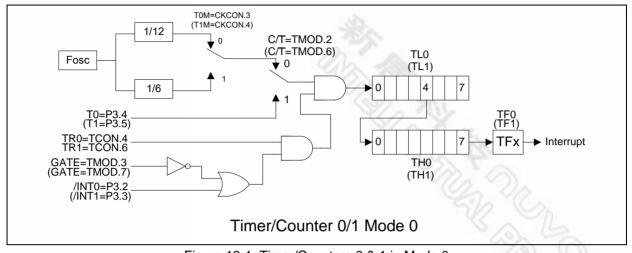

Figure 13-1: Timer/Counters 0 & 1 in Mode 0

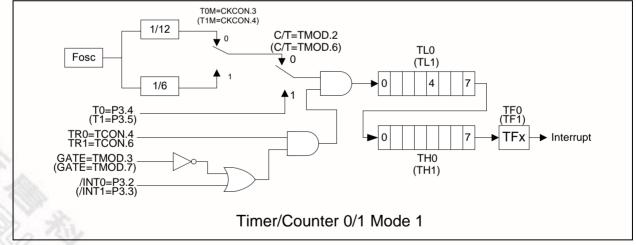

#### 13.2.2 Mode 1

Mode 1 is similar to Mode 0 except that the counting register forms a 16-bit counter, rather than a 13bit counter. This means that all the bits of THx and TLx are used. Roll-over occurs when the timer moves from a count of FFFFh to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupt will occur. The selection of the time-base in the timer mode is similar to that in Mode 0. The gate function operates similarly to that in Mode 0.

Figure 13-2: Timer/Counters 0 & 1 in Mode 1

#### 13.2.3 Mode 2

In Mode 2, the timer/counter is in the Auto Reload Mode. In this mode, TLx acts as an 8-bit count register, while THx holds the reload value. When the TLx register overflows from FFh to 00h, the TFx bit in TCON is set and TLx is reloaded with the contents of THx, and the counting process continues from here. The reload operation leaves the contents of the THx register unchanged. Counting is

enabled by the TRx bit and proper setting of GATE and INTx pins. As in the other two modes 0 and 1 mode 2 allows counting of either clock cycles (clock/12 or clock/6) or pulses on pin Tn.

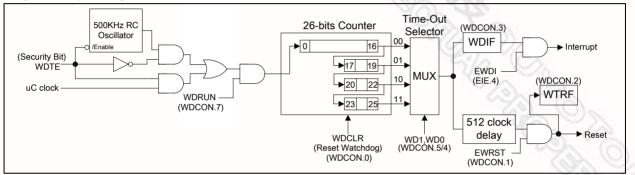

#### **15 WATCHDOG TIMER**

The Watchdog Timer is a free-running Timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval. When the time-out occurs a flag is set, which can cause an interrupt if enabled, and a system reset can also be caused if it is enabled. The interrupt will occur if the individual interrupt enable and the global enable are set. The interrupt and reset functions are independent of each other and may be used separately or together depending on the user's software.

Figure 15-1: Watchdog Timer

The Watchdog Timer should first be restarted by using WDCLR. This ensures that the timer starts from a known state. The WDCLR bit is used to restart the Watchdog Timer. This bit is self clearing, i.e. after writing a 1 to this bit the software will automatically clear it. The Watchdog Timer will now count clock cycles. The time-out interval is selected by the two bits WD1 and WD0 (WDCON.5 and WDCON.4). When the selected time-out occurs, the Watchdog interrupt flag WDIF (WDCON.3) is set. After the time-out has occurred, the Watchdog Timer waits for an additional 512 WDT clock cycles. If the Watchdog Reset EWRST (WDCON.1) is enabled, then 512 clocks after the time-out, if there is no WDCLR, a system reset due to Watchdog Timer will occur. This will last for two machine cycles, and the Watchdog Timer reset flag WTRF (WDCON.2) will be set. This indicates to the software that the Watchdog was the cause of the reset.

When used as a simple timer, the reset and interrupt functions are disabled. The timer will set the WDIF flag each time the timer completes the selected time interval. The WDIF flag is polled to detect a time-out and the WDCLR allows software to restart the timer. The Watchdog Timer can also be used as a very long timer. The interrupt feature is enabled in this case. Every time the time-out occurs an interrupt will occur if the global interrupt enable EA is set.

The main use of the Watchdog Timer is as a system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash. Using the watchdog timer interrupt during software development will allow the user to select ideal watchdog reset locations. The code is first written without the watchdog interrupt or reset. Then the Watchdog interrupt is enabled to identify code locations where interrupt occurs. The user can now insert instructions to reset the Watchdog Timer, which will allow the code to run without any Watchdog Timer interrupts. Now the Watchdog Timer reset is enabled and the Watchdog interrupt may be disabled. If any errant code is executed now, then the reset Watchdog Timer instructions will not be executed at the required instants and Watchdog reset will occur.

The Watchdog Timer time-out selection will result in different time-out values depending on the clock

WDCLR bit is set, to reset it, the counter must be non-zero. Since the counter is running off a much slower clock, the counter may not have time to increment before the CPU clock halts as it entered the idle/power-down mode. This results in the WDCLR bit is always set & the watchdog counter remaining at zero. The solution to this problem is to monitor the WDCLR bit, ensuring that it's cleared before issue the instruction for the CPU to go into idle/power-down mode.

Publication Release Date: April 16, 2009 Revision A06

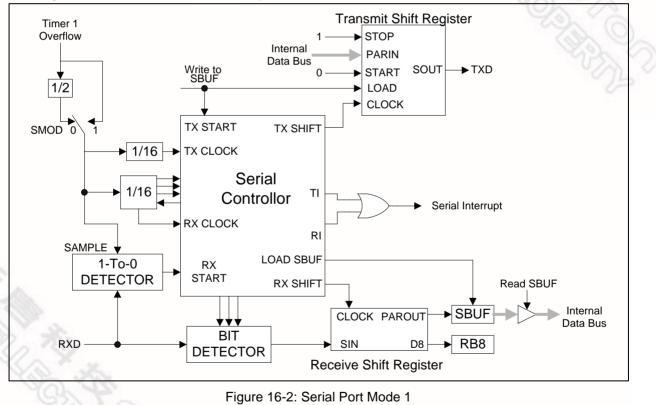

The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three bases. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port. If the first bit detected after the falling edge of RxD pin is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF.

After shifting in 8 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

## nuvoton

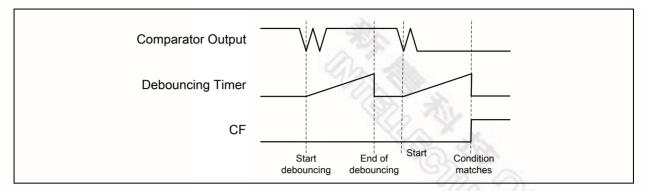

Figure 18-2: Example of Negative Edge Comparator Interrupt with Debouncing

#### **18.2 Application circuit**

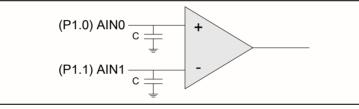

It is recommended to add a decoupled capacitor as close as port pin for reducing the variation of offset voltage as show in Figure 18-3.

Figure 18-3: Application Circuit of Comparator

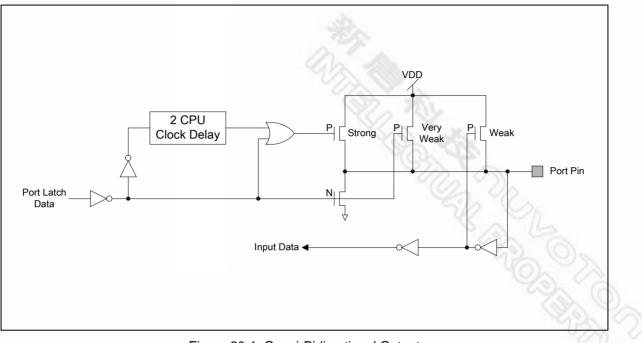

Figure 20-1: Quasi-Bidirectional Output

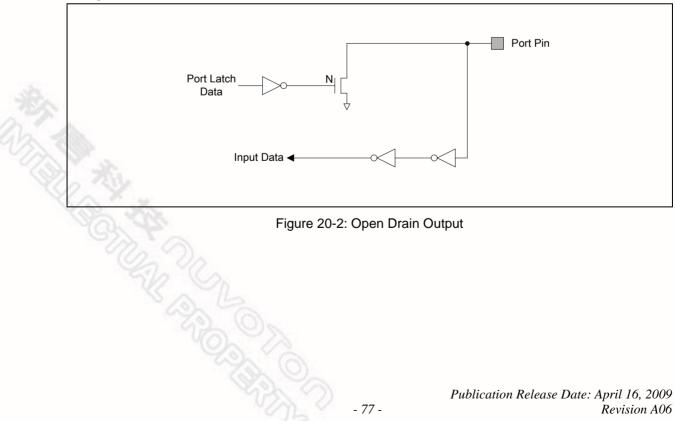

#### 20.2 Open Drain Output Configuration

P1.0 and P1.1 are in open drain type after chip reset. To configure this mode is turned off all pull-ups. If used similar as a logic output, the port must has an external pull-up resister. The open drain port configuration is shown as below.

## nuvoTon

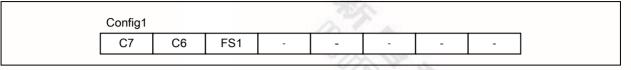

#### 24.2 CONFIG1

#### Figure 24-2: Config1 register bits

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | C7   | 4K/2K Program Flash EPROM Lock bit<br>This bit is used to protect the customer's program code. It may be set after the programmer<br>finishes the programming and verifies sequence. Once this bit is set to logic 0, both the Flash<br>EPROM data and CONFIG Registers can not be accessed again.                        |

| 6   | C6   | 128 byte Data Flash EPROM Lock bit<br>This bit is used to protect the customer's 128 bytes of data code. It may be set after the<br>programmer finishes the programming and verifies sequence. Once this bit is set to logic 0,<br>both the 128 bytes of Flash EPROM data and CONFIG Registers can not be accessed again. |

| 5   | FS1  | Internal Oscillator 11MHz/22MHz selection bit<br>This bit is used to select 11MHz or 22MHz internal oscillator.<br>1: Internal oscillator is set to 22MHz<br>0: Internal oscillator is set to 11MHz                                                                                                                       |

| 0~4 | -    | Reserved.                                                                                                                                                                                                                                                                                                                 |

#### Lock bits C7 and C6:

| Bit 7 | Bit 6   | Function Description                                                                                                                                            |  |  |  |  |  |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1     | 1       | Both security of <b>4K/2KB</b> program code and <b>128</b> Bytes data area are not locked. They can be erased, programmed or read by Writer or ICP.             |  |  |  |  |  |

| 0     | 1       | The <b>4K/2KB</b> program code area is locked. It can not be read and written by Writer or ICP. The <b>128</b> Bytes data area can be program one time or read. |  |  |  |  |  |

| 1     | 0       | Not supported.                                                                                                                                                  |  |  |  |  |  |

| 0     | 0       | Both security of <b>4K/2KB</b> program code and <b>128</b> Bytes data area are locked. They car                                                                 |  |  |  |  |  |

|       |         | not be read and written by Writer or ICP.                                                                                                                       |  |  |  |  |  |

|       |         | not be read and written by Writer or ICP.                                                                                                                       |  |  |  |  |  |

|       | A ANDER | not be read and written by Writer or ICP.                                                                                                                       |  |  |  |  |  |

### **25 ELECTRICAL CHARACTERISTICS**

### 25.1 Absolute Maximum Ratings

| SYMBOL                                                                        | PARAMETER        | CONDITION                        | MINIMUM              | MAXIMUM              | UNIT |

|-------------------------------------------------------------------------------|------------------|----------------------------------|----------------------|----------------------|------|

| DC Power Supply                                                               | V <sub>DD</sub>  | V <sub>DD</sub> -V <sub>SS</sub> | -0.3                 | +7.0                 | V    |

| Input Voltage                                                                 | V <sub>IN</sub>  |                                  | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Operating Temperature                                                         | TA               |                                  | -40                  | +85                  | °C   |

| Storage Temperature                                                           | Tst              |                                  | -55                  | +150                 | °C   |

| Sink current                                                                  | ISK              |                                  | - 9                  | 95                   | mA   |

| RAM Keep Alive<br>Voltage                                                     | V <sub>RAM</sub> |                                  | 1.4                  | +7.0                 | V    |

| Maximum Current into V <sub>DD</sub>                                          |                  | -                                |                      | 120                  | mA   |

| $\begin{array}{c} \text{Maximum Current out of} \\ V_{\text{SS}} \end{array}$ |                  |                                  |                      | 120                  | mA   |

| Maximum Current suck by a I/O pin                                             |                  |                                  |                      | 25                   | mA   |

| Maximum Current sourced by a I/O pin                                          |                  |                                  |                      | 25                   | mA   |

| Maximum Current suck by total I/O pins                                        |                  |                                  |                      | 80                   | mA   |

| Maximum Current sourced by total I/O pins                                     |                  |                                  |                      | 80                   | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability

- 84 -

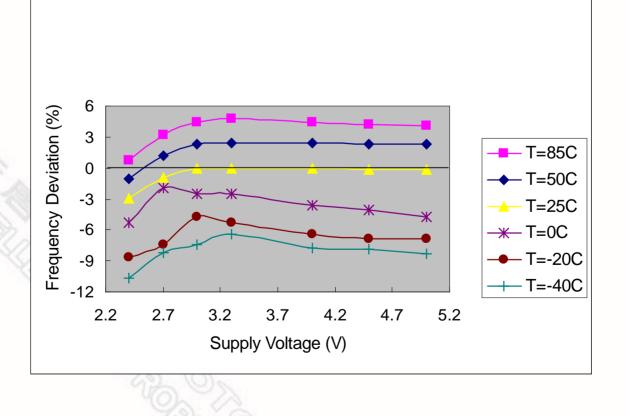

#### 25.6 RC OSC AND AC CHARACTERISTICS

(VDD-VSS = 2.4~5V, TA = -40~85°C.)

| Parameter                                                                                     | Specification (reference) |      |      |      | Test Conditions                              |

|-----------------------------------------------------------------------------------------------|---------------------------|------|------|------|----------------------------------------------|

|                                                                                               | Min.                      | Тур. | Max. | Unit |                                              |

| W79E2051/W79E4051<br>Frequency accuracy of On-<br>chip RC oscillator<br>(Without calibration) | -25                       |      | 25   | %    | V <sub>DD</sub> =2.4V~5.5V, TA = -40°C ~85°C |

| W79E2051R/W79E4051R                                                                           | -2                        |      | 2    | %    | V <sub>DD</sub> =5.0V, TA = 25°C             |

| On-chip RC oscillator with calibration <sup>1,2</sup>                                         | -5                        |      | 5    | %    | V <sub>DD</sub> =2.7V~5.5V, TA = 0~85°C      |

| (Fosc = 22.1184MHz with                                                                       | -7                        |      | 7    | %    | V <sub>DD</sub> =2.7V~5.5V, TA = -20~85°C    |

| factory calibration)                                                                          | -9                        |      | 7    | %    | V <sub>DD</sub> =2.7V~5.5V, TA = -40~85°C    |

| Wakeup time                                                                                   |                           | 256  |      | clk  | 92.12                                        |

Note:

- 1. These values are for design guidance only and are not tested.

- 2. RC frequency deviation vs.  $V_{\text{DD}}$  and Temperature is shown below

Publication Release Date: April 16, 2009 Revision A06

## nuvoTon

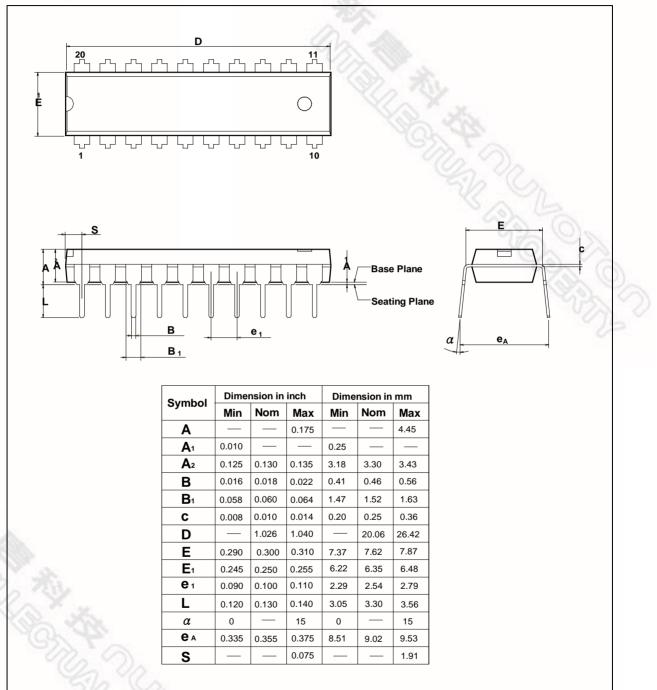

#### 27.2 20-pin DIP

Figure 27-2: 20L DIP-300mil