Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decalis                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 24MHz                                                                                    |

| Connectivity               | UART/USART                                                                               |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                          |

| Number of I/O              | 17                                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                                             |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | 128 x 8                                                                                  |

| RAM Size                   | 256 x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                           |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e4051rasg |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

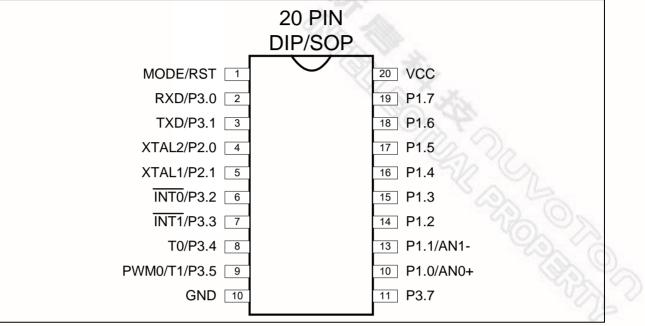

### **4 PIN CONFIGURATION**

Table 4-1: Pin Configuration

Table 6-1: Data Pointer

### 6.7 Architecture

The W79E4051/2051 is based on the standard MCS-51 device. It is built around an 8-bit ALU that uses internal registers for temporary storage and control of the peripheral devices. It can execute the standard MCS-51 instruction set.

### 6.7.1 ALU

The ALU is the heart of the W79E4051/2051. It is responsible for the arithmetic and logical functions. It is also used in decision making, in case of jump instructions, and is also used in calculating jump address. The user cannot directly use the ALU, but the Instruction Decoder reads the op-code, decodes it, and sequences the data through the ALU and its associated registers to generate the required result. The ALU mainly uses the ACC which is a special function register (SFR) on the chip. Another SFR, namely B register is also used in Multiply and Divide instructions. The ALU generates several status signals which are stored in the Program Status Word register (PSW).

### 6.7.2 Accumulator

The Accumulator (ACC) is the primary register used in arithmetic, logical and data transfer operations in the W79E4051/2051. Since the Accumulator is directly accessible by the CPU, most of the high speed instructions make use of the ACC as one argument.

### 6.7.3 B Register

This is an 8-bit register that is used as the second argument in the MUL and DIV instructions. For all other instructions it can be used simply as a general purpose register.

### 6.7.4 Program Status Word:

This is an 8-bit SFR that is used to store the status bits of the ALU. It holds the Carry flag, the Auxiliary Carry flag, General purpose flags, the Register Bank Select, the Overflow flag, and the Parity flag.

### 6.7.5 Scratch-pad RAM

The W79E4051/2051 has a 256 byte on-chip scratch-pad RAM. This can be used by the user for temporary storage during program execution. A certain section of this RAM is bit addressable, and can be directly addressed for this purpose.

### 6.7.6 Stack Pointer

The W79E4051/2051 has an 8-bit Stack Pointer which points to the top of the Stack. This stack resides in the Scratch Pad RAM in the W79E4051/2051. Hence the size of the stack is limited by the size of this RAM.

- 11 -

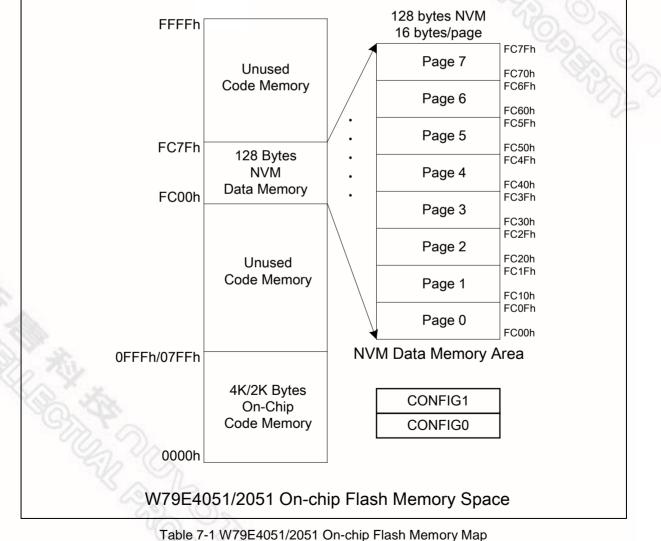

### 7 MEMORY ORGANIZATION

The W79E4051/2051 series separate the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

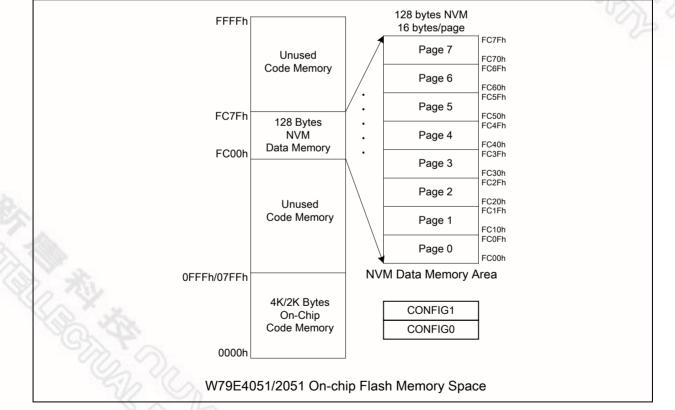

### 7.1 Program Memory (on-chip Flash)

The Program Memory on the W79E4051/2051 series can be up to **4K/2K** bytes long. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region.

### 7.2 Data Flash Memory

The Data Flash EPROM on the W79E4051/2051 series is **128** bytes long with page size of **16** bytes. The W79E4051/2051 series read the content of data memory by using "MOVC A, @A+DPTR". To write data is by NVMADDRL, NVMDATA and NVMCON SFR's registers.

# nuvoTon

### TIMED ACCESS

| Bit: | 7           | 6                       | 5                            | 4                             | 3                        | 2                           | 1    | 0                          |

|------|-------------|-------------------------|------------------------------|-------------------------------|--------------------------|-----------------------------|------|----------------------------|

|      | TA.7        | TA.6                    | TA.5                         | TA.4                          | TA.3                     | TA.2                        | TA.1 | TA.0                       |

| М    | nemonic: TA | ł                       |                              |                               | VAN                      |                             |      | Address: C7h               |

| BIT  | NAME        | FUNCTIO                 | FUNCTION                     |                               |                          |                             |      |                            |

| 7-0  | TA.[7:0]    | The Time                | d Access re                  | egister:                      | N.                       | 2. 3                        |      |                            |

|      |             | protected<br>followed b | bits, the us<br>by a write o | er must first<br>f 55H to TA. | t write AAH<br>Now a win | to the TA. T<br>dow is oper |      | e immediately otected bits |

### **NVM CONTROL**

| Bit: | 7          | 6     | 5 | 4 | 3 | 2 | 1 20 | 00          |

|------|------------|-------|---|---|---|---|------|-------------|

|      | EER        | EWR   | - | - | - | - | - 6  |             |

| Μ    | nemonic: N | /MCON |   |   |   |   | A    | ddress: CEh |

### Mnemonic: NVMCON

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EER  | NVM page(n) erase bit:                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |      | 0: Without erase NVM page(n).                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      | 1: Set this bit to erase page(n) of NVM. The NVM has 8 pages and each page<br>have 16 bytes data memory. Initiate page select by programming NVMADDRL<br>registers, which will automaticly enable page area. When user set this bit, the<br>page erase process will begin and program counter will halt at this instruction.<br>After the erase process is completed, program counter will continue executing<br>next instruction. |

| 6   | EWR  | NVM data write bit:                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |      | 0: Without write NVM data.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |      | 1: Set this bit to write NVM bytes and program counter will halt at this instruction.<br>After write is finished, program counter will kept next instruction then executed.                                                                                                                                                                                                                                                        |

| 5-0 | -    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                          |

### NVM DATA

| Bit: | 7                              | 6             | 5                                                                      | 4             | 3            | 2             | 1             | 0             |

|------|--------------------------------|---------------|------------------------------------------------------------------------|---------------|--------------|---------------|---------------|---------------|

|      | NVMDAT<br>A.7                  | NVMDAT<br>A.6 | NVMDAT<br>A.5                                                          | NVMDAT<br>A.4 | NVMDAT<br>A3 | NVMDAT<br>A.2 | NVMDAT<br>A.1 | NVMDAT<br>A.0 |

| М    | Mnemonic: NVMDATA Address: CFh |               |                                                                        |               |              |               |               | ddress: CFh   |

| BIT  | NAME                           | FUN           | FUNCTION                                                               |               |              |               |               |               |

| 7~0  | NVMDATA                        | [7:0] The     | The NVM data write register. The read NVM data is by MOVC instruction. |               |              |               |               |               |

### PROGRAM STATUS WORD

| Bit: | 7     | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|------|-------|----|----|-----|-----|----|----|---|

|      | CY    | AC | F0 | RS1 | RS0 | OV | F1 | Р |

|      | - · · |    | 0) |     |     |    |    | - |

| Ν   | Inemonic: | PSW Address: D0h                                                                                                                                  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | NAME      | FUNCTION                                                                                                                                          |

| 7   | CY        | Carry flag:                                                                                                                                       |

|     |           | Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations. |

| 6   | AC        | Auxiliary carry:                                                                                                                                  |

|     |           | Set when the previous operation resulted in a carry from the high order nibble.                                                                   |

| 5   | F0        | User flag 0:                                                                                                                                      |

|     |           | The General purpose flag that can be set or cleared by the user.                                                                                  |

| 4   | RS1       | Register bank select bits:                                                                                                                        |

| 3   | RS0       | Register bank select bits:                                                                                                                        |

| 2   | OV        | Overflow flag:                                                                                                                                    |

|     |           | Set when a carry was generated from the seventh bit but not from the 8 <sup>th</sup> bit as a result of the previous operation, or vice-versa.    |

| 1   | F1        | User Flag 1:                                                                                                                                      |

|     |           | The General purpose flag that can be set or cleared by the user by software.                                                                      |

| 0   | Р         | Parity flag:                                                                                                                                      |

|     |           | Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.                                                                    |

| RS1 | RS0 | Register bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00-07h  |

| 0   | 1   | 1             | 08-0Fh  |

| 1   | 0   | 2             | 10-17h  |

| 1   | 1   | 3             | 18-1Fh  |

### DS 1 0. Desister bank calestion bits

#### **PWM COUNTER HIGH BITS REGISTER**

| Bit: | 7            | 6                 | 5                                  | 4 | 3 | 2 | 1      | 0      |

|------|--------------|-------------------|------------------------------------|---|---|---|--------|--------|

|      |              | -                 | -                                  | - | - | - | PWMP.9 | PWMP.8 |

| M    | Inemonic: PW | WMPH Address: D1h |                                    |   |   |   |        |        |

| BIT  | NAME         | FUNCT             | UNCTION                            |   |   |   |        |        |

| 7-2  | ¥            | Reserve           | Reserved.                          |   |   |   |        |        |

| 1-0  | PWMP.[9:8]   | The PW            | The PWM Counter Register bits 9~8. |   |   |   |        |        |

### **PWM 0 HIGH BITS REGISTER**

| Bit: | 750        | 6    | 5     | 4 | 3 | 2 | 1      | 0            |

|------|------------|------|-------|---|---|---|--------|--------------|

|      | - 35       | ~11  | 0     | - | - | - | PWM0.9 | PWM0.8       |

| М    | nemonic: P | ₩МОН | 0     |   |   |   | /      | Address: D2h |

| BIT  | NAME       | FUNC | CTION |   |   |   |        |              |

|     |             |                                                                                                                           | er. The reset                                                                                                                                                                                                                                                                                                                                                                                             |                         | etermine the time-out p<br>2 clocks longer than th                              |           |  |  |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-----------|--|--|

| 5 / | 5~4 WD1~WD0 | WD1                                                                                                                       | WD0                                                                                                                                                                                                                                                                                                                                                                                                       | Interrupt time-<br>out  | Reset<br>time-out                                                               |           |  |  |

| 5~4 |             | 0                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                         | 2 <sup>17</sup>         | 2 <sup>17</sup> + 512                                                           |           |  |  |

|     |             | 0                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                         | 2 <sup>20</sup>         | 2 <sup>20</sup> + 512                                                           |           |  |  |

|     |             | 1                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                         | 2 <sup>23</sup>         | 2 <sup>23</sup> + 512                                                           |           |  |  |

|     |             | 1                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                         | 2 <sup>26</sup>         | 2 <sup>26</sup> + 512                                                           |           |  |  |

| 3   | WDIF        | elapsed. This<br>1: If the watchdo<br>watchdog inte<br>Watchdog Timer                                                     | <ul> <li>0: If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed. This bit must be cleared by software.</li> <li>1: If the watchdog interrupt is enabled, hardware will set this bit to indicate that th watchdog interrupt has occurred.</li> <li>Watchdog Timer Reset flag:</li> </ul>                                                                         |                         |                                                                                 |           |  |  |

| 2   | WTRF        | 1: Hardware will read it but mu                                                                                           | set this bit wh<br>st clear it mar                                                                                                                                                                                                                                                                                                                                                                        | nually. A power-fail re | er causes a reset. Soft<br>set will also clear the b<br>reset. If EWRST = 0. th | oit. This |  |  |

|     |             | bit helps software in determining the cause of a reset. If EWRST = 0, the watchdog timer will have no affect on this bit. |                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                                                                                 |           |  |  |

| 1   | EWRST       | 0: Disable Watch<br>1: Enable Watch                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                         |                         |                                                                                 | 8         |  |  |

| 0   | WDCLR       | This bit helps in resetting the wat                                                                                       | 1: Enable Watchdog Timer Reset.<br>Reset Watchdog Timer:<br>This bit helps in putting the watchdog timer into a know state. It also helps in<br>resetting the watchdog timer before a time-out occurs. Failing to set the EWRST<br>before time-out will cause an interrupt (if EWDI (EIE.4) is set), and 512 clocks<br>after that a watchdog timer reset will be generated (if EWRST is set). This bit is |                         |                                                                                 |           |  |  |

The WDCON SFR is set to a 0x000000B on a power-on-reset. WTRF (WDCON.2) is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF (WDCON.2) is not altered by an external reset. EWRST (WDCON.1) is set to 0 on all resets.

All the bits in this SFR have unrestricted read access. WDRUN, EWRST, WDIF and WDCLR require Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

| ТА    | REG      | C7H        |                                 |

|-------|----------|------------|---------------------------------|

| WDCON | REG      | D8H        |                                 |

| MOV   | TA, #AAH |            | ; To access protected bits      |

| MOV   | TA, #55H |            |                                 |

| SETB  | WDCON.0  |            | ; Reset watchdog timer          |

| ORL   | WDCON, # | #00110000B | ; Select 26 bits watchdog timer |

| MOV   | TA, #AAH |            |                                 |

| MOV   | TA, #55H |            |                                 |

| ORL   | WDCON, # | #00000010B | ; Enable watchdog               |

# ηυνοτοη

| Op-code        | HEX Code | Bytes | W79E4051<br>/2051<br>series<br>Machine<br>Cycle | W79E4051<br>/2051<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E4051/205<br>1 series vs.<br>8032 Speed<br>Ratio |

|----------------|----------|-------|-------------------------------------------------|------------------------------------------------|-------------------------|-----------------------------------------------------|

| ADDC A, @R1    | 37       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| ADDC A, direct | 35       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| ADDC A, #data  | 34       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| SUBB A, R0     | 98       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R1     | 99       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R2     | 9A       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R3     | 9B       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R4     | 9C       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R5     | 9D       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R6     | 9E       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, R7     | 9F       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, @R0    | 96       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, @R1    | 97       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SUBB A, direct | 95       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| SUBB A, #data  | 94       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| INC A          | 04       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R0         | 08       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R1         | 09       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R2         | 0A       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R3         | 0B       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R4         | 0C       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R5         | 0D       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R6         | 0E       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC R7         | 0F       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC @R0        | 06       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC @R1        | 07       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| INC direct     | 05       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| INC DPTR       | A3       | 1     | 2                                               | 8                                              | 24                      | 3                                                   |

| DEC A          | 14       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| DEC R0         | 18       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| DEC R1         | 19       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| DEC R2         | 1A       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| DEC R3         | 1B       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| DEC R4         | 1C       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

# ηυνοτοη

| Op-code           | HEX Code | Bytes | W79E4051<br>/2051<br>series<br>Machine<br>Cycle | W79E4051<br>/2051<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E4051/205<br>1 series vs.<br>8032 Speed<br>Ratio |

|-------------------|----------|-------|-------------------------------------------------|------------------------------------------------|-------------------------|-----------------------------------------------------|

| ORL A, direct     | 45       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| ORL A, #data      | 44       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| ORL direct, A     | 42       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| ORL direct, #data | 43       | 3     | 3                                               | 12                                             | 24                      | 2                                                   |

| XRL A, R0         | 68       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R1         | 69       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R2         | 6A       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R3         | 6B       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R4         | 6C       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R5         | 6D       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R6         | 6E       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, R7         | 6F       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, @R0        | 66       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, @R1        | 67       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| XRL A, direct     | 65       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| XRL A, #data      | 64       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| XRL direct, A     | 62       | 2     | 2                                               | 8                                              | 12                      | 1.5                                                 |

| XRL direct, #data | 63       | 3     | 3                                               | 12                                             | 24                      | 2                                                   |

| CLR A             | E4       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| CPL A             | F4       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| RL A              | 23       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| RLC A             | 33       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| RR A              | 03       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| RRC A             | 13       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| SWAP A            | C4       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R0         | E8       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R1         | E9       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R2         | EA       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R3         | EB       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R4         | EC       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R5         | ED       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R6         | D_EE(O)  | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, R7         | EF.      | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

| MOV A, @R0        | E6       | 1     | 1                                               | 4                                              | 12                      | 3                                                   |

# nuvoTon

| Op-code              | HEX Code | Bytes | W79E4051<br>/2051<br>series<br>Machine<br>Cycle | W79E4051<br>/2051<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E4051/205<br>1 series vs.<br>8032 Speed<br>Ratio |

|----------------------|----------|-------|-------------------------------------------------|------------------------------------------------|-------------------------|-----------------------------------------------------|

| CJNE A, direct, rel  | B5       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE A, #data, rel   | B4       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE @R0, #data, rel | B6       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE @R1, #data, rel | B7       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R0, #data, rel  | B8       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R1, #data, rel  | B9       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R2, #data, rel  | BA       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R3, #data, rel  | BB       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R4, #data, rel  | BC       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R5, #data, rel  | BD       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R6, #data, rel  | BE       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| CJNE R7, #data, rel  | BF       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

| DJNZ R0, rel         | D8       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R1, rel         | D9       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R5, rel         | DD       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R2, rel         | DA       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R3, rel         | DB       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R4, rel         | DC       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R6, rel         | DE       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ R7, rel         | DF       | 2     | 3                                               | 12                                             | 24                      | 2                                                   |

| DJNZ direct, rel     | D5       | 3     | 4                                               | 16                                             | 24                      | 1.5                                                 |

Table 9-1: Instruction Set for W79E4051/2051

- 44 -

### **10 POWER MANAGEMENT**

The W79E4051/2051 series has several features that help the user to control the power consumption of the device. These modes are discussed in the next two sections.

### 10.1 Idle Mode

The user can put the device into idle mode by writing 1 to the bit PCON.0. The instruction that sets the idle bit is the last instruction that will be executed before the device goes into Idle Mode. In the Idle mode, the clock to the CPU is halted, but not to the Interrupt, Timer, Watchdog timer, PWM, Analog Comparator(CIPE=1) and Serial port blocks. This forces the CPU state to be frozen; the Program counter, the Stack Pointer, the Program Status Word, the Accumulator and the other registers hold their contents. The port pins hold the logical states they had at the time Idle was activated. The Idle mode can be terminated in two ways. Since the interrupt controller is still active, the activation of any enabled interrupt can wake up the processor. This will automatically clear the Idle bit, terminate the Idle mode, and the Interrupt Service Routine (ISR) will be executed. After the ISR, execution of the program will continue from the instruction which put the device into Idle Mode.

The Idle mode can also be exited by activating the reset. The device can put into reset either by applying a high on the external RST pin, a Power on reset condition or a Watchdog timer reset. The external reset pin has to be held high for at least two machine cycles i.e. 8 clock periods to be recognized as a valid reset. In the reset condition the program counter is reset to 0000h and all the SFRs are set to the reset condition. Since the clock is already running there is no delay and execution starts immediately. In the Idle mode, the Watchdog timer continues to run, and if enabled, a time-out will cause a watchdog timer interrupt which will wake up the device. The software must reset the Watchdog timer in order to preempt the reset which will occur after 512 clock periods of the time-out. When the W79E4051/2051 series are exiting from an Idle Mode with a reset, the instruction following the one which put the device into Idle Mode is not executed. So there is no danger of unexpected writes.

P1.0 and P1.1 should be set to 1 if external pull-ups are applied, or set to 0 if without external pull-ups, or configured to quasi I/O mode by setting P1M1 bit0 and bit1 to high.

### **10.2** Power Down Mode

The device can be put into Power Down mode by writing 1 to bit PCON.1. The instruction that does this will be the last instruction to be executed before the device goes into Power Down mode. In the Power Down mode, all the clocks are stopped and the device comes to a halt. All activity, exception of Brownout reset, INT1, INT0, watchdog timer(Config0.WDTCK=0) and Analog Comparator(CIPE=1), is completely stopped and the power consumption is reduced to the lowest possible value. The port pins output the values held by their respective SFRs.

Before CPU enters power-down mode, P1.0 and P1.1 should be set to 1 if external pull-ups are applied, or set to 0 if without external pull-ups, or configured to quasi I/O mode by setting P1M1 bit0 and bit1 to high.

An external reset can be used to exit the Power down state. The high on RST pin terminates the Power Down mode, and restarts the clock. The program execution will restart from 0000h. In the Power down mode, the clock is stopped, so the Watchdog timer cannot be used to provide the reset to exit Power down mode when its clock source is external OSC or crystal.

The sources that can wake up from the power down mode are external interrupts, brownout reset (BOR), watchdog timer interrupt (if Config0 bit WDTCK = 0) and Analog Comparator(if SFR bit

Some of the bits in the WDCON SFR (WDRUN, WDCLR, EWRST, WDIF, WD0 and WD1) have unrestricted read access which required Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

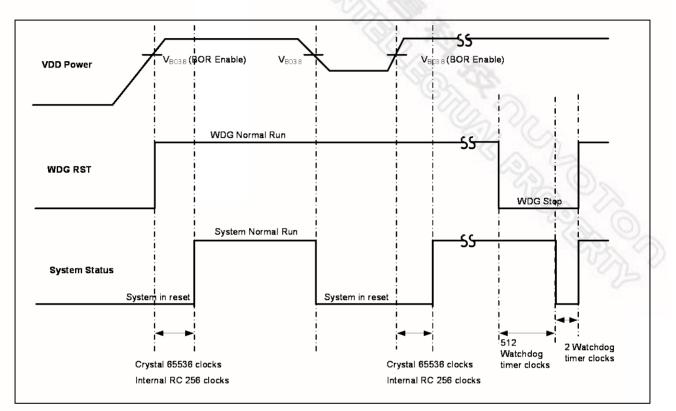

Figure 11-1: Internal reset and VDD monitor timing diagram

Revision A06

The W79E4051/2051 series uses a four priority level interrupt structure (highest, high, low and lowest) and supports up to 9 interrupt sources. The interrupt sources can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as table below. This allows great flexibility in controlling and handling many interrupt sources.

| Priori | ty Bits | Interrupt Drievity Lavel   |

|--------|---------|----------------------------|

| IPxH   | IPx     | Interrupt Priority Level   |

| 0      | 0       | Level 0 (lowest priority)  |

| 0      | 1       | Level 1                    |

| 1      | 0       | Level 2                    |

| 1      | 1       | Level 3 (highest priority) |

Table 12-2: Four-level interrupt priority

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the IPx and IPxH registers. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. So, if two requests of different priority levels are received simultaneously, the request of higher priority level is serviced.

If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve simultaneous requests of the same priority level.

As below Table summarizes the interrupt sources, flag bits, vector addresses, enable bits, priority bits, arbitration ranking, and whether each interrupt may wake up the CPU from Power Down mode.

| Source                  | Flag | Vector<br>address | Interrupt<br>Enable Bits | Interrupt<br>Priority | Flag<br>cleared by                                                        | Arbitration<br>Ranking | Power<br>Down<br>Wakeup |

|-------------------------|------|-------------------|--------------------------|-----------------------|---------------------------------------------------------------------------|------------------------|-------------------------|

| External<br>Interrupt 0 | IEO  | 0003Н             | EX0 (IE0.0)              | IP0H.0, IP0.0         | Edge:<br>Hardware,<br>Software;<br>Level:<br>Follow the<br>inverse of pin | 1(highest)             | Yes                     |

| Brownout<br>Detect      | BOF  | 002BH             | EBOV (EIE.6)             | IP1H.6, IP1.6         | Software                                                                  | 2                      | Yes                     |

| Watchdog Timer          | WDIF | 0053H             | EWDI (EIE.4)             | IP1H.4, IP1.4         | Software                                                                  | 3                      | Yes <sup>(1)</sup>      |

| Timer 0<br>Interrupt    | TF0  | 000BH             | ET0 (IE.1)               | IP0H.1, IP0.1         | Hardware,<br>Software                                                     | 4                      | No                      |

| External<br>Interrupt 1 | IE1  | 0013H             | EX1 (IE.2)               | IP0H.2, IP0.2         | Edge:<br>Hardware,<br>Software;<br>Level:                                 | 5                      | Yes                     |

Figure 13-4: Timer/Counter Mode 3

### **14 NVM MEMORY**

The W79E4051/2051 series have NVM data memory of **128** bytes for customer's data store used. The NVM data memory has **8** pages area and each page has **16** bytes. The page addresses are shown on Figure 14-1

The NVM memory can be read/write by customer program to access. Read NVM data is by MOVC A,@A+DPTR instruction, and write data is by SFR of NVMADDRL, NVMDATA and NVMCON. Before write data to NVM memory, the page must be erased by providing page address on NVMADDRL, which high and low byte address of On-Chip Code Memory space will decode, then set EER of NVMCON.7. This will automatically hold fetch program code and PC Counter, and execute page erase. After finished, this bit will be cleared by hardware. The erase time is ~ 5ms.

For writing data to NVM memory, user must set address and data to NVMADDRL and NVMDATA, then set EWR of NVMCON.6 to initiate NVM data write. The uC will hold program code and PC Counter, and then write data to mapping address. Upon write completion, the EWR bit will be cleared by hardware, the uC will continue execute next instruction. The program time is ~50us.

Figure 14-1: W79E4051/2051 Memory Map

All the slaves can be addressed together using the Broadcast Address. The addresses for each slave are defined by the SADDR and SADEN SFRs. The slave address is an 8-bit value specified in the SADDR SFR. The SADEN SFR is actually a mask for the byte value in SADDR. If a bit position in SADEN is 0, then the corresponding bit position in SADDR is don't care. Only those bit positions in SADDR whose corresponding bits in SADEN are 1 are used to obtain the Given Address. This gives the user flexibility to address multiple slaves without changing the slave address in SADDR.

The following example shows how the user can define the Given Address to address different slaves. Slave 1:

SADDR 1010 0100 SADEN 1111 1010 Given 1010 0x0x

Slave 2:

SADDR 1010 0111 SADEN 1111 1001 Given 1010 0xx1

The Given address for slave 1 and 2 differ in the LSB. For slave 1, it is a don't care, while for slave 2 it is 1. Thus to communicate only with slave 1, the master must send an address with LSB = 0 (1010 0000). Similarly the bit 1 position is 0 for slave 1 and don't care for slave 2. Hence to communicate only with slave 2 the master has to transmit an address with bit 1 = 1 (1010 0011). If the master wishes to communicate with both slaves simultaneously, then the address must have bit 0 = 1 and bit 1 = 0. The bit 3 position is don't care for both the slaves. This allows two different addresses to select both slaves (1010 0001 and 1010 0101).

The master can communicate with all the slaves simultaneously with the Broadcast Address. This address is formed from the logical OR of the SADDR and SADEN SFRs. The zeros in the result are defined as don't cares. In most cases the Broadcast Address is FFh. In the previous case, the Broadcast Address is (1111111x) for slave 1 and (1111111) for slave 2.

The SADDR and SADEN SFRs are located at address A9h and B9h respectively. On reset, these two SFRs are initialized to 00h. This results in Given Address and Broadcast Address being set as xxxx xxxx (i.e. all bits don't care). This effectively removes the multiprocessor communications feature, since any selectivity is disabled.

# nuvoTon

### **18.1 Comparator Interrupt with Debouncing**

The comparator output is sampled at every State 4 (S4) of every machine cycle. The conditions on the analog inputs maybe cause the comparator output toggle excessively, especially applying slow moving analog inputs. Table 18-2: Comparator Interrupt Mode shows the 8 comparator interrupt modes set by CM[2:0] in ACSR(97H). A built-in configurable debouncing timer provides 8 debouncing timing controlled by CPCK[2:0] for widely applications. The debouncing timing is shown in Table 18-1. If CPU is in normal/Idle mode  $F_{DB}$  is from Fosc; if CPU is in power-down mode  $F_{DB}$  is from internal RC 22M/11M Hz oscillator.

| CPCK2 | CPCK 1 | CPCK 0 | Debouncing Time                                   |

|-------|--------|--------|---------------------------------------------------|

| 0     | 0      | 0      | (3/F <sub>DB</sub> )*2~(4/F <sub>DB</sub> )*2     |

| 0     | 0      | 1      | (3/F <sub>DB</sub> )*4~(4/F <sub>DB</sub> )*4     |

| 0     | 1      | 0      | (3/F <sub>DB</sub> )*8~(4/F <sub>DB</sub> )*8     |

| 0     | 1      | 1      | (3/F <sub>DB</sub> )*16~(4/F <sub>DB</sub> )*16   |

| 1     | 0      | 0      | (3/F <sub>DB</sub> )*32~(4/F <sub>DB</sub> )*32   |

| 1     | 0      | 1      | (3/F <sub>DB</sub> )*64~(4/F <sub>DB</sub> )*64   |

| 1     | 1      | 0      | (3/F <sub>DB</sub> )*128~(4/F <sub>DB</sub> )*128 |

| 1     | 1      | 1      | (3/F <sub>DB</sub> )*256~(4/F <sub>DB</sub> )*256 |

|       |        |        |                                                   |

Table 18-1: Comparator Debouncing Time

| CM2 | CM1 | CM0 | Comparator interrupt mode   |

|-----|-----|-----|-----------------------------|

| 0   | 0   | 0   | Negative (Low) level        |

| 0   | 0   | 1   | Positive edge               |

| 0   | 1   | 0   | Toggle with debounce        |

| 0   | 1   | 1   | Positive edge with debounce |

| 1   | 0   | 0   | Negative edge               |

| 1   | 0   | 1   | Toggle                      |

| 1   | 1   | 0   | Negative edge with debounce |

| 1   | 1   | 1   | Positive (High) level       |

Table 18-2: Comparator Interrupt Mode

Three debouncing modes are provided to filter out this noise. In debouncing mode when the comparator output matches one of three debouncing mode condition, the debouncing timer resets and starts up-counting. The end of debouncing triggers the hardware to check if the comparator output matches the mode condition or not. If it is compliant with the mode condition the comparator flag CF is set by hardware, otherwise CF keeps low. Refer to Figure 18-2.

# nuvoton

### 20 I/O PORT MODE SETTING

W79E4051/2051 has maximum one 8-bit(P1), one 7-bit(P3) and one 2-bit(P2) ports. Except P1.0 and P1.1, all pins are quasi-bidrectional mode, which are common with standard 80C51, that the internal weakly pull-ups are present as the port registers are set to logic one. P1.0 and P1.1, the alternate function are analog comparator inputs, stays in PMOS-off open-drain mode after CPU reset. The P2.0 (XTAL2) can be configured as clock output by setting bit ENCLK to high when CPU clock source is from on-chip RC or external Oscillator, and the frequency of clock output is divided by 4 on on-chip RC clock or external Oscillator.

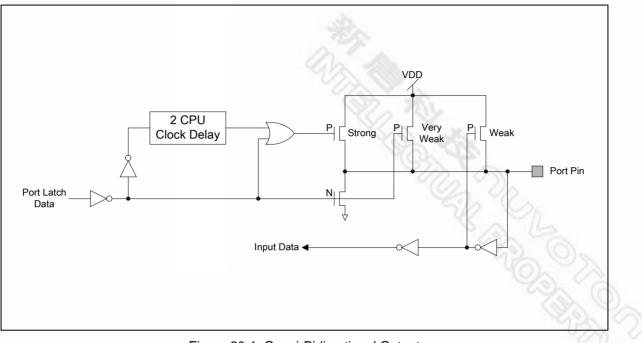

### 20.1 Quasi-Bidirectional Output Configuration

After chip was power on or reset, the all ports except P1.0 and P1.1 output are in this mode, and output is common with the MCS-51. This mode can be used as both an input and output without the need to reconfigure the port. P1.0~P1.1 stays in PMOS-off open-drain mode after CPU reset.

| P1M1.Y |                     |

|--------|---------------------|

| 0      | Open Drain          |

| 1      | Quasi-bidirectional |

| Table 20-1: | I/O port Configuration Table | ; |

|-------------|------------------------------|---|

|-------------|------------------------------|---|

When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are similar to an open drain output except that there are three pull-up transistors in the quasibidirectional output that serve different purposes.

This mode has three pull-up resisters that are "strong" pull-up, "weak" pull-up and "very weak" pull-up. The "strong" pull-up is used fast transition from logic "0" change to logic "1", and it is fast latch and transition. When port pins is occur from logic "0" to logic "1", the strong pull-up will quickly turn on two CPU clocks to pull high then turn off.

The "weak" pull-up is turned on when the input port pin is logic "1" level or itself is logic "1", and it provides the most source current for a quasi-bidirectional pin that output is "1" or port latch is logic "0".

The "very weak" pull-up is turned on when the port latch is logic "1". If port latch is logic "0", it will be turned off. The very weak pull-up is support a very small current that will pull the pin high if it is left floating. And the quasi-bidirectional port configuration is shown as below figure.

If port pin is low, it can drives large sink current up to about 20mA/10mA at  $V_{DD}=5V/2.7V$ . JW.

- 76 -

Figure 20-1: Quasi-Bidirectional Output

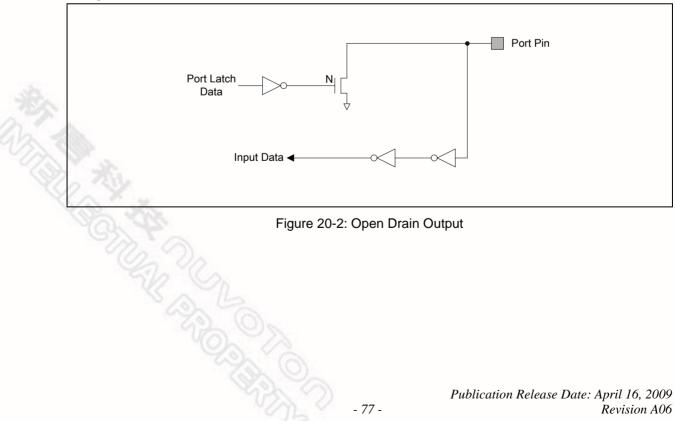

### 20.2 Open Drain Output Configuration

P1.0 and P1.1 are in open drain type after chip reset. To configure this mode is turned off all pull-ups. If used similar as a logic output, the port must has an external pull-up resister. The open drain port configuration is shown as below.

### 22 POWER MONITORING FUNCTION

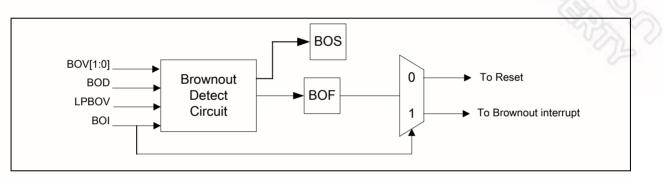

In order to prevent incorrect operation during power up and power drop, the W79E4051/2051 is provided a power monitor function, Brownout Detect.

### 22.1 Brownout Detect and Reset

The W79E4051/2051 has an on-chip Brown-out Detection circuit for monitoring the Vbb level during operation by comparing it to a programmable brownout trigger level. There are 4 brownout trigger levels available for wider voltage applications. The 4 nominal levels are 2.4V, 2.7V, 3.8V and 4.5V (programmable through BOV.1-0 bits). When V<sub>DD</sub> drops to the selected brownout trigger level (V<sub>BOR</sub>), the brownout detection logics will either reset the CPU until the V<sub>DD</sub> voltage raises above V<sub>BOR</sub> or requests a brownout interrupt at the moment that V<sub>DD</sub> falls and raises through V<sub>BOR</sub>. The brownout detection circuits also provides a low power brownout detection mode for power saving. When LPBOV=1, the brownout detection repeatedly senses the voltage for 64/f<sub>BRC</sub> then turn off detector for 960/ f<sub>BRC</sub> if V<sub>DD</sub> voltage still below brownout trigger level. f<sub>BRC</sub>, the frequency of built-in RC oscillator, is approximately 100K\* V<sub>DD</sub> HZ ±50%. The relative control bits are located in SFR AUXR1 @A2h. The Brownout Detect block is shown in Figure 22-1.

Figure 22-1: Brown-out Detect Block

### 24 CONFIG BITS

The W79E4051/2051 has two CONFIG bits (CONFIG0 located at FB00h, CONFIG1 located at FB01h) that must be defined at power up and can not be set by the program after start of execution. Those features are configured through the use of two flash EPROM bytes, and the flash EPROM can be programmed and verified repeatedly. Until the code inside the Flash EPROM is confirmed OK, the code can be protected. The protection of flash EPROM (CONFIG1) and those operations on it are described below.

### 24.1 CONFIG0

| Config0 |       |       |   |   |      | SUY   | 20    |

|---------|-------|-------|---|---|------|-------|-------|

| WDTCK   | CBOV1 | CBOV0 | 0 | - | BPFR | Fosc1 | Fosc0 |

Figure 24-1: Config0 register bits

| -      |       |                                |                                                                                                   |                                      | Mandatan Milling     |  |  |  |  |  |

|--------|-------|--------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|--|--|--|--|--|

| Bit    | Name  | Function                       |                                                                                                   |                                      | ~O~~~~               |  |  |  |  |  |

| 7      | WDTCK | Clock source                   | lock source of Watchdog Timer select bit:                                                         |                                      |                      |  |  |  |  |  |

|        |       | 0: The inter                   | nal 500KH                                                                                         | z RC oscillator clock is for Watchdo | og Timer clock used. |  |  |  |  |  |

|        |       | 1: The uC o                    | clock is for                                                                                      | Watchdog Timer clock used.           | 24                   |  |  |  |  |  |

| 6~5    | CBOV1 | Brownout v                     | oltage sele                                                                                       | ection bits:                         | 6                    |  |  |  |  |  |

|        | CBOV0 |                                | FR bits (BOV1,BOV0) are initialized at reset with the inversed value of config0-bits CBOV1,CBOV0) |                                      |                      |  |  |  |  |  |

|        |       | CBOV.1 CBOV.0 Brownout Voltage |                                                                                                   |                                      |                      |  |  |  |  |  |

|        |       | 1                              | 1                                                                                                 | Brownout voltage is 2.4V             |                      |  |  |  |  |  |

|        |       | 1                              | 0                                                                                                 | Brownout voltage is 2.7V             |                      |  |  |  |  |  |

|        |       | 0                              | 1                                                                                                 | Brownout voltage is 3.8V             |                      |  |  |  |  |  |

|        |       | 0                              | 0                                                                                                 | Brownout voltage is 4.5V             |                      |  |  |  |  |  |

| 2      | BPFR  | Bypass Clo                     | ock Filter.                                                                                       |                                      |                      |  |  |  |  |  |

| 2      |       | 0: Disable (                   | Clock Filter                                                                                      |                                      |                      |  |  |  |  |  |

| $\sim$ |       | 1: Enable C                    | Clock Filter.                                                                                     |                                      |                      |  |  |  |  |  |

| 1      | Fosc1 | CPU Oscill                     | ator Type S                                                                                       | Select bit 1.                        |                      |  |  |  |  |  |

| 0      | Fosc0 | CPU Oscill                     | ator Type S                                                                                       | Select bit 0.                        |                      |  |  |  |  |  |

### **Oscillator Configuration bits:**

| Fosc1 | Fosc0  | OSC source                                                                                                                     |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0      | 4MHz ~ 24MHz crystal                                                                                                           |

| 0     | Stor L | Internal RC Oscillator (FS1 bit in CONFIG1.5 will determine<br>either 11MHz or 22MHZ)<br>XT1 and XT2 function as P2.1 and P2.0 |

| 1     | 0      | Reserved                                                                                                                       |

| 1     | 1      | External Oscillator in XTAL1; XT2 is in Tri-state                                                                              |