Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | 56800E                                                     |

| Core Size                  | 16-Bit                                                     |

| Speed                      | 40MHz                                                      |

| Connectivity               | SCI, SPI                                                   |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 27                                                         |

| Program Memory Size        | 32KB (16K x 16)                                            |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 8K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                  |

| Data Converters            | A/D 8x12b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 64-LQFP                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc56f8123vfbe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| Part 1: Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1.1. 56F8323/56F8123 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 7                                                                                                            |

| 1.2. Device Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 9                                                                                                            |

| 1.3. Award-Winning Development Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                             |

| 1.4. Architecture Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| 1.5. Product Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                             |

| 1.6. Data Sheet Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| Part 2: Signal/Connection Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| 2.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 2.2. Signal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                                             |

| Part 2: On Chin Cleak Synthesis (OCCS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                                                                             |

| Part 3: On-Chip Clock Synthesis (OCCS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| 3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                                             |

| 3.2. External Clock Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

| 3.3. Use of On-Chip Relaxation Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

| 3.4. Internal Clock Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

| 3.5. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                                             |

| Port 4. Momory Mon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                             |

| Part 4: Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

| 4.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| 4.2. Program Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                |

| 4.3. Interrupt Vector Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

| 4.4. Data Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

| 4.5. Flash Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

| 4.6. EOnCE Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| 4.7. Peripheral Memory Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

| 4.7. Peripheral Memory Mapped Registers<br>4.8. Factory Programmed Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40<br>56                                                                                                       |

| 4.8. Factory Programmed Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                                                                             |

| 4.8. Factory Programmed Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br><b>57</b>                                                                                                |

| 4.8. Factory Programmed Memory Part 5: Interrupt Controller (ITCN) 5.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56<br><b>57</b><br>57                                                                                          |

| 4.8. Factory Programmed Memory Part 5: Interrupt Controller (ITCN) 5.1. Introduction 5.2. Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56<br><b>57</b><br>57<br>57                                                                                    |

| 4.8. Factory Programmed Memory<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br><b>57</b><br>57<br>57<br>57<br>57                                                                        |

| 4.8. Factory Programmed Memory<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56<br>57<br>57<br>57<br>57<br>57<br>57<br>59                                                                   |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                              | 56<br>57<br>57<br>57<br>57<br>59<br>59<br>59                                                                   |

| 4.8. Factory Programmed Memory.         Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions                                                                                                                                                                                                                                                                                                                                                             | 56<br>57<br>57<br>57<br>59<br>59<br>60                                                                         |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                              | 56<br>57<br>57<br>57<br>59<br>59<br>60                                                                         |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets                                                                                                                                                                                                                                                                                                                                                                                 | 56<br>57<br>57<br>57<br>57<br>59<br>59<br>60<br>82                                                             |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)                                                                                                                                                                                                                                                                                                                                      | 56<br>57<br>57<br>59<br>60<br>82<br>83                                                                         |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets                                                                                                                                                                                                                                                                                                                                                                                 | 56<br>57<br>57<br>57<br>59<br>59<br>60<br>82<br>83<br>83                                                       |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features                                                                                                                                                                                                                                                                                                | 56<br>57<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83                                                       |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes                                                                                                                                                                                                                                                                        | 56<br>57<br>57<br>59<br>59<br>60<br>82<br>83<br>83<br>83<br>83<br>84                                           |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes<br>6.4. Operating Mode Register                                                                                                                                                                                                                                        | 56<br>57<br>57<br>59<br>59<br>60<br>82<br>83<br>83<br>83<br>83<br>84<br>84                                     |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes                                                                                                                                                                                                                                                                        | 56<br>57<br>57<br>59<br>59<br>60<br>82<br>83<br>83<br>83<br>84<br>84<br>84                                     |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes<br>6.4. Operating Mode Register<br>6.5. Register Descriptions                                                                                                                                                                                                          | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>84<br>84<br>85<br>97                                     |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes<br>6.4. Operating Mode Register<br>6.5. Register Descriptions<br>6.6. Clock Generation Overview.<br>6.7. Power-Down Modes                                                                                                                                              | 56<br>57<br>57<br>59<br>59<br>60<br>82<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97                         |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes<br>6.4. Operating Mode Register<br>6.5. Register Descriptions<br>6.6. Clock Generation Overview.                                                                                                                                                                       | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97<br>98                   |

| 4.8. Factory Programmed Memory.         Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Introduction         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.         6.7. Power-Down Modes         6.8. Stop and Wait Mode Disable Function                     | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97<br>98                   |

| 4.8. Factory Programmed Memory.         Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Introduction         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.         6.7. Power-Down Modes         6.8. Stop and Wait Mode Disable Function                     | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97<br>98<br>98             |

| 4.8. Factory Programmed Memory.         Part 5: Interrupt Controller (ITCN)         5.1. Introduction         5.2. Features         5.3. Functional Description         5.4. Block Diagram         5.5. Operating Modes         5.6. Register Descriptions         5.7. Resets         Part 6: System Integration Module (SIM)         6.1. Introduction         6.2. Features         6.3. Operating Modes         6.4. Operating Modes         6.5. Register Descriptions         6.6. Clock Generation Overview.         6.7. Power-Down Modes         6.8. Stop and Wait Mode Disable Function         6.9. Resets | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97<br>98<br>98<br>98<br>99<br>99 |

| 4.8. Factory Programmed Memory.<br>Part 5: Interrupt Controller (ITCN)<br>5.1. Introduction<br>5.2. Features<br>5.3. Functional Description<br>5.4. Block Diagram<br>5.5. Operating Modes<br>5.6. Register Descriptions<br>5.7. Resets<br>Part 6: System Integration Module (SIM)<br>6.1. Introduction<br>6.2. Features<br>6.3. Operating Modes<br>6.4. Operating Modes<br>6.5. Register Descriptions<br>6.6. Clock Generation Overview.<br>6.7. Power-Down Modes<br>6.8. Stop and Wait Mode Disable Function<br>6.9. Resets<br>Part 7: Security Features                                                              | 56<br>57<br>57<br>59<br>60<br>82<br>83<br>83<br>83<br>84<br>84<br>85<br>97<br>97<br>98<br>98<br>98<br>99<br>99 |

| Part 8: General Purpose Input/Output<br>(GPIO)                                 |

|--------------------------------------------------------------------------------|

| 8.1. Introduction                                                              |

| 8.2. Configuration                                                             |

| 8.3. Memory Maps104                                                            |

| Part 9: Joint Test Action Group (JTAG) 104                                     |

| 9.1. JTAG Information 104                                                      |

| Part 10: Specifications 105                                                    |

| 10.1. General Characteristics                                                  |

| 10.2. DC Electrical Characteristics 109                                        |

| 10.3. AC Electrical Characteristics                                            |

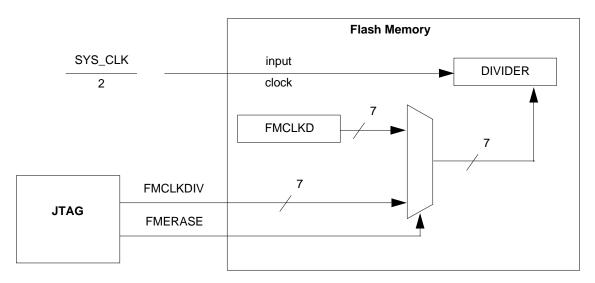

| 10.4. Flash Memory Characteristics 114                                         |

| 10.5. External Clock Operation Timing 114                                      |

| 10.6. Phase Locked Loop Timing115                                              |

| 10.7. Crystal Oscillator Parameters                                            |

| 10.8. Reset, Stop, Wait, Mode Select, and                                      |

| Interrupt Timing                                                               |

| 10.9. Serial Peripheral Interface (SPI) Timing 119<br>10.10. Quad Timer Timing |

| 10.10. Quadrature Decoder Timing                                               |

| 10.12. Serial Communication Interface                                          |

| (SCI) Timing                                                                   |

| 10.13. Controller Area Network (CAN) Timing. 124                               |

| 10.14. JTAG Timing                                                             |

| 10.15. Analog-to-Digital Converter                                             |

| (ADC) Parameters 126                                                           |

| 10.16. Equivalent Circuit for ADC Inputs 129                                   |

| 10.17. Power Consumption                                                       |

| ·                                                                              |

| Part 11: Packaging 131                                                         |

| 11.1. 56F8323 Package and Pin-Out                                              |

| Information                                                                    |

| 11.2. 56F8123 Package and Pin-Out                                              |

| Information 133                                                                |

| Part 12: Design Considerations 136                                             |

| 12.1. Thermal Design Considerations 136                                        |

| 12.2. Electrical Design Considerations                                         |

| 12.3. Power Distribution and I/O Ring                                          |

| Implementation                                                                 |

Part 13: Ordering Information ..... 139

| Signal Name         | Pin No. | Туре                        | State During<br>Reset        | Signal Description                                                                                                                                                                                                                                                                                             |

|---------------------|---------|-----------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REFP</sub>   | 37      | Input/                      | Analog Input/                | V <sub>REFP</sub> , V <sub>REFMID</sub> & V <sub>REFN</sub> — Internal pins for voltage reference which                                                                                                                                                                                                        |

| V <sub>REFMID</sub> | 36      | Output                      | Output                       | are brought off-chip so that they can be bypassed. Connect to a $0.1\mu F$ ceramic low ESR capacitor                                                                                                                                                                                                           |

| V <sub>REFN</sub>   | 35      |                             |                              |                                                                                                                                                                                                                                                                                                                |

| V <sub>REFLO</sub>  | 38      | Schmitt<br>Input            | Analog Input                 | $\mathbf{V_{REFLO}}$ — Analog Reference Voltage Low. This should normally be connected to a low-noise V <sub>SS</sub> .                                                                                                                                                                                        |

| TEMP_SENSE          | 34      | Output                      | Analog<br>Output             | <b>Temperature Sense Diode</b> — This signal connects to an on-chip diode that can be connected to one of the ADC inputs and used to monitor the temperature of the die. Must be bypassed with a $0.01 \mu$ F capacitor                                                                                        |

| CAN_RX              | 61      | Schmitt<br>Input            | Input,<br>pull-up<br>enabled | FlexCAN Receive Data — This is the CAN input. This pin has an internal pull-up resistor.                                                                                                                                                                                                                       |

| (GPIOC2)            |         | Schmitt<br>Input/<br>Output | enabled                      | <b>Port C GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                   |

|                     |         | Output                      |                              | In the 56F8323, the default state after reset is CAN_RX.                                                                                                                                                                                                                                                       |

|                     |         |                             |                              | In the 56F8123, the default state is not one of the functions offered and must be reconfigured.                                                                                                                                                                                                                |

| CAN_TX              | 62      | Open<br>Drain<br>Output     | Open<br>Drain<br>Output      | FlexCAN Transmit Data — CAN output with internal pull-up enable at reset.*                                                                                                                                                                                                                                     |

|                     |         | Ouput                       | Ouput                        | * <b>Note</b> : If a pin is configured as open drain output mode, internal pull-up will automatically be disabled when it outputs low. Internal pull-up will be enabled unless it has been manually disabled by clearing the corresponding bit in the PUREN register of the GPIO module, when it outputs high. |

|                     |         |                             |                              | If a pin is configured as push-pull output mode, internal pull-up will automatically be disabled, whether it outputs low or high.                                                                                                                                                                              |

| (GPIOC3)            |         | Schmitt<br>Input/<br>Output |                              | <b>Port C GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                   |

|                     |         | Juipui                      |                              | In the 56F8323, the default state after reset is CAN_TX.                                                                                                                                                                                                                                                       |

|                     |         |                             |                              | In the 56F8123, the default state is not one of the functions offered and must be reconfigured.                                                                                                                                                                                                                |

## Part 3 On-Chip Clock Synthesis (OCCS)

### 3.1 Introduction

Refer to the OCCS chapter of the **56F8300 Peripheral User Manual** for a full description of the OCCS. The material contained here identifies the specific features of the OCCS design.

## 3.2 External Clock Operation

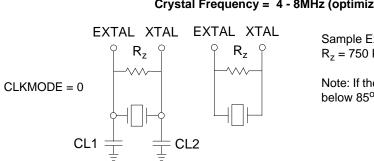

The system clock can be derived from an external crystal, ceramic resonator, or an external system clock signal. To generate a reference frequency using the internal oscillator, a reference crystal or ceramic resonator must be connected between the EXTAL and XTAL pins.

### 3.2.1 Crystal Oscillator

The internal oscillator is designed to interface with a parallel-resonant crystal resonator in the frequency range specified for the external crystal in **Table 10-15**. A recommended crystal oscillator circuit is shown in **Figure 3-1**. Follow the crystal supplier's recommendations when selecting a crystal, since crystal parameters determine the component values required to provide maximum stability and reliable start-up. The crystal and associated components should be mounted as near as possible to the EXTAL and XTAL pins to minimize output distortion and start-up stabilization time.

Crystal Frequency = 4 - 8MHz (optimized for 8MHz)

Sample External Crystal Parameters:  $R_7 = 750 \text{ K}\Omega$

Note: If the operating temperature range is limited to below 85°C (105°C junction), then  $R_z = 10 \text{ Meg } \Omega$

### Figure 3-1 Connecting to a Crystal Oscillator

**Note:** The OCCS\_COHL bit should be set to 1 when a crystal oscillator is used. The reset condition on the OCCS\_COHL bit is 0. Please see the COHL bit in the Oscillator Control (OSCTL) register, discussed in the **56F8300 Peripheral User Manual**.

### 3.2.2 Ceramic Resonator (Default)

It is also possible to drive the internal oscillator with a ceramic resonator, assuming the overall system design can tolerate the reduced signal integrity. A typical ceramic resonator circuit is shown in **Figure 3-2**. Refer to the supplier's recommendations when selecting a ceramic resonator and associated components. The resonator and components should be mounted as near as possible to the EXTAL and XTAL pins.

### 3.5 Registers

When referring to the register definitions for the OCCS in the **56F8300 Peripheral User Manual**, use the register definitions **with** the internal Relaxation Oscillator, since the 56F8323 and 56F8123 contain this oscillator.

## Part 4 Memory Map

## 4.1 Introduction

The 56F8323 and 56F8123 devices are 16-bit motor-control chips based on the 56800E core. These parts use a Harvard-style architecture with two independent memory spaces for Data and Program. On-chip RAM and Flash memories are used in both spaces.

This section provides memory maps for:

- Program Address Space, including the Interrupt Vector Table

- Data Address Space, including the EOnCE Memory and Peripheral Memory Maps

On-chip memory sizes for the device are summarized in **Table 4-1**. Flash memories' restrictions are identified in the "Use Restrictions" column of **Table 4-1**.

Note: Data Flash and Program RAM are NOT available on the 56F8123 device.

| On-Chip Memory     | 56F8323 | 56F8123 | Use Restrictions                                                                                                                                       |

|--------------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Flash      | 32KB    | 32KB    | Erase / Program via Flash interface unit and word writes to CDBW                                                                                       |

| Data Flash         | 8KB     | _       | Erase / Program via Flash interface unit and word<br>writes to CDBW. Data Flash can be read via either<br>CDBR or XDB2, but not by both simultaneously |

| Program RAM        | 4KB     | —       | None                                                                                                                                                   |

| Data RAM           | 8KB     | 8KB     | None                                                                                                                                                   |

| Program Boot Flash | 8KB     | 8KB     | Erase / Program via Flash Interface unit and word writes to CDBW                                                                                       |

**Table 4-1 Chip Memory Configurations**

## 4.2 Program Map

The Program Memory map is located in **Table 4-2**. The operating mode control bits (MA and MB) in the Operating Mode Register (OMR) control the Program Memory map. Because the 56F8323 and 56F8123 do not include EMI, the OMR MA bit, which is used to decide internal or external BOOT, will have no effect on the Program Memory Map. OMR MB reflects the security status of the Program Flash. After reset, changing the OMR MB bit will have no effect on the Program Flash.

| Peripheral | Vector<br>Number | Priority<br>Level | Vector Base<br>Address + | Interrupt Function                            |

|------------|------------------|-------------------|--------------------------|-----------------------------------------------|

| SCI1       | 45               | 0-2               | P:\$5A                   | SCI 1 Receiver Error                          |

| SCI1       | 46               | 0-2               | P:\$5C                   | SCI 1 Receiver Full                           |

|            |                  |                   |                          | Reserved                                      |

| DEC0       | 49               | 0-2               | P:\$62                   | Quadrature Decoder #0 Home Switch or Watchdog |

| DEC0       | 50               | 0-2               | P:\$64                   | Quadrature Decoder #0 INDEX Pulse             |

|            |                  |                   |                          | Reserved                                      |

| TMRC       | 56               | 0-2               | P:\$70                   | Timer C Channel 0                             |

| TMRC       | 57               | 0-2               | P:\$72                   | Timer C Channel 1                             |

| TMRC       | 58               | 0-2               | P:\$74                   | Timer C Channel 2                             |

| TMRC       | 59               | 0-2               | P:\$76                   | Timer C Channel 3                             |

|            |                  |                   |                          | Reserved                                      |

| TMRA       | 64               | 0-2               | P:\$80                   | Timer A Channel 0                             |

| TMRA       | 65               | 0-2               | P:\$82                   | Timer A Channel 1                             |

| TMRA       | 66               | 0-2               | P:\$84                   | Timer A Channel 2                             |

| TMRA       | 67               | 0-2               | P:\$86                   | Timer A Channel 3                             |

| SCI0       | 68               | 0-2               | P:\$88                   | SCI 0 Transmitter Empty                       |

| SCI0       | 69               | 0-2               | P:\$8A                   | SCI 0 Transmitter Idle                        |

|            |                  |                   |                          | Reserved                                      |

| SCI0       | 71               | 0-2               | P:\$8E                   | SCI 0 Receiver Error                          |

| SCI0       | 72               | 0-2               | P:\$90                   | SCI 0 Receiver Full                           |

|            |                  |                   |                          | Reserved                                      |

| ADCA       | 74               | 0-2               | P:\$94                   | ADC A Conversion Complete / End of Scan       |

|            |                  |                   |                          | Reserved                                      |

| ADCA       | 76               | 0-2               | P:\$98                   | ADC A Zero Crossing or Limit Error            |

|            |                  |                   |                          | Reserved                                      |

| PWMA       | 78               | 0-2               | P:\$9C                   | Reload PWM A                                  |

|            |                  |                   |                          | Reserved                                      |

| PWMA       | 80               | 0-2               | P:\$A0                   | PWM A Fault                                   |

| core       | 81               | - 1               | P:\$A2                   | SW Interrupt LP                               |

|            | 82               | 0 - 2             | P:\$A4                   |                                               |

|            |                  |                   |                          |                                               |

### Table 4-3 Interrupt Vector Table Contents<sup>1</sup> (Continued)

1. Two words are allocated for each entry in the vector table. This does not allow the full address range to be referenced from the vector table, providing only 19 bits of address.

2. If the VBA is set to \$0200, the first two locations of the vector table will overlay the chip reset addresses.

| Register Acronym | Address Offset | Register Description                   |

|------------------|----------------|----------------------------------------|

| TMRA0_CMP1       | \$0            | Compare Register 1                     |

| TMRA0_CMP2       | \$1            | Compare Register 2                     |

| TMRA0_CAP        | \$2            | Capture Register                       |

| TMRA0_LOAD       | \$3            | Load Register                          |

| TMRA0_HOLD       | \$4            | Hold Register                          |

| TMRA0_CNTR       | \$5            | Counter Register                       |

| TMRA0_CTRL       | \$6            | Control Register                       |

| TMRA0_SCR        | \$7            | Status and Control Register            |

| TMRA0_CMPLD1     | \$8            | Comparator Load Register 1             |

| TMRA0_CMPLD2     | \$9            | Comparator Load Register 2             |

| TMRA0_COMSCR     | \$A            | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRA1_CMP1       | \$10           | Compare Register 1                     |

| TMRA1_CMP2       | \$11           | Compare Register 2                     |

| TMRA1_CAP        | \$12           | Capture Register                       |

| TMRA1_LOAD       | \$13           | Load Register                          |

| TMRA1_HOLD       | \$14           | Hold Register                          |

| TMRA1_CNTR       | \$15           | Counter Register                       |

| TMRA1_CTRL       | \$16           | Control Register                       |

| TMRA1_SCR        | \$17           | Status and Control Register            |

| TMRA1_CMPLD1     | \$18           | Comparator Load Register 1             |

| TMRA1_CMPLD2     | \$19           | Comparator Load Register 2             |

| TMRA1_COMSCR     | \$1A           | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRA2_CMP1       | \$20           | Compare Register 1                     |

| TMRA2_CMP2       | \$21           | Compare Register 2                     |

| TMRA2_CAP        | \$22           | Capture Register                       |

| TMRA2_LOAD       | \$23           | Load Register                          |

| TMRA2_HOLD       | \$24           | Hold Register                          |

| TMRA2_CNTR       | \$25           | Counter Register                       |

| TMRA2_CTRL       | \$26           | Control Register                       |

| TMRA2_SCR        | \$27           | Status and Control Register            |

| TMRA2_CMPLD1     | \$28           | Comparator Load Register 1             |

|                  |                |                                        |

#### Table 4-8 Quad Timer A Registers Address Map (TMRA\_BASE = \$00 F040)

| Register Acronym | Address Offset | Register Description              | Reset Value |

|------------------|----------------|-----------------------------------|-------------|

| GPIOC_PUR        | \$0            | Pull-up Enable Register           | 0 x 007C    |

| GPIOC_DR         | \$1            | Data Register                     | 0 x 0000    |

| GPIOC_DDR        | \$2            | Data Direction Register           | 0 x 0000    |

| GPIOC_PER        | \$3            | Peripheral Enable Register        | 0 x 007F    |

| GPIOC_IAR        | \$4            | Interrupt Assert Register         | 0 x 0000    |

| GPIOC_IENR       | \$5            | Interrupt Enable Register         | 0 x 0000    |

| GPIOC_IPOLR      | \$6            | Interrupt Polarity Register       | 0 x 0000    |

| GPIOC_IPR        | \$7            | Interrupt Pending Register        | 0 x 0000    |

| GPIOC_IESR       | \$8            | Interrupt Edge-Sensitive Register | 0 x 0000    |

| GPIOC_PPMODE     | \$9            | Push-Pull Mode Register           | 0 x 007F    |

| GPIOC_RAWDATA    | \$A            | Raw Data Input Register           | —           |

#### Table 4-23 GPIOC Registers Address Map (GPIOC\_BASE = \$00 F310)

# Table 4-24 System Integration Module Registers Address Map(SIM\_BASE = \$00 F350)

| Register Acronym | Address Offset                               | Register Description                    |

|------------------|----------------------------------------------|-----------------------------------------|

| SIM_CONTROL      | \$0                                          | Control Register                        |

| SIM_RSTSTS       | \$1                                          | Reset Status Register                   |

| SIM_SCR0         | \$2                                          | Software Control Register 0             |

| SIM_SCR1         | \$3                                          | Software Control Register 1             |

| SIM_SCR2         | \$4                                          | Software Control Register 2             |

| SIM_SCR3         | \$5                                          | Software Control Register 3             |

| SIM_MSH_ID       | \$6                                          | Most Significant Half JTAG ID           |

| SIM_LSH_ID       | \$7                                          | Least Significant Half JTAG ID          |

| SIM_PUDR         | \$8                                          | Pull-up Disable Register                |

|                  |                                              | Reserved                                |

| SIM_CLKOSR       | \$A                                          | Clock Out Select Register               |

| SIM_GPS          | \$B                                          | GPIO Peripheral Select Register         |

| SIM_PCE          | \$C                                          | Peripheral Clock Enable Register        |

| SIM_ISALH        | \$D I/O Short Address Location High Register |                                         |

| SIM_ISALL        | \$E                                          | I/O Short Address Location Low Register |

| Table 4-27 FlexCAN Registers Address Map (Continued) |

|------------------------------------------------------|

| (FC_BĂSE = \$00 F800)                                |

| FlexCAN is NOT available in the 56F8123 device       |

| Register Acronym | Address Offset | Register Description                       |

|------------------|----------------|--------------------------------------------|

| FCMB1_DATA       | \$4B           | Message Buffer 1 Data Register             |

| FCMB1_DATA       | \$4C           | Message Buffer 1 Data Register             |

| FCMB1_DATA       | \$4D           | Message Buffer 1 Data Register             |

| FCMB1_DATA       | \$4E           | Message Buffer 1 Data Register             |

|                  |                | Reserved                                   |

| FCMB2_CONTROL    | \$50           | Message Buffer 2 Control / Status Register |

| FCMB2_ID_HIGH    | \$51           | Message Buffer 2 ID High Register          |

| FCMB2_ID_LOW     | \$52           | Message Buffer 2 ID Low Register           |

| FCMB2_DATA       | \$53           | Message Buffer 2 Data Register             |

| FCMB2_DATA       | \$54           | Message Buffer 2 Data Register             |

| FCMB2_DATA       | \$55           | Message Buffer 2 Data Register             |

| FCMB2_DATA       | \$56           | Message Buffer 2 Data Register             |

|                  |                | Reserved                                   |

| FCMB3_CONTROL    | \$58           | Message Buffer 3 Control / Status Register |

| FCMB3_ID_HIGH    | \$59           | Message Buffer 3 ID High Register          |

| FCMB3_ID_LOW     | \$5A           | Message Buffer 3 ID Low Register           |

| FCMB3_DATA       | \$5B           | Message Buffer 3 Data Register             |

| FCMB3_DATA       | \$5C           | Message Buffer 3 Data Register             |

| FCMB3_DATA       | \$5D           | Message Buffer 3 Data Register             |

| FCMB3_DATA       | \$5E           | Message Buffer 3 Data Register             |

|                  |                | Reserved                                   |

| FCMB4_CONTROL    | \$60           | Message Buffer 4 Control / Status Register |

| FCMB4_ID_HIGH    | \$61           | Message Buffer 4 ID High Register          |

| FCMB4_ID_LOW     | \$62           | Message Buffer 4 ID Low Register           |

| FCMB4_DATA       | \$63           | Message Buffer 4 Data Register             |

| FCMB4_DATA       | \$64           | Message Buffer 4 Data Register             |

| FCMB4_DATA       | \$65           | Message Buffer 4 Data Register             |

| FCMB4_DATA       | \$66           | Message Buffer 4 Data Register             |

|                  |                | Reserved                                   |

| FCMB5_CONTROL    | \$68           | Message Buffer 5 Control / Status Register |

| FCMB5_ID_HIGH    | \$69           | Message Buffer 5 ID High Register          |

| FCMB5_ID_LOW     | \$6A           | Message Buffer 5 ID Low Register           |

| FCMB5_DATA       | \$6B           | Message Buffer 5 Data Register             |

#### 5.6.6.3 SCI1 Receiver Error Interrupt Priority Level (SCI1\_RERR IPL)— Bits 9–8

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.6.6.4 Reserved—Bits 7–6

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

#### 5.6.6.5 SCI1 Transmitter Idle Interrupt Priority Level (SCI1\_TIDL IPL)— Bits 5–4

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

# 5.6.6.6 SCI1 Transmitter Empty Interrupt Priority Level (SCI1\_XMIT IPL)— Bits 3–2

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

### 5.6.6.7 SPI0 Transmitter Empty Interrupt Priority Level (SPI0\_XMIT IPL)— Bits 1–0

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

### 5.6.8 Interrupt Priority Register 7 (IPR7)

| Base + \$7 | 15        | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5          | 4 | 3         | 2 | 1         | 0 |

|------------|-----------|----|----|----|----|----|---|---|---|---|------------|---|-----------|---|-----------|---|

| Read       |           |    |    | 0  | 0  | 0  | 0 | 0 | 0 | 0 | TMRC3 IPL  |   | TMRC2 IPL |   | TMRC1 IPL |   |

| Write      | TMRA0 IPL |    |    |    |    |    |   |   |   |   | T MRC3 IPL |   | TMRC2 IPL |   | TMRCTIPL  |   |

| RESET      | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0          | 0 | 0         | 0 | 0         | 0 |

Figure 5-10 Interrupt Priority Register (IPR7)

### 5.6.8.1 Timer A, Channel 0 Interrupt Priority Level (TMRA0 IPL)— Bits 15–14

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.6.8.2 Reserved—Bits 13–6

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

#### 5.6.8.3 Timer C, Channel 3 Interrupt Priority Level (TMRC3 IPL)—Bits 5–4

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

#### 5.6.8.4 Timer C, Channel 2 Interrupt Priority Level (TMRC2 IPL)—Bits 3–2

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0 through 2. They are disabled by default.

- 00 = IRQ disabled (default)

- 01 = IRQ is priority level 0

- 10 = IRQ is priority level 1

- 11 = IRQ is priority level 2

### 5.6.21.1 IRQ Pending (PENDING)—Bits 64–49

This register combines with the other five to represent the pending IRQs for interrupt vector numbers two through 81.

- 0 = IRQ pending for this vector number

- 1 = No IRQ pending for this vector number

### 5.6.22 IRQ Pending 4 Register (IRQP4)

| Base + \$15 | 15 | 14              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|----|-----------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Read        |    | PENDING [80:65] |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Write       |    |                 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| RESET       | 1  | 1               | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### Figure 5-24 IRQ Pending 4 Register (IRQP4)

#### 5.6.22.1 IRQ Pending (PENDING)—Bits 80–65

This register combines with the other five to represent the pending IRQs for interrupt vector numbers 2 through 81.

- 0 = IRQ pending for this vector number

- 1 = No IRQ pending for this vector number

### 5.6.23 IRQ Pending 5 Register (IRQP5)

| Base + \$16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                    |

|-------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----------------------|

| Read        | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | PEND-<br>ING<br>[81] |

| Write       |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |                      |

| RESET       | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1                    |

#### Figure 5-25 IRQ Pending Register 5 (IRQP5)

#### 5.6.23.1 Reserved—Bits 96-82

This bit field is reserved or not implemented. The bits are read as 1 and cannot be modified by writing.

### 5.6.23.2 IRQ Pending (PENDING)—Bit 81

This register combines with the other five to represent the pending IRQs for interrupt vector numbers 2 through 81.

- 0 = IRQ pending for this vector number

- 1 =No IRQ pending for this vector number

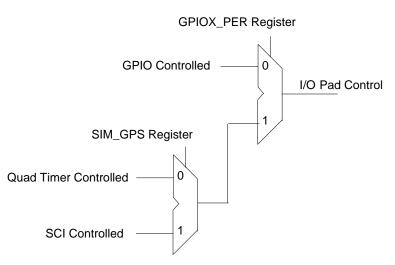

#### Figure 6-10 Overall Control of Pads Using SIM\_GPS Control

| Base + \$B | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------------|----|----|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | C6 | C5 | B1 | B0 | A5 | A4 | A3 | A2 |

| Write      |    |    |    |    |    |    |   |   | 0  | 05 | ы  | BU | A3 | 74 | A3 | 72 |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### Figure 6-11 GPIO Peripheral Select Register (SIM\_GPS)

#### 6.5.8.1 Reserved—Bits 15-8

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

### 6.5.8.2 GPIOC6 (C6)—Bit 7

This bit selects the alternate function for GPIOC6.

- 0 = TC0 (default)

- 1 = TXD0

#### 6.5.8.3 GPIOC5 (C5)—Bit 6

This bit selects the alternate function for GPIOC5.

- 0 = TC1 (default)

- 1 = RXD0

### 6.5.8.4 GPIOB1 (B1)—Bit 5

This bit selects the alternate function for GPIOB1.

- 0 = MISO0 (default)

- 1 = RXD1

### 6.5.10.2 Input/Output Short Address Low (ISAL[21:6])—Bit 15–0

This field represents the lower 16 address bits of the "hard coded" I/O short address.

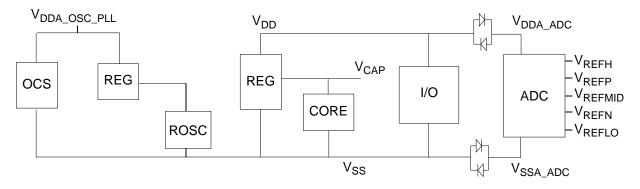

### 6.6 Clock Generation Overview

The SIM uses an internal master clock from the OCCS (CLKGEN) module to produce the peripheral and system (core and memory) clocks. The maximum master clock frequency is 120MHz. Peripheral and system clocks are generated at half the master clock frequency and therefore at a maximum 60MHz. The SIM provides power modes (Stop, Wait) and clock enables (SIM\_PCE register, CLK\_DIS, ONCE\_EBL) to control which clocks are in operation. The OCCS, power modes, and clock enables provide a flexible means to manage power consumption.

Power utilization can be minimized in several ways. In the OCCS, the relaxation oscillator, crystal oscillator, and PLL may be shut down when not in use. When the PLL is in use, its prescaler and postscaler can be used to limit PLL and master clock frequency. Power modes permit system and/or peripheral clocks to be disabled when unused. Clock enables provide the means to disable individual clocks. Some peripherals provide further controls to disable unused subfunctions. Refer to **Part 3 On-Chip Clock Synthesis (OCCS)**, and the **56F8300 Peripheral User Manual** for further details.