## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                      |

| Number of I/O              | 38                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 96K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 8x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamg53n19b-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SAM G53G / SAM G53N

# Atmel

## Atmel | SMART ARM-based Flash MCU

#### SUMMARY DATASHEET

### Description

The Atmel<sup>®</sup> | SMART SAM G53 is a series of Flash microcontrollers based on the high-performance 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M4 RISC processor. It operates at a maximum speed of 48 MHz and features up to 512 Kbytes of Flash and 96 Kbytes of SRAM. The peripheral set includes one USART, two UARTs, three I<sup>2</sup>C-bus interfaces (TWI), up to two SPIs, two three-channel general-purpose 16-bit timers, two I<sup>2</sup>S controllers with two-way, one-channel pulse density modulation, one real-time timer (RTT) and one 8-channel 12-bit ADC.

The Atmel | SMART SAM G53 devices have two software-selectable low-power modes: Sleep and Wait. In Sleep mode, the processor is stopped while all other functions can be kept running. In Wait mode, all clocks and functions are stopped but some peripherals can be configured to wake up the system based on events, including partial asynchronous wake-up (SleepWalking<sup>™</sup>).

The Event System allows peripherals to receive, react to and send events in Active and Sleep modes without processor intervention.

A general-purpose microcontroller with the best ratio in terms of reduced power consumption, processing power and peripheral set, the SAM G53 series sustains a wide range of applications including consumer, industrial control, and PC peripherals.

The device operates from 1.62V to 3.6V and is available in a 49-ball WLCSP package and a 100-pin LQFP package.

This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

## Features

- Core

- ARM Cortex-M4 up to 48 MHz

- Memory Protection Unit (MPU)

- DSP Instructions

- Floating Point Unit (FPU)

- Thumb<sup>®</sup>-2 instruction set

- Memories

- 512 Kbytes embedded Flash

- 96 Kbytes embedded SRAM

- System

- Embedded voltage regulator for single-supply operation

- Power-on reset (POR) and Watchdog for safe operation

- Quartz or ceramic resonator oscillators: 3 to 20 MHz with clock failure detection and 32.768 kHz for RTT or device clock

- High-precision 8/16/24 MHz factory-trimmed internal RC oscillator. In-application trimming access for frequency adjustment

- Slow clock internal RC oscillator as permanent Low-power mode device clock

- PLL range from 24 MHz to 48 MHz for device clock

- 28 peripheral DMA (PDC) channels

- 256-bit General-Purpose Registers (GPBR)

- 16 external interrupt lines

- Power consumption in Active mode

- 102 µA/MHz running Fibonacci in SRAM

- Low power modes (typical value)

- Wait mode down to 8 µA

- Wake-up time less than 5 µs

- Asynchronous partial wake-up (SleepWalking™) on UART and TWI

- Peripherals

- One USART with SPI mode

- Two Inter-IC Sound Controllers (I<sup>2</sup>S)

- Two-way one-channel Pulse Density Modulation (PDM) (interfaces up to two microphones in PDM mode)

- Two UARTs

- Three Two-Wire Interface (TWI) modules featuring two TWI masters and one high-speed TWI slave

- One fast SPI at up to 24Mbit/s

- Two three-channel 16-bit Timer/Counters (TC) with Capture, Waveform, Compare and PWM modes

- One 32-bit Real-Time Timer (RTT)

- I/O

- Up to 38 controllable I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and on-die series resistor termination. Individually programmable open-drain, pull-up and pull-down resistor and synchronous output

- Analog

- One 8-channel ADC, resolution up to 12 bits, sampling rate up to 800 kSps

- Package

- 49-ball WLCSP

- 100-pin LQFP, 14 x 14 mm, pitch 0.5 mm

- Temperature operating range

- Industrial (-40 °C to +85 °C)

## 1. Configuration Summary

Table 1-1 summarizes the SAM G53 device configurations.

| Feature        | SAM G53G19                    | SAM G53N19                    |

|----------------|-------------------------------|-------------------------------|

| Flash          | 512 Kbytes                    | 512 Kbytes                    |

| SRAM           | 96 Kbytes                     | 96 Kbytes                     |

| Package        | WLCSP49                       | LQFP100                       |

| Number of PIOs | 38                            | 38                            |

| Event System   | Yes                           | Yes                           |

|                | 8 channels                    | 8 channels                    |

|                | Performance:                  | Performance                   |

|                | 800 KSps at 10-bit resolution | 800 KSps at 10-bit resolution |

|                | 200 KSps at 11-bit resolution | 200 KSps at 11-bit resolution |

| 12-bit ADC     | 50 KSps at 12-bit resolution  | 50 KSps at 12-bit resolution  |

|                | 6 channels                    | 6 channels                    |

| 16-bit Timer   | (3 external channels)         | (3 external channels)         |

| I2SC/PDM       | 2 / 1-channel 2-way           | 2 / 1-channel 2-way           |

| PDC Channels   | 28                            | 28                            |

| USART/UART     | 1/2                           | 1/2                           |

| SPI            | 1                             | 1                             |

|                | 2 masters at 400Kbits/s and   | 2 masters 400Kbits/s and      |

| тwi            | 1 slave at 3.4Mbit/s          | 1 slave 3.4Mbit/s             |

#### Table 1-1.Configuration Summary

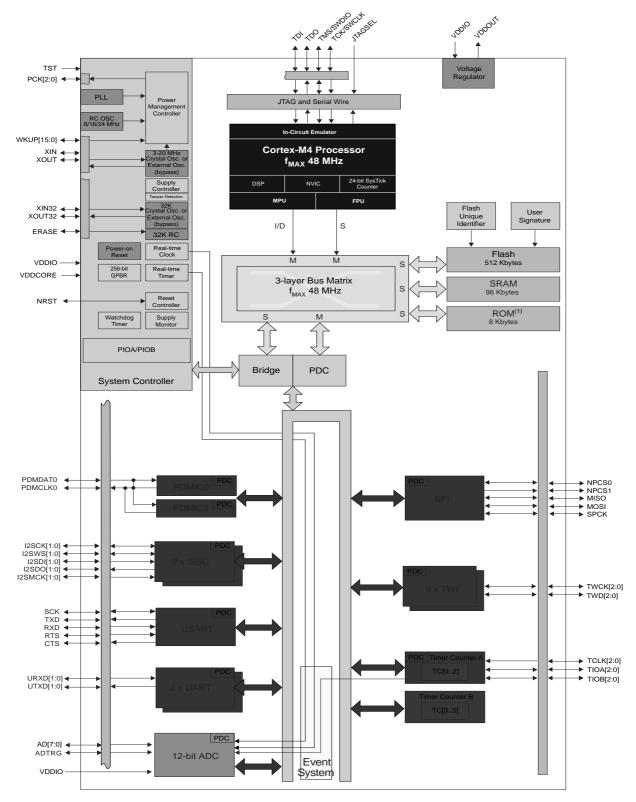

## 2. Block Diagram

#### Figure 2-1. SAM G53 Block Diagram

Note: 1. The ROM is reserved for future use.

## 3. Signal Description

Table 3-1 provides details on the signal names classified by peripheral.

| Table 3-1. | Signal Description List |

|------------|-------------------------|

|------------|-------------------------|

| Signal Name | Function                                                     | Туре        | Active<br>Level | Voltage<br>Reference | Comments                                                                                     |

|-------------|--------------------------------------------------------------|-------------|-----------------|----------------------|----------------------------------------------------------------------------------------------|

|             | Power Sup                                                    | plies       |                 |                      |                                                                                              |

| VDDIO       | Peripheral I/O Lines, Voltage Regulator,<br>ADC Power Supply | Power       | -               | _                    | 1.62V to 3.6V                                                                                |

| VDDOUT      | Voltage Regulator Output                                     | Power       | _               | _                    | -                                                                                            |

| VDDCORE     | Core Chip Power Supply                                       | Power       | -               | _                    | Connected externally to VDDOUT                                                               |

| GND         | Ground                                                       | Ground      | -               | _                    | -                                                                                            |

|             | Clocks, Oscillato                                            | rs and PLLs |                 |                      |                                                                                              |

| XIN         | Main Oscillator Input (Bypass mode)                          | Input       | _               | VDDIO                | Reset state:                                                                                 |

| XOUT        | Main Oscillator Output                                       | Output      | _               | _                    | - PIO input                                                                                  |

| XIN32       | Slow Clock Oscillator Input (Bypass mode)                    | Input       | -               | VDDIO                | - Internal pull-up<br>disabled                                                               |

| XOUT32      | Slow Clock Oscillator Output                                 | Output      | -               | _                    | - Schmitt Trigger<br>enabled                                                                 |

| PCK0 - PCK2 | Programmable Clock Output                                    | Output      | -               | -                    | Reset state:<br>- PIO input<br>- Internal pull-up<br>enabled<br>- Schmitt Trigger<br>enabled |

|             | ICE and J                                                    | TAG         |                 |                      |                                                                                              |

| ТСК         | Test Clock                                                   | Input       | _               | VDDIO                | No pull-up resistor                                                                          |

| TDI         | Test Data In                                                 | Input       | _               | VDDIO                | No pull-up resistor                                                                          |

| TDO         | Test Data Out                                                | Output      | _               | VDDIO                | -                                                                                            |

| TRACESWO    | Trace Asynchronous Data Out                                  | Output      | _               | VDDIO                | -                                                                                            |

| SWDIO       | Serial Wire Input/Output                                     | I/O         | _               | VDDIO                | -                                                                                            |

| SWCLK       | Serial Wire Clock                                            | Input       | -               | VDDIO                | -                                                                                            |

| TMS         | Test Mode Select                                             | Input       | -               | VDDIO                | No pull-up resistor                                                                          |

| JTAGSEL     | JTAG Selection                                               | Input       | High            | VDDIO                | Pull-down resistor                                                                           |

|             | Flash Mer                                                    | nory        |                 |                      |                                                                                              |

| ERASE       | Flash and NVM Configuration Bits Erase Command               | Input       | High            | VDDIO                | Pull-down (15 kΩ)<br>resistor                                                                |

| Signal Name | Function                          | Туре             | Active<br>Level | Voltage<br>Reference | Comments                                                       |

|-------------|-----------------------------------|------------------|-----------------|----------------------|----------------------------------------------------------------|

|             | Reset                             | /Test            |                 |                      |                                                                |

| NRST        | Microcontroller Reset             | I/O              | Low             | VDDIO                | Pull-up resistor                                               |

| TST         | Test Mode Select                  | Input            | _               | VDDIO                | Pull-down resistor                                             |

|             | Universal Ansynchronous Re        | eceiver Transco  | eiver - UAR     | Тх                   |                                                                |

| URXDx       | UART Receive Data                 | Input            | _               | -                    | -                                                              |

| UTXDx       | UART Transmit Data                | Output           | _               | -                    | -                                                              |

|             | PIO Controller                    | - PIOA - PIOB    |                 |                      |                                                                |

| PA0 - PA24  | Parallel I/O Controller A         | I/O              | _               | VDDIO                | Pulled-up input at<br>reset. No pull-down<br>for PA3/PA4/PA14. |

| PB0 - PB12  | Parallel I/O Controller B         | I/O              | _               | VDDIO                | Pulled-up input at reset                                       |

|             | Wake-u                            | p Pins           |                 |                      |                                                                |

| WKUP 0-15   | Wake-up Pin / External Interrupt  | I/O              | _               | VDDIO                | Wake-up pins are<br>used also as External<br>Interrupt         |

|             | Universal Synchronous Asynchron   | nous Receiver    | Transmitter     | USART                |                                                                |

| SCK         | USART Serial Clock                | I/O              | -               | -                    | -                                                              |

| TXD         | USART Transmit Data               | I/O              | -               | -                    | -                                                              |

| RXD         | USART Receive Data                | Input            | _               | -                    | -                                                              |

| RTS         | USART Request To Send             | Output           | -               | -                    | -                                                              |

| CTS         | USART Clear To Send               | Input            | _               | _                    | -                                                              |

|             | Timer/Cou                         | nter - TCx       |                 |                      |                                                                |

| TCLKx       | TC Channel x External Clock Input | Input            | _               | -                    | -                                                              |

| TIOAx       | TC Channel x I/O Line A           | I/O              | _               | _                    | -                                                              |

| TIOBx       | TC Channel x I/O Line B           | I/O              | _               | _                    | -                                                              |

|             | Serial Periphera                  | I Interface - SP | 1               |                      |                                                                |

| MISO        | Master In Slave Out               | I/O              | _               | -                    | -                                                              |

| MOSI        | Master Out Slave In               | I/O              | -               | -                    | -                                                              |

| SPCK        | SPI Serial Clock                  | I/O              | -               | _                    | High-speed pad                                                 |

| NPCS0       | SPI Peripheral Chip Select 0      | I/O              | Low             | _                    | _                                                              |

| NPCS1       | SPI Peripheral Chip Select 1      | Output           | Low             | _                    | -                                                              |

#### Table 3-1. Signal Description List (Continued)

#### Table 3-1. Signal Description List (Continued)

| Signal Name | Function                          | Туре        | Active<br>Level | Voltage<br>Reference | Comments                     |

|-------------|-----------------------------------|-------------|-----------------|----------------------|------------------------------|

|             | Two-Wire Inter                    | face- TWIx  |                 |                      |                              |

| TWDx        | TWIx Two-wire Serial Data         | I/O         | _               | _                    | High-speed pad for TWD0      |

| TWCKx       | TWIx Two-wire Serial Clock        | I/O         | _               | -                    | High-speed pad for<br>TWDCK0 |

|             | 10-bit Analog-to-Digital          | Converter - | ADCC            | •                    |                              |

| AD0 - AD7   | Analog Inputs                     | Analog      | _               | _                    | -                            |

| ADTRG       | ADC Trigger                       | Input       | _               | _                    | -                            |

|             | Inter-IC Sound Controller - I2SCx |             |                 |                      |                              |

| I2SMCKx     | I2SMCKx Master Clock Output       |             |                 |                      | -                            |

| I2SCKx      | Serial Clock                      | I/O         | _               | _                    | -                            |

| I2SWSx      | I2S Word Select                   | I/O         | _               | _                    | -                            |

| I2SDIx      | Serial Data Input                 | Input       | _               | _                    | -                            |

| I2SDOx      | Serial Data Output                | Output      | _               | _                    | -                            |

| PDMCLK0     | Pulse Density Modulation Clock    | Output      | _               | _                    | -                            |

| PDMDAT0     | Pulse Density Modulation Data     | Input       | -               | -                    | _                            |

## 4. Package and Pinout

| Table 4-1. | SAM G53 Packages |

|------------|------------------|

|------------|------------------|

| Device     | Package |

|------------|---------|

| SAM G53G19 | WLCSP49 |

| SAM G53N19 | LQFP100 |

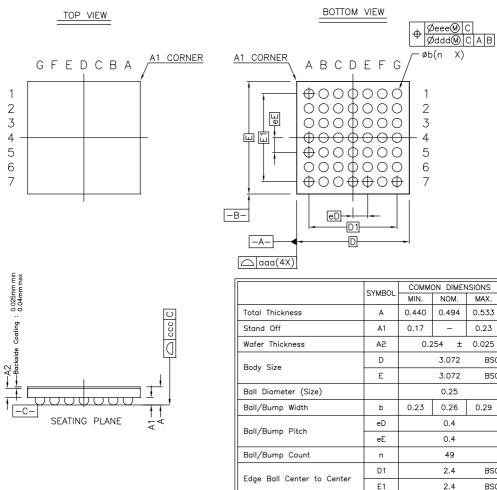

#### 4.1 49-ball WLCSP Pinout

#### Table 4-2. SAM G53G19 49-ball WLCSP Pinout

| A1 | PA9      | C1 |

|----|----------|----|

| A2 | GND      | C2 |

| A3 | PA24     | C3 |

| A4 | PB8/XOUT | C4 |

| A5 | PB9/XIN  | C5 |

| A6 | PB4      | C6 |

| A7 | VDDIO    | C7 |

| B1 | PB11     | D1 |

| B2 | PB5      | D2 |

| B3 | PB7      | D3 |

| B4 | PA2      | D4 |

| B5 | JTAGSEL  | D5 |

| B6 | NRST     | D6 |

| B7 | PB12     | D7 |

|    |          |    |

| C1 | VDDCORE |  |

|----|---------|--|

| C2 | PA11    |  |

| C3 | PA12    |  |

| C4 | PB6     |  |

| C5 | PA4     |  |

| C6 | PA3     |  |

| C7 | PA0     |  |

| D1 | PA13    |  |

| D2 | PB3/AD7 |  |

| D3 | PB1/AD5 |  |

| D4 | PB10    |  |

| D5 | PA1     |  |

| D6 | PA5     |  |

| D7 | VDDCORE |  |

|    |         |  |

| E1 | PB2/AD6    |  |  |

|----|------------|--|--|

| E2 | PB0/AD4    |  |  |

| E3 | PA18/AD1   |  |  |

| E4 | PA14       |  |  |

| E5 | PA10       |  |  |

| E6 | TST        |  |  |

| E7 | PA7/XIN32  |  |  |

| F1 | PA20/AD3   |  |  |

| F2 | PA19/AD2   |  |  |

| F3 | PA17/AD0   |  |  |

| F4 | PA21       |  |  |

| F5 | PA23       |  |  |

| F6 | PA16       |  |  |

| F7 | PA8/XOUT32 |  |  |

|    |            |  |  |

| G1 | VDDIO  |

|----|--------|

| G2 | VDDOUT |

| G3 | GND    |

| G4 | VDDIO  |

| G5 | PA22   |

| G6 | PA15   |

| G7 | PA6    |

## 4.2 100-lead LQFP Pinout

#### Table 4-3. SAM G53N19 100-pin LQFP Pinout

| 1  | NC    |  |  |  |  |  |  |

|----|-------|--|--|--|--|--|--|

| 2  | NC    |  |  |  |  |  |  |

| 3  | NC    |  |  |  |  |  |  |

| 4  | NC    |  |  |  |  |  |  |

| 5  | VDDIO |  |  |  |  |  |  |

| 6  | VDDIO |  |  |  |  |  |  |

| 7  | NRST  |  |  |  |  |  |  |

| 8  | PB12  |  |  |  |  |  |  |

| 9  | PA4   |  |  |  |  |  |  |

| 10 | PA3   |  |  |  |  |  |  |

| 11 | PA0   |  |  |  |  |  |  |

| 12 | PA1   |  |  |  |  |  |  |

| 13 | PA5   |  |  |  |  |  |  |

| -pin LQFP Pinout |       |  |  |  |

|------------------|-------|--|--|--|

| 26               | NC    |  |  |  |

| 27               | NC    |  |  |  |

| 28               | PA6   |  |  |  |

| 29               | VDDIO |  |  |  |

| 30               | PA16  |  |  |  |

| 31               | PA15  |  |  |  |

| 32               | PA23  |  |  |  |

| 33               | NC    |  |  |  |

| 34               | NC    |  |  |  |

| 35               | PA22  |  |  |  |

| 36               | PA21  |  |  |  |

| 37               | VDDIO |  |  |  |

| 38               | VDDIO |  |  |  |

|                  |       |  |  |  |

| 51 | NC    |

|----|-------|

| 52 | NC    |

| 53 | PA17  |

| 54 | PA18  |

| 55 | PA19  |

| 56 | PA20  |

| 57 | PB0   |

| 58 | PB1   |

| 59 | PB2   |

| 60 | PB3   |

| 61 | VDDIO |

| 62 | PA14  |

| 63 | PA13  |

|    |       |

| 76 | NC   |  |  |  |  |

|----|------|--|--|--|--|

| 77 | NC   |  |  |  |  |

| 78 | NC   |  |  |  |  |

| 79 | PA9  |  |  |  |  |

| 80 | PB5  |  |  |  |  |

| 81 | GND  |  |  |  |  |

| 82 | GND  |  |  |  |  |

| 83 | GND  |  |  |  |  |

| 84 | PB6  |  |  |  |  |

| 85 | PB7  |  |  |  |  |

| 86 | PA24 |  |  |  |  |

| 87 | PB8  |  |  |  |  |

| 88 | PB9  |  |  |  |  |

|    |      |  |  |  |  |

#### Table 4-3. SAM G53N19 100-pin LQFP Pinout

| 14 | VDDIO   |

|----|---------|

| 15 | VDDCORE |

| 16 | VDDCORE |

| 17 | TEST    |

| 18 | PA7     |

| 19 | PA8     |

| 20 | GND     |

| 21 | NC      |

| 22 | NC      |

| 23 | NC      |

| 24 | NC      |

| 25 | NC      |

| 39 | GND    |  |  |  |

|----|--------|--|--|--|

| 40 | GND    |  |  |  |

| 41 | GND    |  |  |  |

| 42 | GND    |  |  |  |

| 43 | GND    |  |  |  |

| 44 | VDDOUT |  |  |  |

| 45 | VDDOUT |  |  |  |

| 46 | VDDIO  |  |  |  |

| 47 | VDDIO  |  |  |  |

| 48 | VDDIO  |  |  |  |

| 49 | NC     |  |  |  |

| 50 | NC     |  |  |  |

| 64 | PA12    |

|----|---------|

| 65 | PA11    |

| 66 | VDDCORE |

| 67 | VDDCORE |

| 68 | PB10    |

| 69 | PB11    |

| 70 | GND     |

| 71 | GND     |

| 72 | PA10    |

| 73 | NC      |

| 74 | NC      |

| 75 | NC      |

| VDDIO   |  |  |  |  |

|---------|--|--|--|--|

| PA2     |  |  |  |  |

| PB4     |  |  |  |  |

| NC      |  |  |  |  |

| JTAGSEL |  |  |  |  |

| VDDIO   |  |  |  |  |

| VDDIO   |  |  |  |  |

| NC      |  |  |  |  |

|         |  |  |  |  |

#### **Mechanical Characteristics** 5.

#### 5.1 49-lead WLCSP Package

#### Figure 5-1. 49-lead WLCSP Package Mechanical Drawing

Package Edge Tolerance

Coplanarity (whole wafer)

Ball/Bump Offset (Ball)

Ball/Bump Offset (Package)

MAX

0.533

0.23

0.025

0.29

BSC

BSC

BSC

BSC

0.03

0.075

0.05

0.015

aaa

ccc

ddd

eee

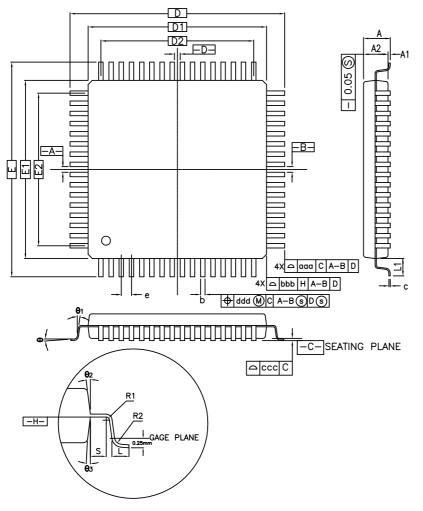

#### 5.2 100-lead LQFP Package

COTROL DIMENSIONS ARE IN MILLIMETERS.

| SYMPOL | MILLIMETER |             |      | INCH       |        |       |

|--------|------------|-------------|------|------------|--------|-------|

| SYMBOL | MIN. NOM.  |             | MAX. | MIN.       | NOM.   | MAX.  |

| A      | —          | _           | 1.60 | —          | —      | 0.063 |

| A1     | 0.05       |             | 0.15 | 0.002      |        | 0.006 |

| A2     | 1.35       | 1.40        | 1.45 | 0.053      | 0.055  | 0.057 |

| D      | 10         | 6.00 B      | SC.  | 0.         | 630 BS | SC.   |

| D1     | 1.         | 4.00 B      | SC.  | 0.551 BSC. |        |       |

| E      | 16.00 BSC. |             |      | 0.630 BSC. |        |       |

| E1     | 14.00 BSC. |             |      | 0.551 BSC. |        |       |

| R2     | 0.08       |             | 0.20 | 0.003      |        | 0.008 |

| R1     | 0.08       | —           | —    | 0.003      | —      | —     |

| θ      | 0*         | 3.5*        | 7'   | 0.         | 3.5*   | 7•    |

| θ1     | 0"         |             | —    | 0.         |        | —     |

| θε     | 11*        | 12          | 13   | 11.        | 12     | 13*   |

| θ₃     | 11•        | 12 <b>'</b> | 13   | 11.        | 12     | 13*   |

| с      | 0.09       |             | 0.20 | 0.004      |        | 0.008 |

| L      | 0.45       | 0.60        | 0.75 | 0.018      | 0.024  | 0.030 |

| L 1    | 1.00 REF   |             |      | 0.039 REF  |        |       |

| S      | 0.20       | _           |      | 0.008      | _      | —     |

|        | 100L      |                          |       |            |       |      |

|--------|-----------|--------------------------|-------|------------|-------|------|

| SYMBOL | М         | ILLIMET                  | ER    |            | INCH  |      |

|        | MIN.      | NOM.                     | MAX.  | MIN.       | NOM.  | MAX. |

| b      | 0.17      | ).17 0.20 0.27 0.007 0.0 | 0.008 | 0.011      |       |      |

| е      | 0.50 BSC. |                          |       | 0.020 BSC. |       |      |

| D2     | 12.00     |                          |       | 0.472      |       |      |

| E2     | 12.00     |                          |       | 0.472      |       |      |

| · · ·  |           |                          |       |            |       |      |

| aaa    | 0.20      |                          |       | (          | 3.008 |      |

| bbb    | 0.20      |                          |       |            | 800.0 |      |

| CCC    | 0.08      |                          | 0.003 |            |       |      |

| ddd    | 0.08      |                          |       |            | 0.003 |      |

## 6. Ordering Information

| Ordering Code    | MRL | Flash<br>(Kbytes) | Package | Carrier Type  | Package Type | Temperature<br>Operating Range |

|------------------|-----|-------------------|---------|---------------|--------------|--------------------------------|

| ATSAMG53G19A-UUT | А   | 512               | WLCSP49 | Tape and Reel | Green        | Industrial<br>-40°C to 85°C    |

| ATSAMG53N19A-AU  | А   | 512               | LQFP100 | Tray          | Green        | Industrial<br>-40°C to 85°C    |

| ATSAMG53G19B-UUT | В   | 512               | WLCSP49 | Tape and Reel | Green        | Industrial<br>-40°C to 85°C    |

| ATSAMG53N19B-AU  | В   | 512               | LQFP100 | Tray          | Green        | Industrial<br>-40°C to 85°C    |

Table 6-1.

Ordering Codes for SAM G53 Devices

## 7. Revision History

#### Table 7-1. SAM G53 Datasheet Rev. 11240ES Revision History

| Doc. Rev.<br>11240ES | Changes                                                       |

|----------------------|---------------------------------------------------------------|

|                      | Modified "Description" and "Features"                         |

| 27-Jul-15            | Updated Figure 2-1 "SAM G53 Block Diagram"                    |

|                      | Modified Table 3-1, "Signal Description List" (XIN and XIN32) |

#### Table 7-2. SAM G53 Datasheet Rev. 11240DS Revision History

| Doc. Rev.<br>11240DS | Changes                                                                                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                      | Updated document title on first page                                                                                            |

|                      | Modified operating range minimum value from 1.7V to 1.62V.                                                                      |

|                      | "Description"                                                                                                                   |

|                      | Added information about low-power modes and Event System.                                                                       |

|                      | "Features"                                                                                                                      |

| 17-Oct-14            | Added "on UART and TWI" to "Asynchronous partial wake-up (SleepWalking™)" in "Low power modes (typical value)"                  |

|                      | Corrected 4th line under "Peripherals" to read "Two UARTs" (was "Two two-wire UARTs")                                           |

|                      | Section 2. "Block Diagram"                                                                                                      |

|                      | Updated Figure 2-1 "SAM G53 Block Diagram"                                                                                      |

|                      | Section 6. "Ordering Information"                                                                                               |

|                      | Table 6-1, "Ordering Codes for SAM G53 Devices,": added ordering codes SAMG53G19B-UUT and SAMG53N19B-AU. Removed SAMG53N19A-AUT |

#### Table 7-3. SAM G53 Datasheet Rev. 11240CS Revision History

| Doc. Rev.<br>11240CS | Changes                                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04-Jun-14            | Updated document title on first page                                                                                                                                   |

|                      | Minor formatting changes throughout                                                                                                                                    |

|                      | Section 6. "Ordering Information"                                                                                                                                      |

|                      | Table 6-1, "Ordering Codes for SAM G53 Devices,": added prefix 'AT' to ordering codes; deleted "(Kbytes)" from<br>"Package" column header; added "Carrier Type" column |

Atmel

#### Table 7-4. SAM G53 Datasheet Rev. 11240BS Revision History

| Doc. Rev.<br>11240Bs | Changes                                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------------------|

| 06-May-14            | Operating voltage range changed to 1.70V to 3.6V throughout.                                              |

|                      | Figure 2-1 "SAM G53 Block Diagram": added VDDIO on ADC.                                                   |

|                      | Table 4-3, "SAM G53N19 100-pin LQFP Pinout,": corrected pin 92 to NC.                                     |

|                      | Figure 5-1 "49-lead WLCSP Package Mechanical Drawing": changed values for backside coating and for min of |

|                      | Total Thickness.                                                                                          |

#### Table 7-5. SAM G53 Datasheet Rev. 11240As Revision History

| Doc. Rev.<br>11240AS | Changes     |

|----------------------|-------------|

| 14-Jan-14            | First issue |

## Atmel Enabling Unlimited Possibilities

Т

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-11240ES-ATARM-SAM-G53G-SAM-G53N-Summary Datasheet\_27-Jul-15.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM<sup>®</sup>, ARM Connected<sup>®</sup> logo, and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL MEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR SAND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.