#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 10MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI                                                   |

| Peripherals                | LCD, POR, PWM, WDT                                                            |

| Number of I/O              | 55                                                                            |

| Program Memory Size        | 52KB (52K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-BQFP                                                                       |

| Supplier Device Package    | 80-QFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38076rh10v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8/38076R Group

# Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300H Super Low Power Series H8/38076RF H8/38076R H8/38075R

H8/38075R H8/38074R H8/38073R

Renesas Electronics

Rev.4.00 2006.08

| Document Title                            | Document No. |

|-------------------------------------------|--------------|

| F-ZTAT Microcomputer On-Board Programming | REJ05B0523   |

|         |                  |        | Coordinate |  |

|---------|------------------|--------|------------|--|

| Pad No. | Pad Name         | Χ (μm) | Υ (μm)     |  |

| 61      | P85/SEG30        | 2223   | 1987       |  |

| 62      | P86/SEG31        | 1987   | 2223       |  |

| 63      | P87/SEG32        | 1852   | 2223       |  |

| 64      | PB7/AN7          | 1483   | 2223       |  |

| 65      | PB6/AN6          | 1341   | 2223       |  |

| 66      | PB5/AN5          | 1150   | 2223       |  |

| 67      | PB4/AN4          | 941    | 2223       |  |

| 68      | PB3/AN3          | 732    | 2223       |  |

| 69      | PB2/AN2/IRQ3     | 523    | 2223       |  |

| 70      | PB1/AN1/IRQ1     | 314    | 2223       |  |

| 71      | PB0/AN0/IRQ0     | 105    | 2223       |  |

| 72      | AVcc             | -105   | 2223       |  |

| 73      | Vss/AVss         | -314   | 2223       |  |

| 74      | IRQAEC           | -523   | 2223       |  |

| 75      | P90/PWM1         | -732   | 2223       |  |

| 76      | P91/PWM2         | -941   | 2223       |  |

| 77      | P92/IRQ4         | -1150  | 2223       |  |

| 78      | P93              | -1360  | 2223       |  |

| 79      | P10/AEVH         | -1569  | 2223       |  |

| 80      | P11/AEVL         | -1778  | 2223       |  |

| 81      | P12/TIOCA1/TCLKA | -1987  | 2223       |  |

Note: The power supply (Vss) pads in pad numbers 12 and 13 must not be open but connected. When the TEST pad in pad number 16 is not used as the ADTRG pin, it must be connected to the Vss voltage level. If not, this LSI does not operate correctly.

When the TEST pad is used as the ADTRG pin, the function should be changed to the ADTRG pin at Vss voltage level during a reset in advance.

| Instruction | Size | Function        |                                                                                                              |                           |  |  |  |  |

|-------------|------|-----------------|--------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|

| Bcc*        |      |                 | Branches to a specified address if a specified condition is true. The branching conditions are listed below. |                           |  |  |  |  |

|             |      | Mnemonic        | Description                                                                                                  | Condition                 |  |  |  |  |

|             |      | BRA(BT)         | Always (true)                                                                                                | Always                    |  |  |  |  |

|             |      | BRN(BF)         | Never (false)                                                                                                | Never                     |  |  |  |  |

|             |      | BHI             | High                                                                                                         | $C \lor Z = 0$            |  |  |  |  |

|             |      | BLS             | Low or same                                                                                                  | C ∨ Z = 1                 |  |  |  |  |

|             |      | BCC(BHS)        | Carry clear<br>(high or same)                                                                                | C = 0                     |  |  |  |  |

|             |      | BCS(BLO)        | Carry set (low)                                                                                              | C = 1                     |  |  |  |  |

|             |      | BNE             | Not equal                                                                                                    | Z = 0                     |  |  |  |  |

|             |      | BEQ             | Equal                                                                                                        | Z = 1                     |  |  |  |  |

|             |      | BVC             | Overflow clear                                                                                               | V = 0                     |  |  |  |  |

|             |      | BVS             | Overflow set                                                                                                 | V = 1                     |  |  |  |  |

|             |      | BPL             | Plus                                                                                                         | N = 0                     |  |  |  |  |

|             |      | BMI             | Minus                                                                                                        | N = 1                     |  |  |  |  |

|             |      | BGE             | Greater or equal                                                                                             | $N \oplus V = 0$          |  |  |  |  |

|             |      | BLT             | Less than                                                                                                    | $N \oplus V = 1$          |  |  |  |  |

|             |      | BGT             | Greater than                                                                                                 | $Z \lor (N \oplus V) = 0$ |  |  |  |  |

|             |      | BLE             | Less or equal                                                                                                | $Z \vee (N \oplus V) = 1$ |  |  |  |  |

| JMP         |      | Branches unco   | nditionally to a specified                                                                                   | d address.                |  |  |  |  |

| BSR         |      | Branches to a s | subroutine at a specified                                                                                    | d address.                |  |  |  |  |

| JSR         |      | Branches to a s | subroutine at a specified                                                                                    | d address.                |  |  |  |  |

| RTS         |      | Returns from a  | subroutine                                                                                                   |                           |  |  |  |  |

# Table 2.7Branch Instructions

Note: \* Bcc is the general name for conditional branch instructions.

| Origin of<br>Interrupt Source | Name                          | Vector<br>Number | Vector Address | IPR          | Priority |

|-------------------------------|-------------------------------|------------------|----------------|--------------|----------|

| Reset                         | RES, Watchdog Timer           | 0                | H'0000         | _            | High     |

| NMI                           | NMI                           | 3                | H'0006         | _            | <b>≜</b> |

| Address break                 | Break conditions satisfied    | 5                | H'000A         | _            |          |

| External pins                 | IRQ0                          | 6                | H'000C         | IPRA7, IPRA6 | _        |

|                               | IRQ1                          | 7                | H'000E         | IPRA5, IPRA4 |          |

|                               | IRQAEC                        | 8                | H'0010         | IPRA3, IPRA2 | _        |

|                               | IRQ3                          | 9                | H'0012         | IPRA1, IPRA0 | _        |

|                               | IRQ4                          | 10               | H'0014         | _            |          |

|                               | WKP0                          | 11               | H'0016         | IPRB7, IPRB6 | _        |

|                               | WKP1                          | 12               | H'0018         | _            |          |

|                               | WKP2                          | 13               | H'001A         | _            |          |

|                               | WKP3                          | 14               | H'001C         | _            |          |

|                               | WKP4                          | 15               | H'001E         | _            |          |

|                               | WKP5                          | 16               | H'0020         | _            |          |

|                               | WKP6                          | 17               | H'0022         | _            |          |

|                               | WKP7                          | 18               | H'0024         | _            |          |

| RTC                           | 0.25-second overflow          | 19               | H'0026         | IPRB5, IPRB4 |          |

|                               | 0.5-second overflow           | 20               | H'0028         | _            |          |

|                               | Second periodic overflow      | 21               | H'002A         | _            |          |

|                               | Minute periodic overflow      | 22               | H'002C         | _            |          |

|                               | Hour periodic overflow        | 23               | H'002E         | _            |          |

|                               | Day-of-week periodic overflow | 24               | H'0030         | _            |          |

|                               | Week periodic overflow        | 25               | H'0032         | _            | <b>↓</b> |

|                               | Free-running overflow         | 26               | H'0034         | _            | Low      |

# Table 4.2 Interrupt Sources, Vector Addresses, and Interrupt Priorities

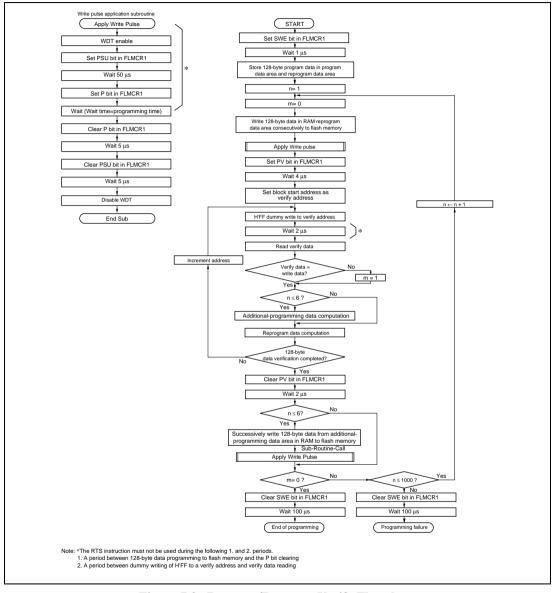

8. The maximum number of repetitions of the program/program-verify sequence of the same bit is 1,000.

Figure 7.3 Program/Program-Verify Flowchart

RENESAS

# 9.5.1 Port Data Register 6 (PDR6)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                          |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------|

| 7   | P67      | 0                | R/W | If port 6 is read while PCR6 bits are set to 1, the values                           |

| 6   | P66      | 0                | R/W | stored in PDR6 are read, regardless of the actual pin                                |

| 5   | P65      | 0                | R/W | states. If port 6 is read while PCR6 bits are cleared to 0, the pin states are read. |

| 4   | P64      | 0                | R/W |                                                                                      |

| 3   | P63      | 0                | R/W |                                                                                      |

| 2   | P62      | 0                | R/W |                                                                                      |

| 1   | P61      | 0                | R/W |                                                                                      |

| 0   | P60      | 0                | R/W |                                                                                      |

PDR6 is a register that stores data of port 6.

# 9.5.2 Port Control Register 6 (PCR6)

PCR6 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 6.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                    |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------|

| 7   | PCR67    | 0                | W   | Setting a PCR6 bit to 1 makes the corresponding pin an                                                         |

| 6   | PCR66    | 0                | W   | output pin, while clearing the bit to 0 makes the pin an                                                       |

| 5   | PCR65    | 0                | W   | input pin. The settings in PCR6 and in PDR6 are valid<br>when the corresponding pin is designated as a general |

| 4   | PCR64    | 0                | W   | I/O pin.                                                                                                       |

| 3   | PCR63    | 0                | W   | PCR6 is a write-only register. These bits are always                                                           |

| 2   | PCR62    | 0                | W   | read as 1.                                                                                                     |

| 1   | PCR61    | 0                | W   |                                                                                                                |

| 0   | PCR60    | 0                | W   |                                                                                                                |

# 9.7.1 Port Data Register 8 (PDR8)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                          |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------|

| 7   | P87      | 0                | R/W | If port 8 is read while PCR8 bits are set to 1, the values                           |

| 6   | P86      | 0                | R/W | stored in PDR8 are read, regardless of the actual pin                                |

| 5   | P85      | 0                | R/W | states. If port 8 is read while PCR8 bits are cleared to 0, the pin states are read. |

| 4   | P84      | 0                | R/W |                                                                                      |

| 3   | P83      | 0                | R/W |                                                                                      |

| 2   | P82      | 0                | R/W |                                                                                      |

| 1   | P81      | 0                | R/W |                                                                                      |

| 0   | P80      | 0                | R/W |                                                                                      |

PDR8 is a register that stores data of port 8.

# 9.7.2 Port Control Register 8 (PCR8)

PCR8 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 8.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                          |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------|

| 7   | PCR87    | 0                | W   | Setting a PCR8 bit to 1 makes the corresponding pin                                                  |

| 6   | PCR86    | 0                | W   | (P87 to P80) an output pin, while clearing the bit to 0                                              |

| 5   | PCR85    | 0                | W   | makes the pin an input pin. The settings in PCR8 and in PDR8 are valid when the corresponding pin is |

| 4   | PCR84    | 0                | W   | designated as a general I/O pin.                                                                     |

| 3   | PCR83    | 0                | W   | PCR8 is a write-only register. These bits are always                                                 |

| 2   | PCR82    | 0                | W   | read as 1.                                                                                           |

| 1   | PCR81    | 0                | W   |                                                                                                      |

| 0   | PCR80    | 0                | W   |                                                                                                      |

# 9.8.2 Port Control Register 9 (PCR9)

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                    |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------|

| 7 to 4 |          | All 1            |     | Reserved                                                                                                       |

|        |          |                  |     | These bits are always read as 1 and cannot be modified.                                                        |

| 3      | PCR93    | 0                | W   | Setting a PCR9 bit to 1 makes the corresponding pin an                                                         |

| 2      | PCR92    | 0                | W   | output pin, while clearing the bit to 0 makes the pin an                                                       |

| 1      | PCR91    | 0                | W   | input pin. The settings in PCR9 and in PDR9 are valid<br>when the corresponding pin is designated as a general |

| 0      | PCR90    | 0                | W   | I/O pin.                                                                                                       |

|        |          |                  |     | PCR9 is a write-only register. These bits are always read as 1.                                                |

PCR9 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 9.

# 9.8.3 Port Mode Register 9 (PMR9)

PMR9 controls the selection of functions for port 9 pins.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                         |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------|

| 7 to 4 | —        | All 1            | _   | Reserved                                                                            |

|        |          |                  |     | These bits are always read as 1 and cannot be modified.                             |

| 3      | _        | 0                | R/W | Reserved                                                                            |

|        |          |                  |     | Although this bit is readable/writable, 1 should not be written to this bit.        |

| 2      | IRQ4     | 0                | R/W | P92/IRQ4 Pin Function Switch                                                        |

|        |          |                  |     | Selects whether pin P92/ $\overline{IRQ4}$ is used as P92 or as $\overline{IRQ4}$ . |

|        |          |                  |     | 0: P92 I/O pin                                                                      |

|        |          |                  |     | 1: IRQ4 input pin                                                                   |

RENESAS

# • PB2/AN2/IRQ3 pin

The pin function is switched as shown below according to the combination of the CH3 to CH0 bits in AMR and IRQ3 bit in PMRB.

| IRQ3         | 0                    |               | 1              |

|--------------|----------------------|---------------|----------------|

| CH3 to CH0   | Other than<br>B'0110 | B'0110        | х              |

| Pin Function | PB2 input pin        | AN2 input pin | IRQ3 input pin |

[Legend] x: Don't care.

# • PB1/AN1/IRQ1 pin

The pin function is switched as shown below according to the combination of the CH3 to CH0 bits in AMR and IRQ1 bit in PMRB.

| IRQ1         | (                    | )             | 1              |

|--------------|----------------------|---------------|----------------|

| CH3 to CH0   | Other than<br>B'0101 | B'0101        | х              |

| Pin Function | PB1 input pin        | AN1 input pin | IRQ1 input pin |

[Legend] x: Don't care.

# • PB0/AN0/IRQ0 pin

The pin function is switched as shown below according to the combination of the CH3 to CH0 bits in AMR and IRQ0 bit in PMRB.

| IRQ0         | (                    | )             | 1              |  |  |

|--------------|----------------------|---------------|----------------|--|--|

| CH3 to CH0   | Other than<br>B'0100 | B'0100        | x              |  |  |

| Pin Function | PB0 input pin        | AN0 input pin | IRQ0 input pin |  |  |

[Legend] x: Don't care.

# **11.3** Register Descriptions

The timer F has the following registers.

- Timer counters FH and FL (TCFH, TCFL)

- Output compare registers FH and FL (OCRFH, OCRFL)

- Timer control register F (TCRF)

- Timer control/status register F (TCSRF)

# 11.3.1 Timer Counters FH and FL (TCFH, TCFL)

TCF is a 16-bit read/write up-counter configured by cascaded connection of 8-bit timer counters TCFH and TCFL. In addition to the use of TCF as a 16-bit counter with TCFH as the upper 8 bits and TCFL as the lower 8 bits, TCFH and TCFL can also be used as independent 8-bit counters.

TCFH and TCFL are initialized to H'00 upon a reset.

# (1) 16-Bit Mode (TCF)

When CKSH2 is cleared to 0 in TCRF, TCF operates as a 16-bit counter. The TCF input clock is selected by bits CKSL2 to CKSL0 in TCRF.

TCF can be cleared in the event of a compare match by means of CCLRH in TCSRF.

When TCF overflows from H'FFFF to H'0000, OVFH is set to 1 in TCSRF. If OVIEH in TCSRF is 1 at this time, IRRTFH is set to 1 in IRR2, and if IENTFH in IENR2 is 1, an interrupt request is sent to the CPU.

# (2) 8-Bit Mode (TCFH/TCFL)

When CKSH2 is set to 1 in TCRF, TCFH and TCFL operate as two independent 8-bit counters. The TCFH (TCFL) input clock is selected by bits CKSH2 to CKSH0 (CKSL2 to CKSL0) in TCRF.

TCFH (TCFL) can be cleared in the event of a compare match by means of CCLRH (CCLRL) in TCSRF.

When TCFH (TCFL) overflows from H'FF to H'00, OVFH (OVFL) is set to 1 in TCSRF. If OVIEH (OVIEL) in TCSRF is 1 at this time, IRRTFH (IRRTFL) is set to 1 in IRR2, and if IENTFH (IENTFL) in IENR2 is 1, an interrupt request is sent to the CPU.

| Bit | Bit Name | Initial<br>Value | R/W  | Description                                                                                                                                                                  |

|-----|----------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | OVIEH    | 0                | R/W  | Timer Overflow Interrupt Enable H                                                                                                                                            |

|     |          |                  |      | Selects enabling or disabling of interrupt generation when TCFH overflows.                                                                                                   |

|     |          |                  |      | 0: TCFH overflow interrupt request is disabled                                                                                                                               |

|     |          |                  |      | 1: TCFH overflow interrupt request is enabled                                                                                                                                |

| 4   | CCLRH    | 0                | R/W  | Counter Clear H                                                                                                                                                              |

|     |          |                  |      | In 16-bit mode, this bit selects whether TCF is cleared<br>when TCF and OCRF match. In 8-bit mode, this bit<br>selects whether TCFH is cleared when TCFH and<br>OCRFH match. |

|     |          |                  |      | In 16-bit mode:                                                                                                                                                              |

|     |          |                  |      | 0: TCF clearing by compare match is disabled                                                                                                                                 |

|     |          |                  |      | 1: TCF clearing by compare match is enabled                                                                                                                                  |

|     |          |                  |      | In 8-bit mode:                                                                                                                                                               |

|     |          |                  |      | 0: TCFH clearing by compare match is disabled                                                                                                                                |

|     |          |                  |      | 1: TCFH clearing by compare match is enabled                                                                                                                                 |

| 3   | OVFL     | 0                | R/W* | Timer Overflow Flag L                                                                                                                                                        |

|     |          |                  |      | This is a status flag indicating that TCFL has overflowed.                                                                                                                   |

|     |          |                  |      | [Setting condition]                                                                                                                                                          |

|     |          |                  |      | When TCFL overflows from H'FF to H'00                                                                                                                                        |

|     |          |                  |      | [Clearing condition]                                                                                                                                                         |

|     |          |                  |      | When this bit is written to 0 after reading OVFL = 1                                                                                                                         |

| 2   | CMFL     | 0                | R/W* | Compare Match Flag L                                                                                                                                                         |

|     |          |                  |      | This is a status flag indicating that TCFL has matched OCRFL.                                                                                                                |

|     |          |                  |      | [Setting condition]                                                                                                                                                          |

|     |          |                  |      | When the TCFL value matches the OCRFL value                                                                                                                                  |

|     |          |                  |      | [Clearing condition]                                                                                                                                                         |

|     |          |                  |      | When this bit is written to 0 after reading CMFL = 1                                                                                                                         |

# 12.8.3 Caution on Period Setting

When counter clearing on compare match is set, TCNT is cleared in the last state in which it matches the TGR value (the point at which the count value matched by TCNT is updated). Consequently, the actual counter frequency is given by the following formula:

$$f = \frac{\phi}{(N+1)}$$

Wheref: Counter frequency<br/>φ: Operating frequency<br/>N: TGR set value

# 12.8.4 Contention between TCNT Write and Clear Operation

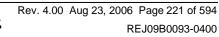

If the counter clear signal is generated in the T2 state of a TCNT write cycle, TCNT clearing takes priority and the TCNT write is not performed.

Figure 12.31 shows the timing in this case.

Figure 12.31 Contention between TCNT Write and Clear Operation

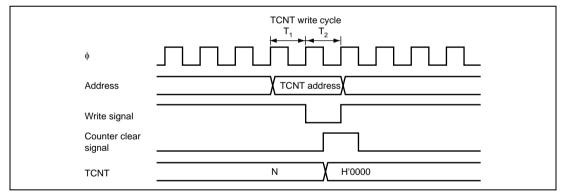

# 15.5 Operation in Clocked Synchronous Mode

Figure 15.9 shows the general format for clocked synchronous communication. In clocked synchronous mode, data is transmitted or received synchronous with clock pulses. A single character in the transmit data consists of the 8-bit data starting from the LSB. In clocked synchronous serial communication, data on the transmission line is output from one falling edge of the serial clock to the next. In clocked synchronous mode, the SCI3 receives data in synchronous with the rising edge of the serial clock. After 8-bit data is output, the transmission line holds the MSB state. In clocked synchronous mode, no parity or multiprocessor bit is added. Inside the SCI3, the transmitter and receiver are independent units, enabling full-duplex communication through the use of a common clock. Both the transmitter and the receiver also have a double-buffered structure, so data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 15.9 Data Format in Clocked Synchronous Communication

# 15.5.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external synchronization clock input at the SCK31 (SCK32) pin can be selected, according to the setting of the COM bit in SMR and CKE0 and CKE1 bits in SCR. When the SCI3 is operated on an internal clock, the serial clock is output from the SCK31 (SCK32) pin. Eight serial clock pulses are output in the transfer of one character, and when no transfer is performed the clock is fixed high.

# 15.5.2 SCI3 Initialization

Before transmitting and receiving data, the SCI3 should be initialized as described in a sample flowchart in figure 15.4.

# 16.3.3 Transmit Data Register 4 (TDR4)

TDR4 is an 8-bit register that stores data for serial transmission. When the SCI4 detects that SR4 is empty, it transfers the transmit data written in TDR4 to SR4 and starts serial transmission. If the next transmit data is written to TDR4 while serial data in SR4 is being transmitted, continuous serial transmission is possible. TDR4 can be read from or written to by the CPU at any time. TDR4 is initialized to H'FF.

# 16.3.4 Receive Data Register 4 (RDR4)

RDR4 is an 8-bit register that stores receive data. When the SCI4 has received one byte of serial data, it transfers the received serial data from SR4 to RDR4, where it is stored. Then receive operation is completed. After this, SR4 is receive-enabled. RDR4 cannot be written to by the CPU. RDR4 is initialized to H'00.

# 16.3.5 Shift Register 4 (SR4)

SR4 is a register that receives or transmits serial data. SR4 cannot be directly read from or written to by the CPU.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                        |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| 2      | CTRM2    | 0                | R/W | Variable Voltage Adjustment of 3-V Constant-Voltage                                                                |

| 1      | CTRM1    | 0                | R/W | Power Supply*                                                                                                      |

| 0      | CTRM0    | 0                | R/W | The LCD drive power supply adjusted by the TRM bits<br>can further be adjusted.                                    |

|        |          |                  |     | If an LCD panel does not function normally due to a temperature in which LCD is used, set these bits to adjust it. |

|        |          |                  |     | 000: ±0 V                                                                                                          |

|        |          |                  |     | 001: 0.09 V                                                                                                        |

|        |          |                  |     | 010: 0.18 V                                                                                                        |

|        |          |                  |     | 011: 0.27 V                                                                                                        |

|        |          |                  |     | 100: -0.36 V                                                                                                       |

|        |          |                  |     | 101: -0.27 V                                                                                                       |

|        |          |                  |     | 110: -0.18 V                                                                                                       |

| Natara |          |                  |     | 111: -0.09 V                                                                                                       |

Notes: Setting Method for LCD Trimming Register (LTRMR) Assuming the following definitions,

V1 initial state voltage: A

LTRMR register TRM3 to TRM0: B

CTRM2 to CTRM0: C

rough guidelines for the voltages after trimming are as follows:

V1 voltage = A + B + C

V2 voltage =  $(A + B + C) \times 2/3$

V3 voltage = (A + B + C) / 3

After monitoring voltage A, set B and C so the V1 voltage is 3 V.

\* These are approximate values and are not guaranteed. Therefore these values should be used as reference values.

Table 19.5 shows a output levels.

|          | Data           | 0      | 0      | 1   | 1   |

|----------|----------------|--------|--------|-----|-----|

|          | Μ              | 0      | 1      | 0   | 1   |

| Static   | Common output  | V1     | VSS    | V1  | VSS |

|          | Segment output | V1     | VSS    | VSS | V1  |

| 1/2 duty | Common output  | V2, V3 | V2, V3 | V1  | VSS |

|          | Segment output | V1     | VSS    | VSS | V1  |

| 1/3 duty | Common output  | V3     | V2     | V1  | VSS |

|          | Segment output | V2     | V3     | VSS | V1  |

| 1/4 duty | Common output  | V3     | V2     | V1  | VSS |

|          | Segment output | V2     | V3     | VSS | V1  |

### Table 19.5Output Levels

M: LCD alternation signal

# 19.4.3 3-V Constant-Voltage Power Supply Circuit

This LSI incorporates a 3-V constant-voltage power supply circuit consisting of a band gap reference circuit (BGR), a triple step-up circuit, etc. This allows the 3 V constant voltage to drive LCD driver independently of Vcc.

Before activating a step-up circuit, LCD controller/driver operates and set the duty cycle, pin function of the LCD driver or I/O, display data, frame frequencies, etc. Insert a capacitance of 0.1  $\mu$ F between the C1 pin and C2 pin, and connect a capacitance of 0.1  $\mu$ F to each of V1, V2, and V3 pins. (See figure 19.9.)

After this setting, setting the BGRSTPN bit in the BGR control register (BGRMR) to 1 activates the band gap reference circuit, generating 1 V constant voltage ( $V_{LCD3}$ ) at the V3 pin. Furthermore, selecting the step-up circuit clock of the LCD control register 2 (LCR2) and setting the SUPS bit to 1 activates the triple step-up circuit, generating 2 V constant voltage, twice  $V_{LCD3}$ , at the V2 pin, and generating 3 V constant voltage, triple  $V_{LCD3}$ , at the V1 pin.

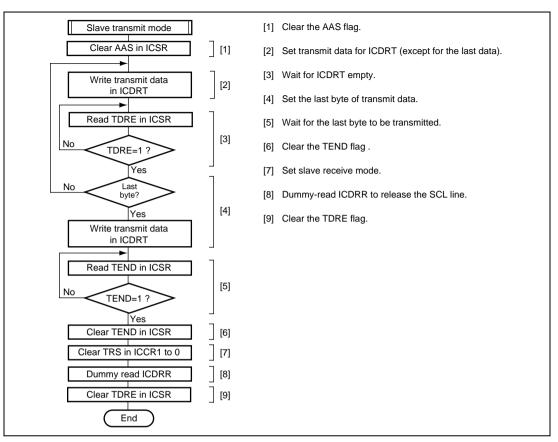

Figure 20.19 Sample Flowchart for Slave Transmit Mode

| Instruction | Mnemonic         | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| MULXS       | MULXS.B Rs, Rd   | 2                         |                           |                         |                          |                          | 12                         |

|             | MULXS.W Rs, ERd  | 2                         |                           |                         |                          |                          | 20                         |

| MULXU       | MULXU.B Rs, Rd   | 1                         |                           |                         |                          |                          | 12                         |

|             | MULXU.W Rs, ERd  | 1                         |                           |                         |                          |                          | 20                         |

| NEG         | NEG.B Rd         | 1                         |                           |                         |                          |                          |                            |

|             | NEG.W Rd         | 1                         |                           |                         |                          |                          |                            |

|             | NEG.L ERd        | 1                         |                           |                         |                          |                          |                            |

| NOP         | NOP              | 1                         |                           |                         |                          |                          |                            |

| NOT         | NOT.B Rd         | 1                         |                           |                         |                          |                          |                            |

|             | NOT.W Rd         | 1                         |                           |                         |                          |                          |                            |

|             | NOT.L ERd        | 1                         |                           |                         |                          |                          |                            |

| OR          | OR.B #xx:8, Rd   | 1                         |                           |                         |                          |                          |                            |

|             | OR.B Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | OR.W #xx:16, Rd  | 2                         |                           |                         |                          |                          |                            |

|             | OR.W Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | OR.L #xx:32, ERd | 3                         |                           |                         |                          |                          |                            |

|             | OR.L ERs, ERd    | 2                         |                           |                         |                          |                          |                            |

| ORC         | ORC #xx:8, CCR   | 1                         |                           |                         |                          |                          |                            |

| POP         | POP.W Rn         | 1                         |                           |                         |                          | 1                        | 2                          |

|             | POP.L ERn        | 2                         |                           |                         |                          | 2                        | 2                          |

| PUSH        | PUSH.W Rn        | 1                         |                           |                         |                          | 1                        | 2                          |

|             | PUSH.L ERn       | 2                         |                           |                         |                          | 2                        | 2                          |

| ROTL        | ROTL.B Rd        | 1                         |                           |                         |                          |                          |                            |

|             | ROTL.W Rd        | 1                         |                           |                         |                          |                          |                            |

|             | ROTL.L ERd       | 1                         |                           |                         |                          |                          |                            |

| ROTR        | ROTR.B Rd        | 1                         |                           |                         |                          |                          |                            |

|             | ROTR.W Rd        | 1                         |                           |                         |                          |                          |                            |

|             | ROTR.L ERd       | 1                         |                           |                         |                          |                          |                            |

| ROTXL       | ROTXL.B Rd       | 1                         |                           |                         |                          |                          |                            |

|             | ROTXL.W Rd       | 1                         |                           |                         |                          |                          |                            |

|             | ROTXL.L ERd      | 1                         |                           |                         |                          |                          |                            |

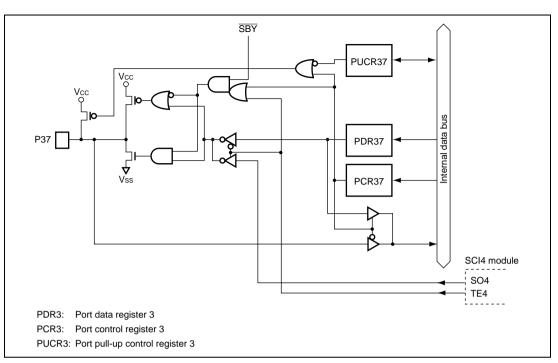

Figure B.2 (a) Port 3 Block Diagram (P37) (F-ZTAT Version)

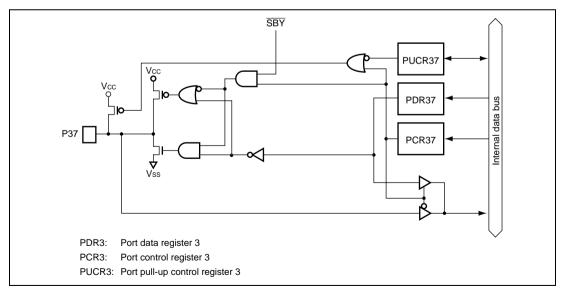

Figure B.2 (b) Port 3 Block Diagram (P37) (Masked ROM Version)

RENESAS