#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 4MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI                                                   |

| Peripherals                | LCD, POR, PWM, WDT                                                            |

| Number of I/O              | 55                                                                            |

| Program Memory Size        | 52KB (52K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | - ·                                                                           |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 85-TFLGA                                                                      |

| Supplier Device Package    | 85-TFLGA (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38076rlp4v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                                           | Page | Revisio                                                                                                                                                | on (S                                | ee Ma                                                | anı                               | ual for D                                            | Detai                 | ls)                                                   |                                         |                           |                                            |

|--------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|-----------------------------------|------------------------------------------------------|-----------------------|-------------------------------------------------------|-----------------------------------------|---------------------------|--------------------------------------------|

| 6.2 Mode Transitions                                                           | 116  | Note an                                                                                                                                                | nend                                 | ed                                                   |                                   |                                                      |                       |                                                       |                                         |                           |                                            |

| and States of LSI                                                              |      | A transition between different modes cannot be made to occur simply because an interrupt request is generated. Make sure to enable interrupt requests. |                                      |                                                      |                                   |                                                      |                       |                                                       |                                         |                           | le to occur                                |

| Figure 6.1 Mode<br>Transition Diagram                                          |      |                                                                                                                                                        |                                      |                                                      |                                   |                                                      |                       |                                                       |                                         |                           | ake sure to                                |

| Table 6.2 TransitionMode after SLEEPInstruction Executionand InterruptHandling | 118  |                                                                                                                                                        |                                      | MSON                                                 |                                   |                                                      | DTON                  | Exect                                                 | after<br>P Transi<br>Iction Mode        | due to                    | Symbol in<br>Figure 6.1                    |

|                                                                                |      | Active<br>(medium-<br>speed)<br>mode                                                                                                                   | 0                                    | 0                                                    | 0                                 | *                                                    | 1                     | Active<br>(high-<br>speed<br>mode<br>(direc<br>transi | l)<br>t                                 |                           | I                                          |

|                                                                                |      |                                                                                                                                                        | 0                                    | 1                                                    | 0                                 | *                                                    | 1                     | Active<br>(medi<br>speec<br>mode<br>(direc<br>transi  | um-<br>I)<br>t                          |                           |                                            |

| Table 6.3 Internal<br>State in Each<br>Operating Mode                          | 120  | Note an                                                                                                                                                | mend                                 | ed                                                   |                                   |                                                      | Suba                  |                                                       | Subsleep<br>Mode                        | Standby<br>Mode           | ,                                          |

|                                                                                |      | Function<br>Peripheral<br>modules                                                                                                                      | RTC                                  |                                                      |                                   | Watch Mode<br>Functioning/<br>retained* <sup>9</sup> |                       | ioning/                                               | Functioning/<br>retained*9              | Function<br>retained      |                                            |

|                                                                                |      | modules                                                                                                                                                | Asynch<br>event c                    |                                                      | - !-                              | Functioning*                                         |                       | tioning                                               | Functioning                             | Function                  |                                            |

|                                                                                |      |                                                                                                                                                        | Timer F                              |                                                      |                                   | Functioning/<br>retained*7                           | Funct<br>etaine       |                                                       | Functioning/<br>retained*7              | Retained                  | 1                                          |

|                                                                                |      |                                                                                                                                                        | TPU                                  |                                                      |                                   | Retained                                             | Retai                 | ned                                                   | Retained                                | Retained                  | 1                                          |

|                                                                                |      |                                                                                                                                                        | WDT                                  |                                                      |                                   | Functioning <sup>*®</sup> /<br>retained              | Functi<br>retaine     | ioning* <sup>8</sup> /<br>ed                          | Functioning* <sup>8</sup> /<br>retained | Functionii<br>retained    | ng* <sup>®</sup> /                         |

|                                                                                |      |                                                                                                                                                        | SCI3/Irl                             | DA                                                   |                                   | Reset                                                | Funct<br>retain       | tioning/<br>ied* <sup>2</sup>                         | Functioning/<br>retained* <sup>2</sup>  | Reset                     |                                            |

|                                                                                |      | overflov<br>7. Fund<br>retained<br>8. Fund<br>9. Fund                                                                                                  | w inte<br>tionir<br>d othe<br>tionir | errupts<br>ng if ø<br>erwise<br>ng if th<br>ng if th | s oj<br>w/2<br>e.<br>ne o<br>ne i | perate.<br>I is sele<br>pn-chip<br>nternal           | cted<br>oscil<br>time | as a<br>lator<br>keep                                 | n interna<br>is select<br>ping time     | al clock<br>ted.<br>-base | ECL/ECH and<br>. Halted and<br>function is |

|                                                                                |      | selecte                                                                                                                                                | d and                                | l retai                                              | ne                                | d if the i                                           | nterv                 | /al tir                                               | ner is se                               | lected                    |                                            |

Rev. 4.00 Aug 23, 2006 Page xvi of Ixxii

#### Page Revision (See Manual for Details)

| Item                                                         | Page | Revisio               | n (Se                                                                                               | e Ma                                                                                                                                                  | nua                                                                                              | l for                                           | Detai                  | ls)                     |                     |              |       |       |              |

|--------------------------------------------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|-------------------------|---------------------|--------------|-------|-------|--------------|

| 15.3.8 Bit Rate                                              | 322  | Table a               | mend                                                                                                | ed                                                                                                                                                    |                                                                                                  |                                                 |                        |                         |                     |              |       |       |              |

| Register (BRR)                                               |      | 4.9152MHz             |                                                                                                     |                                                                                                                                                       | 5MHz                                                                                             |                                                 |                        |                         | 6MI                 | Hz           |       | 6.144 | MHz          |

| Table 15.3                                                   |      | Bit Rate<br>(bit/s) n | N                                                                                                   | Error<br>(%)                                                                                                                                          | n                                                                                                | N                                               | Error<br>(%)           |                         | N                   | Error<br>(%) | n     | N     | Error<br>(%) |

| Examples of BRR                                              |      | 110 2                 | 86                                                                                                  | 0.31                                                                                                                                                  | 2                                                                                                | 88                                              | -0.25                  | 2                       | 106                 | -0.44        | 2     | 108   | 0.08         |

| Settings for Various                                         |      | 150 3                 | 15                                                                                                  | 0.00                                                                                                                                                  | 2                                                                                                | 64                                              | 0.16                   | 2                       | 77                  | 0.16         | 3     | 19    | 0.00         |

| Bit Rates                                                    |      | 200 3                 | 11                                                                                                  | 0.00                                                                                                                                                  | 2                                                                                                | 48                                              | -0.35                  | 2                       | 58                  | -0.69        | 3     | 14    | 0.00         |

| (Asynchronous                                                |      | 250 2                 | 37                                                                                                  | 1.05                                                                                                                                                  | 2                                                                                                | 38                                              | 0.16                   | 2                       | 46                  | -0.27        | 3     | 11    | 0.00         |

| Mode) (3)                                                    |      | 300 3                 | 7                                                                                                   | 0.00                                                                                                                                                  | 2                                                                                                | 32                                              | -1.36                  | 2                       | 38                  | 0.16         | 3     | 9     | 0.00         |

|                                                              |      | 600 3                 | 3                                                                                                   | 0.00                                                                                                                                                  | 0                                                                                                | 255                                             | 1.73                   | 3                       | 4                   | -2.34        | 3     | 4     | 0.00         |

|                                                              |      | 1200 3                | 1                                                                                                   | 0.00                                                                                                                                                  | 0                                                                                                | 129                                             | 0.16                   | 0                       | 155                 | 0.16         | 2     | 9     | 0.00         |

| Table 15.5<br>Maximum Bit Rate                               | 324  | Table a               | mend                                                                                                |                                                                                                                                                       |                                                                                                  |                                                 |                        |                         |                     |              | Sett  | •     |              |

| for Each Frequency                                           |      | OSC (MHz)             |                                                                                                     |                                                                                                                                                       |                                                                                                  | Bit Rat                                         | te (bit/s)             |                         | n                   |              |       | N     |              |

| (Asynchronous                                                |      | 0.0328                |                                                                                                     | 512                                                                                                                                                   | _                                                                                                |                                                 |                        |                         | 0                   |              |       | 0     |              |

| Mode)                                                        |      | 0.0384                |                                                                                                     | 600                                                                                                                                                   |                                                                                                  |                                                 |                        |                         | 0                   |              |       | 0     |              |

|                                                              |      | 2                     |                                                                                                     | 625                                                                                                                                                   | 00                                                                                               |                                                 |                        |                         | 0                   |              |       | 0     |              |

| Table 15.6 BRR<br>Settings for Various<br>Bit Rates (Clocked | 325  |                       | Table amended<br>• 32.8 kHz 38.4 kHz 2 Mi                                                           |                                                                                                                                                       |                                                                                                  |                                                 |                        |                         |                     |              | 2 MHz | :     |              |

|                                                              |      | Bit Rate              |                                                                                                     | -                                                                                                                                                     | -                                                                                                |                                                 |                        |                         |                     |              |       |       |              |

| Synchronous Mode)                                            |      | (bit/s)               | n                                                                                                   | Ν                                                                                                                                                     | Erro                                                                                             | or (%)                                          | n                      | N                       | Error (%            | 5) n         | Ν     | Err   | or (%)       |

| (1)                                                          |      | 200                   | 0                                                                                                   | 20                                                                                                                                                    | -2.3                                                                                             | 8                                               | 0                      | 23                      | 0.00                | 2            | 15    | 5 0.1 | 6            |

| (-)                                                          |      | 250                   | 0                                                                                                   | 15                                                                                                                                                    | 2.50                                                                                             |                                                 | 0                      | 18                      | 1.05                | 2            | 12    | 4 0.0 | 0            |

|                                                              |      | 300                   | 0                                                                                                   | 13                                                                                                                                                    | -2.3                                                                                             | 8                                               | 0                      | 15                      | 0.00                | 2            | 103   | 3 0.1 | 6            |

|                                                              |      | 500                   | 0                                                                                                   | 7                                                                                                                                                     | 2.50                                                                                             |                                                 | -                      |                         | -                   | 2            | 62    | -0.   |              |

|                                                              |      | 1k                    | 0                                                                                                   | 3                                                                                                                                                     | 2.50                                                                                             |                                                 |                        |                         |                     | 2            | 30    | 0.8   | 1            |

| Table 15.6 BRR                                               | 326  | Table a               | nd no                                                                                               | te am                                                                                                                                                 | nend                                                                                             | ed                                              |                        |                         |                     |              |       |       |              |

| Settings for Various                                         |      | ф                     |                                                                                                     | 4                                                                                                                                                     | MHz                                                                                              |                                                 |                        | 8                       | MHz                 |              |       | 10 MH | z            |

| Bit Rates (Clocked                                           |      | Bit Rate              |                                                                                                     |                                                                                                                                                       |                                                                                                  |                                                 |                        | -                       |                     |              |       | -     |              |

| Synchronous Mode)                                            |      | (bit/s)               | n                                                                                                   | N                                                                                                                                                     | Erro                                                                                             | or (%)                                          | n                      | N                       | Error (%            | 5) n         | N     | Err   | or (%)       |

| (2)                                                          |      | 10k                   | 0                                                                                                   | 99                                                                                                                                                    | 0.00                                                                                             |                                                 | 0                      | 199                     | 0.00                | 2            | 15    | -2.   | 34           |

|                                                              |      | The                   | Active (m<br>Active (m<br>N =<br>Subactive<br>N =<br>Bit rat<br>BRR :<br>C: $\phi_{osc}$ v:<br>Baud | et in BRF<br>nedium-s<br>= $\frac{OS}{4 \times 2^2}$<br>e or subs<br>= $\frac{OS}{8 \times 2^2}$<br>te (bit/s)<br>setting for<br>alue (Hz<br>rate gen | R is give<br>speed/f<br>$\frac{SC}{2n \times B}$<br>sleep<br>$\frac{SC}{2n \times B}$<br>or bauc | en by th<br>nigh-spe<br>- 1<br>- 1<br>d rate ge | enerator (<br>ock numb | ng fo<br>eep (<br>0 ≤ I | rmula:<br>(medium-s | r 3)         |       | (5    |              |

| TT 1 1 10 0 |                                          |

|-------------|------------------------------------------|

| Table 19.2  | Duty Cycle and Common Function Selection |

| Table 19.3  | Segment Driver Selection                 |

| Table 19.4  | Frame Frequency Selection                |

| Table 19.5  | Output Levels                            |

| Table 19.6  | Power-Down Modes and Display Operation   |

| Section 20  | I <sup>2</sup> C Bus Interface 2 (IIC2)  |

| Table 20.1  | Pin Configuration                        |

| Table 20.2  | Transfer Rate                            |

| Table 20.2  | Interrupt Requests                       |

| Table 20.3  | Time for Monitoring SCL                  |

| 1000 20.4   | The for Montoning Self                   |

| Section 22  | Address Break                            |

| Table 22.1  | Access and Data Bus Used                 |

| Table 22.2  | Operating States of Address Break        |

|             |                                          |

| Section 24  | Electrical Characteristics               |

| Table 24.1  | Absolute Maximum Ratings                 |

| Table 24.2  | DC Characteristics                       |

| Table 24.3  | Control Signal Timing                    |

| Table 24.4  | Serial Interface Timing                  |

| Table 24.5  | I <sup>2</sup> C Bus Interface Timing    |

| Table 24.6  | A/D Converter Characteristics            |

| Table 24.7  | LCD Characteristics                      |

| Table 24.8  | Power-On Reset Circuit Characteristics   |

| Table 24.9  | Watchdog Timer Characteristics           |

| Table 24.10 | Flash Memory Characteristics             |

| Table 24.11 | Absolute Maximum Ratings                 |

| Table 24.12 | DC Characteristics                       |

| Table 24.13 | Control Signal Timing                    |

| Table 24.14 | Serial Interface Timing                  |

| Table 24.15 | I <sup>2</sup> C Bus Interface Timing    |

| Table 24.16 | A/D Converter Characteristics            |

| Table 24.17 | LCD Characteristics                      |

| Table 24.18 | Power-On Reset Circuit Characteristics   |

| Table 24.19 | Watchdog Timer Characteristics           |

| Table 24.20 | Recommended Crystal Resonators           |

| Table 24.21 | Recommended Ceramic Resonators           |

| Instructio | n Size*       | Function                                                                                                                                                                               |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND        | B/W/L         | $Rd \wedge Rs \rightarrow Rd$ , $Rd \wedge \#IMM \rightarrow Rd$<br>Performs a logical AND operation on a general register and another<br>general register or immediate data.          |

| OR         | B/W/L         | $Rd \lor Rs \rightarrow Rd$ , $Rd \lor \#IMM \rightarrow Rd$<br>Performs a logical OR operation on a general register and another<br>general register or immediate data.               |

| XOR        | B/W/L         | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus \#IMM \rightarrow Rd$<br>Performs a logical exclusive OR operation on a general register and<br>another general register or immediate data. |

| NOT        | B/W/L         | $\neg$ (Rd) $\rightarrow$ (Rd) Takes the one's complement (logical complement) of general register contents.                                                                           |

| Note: *    | Refers to the | operand size.                                                                                                                                                                          |

|            | B: Byte       |                                                                                                                                                                                        |

|            | W: Word       |                                                                                                                                                                                        |

|            | L: Longword   |                                                                                                                                                                                        |

### Table 2.4 Logic Operations Instructions

#### Table 2.5Shift Instructions

| Instructio | n Size*       | Function                                                   |

|------------|---------------|------------------------------------------------------------|

| SHAL       | B/W/L         | $Rd (shift) \rightarrow Rd$                                |

| SHAR       |               | Performs an arithmetic shift on general register contents. |

| SHLL       | B/W/L         | $Rd (shift) \rightarrow Rd$                                |

| SHLR       |               | Performs a logical shift on general register contents.     |

| ROTL       | B/W/L         | $Rd \text{ (rotate)} \rightarrow Rd$                       |

| ROTR       |               | Rotates general register contents.                         |

| ROTXL      | B/W/L         | Rd (rotate) $\rightarrow$ Rd                               |

| ROTXR      |               | Rotates general register contents through the carry flag.  |

| Note: *    | Refers to the | operand size.                                              |

|            | B: Byte       |                                                            |

|            | W: Word       |                                                            |

L: Longword

#### 4.6.2 Interrupt Response Times

Table 4.4 shows interrupt response times – the interval between generation of an interrupt request and execution of the first instruction in the interrupt handling routine.

Table 4.4

Interrupt Response Times (States)

| No. | Execution Status                                               | Number of States |

|-----|----------------------------------------------------------------|------------------|

| 1   | Interrupt mask level determination                             | 1 or 2*1         |

| 2   | Maximum number of wait states until executing instruction ends | 1 to 23          |

| 3   | PC, CCR stack                                                  | 4                |

| 4   | Vector fetch                                                   | 4                |

| 5   | Instruction fetch* <sup>2</sup>                                | 4                |

| 6   | Internal processing*3                                          | 4                |

|     | Total                                                          | 19 to 41         |

Notes: 1. One state for internal interrupts and two states for external interrupts.

2. Prefetch after interrupt acceptance and interrupt handling routine prefetch.

3. Internal processing after interrupt acceptance and internal processing after vector fetch.

#### (2) TCFL, OCRFL

In toggle output, TMOFL pin output is toggled when a compare match occurs. If a TCRF write by a MOV instruction and generation of the compare match signal occur simultaneously, TOLL data is output to the TMOFL pin as a result of the TCRF write.

If an OCRFL write and compare match signal generation occur simultaneously, the compare match signal is invalid. However, a compare match signal may or may not be generated when the written data and the counter value match. As the compare match signal is output in synchronization with the TCFL clock, a compare match will not result in compare match signal generation if the clock is stopped.

If a TCFL write and overflow signal output occur simultaneously, the overflow signal is not output.

#### 11.6.3 Flag Clearing

When  $\phi_w/4$  is selected as the internal clock, "Interrupt source generation signal" will be operated with  $\phi_w$  and the signal will be outputted with  $\phi_w$  width. And, "Overflow signal" and "Compare match signal" are controlled with 2 cycles of  $\phi_w$  signals. Those signals are output with 2-cycle width of  $\phi_w$  (figure 11.3)

In active (high-speed, medium-speed) mode, even if you cleared interrupt request flag during the term of validity of "Interrupt source generation signal", same interrupt request flag is set. (1 in figure 11.3) And, the timer overflow flag and compare match flag cannot be cleared during the term of validity of "Overflow signal" and "Compare match signal".

For interrupt request flag is set right after interrupt request is cleared, interrupt process to one time timer FH, timer FL interrupt might be repeated. (2 in figure 11.3) Therefore, to definitely clear interrupt request flag in active (high-speed, medium-speed) mode, clear should be processed after the time that calculated with below (1) formula. And, to definitely clear timer overflow flag and compare match flag, clear should be processed after read timer control status register F (TCSRF) after the time that calculated with below (1) formula.

For ST of (1) formula, please substitute the longest number of execution states in used instruction.

In subactive mode, there are not limitation for interrupt request flag, timer overflow flag, and compare match flag clear.

## **12.3** Register Descriptions

The TPU has the following registers for each channel.

#### Channel 1:

- Timer control register\_1 (TCR\_1)

- Timer mode register\_1 (TMDR\_1)

- Timer I/O control register\_1 (TIOR\_1)

- Timer interrupt enable register\_1 (TIER\_1)

- Timer status register\_1 (TSR\_1)

- Timer counter\_1 (TCNT\_1)

- Timer general register A\_1 (TGRA\_1)

- Timer general register B\_1 (TGRB\_1)

### Channel 2:

- Timer control register\_2 (TCR\_2)

- Timer mode register\_2 (TMDR\_2)

- Timer I/O control register\_2 (TIOR\_2)

- Timer interrupt enable register\_2 (TIER\_2)

- Timer status register\_2 (TSR\_2)

- Timer counter\_2 (TCNT\_2)

- Timer general register A\_2 (TGRA\_2)

- Timer general register B\_2 (TGRB\_2)

#### Common:

- Timer start register (TSTR)

- Timer synchro register (TSYR)

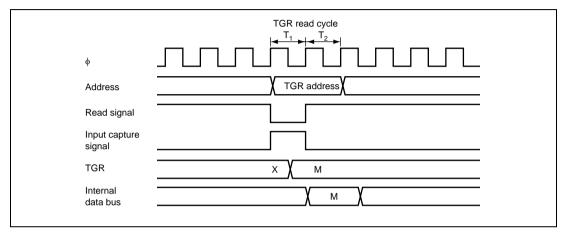

#### 12.8.7 Contention between TGR Read and Input Capture

If an input capture signal is generated in the T1 state of a TGR read cycle, data that is read will be data after input capture transfer.

Figure 12.34 shows the timing in this case.

Figure 12.34 Contention between TGR Read and Input Capture

# 15.2 Input/Output Pins

Table 15.2 shows the SCI3 pin configuration.

#### Table 15.2 Pin Configuration

| Pin Name                   | Abbreviati<br>on | I/O    | Function                  |  |

|----------------------------|------------------|--------|---------------------------|--|

| SCI3 clock                 | SCK31,<br>SCK32  | I/O    | SCI3 clock input/output   |  |

| SCI3 receive data<br>input | RXD31,<br>RXD32  | Input  | SCI3 receive data input   |  |

| SCI3 transmit data output  | TXD31,<br>TXD32  | Output | SCI3 transmit data output |  |

## **15.3 Register Descriptions**

The SCI3 has the following registers for each channel.

- Receive shift register 3 (RSR3)\*

- Receive data register 3 (RDR3)\*

- Transmit shift register 3 (TSR3)\*

- Transmit data register 3 (TDR3)\*

- Serial mode register 3 (SMR3)\*

- Serial control register 3 (SCR3)\*

- Serial status register 3 (SSR3)\*

- Bit rate register 3 (BRR3)\*

- Serial port control register (SPCR)

- IrDA control register (IrCR)

- Note: \* These register names are abbreviated to RSR, RDR, TSR, TDR, SMR, SCR, SSR, and BRR in the text.

#### 15.3.6 Serial Control Register (SCR)

SCR enables or disables SCI3 transfer operations and interrupt requests, and selects the transfer clock source. For details on interrupt requests, refer to section 15.8, Interrupt Requests.

SCR is initialized to H'00 by a reset or in standby mode, watch mode, or module standby mode.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TIE      | 0                | R/W | Transmit Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          | -                |     | When this bit is set to 1, the TXI (TXI32) interrupt request is enabled. TXI (TXI32) can be released by clearing the TDRE it or TI bit to 0.                                                                                                                                                                                                                                                                  |

| 6   | RIE      | 0                | R/W | Receive Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | When this bit is set to 1, RXI and ERI interrupt requests are enabled.                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | RXI (RXI32) and ERI (ERI32) can be released by<br>clearing the RDRF bit or the FER, PER, or OER error<br>flag to 0, or by clearing the RIE bit to 0.                                                                                                                                                                                                                                                          |

| 5   | TE       | 0                | R/W | Transmit Enable                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | When this bit is set to 1, transmission is enabled. When<br>this bit is 0, the TDRE bit in SSR is fixed at 1. When<br>transmit data is written to TDR while this bit is 1, Bit<br>TDRE in SSR is cleared to 0 and serial data<br>tansmission is started. Be sure to carry out SMR<br>settings, and setting of bit SPC31 or SPC32 in SPCR,<br>to decide the transmission format before setting bit TE<br>to 1. |

| 4   | RE       | 0                | R/W | Receive Enable                                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | When this bit is set to 1, reception is enabled. In this state, serial data reception is started when a start bit is detected in asynchronous mode or serial clock input is detected in clocked synchronous mode. Be sure to carry out the SMR settings to decide the reception format before setting bit RE to 1.                                                                                            |

|     |          |                  |     | Note that the RDRF, FER, PER, and OER flags in SSR are not affected when bit RE is cleared to 0, and retain their previous state                                                                                                                                                                                                                                                                              |

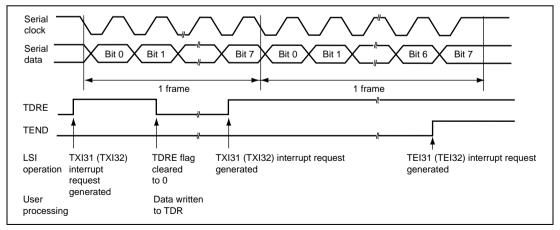

### 15.5.3 Serial Data Transmission

Figure 15.10 shows an example of SCI3 operation for transmission in clocked synchronous mode. In serial transmission, the SCI3 operates as described below.

- 1. The SCI3 monitors the TDRE flag in SSR, and if the flag is 0, the SCI recognizes that data has been written to TDR, and transfers the data from TDR to TSR.

- 2. The SCI3 sets the TDRE flag to 1 and starts transmission. If the TIE bit in SCR is set to 1 at this time, a TXI31 (TXI32) interrupt request is generated.

- 3. 8-bit data is sent from the TXD31 (TXD32) pin synchronized with the output clock when output clock mode has been specified, and synchronized with the input clock when use of an external clock has been specified. Serial data is transmitted sequentially from the LSB (bit 0), from the TXD31 (TXD32) pin.

- 4. The SCI checks the TDRE flag at the timing for sending the MSB (bit 7).

- 5. If the TDRE flag is cleared to 0, data is transferred from TDR to TSR, and serial transmission of the next frame is started.

- 6. If the TDRE flag is set to 1, the TEND flag in SSR is set to 1, and the TDRE flag maintains the output state of the last bit. If the TEIE bit in SCR is set to 1 at this time, a TEI31 (TEI32) is generated.

- 7. The SCK31 (SCK32) pin is fixed high.

Figure 15.11 shows a sample flowchart for serial data transmission. Even if the TDRE flag is cleared to 0, transmission will not start while a receive error flag (OER, FER, or PER) is set to 1. Make sure that the receive error flags are cleared to 0 before starting transmission.

Figure 15.10 Example of SCI3 Operation in Transmission in Clocked Synchronous Mode

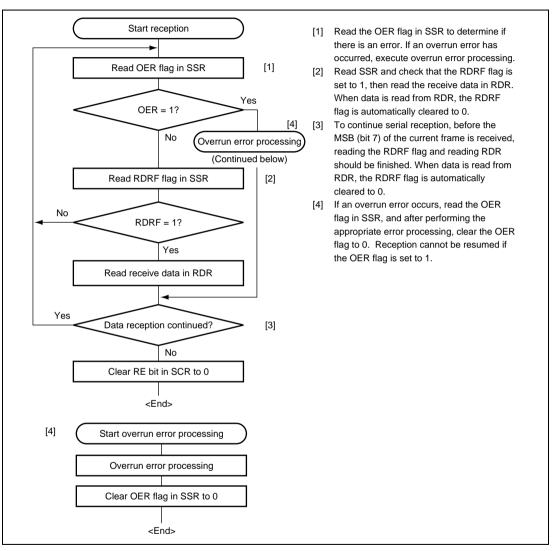

Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the OER, FER, PER, and RDRF bits to 0 before resuming reception. Figure 15.13 shows a sample flowchart for serial data reception.

Figure 15.13 Sample Serial Reception Flowchart (Clocked Synchronous Mode)

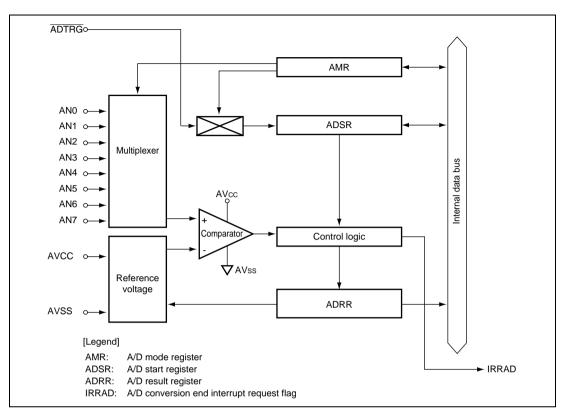

Figure 18.1 Block Diagram of A/D Converter

#### 24.2.2 DC Characteristics

Table 24.2 lists the DC characteristics.

#### Table 24.2 DC Characteristics

$V_{cc} = 1.8$  V to 3.6 V,  $AV_{cc} = 1.8$  V to 3.6 V,  $V_{ss} = AV_{ss} = 0.0$  V, unless otherwise specified.

|                       |                 |                                                                                                                                                                                                                            |                                 |                    | Valu | ies                    |      |       |

|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|------|------------------------|------|-------|

| ltem                  | Symbol          | Applicable Pins                                                                                                                                                                                                            | Test Condition                  | Min.               | Тур. | Max.                   | Unit | Notes |

| Input high<br>voltage | V <sub>iH</sub> | RES, NMI* <sup>3</sup> , WKP0<br>to WKP7, IRQ4,<br>AEVL, AEVH,<br>TMIF, ADTRG,<br>SCK32, SCK31,<br>SCK4                                                                                                                    |                                 | 0.9V <sub>cc</sub> | _    | V <sub>cc</sub> + 0.3  | V    |       |

|                       |                 | IRQ0, IRQ1, IRQ3                                                                                                                                                                                                           |                                 | 0.9V <sub>cc</sub> | _    | AV <sub>cc</sub> + 0.3 | _    |       |

|                       |                 | RXD32, RXD31                                                                                                                                                                                                               |                                 | 0.8V <sub>cc</sub> | _    | V <sub>cc</sub> + 0.3  |      |       |

|                       |                 | OSC1                                                                                                                                                                                                                       |                                 | $0.9V_{cc}$        | _    | V <sub>cc</sub> + 0.3  | _    |       |

|                       |                 | X1                                                                                                                                                                                                                         | $\rm V_{\rm cc}$ = 2.7 to 3.6 V | $0.9V_{cc}$        | —    | V <sub>cc</sub> + 0.3  |      |       |

|                       |                 | P10 to P16,<br>P30 to P32,<br>P36, P37,<br>P40 to P42,<br>P50 to P57,<br>P60 to P67,<br>P70 to P77,<br>P80 to P87,<br>P90 to P93,<br>PA0 to PA3,<br>TCLKA, TCLKB,<br>TCLKC, TIOCA1,<br>TIOCA2, TIOCB1,<br>TIOCB2, SCL, SDA |                                 | 0.8V <sub>cc</sub> | _    | V <sub>cc</sub> + 0.3  |      |       |

|                       |                 | PB0 to PB7                                                                                                                                                                                                                 |                                 | 0.8V <sub>cc</sub> | _    | AV <sub>cc</sub> + 0.3 | _    |       |

|                       |                 | IRQAEC                                                                                                                                                                                                                     |                                 | $0.9V_{\rm cc}$    | —    | V <sub>cc</sub> + 0.3  | _    |       |

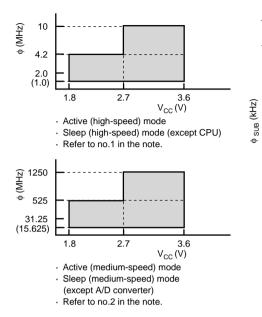

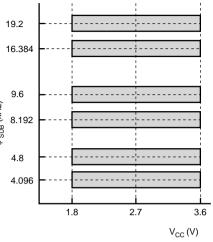

#### (2) Power Supply Voltage and Operating Frequency Range

· Subactive mode

· Subsleep mode (except CPU)

· Watch mode (except CPU)

- Notes: 1. The value in parentheses is the minimum operating frequency when an external clock is input. When using a resonator, the minimum operating frequency ( $\phi$ ) is 2 MHz.

- The value in parentheses is the minimum operating frequency when an external clock is input. When using a resonator, the minimum operating frequency (φ) is 31.25 kHz.

#### 24.4.2 DC Characteristics

Table 24.12 lists the DC characteristics.

#### Table 24.12 DC Characteristics

$V_{cc} = 1.8 \text{ V}$  to 3.6 V,  $AV_{cc} = 1.8 \text{ V}$  to 3.6 V,  $V_{ss} = AV_{ss} = 0.0 \text{ V}$ , unless otherwise specified.

|            |        |                   |                             |                    | Value | es                    |      |       |

|------------|--------|-------------------|-----------------------------|--------------------|-------|-----------------------|------|-------|

| Item       | Symbol | Applicable Pins   | Test Condition              | Min.               | Тур.  | Max.                  | Unit | Notes |

| Input high | V      | RES, NMI, WKPO to |                             | 0.9V <sub>cc</sub> | _     | V <sub>cc</sub> + 0.3 | V    |       |

| voltage    |        | WKP7, IRQ4,       |                             |                    |       |                       |      |       |

|            |        | AEVL, AEVH,       |                             |                    |       |                       |      |       |

|            |        | TMIF, ADTRG,      |                             |                    |       |                       |      |       |

|            |        | SCK32, SCK31      |                             |                    |       |                       |      |       |

|            |        | IRQ0, IRQ1, IRQ3  |                             | $0.9V_{\rm cc}$    | _     | $AV_{cc}$ + 0.3       | _    |       |

|            |        | RXD32, RXD31      |                             | $0.8V_{\rm cc}$    | —     | V <sub>cc</sub> + 0.3 |      |       |

|            |        | OSC1              |                             | $0.9V_{cc}$        | _     | V <sub>cc</sub> + 0.3 |      |       |

|            |        | X1                | $V_{\rm cc}$ = 2.7 to 3.6 V | $0.9V_{\rm cc}$    | _     | V <sub>cc</sub> + 0.3 | _    |       |

|            |        | P10 to P16,       |                             | $0.8V_{cc}$        | —     | V <sub>cc</sub> + 0.3 |      |       |

|            |        | P30 to P32,       |                             |                    |       |                       |      |       |

|            |        | P36, P37,         |                             |                    |       |                       |      |       |

|            |        | P40 to P42,       |                             |                    |       |                       |      |       |

|            |        | P50 to P57,       |                             |                    |       |                       |      |       |

|            |        | P60 to P67,       |                             |                    |       |                       |      |       |

|            |        | P70 to P77,       |                             |                    |       |                       |      |       |

|            |        | P80 to P87,       |                             |                    |       |                       |      |       |

|            |        | P90 to P93,       |                             |                    |       |                       |      |       |

|            |        | PA0 to PA3,       |                             |                    |       |                       |      |       |

|            |        | TCLKA, TCLKB,     |                             |                    |       |                       |      |       |

|            |        | TCLKC, TIOCA1,    |                             |                    |       |                       |      |       |

|            |        | TIOCA2, TIOCB1,   |                             |                    |       |                       |      |       |

|            |        | TIOCB2, SCL, SDA  |                             |                    |       |                       | _    |       |

|            |        | PB0 to PB7        |                             | $0.8V_{\rm cc}$    | _     | $AV_{cc}$ + 0.3       | _    |       |

|            |        | IRQAEC            |                             | $0.9V_{\rm cc}$    | _     | V <sub>cc</sub> + 0.3 |      |       |

#### 24.4.5 LCD Characteristics

Table 24.17 shows the LCD characteristics.

#### Table 24.17 LCD Characteristics

$V_{cc} = 1.8 \text{ V}$  to 3.6 V,  $AV_{cc} = 1.8 \text{ V}$  to 3.6 V,  $V_{ss} = AV_{ss} = 0.0 \text{ V}$ , unless otherwise specified.

|                                                                            |                  | Applicable       |                                                      |      | Values                            | 6    |      |                                                 |

|----------------------------------------------------------------------------|------------------|------------------|------------------------------------------------------|------|-----------------------------------|------|------|-------------------------------------------------|

| Item                                                                       | Symbol           | Pins             | Test Condition                                       | Min. | Тур.                              | Max. | Unit | Notes                                           |

| Segment driver drop voltage                                                | $V_{\rm ds}$     | SEG1 to<br>SEG32 | $I_{_{D}} = 2 \ \mu A$<br>V1 = 2.7 V to 3.6 V        | _    | _                                 | 0.6  | V    | *1                                              |

| Common driver drop<br>voltage                                              | V <sub>dc</sub>  | COM1 to<br>COM4  | $I_{_{D}} = 2 \ \mu A$<br>V1 = 2.7 V to 3.6 V        | -    | _                                 | 0.3  | V    | *1                                              |

| LCD power supply split-<br>resistance                                      | R                |                  | Between V1 and $\rm V_{ss}$                          | 1.5  | 3.0                               | 7.0  | MΩ   |                                                 |

| LCD display voltage                                                        | V                | V1               |                                                      | 2.2  | —                                 | 3.6  | V    | *2                                              |

| V3 power supply voltage                                                    | $V_{LCD3}$       | V3               | Between V3 and $\rm V_{ss}$                          | 0.9  | 1.0                               | 1.1  | V    | * <sup>3</sup> * <sup>4</sup>                   |

| V2 power supply voltage                                                    | $V_{LCD2}$       | V2               | Between V2 and $\mathrm{V}_{\mathrm{ss}}$            | _    | 2.0<br>(V <sub>LCD3</sub> ×<br>2) | _    | V    | * <sup>3</sup> * <sup>4</sup>                   |

| V1 power supply<br>voltage                                                 | $V_{LCD1}$       | V1               | Between V1 and $\rm V_{ss}$                          | _    | 3.0<br>(V <sub>LCD3</sub> ×<br>3) | -    | V    | *3*4                                            |

| 3-V constant voltage<br>LCD power supply<br>circuit current<br>consumption | I <sub>LCD</sub> | Vcc              | V <sub>cc</sub> = 3.0 V<br>Booster clock:<br>125 kHz | _    | 20                                | _    | μΑ   | Reference<br>value* <sup>4</sup> * <sup>5</sup> |

Notes: 1. The voltage drop from power supply pins V1, V2, V3, and V<sub>ss</sub> to each segment pin or common pin.

- 2. When the LCD display voltage is supplied from an external power source, ensure that the following relationship is maintained:  $V1 \ge V2 \ge V3 \ge V_{ss}$ .

- 3. The value when the LCD power supply split-resistor is separated and 3-V constant voltage power supply circuit is driven.

- 4. For details on the register (BGRMR) setting range when the voltage of the V3 pin is set to 1.0 V, refer to section 19.3.5, BGR Control Register (BGRMR).

- 5. Includes the current consumption of the band-gap reference circuit (BGR) (operation).

## Table A.1Instruction Set

#### 1. Data Transfer Instructions

|                                 |                        |              |        | Addressing Mode and<br>Instruction Length (bytes) |   |             |     |          |        |   |           |                                                       |                |    |        |            |          |   |          | No. of<br>States <sup>*1</sup> |  |

|---------------------------------|------------------------|--------------|--------|---------------------------------------------------|---|-------------|-----|----------|--------|---|-----------|-------------------------------------------------------|----------------|----|--------|------------|----------|---|----------|--------------------------------|--|

| Mnemonic<br>MOV MOV.B #xx:8, Rd |                        | Operand Size | #xx    | Rn<br>I, ERn)                                     |   | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa | - | Operation |                                                       | Condition Code |    |        |            |          |   | Advanced |                                |  |

|                                 |                        | в            | ₩<br>2 | ~                                                 | 0 | 0           | 0   | 0        | 0      | 0 |           | #xx:8 → Rd8                                           | 1              | н  | N<br>↓ | z<br>≎     | <b>v</b> | c | Normal   |                                |  |

| MOV                             | MOV.B Rs, Rd           | В            | ~      | 2                                                 |   |             |     |          |        |   |           | $Rs8 \rightarrow Rd8$                                 | 1_             | 1_ | ↓      | 1          | 0        | _ | 2        |                                |  |

|                                 | MOV.B @ERs, Rd         | В            |        | -                                                 | 2 |             |     |          |        |   |           | $@ERs \rightarrow Rd8$                                | _              | _  | ↓      | 1          | 0        | _ | 4        |                                |  |

|                                 | MOV.B @(d:16, ERs), Rd | В            |        |                                                   | - | 4           |     |          |        |   |           | $@(d:16, ERs) \rightarrow Rd8$                        | -              | 1_ | ↓      | 1          | 0        | _ | 6        |                                |  |

|                                 | MOV.B @(d:24, ERs), Rd | В            |        |                                                   |   | 8           |     |          |        |   |           | $@(d:24, ERs) \rightarrow Rd8$                        | 1_             | 1_ | \$     | 1          | 0        | _ | 10       |                                |  |

|                                 | MOV.B @ERs+, Rd        | в            |        |                                                   |   | _           | 2   |          |        |   |           | @ERs → Rd8<br>ERs32+1 → ERs32                         | -              | -  | \$     | \$         | 0        | - | 6        |                                |  |

|                                 | MOV.B @aa:8, Rd        | В            |        |                                                   |   |             |     | 2        |        |   |           | $@aa:8 \rightarrow Rd8$                               | -              | -  | \$     | \$         | 0        | — | 4        |                                |  |

|                                 | MOV.B @aa:16, Rd       | в            |        |                                                   |   |             |     | 4        |        |   |           | @aa:16 → Rd8                                          | -              | 1- | \$     | \$         | 0        | — | 6        |                                |  |

|                                 | MOV.B @aa:24, Rd       | В            |        |                                                   |   |             |     | 6        |        |   |           | @aa:24 → Rd8                                          | -              | -  | \$     | \$         | 0        | — | 8        |                                |  |

|                                 | MOV.B Rs, @ERd         | В            |        |                                                   | 2 |             |     |          |        |   |           | $Rs8 \rightarrow @ERd$                                | -              | -  | \$     | \$         | 0        | — | 4        |                                |  |

|                                 | MOV.B Rs, @(d:16, ERd) | в            |        |                                                   |   | 4           |     |          |        |   |           | $Rs8 \rightarrow @(d:16, ERd)$                        | -              | -  | \$     | \$         | 0        | — | 6        | 3                              |  |

|                                 | MOV.B Rs, @(d:24, ERd) | В            |        |                                                   |   | 8           |     |          |        |   |           | $Rs8 \rightarrow @(d:24, ERd)$                        | -              | -  | \$     | \$         | 0        | — | 10       |                                |  |

|                                 | MOV.B Rs, @-ERd        | В            |        |                                                   |   |             | 2   |          |        |   |           | $ERd32-1 \rightarrow ERd32$<br>$Rs8 \rightarrow @ERd$ | -              | -  | \$     | \$         | 0        | — | 6        |                                |  |

|                                 | MOV.B Rs, @aa:8        | В            |        |                                                   |   |             |     | 2        |        |   |           | Rs8 → @aa:8                                           | -              | -  | \$     | \$         | 0        | — | 4        |                                |  |

|                                 | MOV.B Rs, @aa:16       | в            |        |                                                   |   |             |     | 4        |        |   |           | Rs8 → @aa:16                                          | -              | -  | \$     | \$         | 0        | — | 6        |                                |  |

|                                 | MOV.B Rs, @aa:24       | В            |        |                                                   |   |             |     | 6        |        |   |           | $Rs8 \rightarrow @aa:24$                              | -              | -  | \$     | \$         | 0        | — | 8        |                                |  |

|                                 | MOV.W #xx:16, Rd       | W            | 4      |                                                   |   |             |     |          |        |   |           | #xx:16 → Rd16                                         | -              | -  | \$     | \$         | 0        | — | 4        |                                |  |

|                                 | MOV.W Rs, Rd           | W            |        | 2                                                 |   |             |     |          |        |   |           | $Rs16 \rightarrow Rd16$                               | -              | -  | \$     | \$         | 0        | — | 2        |                                |  |

|                                 | MOV.W @ERs, Rd         | W            |        |                                                   | 2 |             |     |          |        |   |           | $@ERs \to Rd16$                                       | -              | -  | \$     | $\uparrow$ | 0        | — | 4        |                                |  |

|                                 | MOV.W @(d:16, ERs), Rd | W            |        |                                                   |   | 4           |     |          |        |   |           | $@(d:16, ERs) \rightarrow Rd16$                       | -              | -  | \$     | \$         | 0        | — | 6        |                                |  |

|                                 | MOV.W @(d:24, ERs), Rd | W            |        |                                                   |   | 8           |     |          |        |   |           | @(d:24, ERs) → Rd16                                   | -              | -  | \$     | \$         | 0        | — | 1        | 0                              |  |

|                                 | MOV.W @ERs+, Rd        | w            |        |                                                   |   |             | 2   |          |        |   |           | @ERs → Rd16<br>ERs32+2 → @ERd32                       | -              | -  | \$     | \$         | 0        | _ | 6        |                                |  |

|                                 | MOV.W @aa:16, Rd       | W            |        |                                                   |   |             |     | 4        |        |   |           | @aa:16 → Rd16                                         | -              | -  | \$     | \$         | 0        | — | 6        |                                |  |

|                                 | MOV.W @aa:24, Rd       | W            |        |                                                   |   |             |     | 6        |        |   |           | @aa:24 → Rd16                                         | -              | -  | \$     | \$         | 0        | — | 8        |                                |  |

|                                 | MOV.W Rs, @ERd         | W            |        |                                                   | 2 |             |     |          |        |   |           | $Rs16 \rightarrow @ERd$                               | -              | -  | \$     | \$         | 0        | — | 4        |                                |  |

|                                 | MOV.W Rs, @(d:16, ERd) | W            |        |                                                   |   | 4           |     |          |        |   |           | $Rs16 \rightarrow @(d:16, ERd)$                       | -              | -  | \$     | \$         | 0        | — | - 6      |                                |  |

|                                 | MOV.W Rs, @(d:24, ERd) | W            |        |                                                   |   | 8           |     |          |        |   |           | $Rs16 \rightarrow @(d:24, ERd)$                       | -              | -  | \$     | \$         | 0        | — | 1        | 0                              |  |

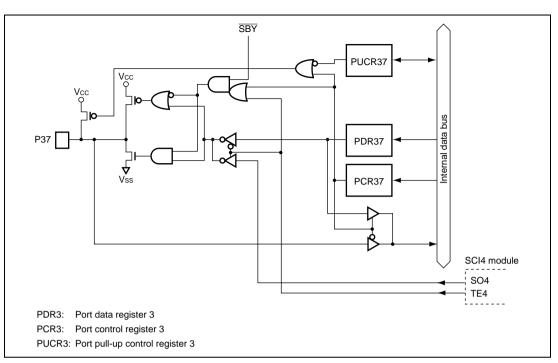

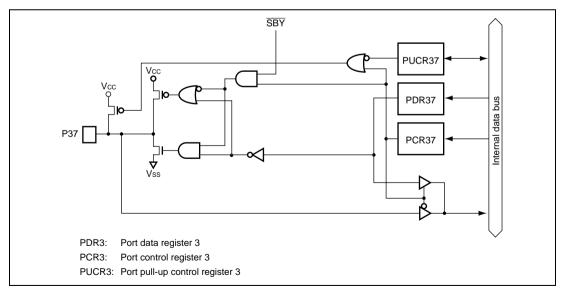

Figure B.2 (a) Port 3 Block Diagram (P37) (F-ZTAT Version)

Figure B.2 (b) Port 3 Block Diagram (P37) (Masked ROM Version)

## Renesas 16-Bit Single-Chip Microcomputer Hardware Manual H8/38076R Group

| Publication Date: | Rev.1.00, November 2003             |

|-------------------|-------------------------------------|

|                   | Rev.4.00, August 23, 2006           |

| Published by:     | Sales Strategic Planning Div.       |

|                   | Renesas Technology Corp.            |

| Edited by:        | Customer Support Department         |

|                   | Global Strategic Communication Div. |

|                   | Renesas Solutions Corp.             |

|                   |                                     |

©2006. Renesas Technology Corp., All rights reserved. Printed in Japan.