#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 10MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI                                                   |

| Peripherals                | LCD, POR, PWM, WDT                                                            |

| Number of I/O              | 55                                                                            |

| Program Memory Size        | 52KB (52K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38076rw10v |

|                            |                                                                               |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | 11.4.3           | TMOFH/TMOFL Output Timing            |     |

|--------------|------------------|--------------------------------------|-----|

|              | 11.4.4           | TCF Clear Timing                     |     |

|              | 11.4.5           | Timer Overflow Flag (OVF) Set Timing |     |

|              | 11.4.6           | Compare Match Flag Set Timing        |     |

| 11.5         | Timer            | F Operating States                   | 225 |

| 11.6         | Usage 1          | Notes                                | 226 |

|              | 11.6.1           | 16-Bit Timer Mode                    |     |

|              | 11.6.2           | 8-Bit Timer Mode                     |     |

|              | 11.6.3           | Flag Clearing                        |     |

|              | 11.6.4           | Timer Counter (TCF) Read/Write       | 229 |

| Sect         | on 10            | 16 Dit Timor Dulco Unit (TDU)        | 221 |

|              |                  | 16-Bit Timer Pulse Unit (TPU)        |     |

| 12.1<br>12.2 |                  | es<br>Dutput Pins                    |     |

| 12.2         | -                | er Descriptions                      |     |

| 12.5         | -                | •                                    |     |

|              |                  | Timer Control Register (TCR)         |     |

|              |                  | Timer Mode Register (TMDR)           |     |

|              | 12.3.3<br>12.3.4 |                                      |     |

|              |                  | Timer Status Register (TSR)          |     |

|              |                  | Timer Status Register (TSR)          |     |

|              |                  | Timer General Register (TGR)         |     |

|              |                  | Timer Start Register (TSTR)          |     |

|              |                  | Timer Synchro Register (TSTR)        |     |

| 12.4         |                  | ce to CPU                            |     |

| 12.4         | 12.4.1           |                                      |     |

|              |                  | 8-Bit Registers                      |     |

| 12.5         |                  | ion                                  |     |

| 12.5         | -                | Basic Functions                      |     |

|              |                  | Synchronous Operation                |     |

|              |                  | Operation with Cascaded Connection   |     |

|              |                  | PWM Modes                            |     |

| 12.6         |                  | pt Sources                           |     |

| 12.0         |                  | ion Timing                           |     |

| 12.7         | -                | Input/Output Timing                  |     |

|              |                  | Interrupt Signal Timing              |     |

| 12.8         |                  | Notes                                |     |

| 12.0         | -                | Module Standby Function Setting      |     |

|              |                  | Input Clock Restrictions             |     |

|              |                  | Caution on Period Setting            |     |

|              | 12.0.5           | Cuttion on I critical Southing       |     |

| Pad No.         Pad Name         X (µm)         Y (µm)           1         P13/TIOCB1/TCLKB         -2223         1797           2         P14/TIOCA2/TCLKC         -2223         1615           3         P15/TIOCB2         -2223         1434           4         P16/SCK4         -2223         1295           5         P30/SCK32/TMOW         -2223         941           7         P32/TXD32/SDA         -2223         941           7         P32/TXD32/SCL         -2223         523           9         P37/SO4         -2223         105           11         X2         -2223         -105           12         AVss         -2223         -314           13         Vss         -2223         -314           14         OSC2         -2223         -418           14         OSC2         -2223         -732           15         OSC1         -2223         -732           16         TEST/ADTRG         -2223         -1150           18         NMI         -2223         -1360           19         P40/SCK31/TMIF         -2223         -1360           19         P40/SCK31/TMOFH                                                                         |         |                       |        | Coordinate |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|--------|------------|--|

| 2         P14/TIOCA2/TCLKC         -2223         1615           3         P15/TIOCB2         -2223         1434           4         P16/SCK4         -2223         1295           5         P30/SCK32/TMOW         -2223         941           7         P32/TXD32/SDA         -2223         732           8         P36/SI4         -2223         523           9         P37/SO4         -2223         314           10         X1         -2223         105           11         X2         -2223         -314           13         Vss         -2223         -314           14         OSC2         -2223         -523           15         OSC1         -2223         -523           16         TEST/ADTRG         -2223         -1150           18         NMI         -2223         -1150           19         P40/SCK31/TMIF         -2223         -1150           21         P42/TXD31/IrTXD/TMOFL         -2223         -1160           19         P40/SCK31/TMIF         -2223         -1169           22         Vcc         -1987         -2223           23         C1 <t< th=""><th>Pad No.</th><th>Pad Name</th><th>X (μm)</th><th>Υ (μm)</th><th></th></t<> | Pad No. | Pad Name              | X (μm) | Υ (μm)     |  |

| 3       P15/TIOCB2       -2223       1434         4       P16/SCK4       -2223       1295         5       P30/SCK32/TMOW       -2223       941         7       P32/TXD32/SDA       -2223       941         7       P32/TXD32/SCL       -2223       523         9       P37/SO4       -2223       314         10       X1       -2223       105         11       X2       -2223       -105         12       AVss       -2223       -314         13       Vss       -2223       -523         14       OSC2       -2223       -523         15       OSC1       -2223       -523         16       TEST/ADTRG       -2223       -523         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrTXD/TMOFL       -2223       -1187         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223 <td>1</td> <td>P13/TIOCB1/TCLKB</td> <td>-2223</td> <td>1797</td> <td></td>                                                                                         | 1       | P13/TIOCB1/TCLKB      | -2223  | 1797       |  |

| 4       P16/SCK4       -2223       1295         5       P30/SCK32/TMOW       -2223       1150         6       P31/RXD32/SDA       -2223       941         7       P32/TXD32/SCL       -2223       732         8       P36/SI4       -2223       523         9       P37/SO4       -2223       314         10       X1       -2223       105         11       X2       -2223       -105         12       AVss       -2223       -314         13       Vss       -2223       -523         14       OSC2       -2223       -523         15       OSC1       -2223       -523         16       TEST/ADTRG       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223                                                                                                                                                                        | 2       | P14/TIOCA2/TCLKC      | -2223  | 1615       |  |

| 5         P30/SCK32/TMOW         -2223         1150           6         P31/RXD32/SDA         -2223         941           7         P32/TXD32/SCL         -2223         732           8         P36/SI4         -2223         523           9         P37/SO4         -2223         314           10         X1         -2223         105           11         X2         -2223         -105           12         AVss         -2223         -314           13         Vss         -2223         -523           14         OSC2         -2223         -523           15         OSC1         -2223         -523           16         TEST/ADTRG         -2223         -941           17         RES         -2223         -1150           18         NMI         -2223         -1360           19         P40/SCK31/TMIF         -2223         -1569           20         P41/RXD31/IrRXD/TMOFL         -2223         -1187           21         P42/TXD31/IrTXD/TMOFH         -2223         -1187           22         Vcc         -1987         -2223           23         C1         -17                                                                                  | 3       | P15/TIOCB2            | -2223  | 1434       |  |

| 6         P31/RXD32/SDA         -2223         941           7         P32/TXD32/SCL         -2223         732           8         P36/SI4         -2223         523           9         P37/SO4         -2223         314           10         X1         -2223         105           11         X2         -2223         -105           12         AVss         -2223         -314           13         Vss         -2223         -418           14         OSC2         -2223         -523           15         OSC1         -2223         -732           16         TEST/ADTRG         -2223         -941           17         RES         -2223         -1150           18         NMI         -2223         -1360           19         P40/SCK31/TMIF         -2223         -1569           20         P41/RXD31/IrXD/TMOFL         -2223         -1778           21         P42/TXD31/IrXD/TMOFH         -2223         -1987           22         Vcc         -1987         -2223           23         C1         -1775         -2223           24         C2         -1569                                                                                            | 4       | P16/SCK4              | -2223  | 1295       |  |

| 7       P32/TXD32/SCL       -2223       732         8       P36/SI4       -2223       523         9       P37/SO4       -2223       314         10       X1       -2223       105         11       X2       -2223       -105         12       AVss       -2223       -314         13       Vss       -2223       -418         14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -1150         18       NMI       -2223       -1150         18       NMI       -2223       -1160         19       P40/SCK31/TMIF       -2223       -1160         20       P41/RXD31/IrTXD/TMOFL       -2223       -1178         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27                                                                                                                                                                                  | 5       | P30/SCK32/TMOW        | -2223  | 1150       |  |

| 8         P36/SI4         -2223         523           9         P37/SO4         -2223         314           10         X1         -2223         105           11         X2         -2223         -105           12         AVss         -2223         -314           13         Vss         -2223         -418           14         OSC2         -2223         -523           15         OSC1         -2223         -732           16         TEST/ADTRG         -2223         -941           17         RES         -2223         -1150           18         NMI         -2223         -1360           19         P40/SCK31/TMIF         -2223         -1569           20         P41/RXD31/IrRXD/TMOFL         -2223         -1778           21         P42/TXD31/IrTXD/TMOFH         -2223         -1987           22         Vcc         -1987         -2223           23         C1         -1775         -2223           24         C2         -1569         -2223           25         V1         -1360         -2223           26         V2         -1150         -2223<                                                                                           | 6       | P31/RXD32/SDA         | -2223  | 941        |  |

| 9         P37/SO4         -2223         314           10         X1         -2223         105           11         X2         -2223         -105           12         AVss         -2223         -314           13         Vss         -2223         -418           14         OSC2         -2223         -523           15         OSC1         -2223         -732           16         TEST/ADTRG         -2223         -941           17         RES         -2223         -1150           18         NMI         -2223         -1150           18         NMI         -2223         -1160           19         P40/SCK31/TMIF         -2223         -1160           20         P41/RXD31/IrRXD/TMOFL         -2223         -1178           21         P42/TXD31/IrTXD/TMOFH         -2223         -1987           22         Vcc         -1987         -2223           23         C1         -1775         -2223           24         C2         -1569         -2223           25         V1         -1360         -2223           26         V2         -1150         -2223 </td <td>7</td> <td>P32/TXD32/SCL</td> <td>-2223</td> <td>732</td> <td></td>                | 7       | P32/TXD32/SCL         | -2223  | 732        |  |

| 10       X1       -2223       105         11       X2       -2223       -105         12       AVss       -2223       -314         13       Vss       -2223       -418         14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrXD/TMOFL       -2223       -1987         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                   | 8       | P36/SI4               | -2223  | 523        |  |

| 11       X2       -2223       -105         12       AVss       -2223       -314         13       Vss       -2223       -418         14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                            | 9       | P37/SO4               | -2223  | 314        |  |

| 12       AVss       -2223       -314         13       Vss       -2223       -418         14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                       | 10      | X1                    | -2223  | 105        |  |

| 13       Vss       -2223       -418         14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                    | 11      | X2                    | -2223  | -105       |  |

| 14       OSC2       -2223       -523         15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                | 12      | AVss                  | -2223  | -314       |  |

| 15       OSC1       -2223       -732         16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13      | Vss                   | -2223  | -418       |  |

| 16       TEST/ADTRG       -2223       -941         17       RES       -2223       -1150         18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14      | OSC2                  | -2223  | -523       |  |

| 17RES-2223-115018NMI-2223-136019P40/SCK31/TMIF-2223-156920P41/RXD31/IrRXD/TMOFL-2223-177821P42/TXD31/IrTXD/TMOFH-2223-198722Vcc-1987-222323C1-1775-222324C2-1569-222325V1-1360-222326V2-1150-222327V3-941-222328PA0/COM1-732-2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15      | OSC1                  | -2223  | -732       |  |

| 18       NMI       -2223       -1360         19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16      | TEST/ADTRG            | -2223  | -941       |  |

| 19       P40/SCK31/TMIF       -2223       -1569         20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17      | RES                   | -2223  | -1150      |  |

| 20       P41/RXD31/IrRXD/TMOFL       -2223       -1778         21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18      | NMI                   | -2223  | -1360      |  |

| 21       P42/TXD31/IrTXD/TMOFH       -2223       -1987         22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19      | P40/SCK31/TMIF        | -2223  | -1569      |  |

| 22       Vcc       -1987       -2223         23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20      | P41/RXD31/IrRXD/TMOFL | -2223  | -1778      |  |

| 23       C1       -1775       -2223         24       C2       -1569       -2223         25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21      | P42/TXD31/IrTXD/TMOFH | -2223  | -1987      |  |

| 24C2-1569-222325V1-1360-222326V2-1150-222327V3-941-222328PA0/COM1-732-2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22      | Vcc                   | -1987  | -2223      |  |

| 25       V1       -1360       -2223         26       V2       -1150       -2223         27       V3       -941       -2223         28       PA0/COM1       -732       -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23      | C1                    | -1775  | -2223      |  |

| 26         V2         -1150         -2223           27         V3         -941         -2223           28         PA0/COM1         -732         -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24      | C2                    | -1569  | -2223      |  |

| 27     V3     -941     -2223       28     PA0/COM1     -732     -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25      | V1                    | -1360  | -2223      |  |

| 28 PA0/COM1 -732 -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26      | V2                    | -1150  | -2223      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27      | V3                    | -941   | -2223      |  |

| 29 PA1/COM2 -523 -2223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28      | PA0/COM1              | -732   | -2223      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29      | PA1/COM2              | -523   | -2223      |  |

#### Table 1.2 Pad Coordinate of HCD64F38076R

| Instructio | on Size*                            | Function                                                                                                                                                                                  |

|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTE        | —                                   | Returns from an exception-handling routine.                                                                                                                                               |

| SLEEP      | —                                   | Causes a transition to a power-down state.                                                                                                                                                |

| LDC        | B/W                                 | $(EAs) \rightarrow CCR$<br>Moves the source operand contents to the CCR. The CCR size is one<br>byte, but in transfer from memory, data is read by word access.                           |

| STC        | B/W                                 | $CCR \rightarrow (EAd)$<br>Transfers the CCR contents to a destination location. The condition code register size is one byte, but in transfer to memory, data is written by word access. |

| ANDC       | В                                   | $CCR \land \#IMM \rightarrow CCR$<br>Logically ANDs the CCR with immediate data.                                                                                                          |

| ORC        | В                                   | $CCR \lor \#IMM \rightarrow CCR$<br>Logically ORs the CCR with immediate data.                                                                                                            |

| XORC       | В                                   | $CCR \oplus \#IMM \rightarrow CCR$<br>Logically XORs the CCR with immediate data.                                                                                                         |

| NOP        | —                                   | $PC + 2 \rightarrow PC$<br>Only increments the program counter.                                                                                                                           |

| Note: *    | Refers to the<br>B: Byte<br>W: Word | e operand size.                                                                                                                                                                           |

# Table 2.8 System Control Instructions

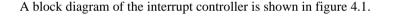

# Section 4 Interrupt Controller

# 4.1 Features

This LSI controls interrupts by the interrupt controller. The interrupt controller has the following features.

• Mask levels settable with IPR

An interrupt priority register (IPR) is provided for setting interrupt mask levels. Three mask levels can be set for each module for all interrupts except NMI and address break.

- Interrupts can be enabled or disabled in three levels by the INTM1 and INTM0 bits in the interrupt mask register (INTM).

- Fourteen external interrupts

NMI is the highest-priority interrupt, and is accepted at all times. Rising or falling edge sensing can be selected for NMI. Rising or falling edge sensing can be selected for IRQ0, IRQ1, IRQ3, IRQ4, and WKP0 to WKP7. Rising, falling, or both edge sensing can be selected for IRQAEC.

Figure 4.1 Block Diagram of Interrupt Controller

Rev. 4.00 Aug 23, 2006 Page 71 of 594 REJ09B0093-0400

RENESAS

#### 4.4.2 Internal Interrupts

Internal interrupts generated from the on-chip peripheral modules have the following features:

- For each on-chip peripheral module, there are flags that indicate the interrupt request status, and enable bits that select enabling or disabling of these interrupts. Internal interrupts can be controlled independently. If an enable bit is set to 1, an interrupt request is sent to the interrupt controller.

- The interrupt mask level can be set by IPR.

# 4.5 Interrupt Exception Handling Vector Table

Table 4.2 shows interrupt exception handling sources, vector addresses, and interrupt priorities. The lower the vector number, the higher the priority. The priority within a module is fixed. Mask levels for interrupts other than NMI and address break can be modified by IPR.

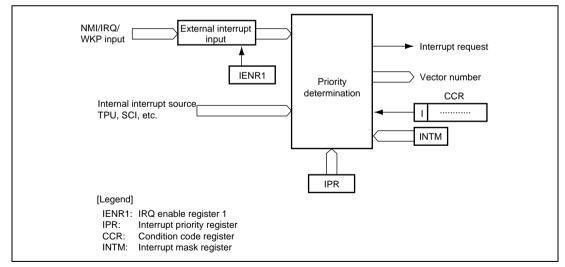

Figure 7.2 Programming/Erasing Flowchart Example in User Program Mode

## 9.1.1 Port Data Register 1 (PDR1)

| -   | <b></b>  | Initial | -   | <b>-</b>                                                                                                          |

|-----|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                       |

| 7   | —        | 1       | —   | If port 1 is read while PCR1 bits are set to 1, the values                                                        |

| 6   | P16      | 0       | R/W | stored in PDR1 are read, regardless of the actual pin states. If port 1 is read while PCR1 bits are cleared to 0, |

| 5   | P15      | 0       | R/W | the pin states are read.                                                                                          |

| 4   | P14      | 0       | R/W | Bit 7 is reserved. This bit is always read as 1 and cannot                                                        |

| 3   | P13      | 0       | R/W | be modified.                                                                                                      |

| 2   | P12      | 0       | R/W |                                                                                                                   |

| 1   | P11      | 0       | R/W |                                                                                                                   |

| 0   | P10      | 0       | R/W |                                                                                                                   |

PDR1 is a register that stores data of port 1.

#### 9.1.2 Port Control Register 1 (PCR1)

PCR1 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 1.

|     |          | Initial |     |                                                                                                                 |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                     |

| 7   | —        | 1       |     | Setting a PCR1 bit to 1 makes the corresponding pin                                                             |

| 6   | PCR16    | 0       | W   | (P16 to P10) an output pin, while clearing the bit to 0 makes the pin an input pin. The settings in PCR1 and in |

| 5   | PCR15    | 0       | W   | PDR1 are valid when the corresponding pin is                                                                    |

| 4   | PCR14    | 0       | W   | designated as a general I/O pin.                                                                                |

| 3   | PCR13    | 0       | W   | PCR1 is a write-only register. These bits are always                                                            |

| 2   | PCR12    | 0       | W   | read as 1.                                                                                                      |

| 1   | PCR11    | 0       | W   | Bit 7 is reserved. This bit cannot be modified.                                                                 |

| 0   | PCR10    | 0       | W   |                                                                                                                 |

## 9.7.1 Port Data Register 8 (PDR8)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                          |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------|

| 7   | P87      | 0                | R/W | If port 8 is read while PCR8 bits are set to 1, the values                           |

| 6   | P86      | 0                | R/W | stored in PDR8 are read, regardless of the actual pin                                |

| 5   | P85      | 0                | R/W | states. If port 8 is read while PCR8 bits are cleared to 0, the pin states are read. |

| 4   | P84      | 0                | R/W |                                                                                      |

| 3   | P83      | 0                | R/W |                                                                                      |

| 2   | P82      | 0                | R/W |                                                                                      |

| 1   | P81      | 0                | R/W |                                                                                      |

| 0   | P80      | 0                | R/W |                                                                                      |

PDR8 is a register that stores data of port 8.

#### 9.7.2 Port Control Register 8 (PCR8)

PCR8 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 8.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                          |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------|

| 7   | PCR87    | 0                | W   | Setting a PCR8 bit to 1 makes the corresponding pin                                                  |

| 6   | PCR86    | 0                | W   | (P87 to P80) an output pin, while clearing the bit to 0                                              |

| 5   | PCR85    | 0                | W   | makes the pin an input pin. The settings in PCR8 and in PDR8 are valid when the corresponding pin is |

| 4   | PCR84    | 0                | W   | designated as a general I/O pin.                                                                     |

| 3   | PCR83    | 0                | W   | PCR8 is a write-only register. These bits are always                                                 |

| 2   | PCR82    | 0                | W   | read as 1.                                                                                           |

| 1   | PCR81    | 0                | W   |                                                                                                      |

| 0   | PCR80    | 0                | W   |                                                                                                      |

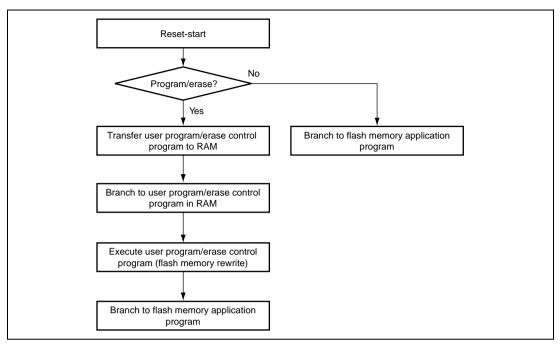

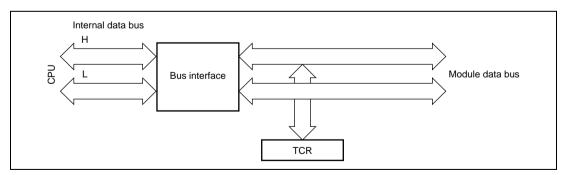

# **12.4** Interface to CPU

#### 12.4.1 16-Bit Registers

TCNT and TGR are 16-bit registers. As the data bus to the CPU is 16 bits wide, these registers cannot be read or written to in 8-bit units; 16-bit access must always be used.

An example of 16-bit register access operation is shown in figure 12.2.

Figure 12.2 16-Bit Register Access Operation [CPU ↔ TCNT (16 Bits)]

#### 12.4.2 8-Bit Registers

Registers other than TCNT and TGR are 8-bit. They can also be read and written to in 8-bit units.

Examples of 8-bit register access operation are shown in figures 12.3 and 12.4.

Figure 12.3 8-Bit Register Access Operation [CPU ↔ TCR (Upper 8 Bits)]

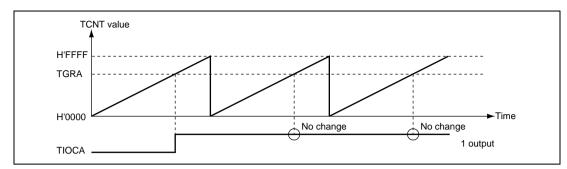

Figure 12.9 Example of 1 Output Operation

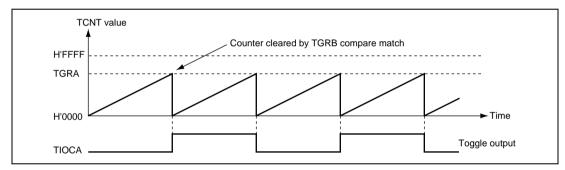

Figure 12.10 shows an example of toggle output.

In this example, TCNT has been designated as a periodic counter (with counter clearing on compare match A), and settings have been made such that the output is toggled by compare match A.

Figure 12.10 Example of Toggle Output Operation

#### (3) Input Capture Function

The TCNT value can be transferred to TGR on detection of the TIOC pin input edge.

Rising edge, falling edge, or both edges can be selected as the detected edge.

#### (a) Example of Input Capture Operation Setting Procedure

Figure 12.11 shows an example of the setting procedure for input capture operation.

#### 14.3.2 Interval Timer Mode

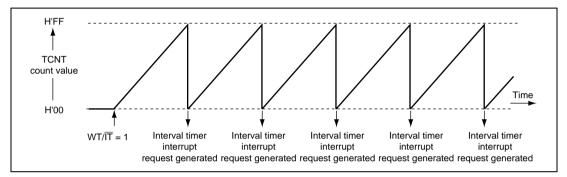

Figure 14.3 shows the operation in interval timer mode. To use the WDT as an interval timer, set the  $WT/\overline{IT}$  bit in TCSRWD2 to 1.

When the WDT is used as an interval timer, an interval timer interrupt request is generated each time the TCNT overflows. Therefore, an interval timer interrupt can be generated at intervals.

Figure 14.3 Interval Timer Mode Operation

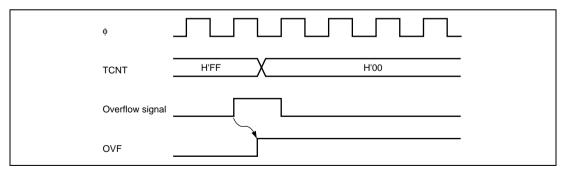

## 14.3.3 Timing of Overflow Flag (OVF) Setting

Figure 14.4 shows the timing of the OVF flag setting. The OVF flag in TCSRWD2 is set to 1 if TCNT overflows. At the same time, a reset signal is output in watchdog timer mode and an interval timer interrupt is generated in interval timer mode.

Figure 14.4 Timing of OVF Flag Setting

RENESAS

|                       | 4.9152MHz |    |              | 5MHz |     |              |   | 6MHz |              |   | 6.144MHz |              |  |

|-----------------------|-----------|----|--------------|------|-----|--------------|---|------|--------------|---|----------|--------------|--|

| Bit Rate<br>(bit/s) n |           | N  | Error<br>(%) | n    | N   | Error<br>(%) | n | N    | Error<br>(%) | n | N        | Error<br>(%) |  |

| 110                   | 2         | 86 | 0.31         | 2    | 88  | -0.25        | 2 | 106  | -0.44        | 2 | 108      | 0.08         |  |

| 150                   | 3         | 15 | 0.00         | 2    | 64  | 0.16         | 2 | 77   | 0.16         | 3 | 19       | 0.00         |  |

| 200                   | 3         | 11 | 0.00         | 2    | 48  | -0.35        | 2 | 58   | -0.69        | 3 | 14       | 0.00         |  |

| 250                   | 2         | 37 | 1.05         | 2    | 38  | 0.16         | 2 | 46   | -0.27        | 3 | 11       | 0.00         |  |

| 300                   | 3         | 7  | 0.00         | 2    | 32  | -1.36        | 2 | 38   | 0.16         | 3 | 9        | 0.00         |  |

| 600                   | 3         | 3  | 0.00         | 0    | 255 | 1.73         | 3 | 4    | -2.34        | 3 | 4        | 0.00         |  |

| 1200                  | 3         | 1  | 0.00         | 0    | 129 | 0.16         | 0 | 155  | 0.16         | 2 | 9        | 0.00         |  |

| 2400                  | 3         | 0  | 0.00         | 0    | 64  | 0.16         | 0 | 77   | 0.16         | 2 | 4        | 0.00         |  |

| 4800                  | 2         | 1  | 0.00         | 0    | 32  | -1.36        | 0 | 38   | 0.16         | 0 | 39       | 0.00         |  |

| 9600                  | 2         | 0  | 0.00         | 2    | 0   | 1.73         | 0 | 19   | -2.34        | 0 | 19       | 0.00         |  |

| 19200                 | 0         | 7  | 0.00         | 0    | 7   | 1.73         | 0 | 9    | -2.34        | 0 | 9        | 0.00         |  |

| 31250                 | 0         | 4  | -1.70        | 0    | 4   | 0.00         | 0 | 5    | 0.00         | 0 | 5        | 2.4          |  |

| 38400                 | 0         | 3  | 0.00         | 0    | 3   | 1.73         | 0 | 4    | -2.34        | 0 | 4        | 0.00         |  |

| Tuble Tele Enamples of Dirit Settings for Various Dir Rates (insynem onous ritoue) ( | Table 15.3 | Examples of BRR Setting | s for Various Bit Rates | (Asynchronous Mode) (3) |

|--------------------------------------------------------------------------------------|------------|-------------------------|-------------------------|-------------------------|

|--------------------------------------------------------------------------------------|------------|-------------------------|-------------------------|-------------------------|

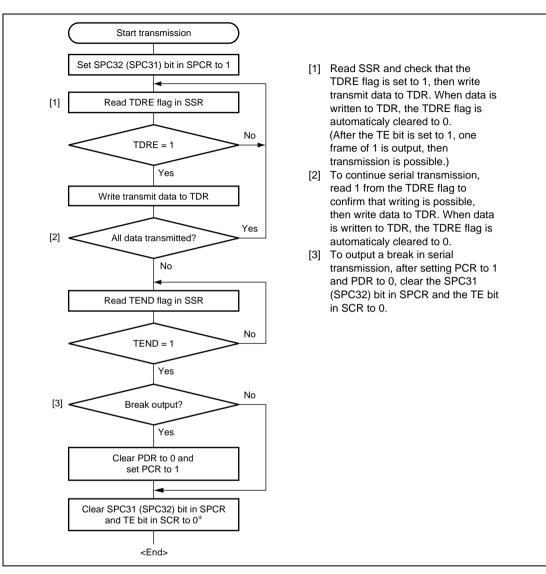

Figure 15.6 Sample Serial Transmission Flowchart (Asynchronous Mode)

RENESAS

| Interrupt        | Flags        | Interrupt Request Conditions                                                                                                                                                                                                                                                                               | Notes                                                                                                                                                                                                                                                      |

|------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXI31<br>(RXI32) | RDRF<br>RIE  | When serial reception is<br>performed normally and receive<br>data is transferred from RSR to<br>RDR, bit RDRF is set to 1, and if<br>bit RIE is set to 1 at this time, an<br>RXI31 (RXI32) is enabled and an<br>interrupt is requested. (See figure<br>15.17 (a).)                                        | The RXI31 (RXI32) interrupt<br>routine reads the receive data<br>transferred to RDR and clears bit<br>RDRF to 0. Continuous reception<br>can be performed by repeating<br>the above operations until<br>reception of the next RSR data is<br>completed.    |

| TXI31<br>(TXI32) | TDRE<br>TIE  | When TSR is found to be empty<br>(on completion of the previous<br>transmission) and the transmit<br>data placed in TDR is transferred<br>to TSR, bit TDRE is set to 1. If bit<br>TIE is set to 1 at this time, a<br>TXI31 (TXI32) is enabled and an<br>interrupt is requested. (See figure<br>15.17 (b).) | The TXI31 (TXI32) interrupt<br>routine writes the next transmit<br>data to TDR and clears bit TDRE<br>to 0. Continuous transmission can<br>be performed by repeating the<br>above operations until the data<br>transferred to TSR has been<br>transmitted. |

| TEI31<br>(TEI32) | TEND<br>TEIE | When the last bit of the character<br>in TSR is transmitted, if bit TDRE<br>is set to 1, bit TEND is set to 1. If<br>bit TEIE is set to 1 at this time, a<br>TEI31 (TEI32) is enabled and an<br>interrupt is requested. (See figure<br>15.17 (c).)                                                         | A TEI31 (TEI32) indicates that the<br>next transmit data has not been<br>written to TDR when the last bit of<br>the transmit character in TSR is<br>transmitted.                                                                                           |

# Table 15.14 Transmit/Receive Interrupts

|                |   |                |                | Function of Pins SEG32 to SEG1 |                   |                   |                   |                   |                  |                |                |  |

|----------------|---|----------------|----------------|--------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------|----------------|--|

| Bit 3:<br>SGS3 |   | Bit 1:<br>SGS1 | Bit 0:<br>SGS0 | SEG32 to<br>SEG29              | SEG28 to<br>SEG25 | SEG24 to<br>SEG21 | SEG20 to<br>SEG17 | SEG16 to<br>SEG13 | SEG12 to<br>SEG9 | SEG8to<br>SEG5 | SEG4to<br>SEG1 |  |

| 0              | 0 | 0              | 0              | Port                           | Port              | Port              | Port              | Port              | Port             | Port           | Port           |  |

|                |   |                | 1              | Port                           | Port              | Port              | Port              | Port              | Port             | Port           | SEG            |  |

|                |   | 1              | 0              | Port                           | Port              | Port              | Port              | Port              | Port             | SEG            | SEG            |  |

|                |   |                | 1              | Port                           | Port              | Port              | Port              | Port              | SEG              | SEG            | SEG            |  |

|                | 1 | 0              | 0              | Port                           | Port              | Port              | Port              | SEG               | SEG              | SEG            | SEG            |  |

|                |   |                | 1              | Port                           | Port              | Port              | SEG               | SEG               | SEG              | SEG            | SEG            |  |

|                |   | 1              | 0              | Port                           | Port              | SEG               | SEG               | SEG               | SEG              | SEG            | SEG            |  |

| _              |   |                | 1              | Port                           | SEG               | SEG               | SEG               | SEG               | SEG              | SEG            | SEG            |  |

| 1              | 0 | 0              | 0              | SEG                            | SEG               | SEG               | SEG               | SEG               | SEG              | SEG            | SEG            |  |

|                |   |                | 1              | SEG                            | SEG               | SEG               | SEG               | SEG               | SEG              | SEG            | Port           |  |

|                |   | 1              | 0              | SEG                            | SEG               | SEG               | SEG               | SEG               | SEG              | Port           | Port           |  |

|                |   |                | 1              | SEG                            | SEG               | SEG               | SEG               | SEG               | Port             | Port           | Port           |  |

|                | 1 | 0              | 0              | SEG                            | SEG               | SEG               | SEG               | Port              | Port             | Port           | Port           |  |

|                |   |                | 1              | SEG                            | SEG               | SEG               | Port              | Port              | Port             | Port           | Port           |  |

|                |   | 1              | 0              | SEG                            | SEG               | Port              | Port              | Port              | Port             | Port           | Port           |  |

|                |   |                | 1              | SEG                            | Port              | Port              | Port              | Port              | Port             | Port           | Port           |  |

#### Table 19.3 Segment Driver Selection

#### 19.3.2 LCD Control Register (LCR)

LCR controls LCD drive power supply and display data, and selects the frame frequency.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                           |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | —        | 1                | —   | Reserved                                                                                                                                                                                                                                                                                              |

|     |          |                  |     | This bit is always read as 1 and cannot be modified.                                                                                                                                                                                                                                                  |

| 6   | PSW      | 0                | R/W | LCD Drive Power Supply Control                                                                                                                                                                                                                                                                        |

|     |          |                  |     | Can be used to turn off the LCD drive power supply<br>when LCD display is not required in power-down mode,<br>or when an external power supply is used. When the<br>ACT bit is cleared to 0 or in standby mode, the LCD<br>drive power supply is turned off regardless of the setting<br>of this bit. |

|     |          |                  |     | 0: LCD drive power supply is turned off                                                                                                                                                                                                                                                               |

|     |          |                  |     | 1: LCD drive power supply is turned on                                                                                                                                                                                                                                                                |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | MST      | 0                | R/W | Master/Slave Select                                                                                                                                                                                                                                                                                                                                                           |

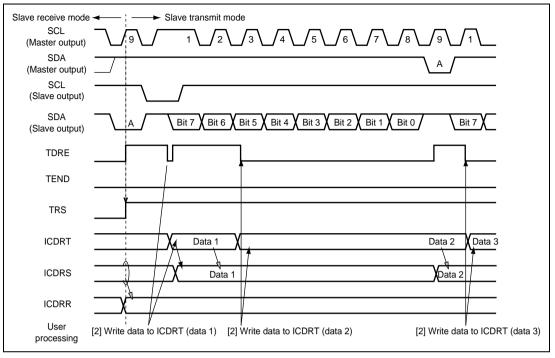

| 4   | TRS      | 0                | R/W | Transmit/Receive Select                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | In master mode with the I2C bus format, when<br>arbitration is lost, MST and TRS are both reset by<br>hardware, causing a transition to slave receive mode.<br>Modification of the TRS bit should be made between<br>transfer frames.                                                                                                                                         |

|     |          |                  |     | After data receive has been started in slave receive<br>mode, when the first seven bits of the receive data<br>agree with the slave address that is set to SAR and the<br>eighth bit is 1, TRS is automatically set to 1. If an<br>overrun error occurs in master mode with the clock<br>synchronous serial format, MST is cleared to 0 and<br>slave receive mode is entered. |

|     |          |                  |     | Operating modes are described below according to MST and TRS combination. When clocked synchronous serial format is selected and MST is 1, clock is output.                                                                                                                                                                                                                   |

|     |          |                  |     | 00: Slave receive mode                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | 01: Slave transmit mode                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 10: Master receive mode                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 11: Master transmit mode                                                                                                                                                                                                                                                                                                                                                      |

| 3   | CKS3     | 0                | R/W | Transfer Clock Select 3 to 0                                                                                                                                                                                                                                                                                                                                                  |

| 2   | CKS2     | 0                | R/W | In master mode, set these bits according to the                                                                                                                                                                                                                                                                                                                               |

| 1   | CKS1     | 0                | R/W | necessary transfer rate (see table 20.2, Transfer Rate).<br>In slave mode, these bits are used to secure the data                                                                                                                                                                                                                                                             |

| 0   | CKS0     | 0                | R/W | setup time in transmission mode. When $CKS3 = 0$ , the data setup time is 10 tcyc and when $CKS3 = 1$ , the data setup time is 20 tcyc.                                                                                                                                                                                                                                       |

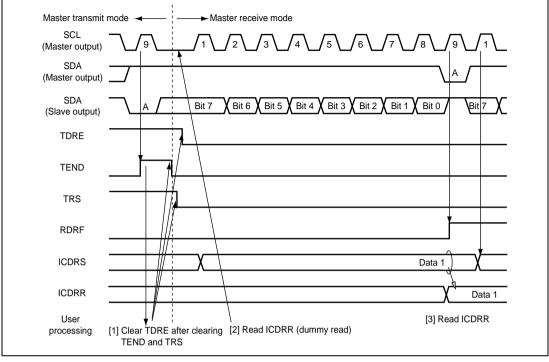

Figure 20.7 Master Receive Mode Operation Timing (1)

Figure 20.9 Slave Transmit Mode Operation Timing (1)

# 5. Bit-Manipulation Instructions

| Mnemonic g |                   |   | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |     |          |                   | ) |                                          |   |                |   |    |   |    | No.<br>Stat |          |

|------------|-------------------|---|---------------------------------------------------|----|------|-----------|-------------|-----|----------|-------------------|---|------------------------------------------|---|----------------|---|----|---|----|-------------|----------|

|            |                   |   | XX#                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @(u, r.c)<br>@@aa | 1 | Operation                                |   | Condition Code |   |    |   |    |             | Advanced |

| BSET       | BSET #xx:3, Rd    | в |                                                   | 2  |      |           |             |     |          |                   |   | (#xx:3 of Rd8) ← 1                       | - | —              | - | -  | — | -  | 2           | 2        |