# E·XFL

#### NXP USA Inc. - MPC8347VRAGDB Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

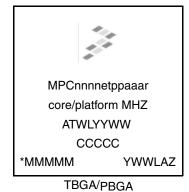

| Product Status                  | Active                                                                |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 400MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR                                                                   |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 620-BBGA Exposed Pad                                                  |

| Supplier Device Package         | 620-HBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8347vragdb |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### NOTE

The information in this document is accurate for revision 3.x silicon and later (in other words, for orderable part numbers ending in A or B). For information on revision 1.1 silicon and earlier versions, see the *MPC8347E PowerQUICC II Pro Integrated Host Processor Hardware Specifications*.

See Section 22.1, "Part Numbers Fully Addressed by This Document," for silicon revision level determination.

# 1 Overview

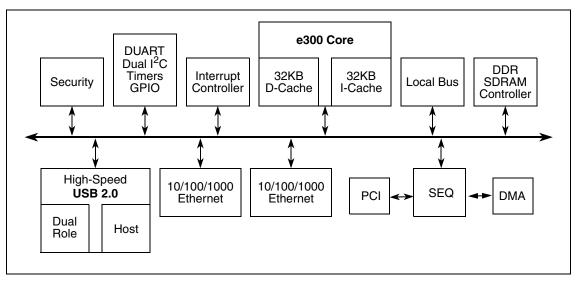

This section provides a high-level overview of the device features. Figure 1 shows the major functional units within the MPC8347EA.

Figure 1. MPC8347EA Block Diagram

Major features of the device are as follows:

- Embedded PowerPC e300 processor core; operates at up to 667 MHz

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the other Freescale processor families that implement Power Architecture technology

- Double data rate, DDR1/DDR2 SDRAM memory controller

- Programmable timing supporting DDR1 and DDR2 SDRAM

- 32- or 64-bit data interface, up to 400 MHz data rate for TBGA, 266 MHz for PBGA

Overview

- Address translation units for address mapping between host and peripheral

- Dual address cycle for target

- Internal configuration registers accessible from PCI

- Security engine is optimized to handle all the algorithms associated with IPSec, SSL/TLS, SRTP, IEEE Std. 802.11i<sup>®</sup>, iSCSI, and IKE processing. The security engine contains four crypto-channels, a controller, and a set of crypto execution units (EUs):

- Public key execution unit (PKEU) :

- RSA and Diffie-Hellman algorithms

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard (DES) execution unit (DEU)

- DES and 3DES algorithms

- Two key (K1, K2) or three key (K1, K2, K3) for 3DES

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric-key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, and counter (CTR) modes

- XOR parity generation accelerator for RAID applications

- ARC four execution unit (AFEU)

- Stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160-, 224-, or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units through an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Universal serial bus (USB) dual role controller

- USB on-the-go mode with both device and host functionality

- Complies with USB specification Rev. 2.0

- Can operate as a stand-alone USB device

- One upstream facing port

- Six programmable USB endpoints

- Can operate as a stand-alone USB host controller

- USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

- External PHY with UTMI, serial and UTMI+ low-pin interface (ULPI)

- Universal serial bus (USB) multi-port host controller

- Can operate as a stand-alone USB host controller

- USB root hub with one or two downstream-facing ports

- Enhanced host controller interface (EHCI) compatible

- Complies with USB Specification Rev. 2.0

- High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

- Direct connection to a high-speed device without an external hub

- External PHY with serial and low-pin count (ULPI) interfaces

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects for eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes controlled by an on-chip memory controller

- Three protocol engines on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user-programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for 1 external (optional) and 7 internal machine checkstop interrupt sources

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to host processor

- Redirects interrupts to external INTA pin in core disable mode.

- Unique vector number for each interrupt source

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

# NP

#### Electrical Characteristics

- On-chip digital filtering rejects spikes on the bus

- System initialization data optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- Handshaking (external control) signals for all channels: DMA\_DREQ[0:3], DMA\_DACK[0:3], DMA\_DDONE[0:3]

- All channels accessible to local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Serial peripheral interface (SPI) for master or slave

- General-purpose parallel I/O (GPIO)

- 52 parallel I/O pins multiplexed on various chip interfaces

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- Designed to comply with IEEE Std. 1149.1<sup>™</sup>, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8347EA. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

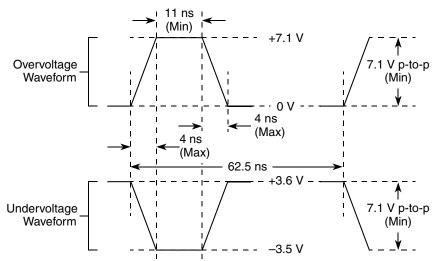

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8347EA for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI Interface for 3.3-V Signaling

### 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                        | Output Impedance<br>(Ω)       | Supply<br>Voltage                                         |

|----------------------------------------------------|-------------------------------|-----------------------------------------------------------|

| Local bus interface utilities signals              | 40                            | OV <sub>DD</sub> = 3.3 V                                  |

| PCI signals (not including PCI output clocks)      | 25                            |                                                           |

| PCI output clocks (including PCI_SYNC_OUT)         | 40                            |                                                           |

| DDR signal                                         | 18                            | GV <sub>DD</sub> = 2.5 V                                  |

| DDR2 signal                                        | 18<br>36 (half-strength mode) | GV <sub>DD</sub> = 1.8 V                                  |

| TSEC/10/100 signals                                | 40                            | LV <sub>DD</sub> = 2.5/3.3 V                              |

| DUART, system control, I <sup>2</sup> C, JTAG, USB | 40                            | OV <sub>DD</sub> = 3.3 V                                  |

| GPIO signals                                       | 40                            | OV <sub>DD</sub> = 3.3 V,<br>LV <sub>DD</sub> = 2.5/3.3 V |

Table 3. Output Drive Capability

### 2.2 **Power Sequencing**

This section details the power sequencing considerations for the MPC8347EA.

### 2.2.1 Power-Up Sequencing

MPC8347EAdoes not require the core supply voltage ( $V_{DD}$  and  $AV_{DD}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) to be applied in any particular order. During the power ramp up, before the power

**Power Characteristics**

|      | Core<br>Frequency<br>(MHz) | CSB<br>Frequency<br>(MHz) | Typical at T <sub>J</sub> = 65 | Typical <sup>2,3</sup> | Maximum <sup>4</sup> | Unit |

|------|----------------------------|---------------------------|--------------------------------|------------------------|----------------------|------|

| TBGA | 333                        | 333                       | 2.0                            | 3.0                    | 3.2                  | W    |

|      |                            | 166                       | 1.8                            | 2.8                    | 2.9                  | W    |

|      | 400                        | 266                       | 2.1                            | 3.0                    | 3.3                  | W    |

|      |                            | 133                       | 1.9                            | 2.9                    | 3.1                  | W    |

|      | 450                        | 300                       | 2.3                            | 3.2                    | 3.5                  | W    |

|      |                            | 150                       | 2.1                            | 3.0                    | 3.2                  | W    |

|      | 500                        | 333                       | 2.4                            | 3.3                    | 3.6                  | W    |

|      |                            | 166                       | 2.2                            | 3.1                    | 3.4                  | W    |

|      | 533                        | 266                       | 2.4                            | 3.3                    | 3.6                  | W    |

|      |                            | 133                       | 2.2                            | 3.1                    | 3.4                  | W    |

|      | 667 <sup>5,6</sup>         | 333                       | 3.5                            | 4.6                    | 5                    | W    |

Table 4. MPC8347EA Power Dissipation<sup>1</sup> (continued)

<sup>1</sup> The values do not include I/O supply power (OV<sub>DD</sub>, LV<sub>DD</sub>, GV<sub>DD</sub>) or AV<sub>DD</sub>. For I/O power values, see Table 5.

<sup>2</sup> Typical power is based on a voltage of  $V_{DD} = 1.2$  V, a junction temperature of  $T_J = 105$  °C, and a Dhrystone benchmark application.

<sup>3</sup> Thermal solutions may need to design to a value higher than typical power based on the end application, T<sub>A</sub> target, and I/O power.

<sup>4</sup> Maximum power is based on a voltage of V<sub>DD</sub> = 1.2 V, worst case process, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoke test.

<sup>5</sup> Typical power is based on a voltage of  $V_{DD}$  = 1.3 V, a junction temperature of  $T_J$  = 105°C, and a Dhrystone benchmark application.

<sup>6</sup> Maximum power is based on a voltage of  $V_{DD}$  = 1.3 V, worst case process, a junction temperature of  $T_J$  = 105°C, and an artificial smoke test.

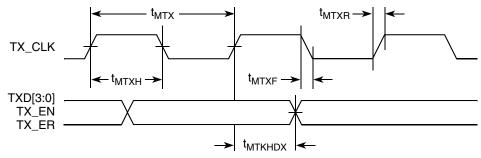

#### Table 27. MII Transmit AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min | Тур | Мах | Unit |

|----------------------------------|---------------------|-----|-----|-----|------|

| TX_CLK data clock rise (20%-80%) | t <sub>MTXR</sub>   | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%-20%) | t <sub>MTXF</sub>   | 1.0 | _   | 4.0 | ns   |

#### Note:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). In general, the clock reference symbol is based on two to three letters representing the clock of a particular function. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub></sub>

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

### 8.2.2.2 MII Receive AC Timing Specifications

Table 28 provides the MII receive AC timing specifications.

#### Table 28. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

#### Ethernet: Three-Speed Ethernet, MII Management

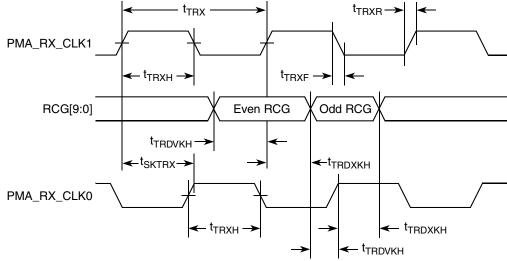

#### Table 30. TBI Receive AC Timing Specifications (continued)

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V  $\pm$  10%.

| Parameter/Condition                                               | Symbol <sup>1</sup>              | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|----------------------------------|-----|-----|-----|------|

| RXD[7:0], RX_DV, RX_ER (RCG[9:0]) setup time to rising PMA_RX_CLK | t <sub>TRDVKH</sub> <sup>2</sup> | 2.5 | —   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER (RCG[9:0]) hold time to rising PMA_RX_CLK  | t <sub>TRDXKH</sub> 2            | 1.5 | —   | —   | ns   |

| RX_CLK clock rise time (20%–80%)                                  | t <sub>TRXR</sub>                | 0.7 | —   | 2.4 | ns   |

| RX_CLK clock fall time (80%–20%)                                  | t <sub>TRXF</sub>                | 0.7 | —   | 2.4 | ns   |

Notes:

The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. In general, the clock reference symbol is based on three letters representing the clock of a particular function. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript SK followed by the clock that is being skewed (TRX).

</sub>

2. Setup and hold time of even numbered RCG are measured from the riding edge of PMA\_RX\_CLK1. Setup and hold times of odd-numbered RCG are measured from the riding edge of PMA\_RX\_CLK0.

#### Figure 15 shows the TBI receive AC timing diagram.

Figure 15. TBI Receive AC Timing Diagram

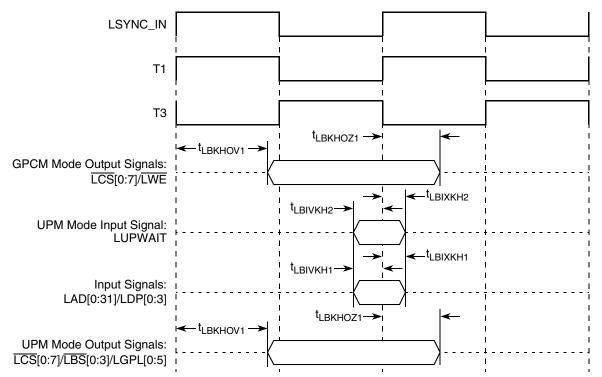

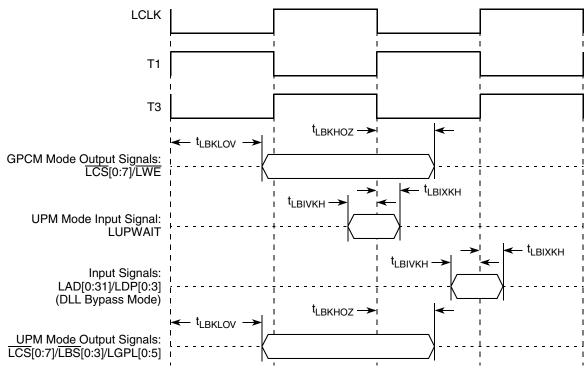

Local Bus

Figure 23. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

Figure 24. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode)

Table 40. JTAG Interface DC Electrical Characteristics (continued)

| Parameter          | Symbol          | Condition                | Min | Max | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA | _   | 0.5 | V    |

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | —   | 0.4 | V    |

## **11.2 JTAG AC Timing Specifications**

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8347EA. Table 41 provides the JTAG AC timing specifications as defined in Figure 28 through Figure 31.

#### Table 41. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Para                         | imeter                         | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|------------------------------|--------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock freque   | ncy of operation               | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle ti | me                             | t <sub>JTG</sub>                           | 30       | _        | ns   | _     |

| JTAG external clock pulse v  | vidth measured at 1.4 V        | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —     |

| JTAG external clock rise an  | d fall times                   | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time             |                                | t <sub>TRST</sub>                          | 25       | —        | ns   | 3     |

| Input setup times:           | Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   |          | ns   | 4     |

| Input hold times:            | Boundary-scan data<br>TMS, TDI | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4     |

| Valid times:                 | Boundary-scan data<br>TDO      | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 2<br>2   | 11<br>11 | ns   | 5     |

| Output hold times:           | Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns   | 5     |

#### Table 55. MPC8347EA (TBGA) Pinout Listing (continued)

| Signal                                 | Package Pin Number         | Pin Type | Power<br>Supply   | Notes |

|----------------------------------------|----------------------------|----------|-------------------|-------|

| TSEC2_TXD[3:0]/GPIO1[17:20]            | B5, A5, F8, B6             | I/O      | LV <sub>DD2</sub> | —     |

| TSEC2_TX_ER/GPIO1[24]                  | F14                        | I/O      | OV <sub>DD</sub>  | —     |

| TSEC2_TX_EN/GPIO1[12]                  | C5                         | I/O      | LV <sub>DD2</sub> | 3     |

| TSEC2_TX_CLK/GPIO1[30]                 | E14                        | I/O      | OV <sub>DD</sub>  | —     |

|                                        | DUART                      | ł        | 1                 |       |

| UART_SOUT[1:2]/MSRCID[0:1]/LSRCID[0:1] | AK27, AN29                 | 0        | OV <sub>DD</sub>  | —     |

| UART_SIN[1:2]/MSRCID[2:3]/LSRCID[2:3]  | AL28, AM29                 | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[1]/MSRCID4/LSRCID4            | AP30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_CTS[2]/MDVAL/ LDVAL               | AN30                       | I/O      | OV <sub>DD</sub>  | —     |

| UART_RTS[1:2]                          | AP31, AM30                 | 0        | OV <sub>DD</sub>  | —     |

|                                        | I <sup>2</sup> C interface | ł        | 1                 |       |

| IIC1_SDA                               | AK29                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC1_SCL                               | AP32                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SDA                               | AN31                       | I/O      | OV <sub>DD</sub>  | 2     |

| IIC2_SCL                               | AM31                       | I/O      | OV <sub>DD</sub>  | 2     |

|                                        | SPI                        | I        | 1                 |       |

| SPIMOSI/LCS[6]                         | AN32                       | I/O      | OV <sub>DD</sub>  | —     |

| SPIMISO/LCS[7]                         | AP33                       | I/O      | OV <sub>DD</sub>  | —     |

| SPICLK                                 | AK30                       | I/O      | OV <sub>DD</sub>  | —     |

| SPISEL                                 | AL31                       | I        | OV <sub>DD</sub>  | —     |

|                                        | Clocks                     |          | 1                 |       |

| PCI_CLK_OUT[0:2]                       | AN9, AP9, AM10             | 0        | OV <sub>DD</sub>  | _     |

| PCI_CLK_OUT[3]/LCS[6]                  | AN10                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_CLK_OUT[4]/LCS[7]                  | AJ11                       | 0        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_IN/PCI_CLOCK                  | AK12                       | I        | OV <sub>DD</sub>  | —     |

| PCI_SYNC_OUT                           | AP11                       | 0        | OV <sub>DD</sub>  | 3     |

| RTC/PIT_CLOCK                          | AM32                       | I        | OV <sub>DD</sub>  | —     |

| CLKIN                                  | AM9                        | I        | OV <sub>DD</sub>  | —     |

|                                        | JTAG                       | I        | 1                 |       |

| ТСК                                    | E20                        | I        | OV <sub>DD</sub>  | _     |

| TDI                                    | F20                        | I        | OV <sub>DD</sub>  | 4     |

| TDO                                    | B20                        | 0        | OV <sub>DD</sub>  | 3     |

| TMS                                    | A20                        | I        | OV <sub>DD</sub>  | 4     |

| TRST                                   | B19                        | I        | OV <sub>DD</sub>  | 4     |

| Table 56. MPC8347EA (I | PBGA) Pinout | Listing (continued) |

|------------------------|--------------|---------------------|

|------------------------|--------------|---------------------|

| MPH1_PCTL0/DR_TX_VALID_PCTL0         A26         O         OVD0         Implementation           MPH1_PCTL1/DR_TX_VALIDH_PCTL1         B25         O         OVD0         Implementation         Implementation | Signal                          | Package Pin Number                   | Pin Type   | Power<br>Supply   | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|------------|-------------------|-------|

| MPH1_CLK/DR_CLK         A25         I         OVD            USB Port 0         USB Port 0         OVD         OVD            MPH0_DD_SER_TXD/DR_D9_DCHGVBUS         C24         I/O         OVD            MPH0_D1_SER_TXD/DR_D9_DCHGVBUS         C24         I/O         OVD            MPH0_D3_SPEED/DR_D10_DPPD         B24         I/O         OVD            MPH0_D4_D7/DR_D12_VBUS_VLD         D23         I/O         OVD            MPH0_D5_DSER_TXD/DR_D11_DMMD         A24         I/O         OVD            MPH0_D5_DD2_12_UBUS_VLD         D23         I/O         OVD            MPH0_D5_SER_RCV/DR_D14         B23         I/O         OVD            MPH0_D5_SER_RCV/DR_D15_IDPULLUP         A23         I/O         OVD            MPH0_DRYD_RA_ACTIVE_ID         D22         I         OVD            MPH0_SER_REV/DR_RESET         C22         I/O         OVD            MPH0_SER_RAUT/DR_RX_ACTIVE_ID         A22         I/O         OVD            MPH0_SER_RAUT/DR_RX_ACTIVE_ID         A22         I/O         OVD <td< td=""><td>MPH1_PCTL0/DR_TX_VALID_PCTL0</td><td>A26</td><td>0</td><td>OV<sub>DD</sub></td><td>—</td></td<>                                                                                                                                                                                                                                                                                                                        | MPH1_PCTL0/DR_TX_VALID_PCTL0    | A26                                  | 0          | OV <sub>DD</sub>  | —     |

| USB Port 0         UV0         OV0D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MPH1_PCTL1/DR_TX_VALIDH_PCTL1   | B25                                  | 0          | OV <sub>DD</sub>  | —     |

| MPH0_D0_ENABLEN/DR_D8_CHGVBUS         D24         I/O         OV <sub>DD</sub> MPH0_D1_SER_TXD/DR_D9_DCHGVBUS         C24         I/O         OV <sub>DD</sub> MPH0_D2_VMO_SE0/DR_D10_DPPD         B24         I/O         OV <sub>DD</sub> MPH0_D3_SPEED/DR_D11_DMMD         A24         I/O         OV <sub>DD</sub> MPH0_D4_DP/DR_D12_VBUS_VLD         D23         I/O         OV <sub>DD</sub> MPH0_D5_SUMDR_D13_SESS_END         C23         I/O         OV <sub>DD</sub> MPH0_D0_SER_RCVDR_D14         B23         I/O         OV <sub>DD</sub> MPH0_D7_DRVNBVS/DR_D15_IDPULLUP         A23         I/O         OV <sub>DD</sub> MPH0_D1R_DPUXLUP/DR_RESET         C22         I/O         OV <sub>DD</sub> MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV <sub>DD</sub> MPH0_PCTL0/DR_LINE_STATE0         E21         I/O         OV <sub>DD</sub> MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV <sub>DD</sub> MPH0_PCTL1/DR_LINE_STATE1         D28         I/O         OV <sub>DD</sub> MPH0_SCLV/DR_D2[12]         J28         I/O         OV                                                                                                                                                                                                                                                                                                                                                                                            | MPH1_CLK/DR_CLK                 | A25                                  | I          | OV <sub>DD</sub>  | —     |

| MPH0_D1_SER_TXD/DR_D9_DCHGVBUS         C24         I/O         OV_DD         I           MPH0_D2_VMO_SE0/DR_D10_DPPD         B24         I/O         OV_DD         I           MPH0_D3_SPEED/DR_D11_DMMD         A24         I/O         OV_DD         I           MPH0_D4_DP/DR_D12_VBUS_VLD         D23         I/O         OV_DD         I           MPH0_D5_DM/DR_D13_SESS_END         C23         I/O         OV_DD         I           MPH0_D6_SER_RCV/DR_D14         B23         I/O         OV_DD         I           MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         I/O         OV_DD         I           MPH0_D1R_RX_ACTIVE_ID         D22         I         OV_DD         I         I           MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_DD         I           MPH0_PCTL1/DR_RX_VALIDH         A22         I/O         OV_DD         I           MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD         I           MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD         I           MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD         I           MPH0_PCTL1/DR_LINE_STATE1         D28         I/O         OV_DD                                                                                                                                                                                                                                                               |                                 | USB Port 0                           |            | 1                 |       |

| MPHO_D2_VMO_SEO/DR_D10_DPPD         B24         I/O         OV_D0         I           MPHO_D3_SPEED/DR_D11_DMMD         A24         I/O         OV_D0         I           MPHO_D4_DP/DR_D12_VBUS_VLD         D23         I/O         OV_D0         I           MPHO_D5_DM/DR_D13_SESS_END         C23         I/O         OV_D0         I           MPHO_D6_SER_RCV/DR_D14         B23         I/O         OV_D0         I           MPHO_D6_SER_RCV/DR_D15_IDPULLUP         A23         I/O         OV_D0         I           MPHO_D7_DRVSUS/DR_TA_REXET         C22         I/O         OV_D0         I           MPHO_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_D0         I           MPHO_PCTL/OR_RA_VALIDH         A22         I         OV_D0         I           MPHO_PCTL/DR_RA_VALID         C21         I         OV_D0         I           MPHO_PCTL/OR_LINE_STATE0         E21         I/O         OV_D0         I           MPHO_PCTU/OR_LINE_STATE1         D21         I/O         OV_D0         I           MPHO_PCTU/OR_LINE_STATE1         D21         I/O         OV_D0         I           MCP_OUT         E8         O         OV_D0         I         I      <                                                                                                                                                                                                                                                                             | MPH0_D0_ENABLEN/DR_D8_CHGVBUS   | D24                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_D3_SPEED/DR_D11_DMMD         A24         I/O         OVDD         I           MPH0_D4_DP/DR_D12_VBUS_VLD         D23         I/O         OVDD         I           MPH0_D5_DM/DR_D13_SESS_END         C23         I/O         OVDD         I           MPH0_D6_SER_RCV/DR_D14         B23         I/O         OVDD         I           MPH0_D6_SER_RCV/DR_D15_IDPULLUP         A23         I/O         OVDD         I           MPH0_DT7_DRVVBUS/DR_TS_END         D22         I         OVDD         I           MPH0_DR_RX_ACTIVE_ID         D22         I/O         OVDD         I           MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OVDD         I           MPH0_PCTLI/DR_RX_VALIDH         A22         I         OVDD         I           MPH0_CLK/DR_RX_VALID         C21         I         OVDD         I           MPH0_PCTLI/DR_LINE_STATE0         E8         O         OVDD         I           MPH0_CLK/DR_RX_VALID         C21         I         OVDD         I           MPH0_PCTLI/DR_LINE_STATE1         D21         I/O         OVDD         I           MCP_OUT         E8         O         OVDD         I         I           MEQ0_IN/GPI02[                                                                                                                                                                                                                                                                                         | MPH0_D1_SER_TXD/DR_D9_DCHGVBUS  | C24                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_D4_DP/DR_D12_VBUS_VLD         D23         V/O         OVD0            MPH0_D5_DM/DR_D13_SESS_END         C23         V/O         OVD0            MPH0_D6_SER_RCV/DR_D14         B23         V/O         OVD0            MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         V/O         OVD0            MPH0_DT_DRVVBUS/DR_D15_IDPULLUP         A23         V/O         OVD0            MPH0_STP_SUSPEND/DR_TX_READY         D22         I         OVD0         0           MPH0_PWRFAULT/DR_RX_VALIDH         A222         I         OVD0         0            MPH0_PVRFAULT/DR_RX_VALIDH         A222         I         OVD0         0            MPH0_PCTL/OR_LINE_STATE0         E21         V/O         OVD0            MPH0_PCTL/DR_LINE_STATE1         D21         V/O         OVD0            MPH0_CLK/DR_RX_VALID         C21         I         OVD0            MPH0_CLK/DR_RX_VALID         C21         I         OVD0            MCP_OUT         E8         O         OVD0            MCP_OUT         G28         I/O         OVD0 <t< td=""><td>MPH0_D2_VMO_SE0/DR_D10_DPPD</td><td>B24</td><td>I/O</td><td>OV<sub>DD</sub></td><td>—</td></t<>                                                                                                                                                                                                                                                                                                                   | MPH0_D2_VMO_SE0/DR_D10_DPPD     | B24                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_D5_DM/DR_D13_SESS_END         C23         I/O         OVDD            MPH0_D6_SER_RCV/DR_D14         B23         I/O         OVDD            MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         I/O         OVDD            MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         I/O         OVDD            MPH0_D1R_DPULLUP/DR_RESET         C22         I/O         OVDD            MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OVDD            MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OVDD            MPH0_PCTLI/DR_LINE_STATE0         E21         I/O         OVDD            MPH0_PCTLI/DR_LINE_STATE1         D21         I/O         OVDD            MPH0_CLK/DR_RX_VALID         C21         I         OVDD            MPH0_CLK/DR_RX_VALID         C21         I         OVDD            MPH0_CLK/DR_RX_VALID         C21         I         OVDD            MCP_OUT         E8         O         OVDD             MCP_OUT         G28         I/O         OVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MPH0_D3_SPEED/DR_D11_DMMD       | A24                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_D6_SER_RCV/DR_D14         B23         I/O         OV_D            MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         I/O         OV_D            MPH0_DXT/DR_RX_ACTIVE_ID         D22         I         OV_D            MPH0_DIR_DPPULLUP/DR_RESET         C22         I/O         OV_D            MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_D            MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV_D            MPH0_PCTLI/DR_LINE_STATE0         E21         I/O         OV_D            MPH0_PCTLI/DR_LINE_STATE1         D21         I/O         OV_D            MPH0_CLK/DR_RX_VALID         C21         I         OV_D            MPH0_PCTLI/DR_LINE_STATE1         D21         I/O         OV_D            MPH0_CLK/DR_RX_VALID         C21         I         OV_D            MPEO_OUT         E8         O         OV_D            IRO_OUT         K25, J25, H26, L24, G27         I/O         OV_D            IRO[GPIO2[13]/CPIO2[13]/CKSTOP_OUT         G28         I/O         OV_D <td< td=""><td>MPH0_D4_DP/DR_D12_VBUS_VLD</td><td>D23</td><td>I/O</td><td>OV<sub>DD</sub></td><td>—</td></td<>                                                                                                                                                                                                                                                                                                                        | MPH0_D4_DP/DR_D12_VBUS_VLD      | D23                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_D7_DRVVBUS/DR_D15_IDPULLUP         A23         V/O         OV_DD            MPH0_NXT/DR_RX_ACTIVE_ID         D22         I         OV_DD            MPH0_DIR_DPPULLUP/DR_RESET         C22         V/O         OV_DD            MPH0_STP_SUSPEND/DR_TX_READY         B22         V/O         OV_DD            MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV_DD            MPH0_PCTL/OR_LINE_STATEO         E21         V/O         OV_DD            MPH0_PCTL/OR_LINE_STATE0         E21         V/O         OV_DD            MPH0_PCTL/OR_LINE_STATE1         D21         V/O         OV_DD            MPH0_PCTLI/DR_RX_VALID         C21         I         OV_DD            MPH0_PCTLI/OR_LINE_STATE1         D21         V/O         OV_DD            MPF0_OUT         E8         O         OV_DD            MCP_OUT         K25, J25, H26, L24, G27         V/O         OV_DD            IRO[6]/GPI02[13]/T]         K25, J25, H26, L24, G27         V/O         OV_DD            IRO[6]/GPI02[19]/CKSTOP_OUT         G28         V/O         V/DD_D                                                                                                                                                                                                                                                                                                                                                                                                        | MPH0_D5_DM/DR_D13_SESS_END      | C23                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_NXT/DR_RX_ACTIVE_ID         D2         I         OV_DD            MPH0_NXT/DR_RX_ACTIVE_ID         D22         I         OV_DD            MPH0_DIR_DPPULLUP/DR_RESET         C22         I/O         OV_DD            MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_DD            MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV_DD            MPH0_PCTLO/DR_LINE_STATE0         E21         I/O         OV_DD            MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD            MPH0_CLK/DR_RX_VALID         C21         I         OV_DD            MPE_OUT         E8         O         OV_DD         2            MCP_OUT         K25, J25, H26, L24, G27         I/O         OV_DD                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MPH0_D6_SER_RCV/DR_D14          | B23                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_DIR_DPPULLUP/DR_RESET         C22         I/O         OV         OV           MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV         OV         OV           MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV         OV         OV         OV         OV           MPH0_PCTLO/DR_LINE_STATEO         E21         I/O         OV         OV<                                                                                                                                                                                                                                                                                                    | MPH0_D7_DRVVBUS/DR_D15_IDPULLUP | A23                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_DD         I           MPH0_STP_SUSPEND/DR_TX_READY         B22         I/O         OV_DD         I           MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV_DD         I           MPH0_PCTL0/DR_LINE_STATE0         E21         I/O         OV_DD         I           MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD         I           MPH0_CLK/DR_RX_VALID         C21         I         OV_DD         I           MCP_OUT         E8         O         OV_DD         2           IRO/MCP_IN/GPIO2[12]         J28         I/O         OV_DD         I           IRO[1/SPIO2[13)/CKSTOP_OUT         G28         I/O         OV_DD         I           IRO[1/GPIO2[19]/CKSTOP_OUT         J26         I/O         OV_DD         I           EC_MDC         Y24         O         LV_DD1         I         I           EC_MDIO         Y2                                                                                                                                                                                                                                                                                                  | MPH0_NXT/DR_RX_ACTIVE_ID        | D22                                  | I          | OV <sub>DD</sub>  | —     |

| MPH0_PWRFAULT/DR_RX_VALIDH         A22         I         OV <sub>DD</sub> MPH0_PCTL0/DR_LINE_STATE0         E21         I/O         OV <sub>DD</sub> MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV <sub>DD</sub> MPH0_CLK/DR_RX_VALID         C21         I         OV <sub>DD</sub> MCP_OUT         E8         O         OV <sub>DD</sub> 2           IRQ0/MCP_IN/GPIO2[12]         J28         I/O         OV <sub>DD</sub> IRQ[1:5/GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OV <sub>DD</sub> IRQ[6/GPIO2[18/CKSTOP_OUT         G28         I/O         OV <sub>DD</sub> IRQ[7/GPIO2[19/CKSTOP_IN         J26         I/O         I/V_DD1         1           EC_MDC         Y24         O         LV <sub>DD1</sub> 1           EC_GTX_CL                                                                                                                                                                                                                                                                                                                                                                                                                | MPH0_DIR_DPPULLUP/DR_RESET      | C22                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_PCTL0/DR_LINE_STATE0         E21         I/O         OV_DD            MPH0_PCTL1/DR_LINE_STATE1         D21         I/O         OV_DD            MPH0_CLK/DR_RX_VALID         C21         I         OV_DD            MPH0_CLK/DR_RX_VALID         C21         I         OV_DD            MCP_OUT         E8         O         OV_DD         2           MCP_OUT         E8         O         OV_DD            IRQ0/MCP_IN/GPIO2[12]         J28         I/O         OV_DD            IRQ[6//GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OV_DD            IRQ[6//GPIO2[18//CKSTOP_OUT         G28         I/O         OV_DD            IRQ[6//GPIO2[19//CKSTOP_IN         J26         I/O         OV_DD            IRQ[7//GPIO2[19//CKSTOP_IN         J26         I/O         OV_DD            EC_MDC         Y24         O         LV_DD1         11           EC_MDC         Y26         I         LV_DD1         11           EC_GTX_CLK125         Y26         I         LV_DD1            Three-Sped Ethernet Controller (Gigabit Etheret U)                                                                                                                                                                                                                                                                                                                                                                                                         | MPH0_STP_SUSPEND/DR_TX_READY    | B22                                  | I/O        | OV <sub>DD</sub>  | —     |

| MPH0_PCTL1/DR_LINE_STATE1         D21         //O         OV_DD            MPH0_CLK/DR_RX_VALID         C21         I         OV_DD            MPH0_CLK/DR_RX_VALID         C21         I         OV_DD            MCP_OUT         C21         I         OV_DD         2           MCP_OUT         E8         O         OV_DD         2           IRQ0/MCP_IN/GPIO2[12]         J28         I/O         OV_DD            IRQ1:5)/GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OV_DD            IRQ6//GPIO2[18)/CKSTOP_OUT         G28         I/O         OV_DD            IRQ1/J/GPIO2[19]/CKSTOP_IN         J26         I/O         OV_DD            IRQ1/J/GPIO2[19]/CKSTOP_IN         J26         I/O         OV_DD            IRQ1/J/GPIO2[19]/CKSTOP_IN         J26         I/O         UV_DD1            EC_MDC         Y24         O         LV_DD1            EC_MDC         Y26         I/O         LV_DD1         11           CGIGabit Reference Clock         E         E         C         T            <                                                                                                                                                                                                                                                                                                                                                                                                                                        | MPH0_PWRFAULT/DR_RX_VALIDH      | A22                                  | I          | OV <sub>DD</sub>  | —     |

| MPH0_CLK/DR_RX_VALID         C21         I         OVD           MPH0_CLK/DR_RX_VALID         C21         I         OVD            MCP_OUT           MCP_OUT         E8         O         OVD         2           IRQ0/MCP_IN/GPI02[12]         J28         I/O         OVD            IRQ[1:5]/GPI02[13:17]         K25, J25, H26, L24, G27         I/O         OVD            IRQ[6]/GPI02[18]/CKSTOP_OUT         G28         I/O         OVD            IRQ[6]/GPI02[19]/CKSTOP_OUT         G28         I/O         OVD            IRQ[6]/GPI02[19]/CKSTOP_IN         J26         I/O         OVD            IRQ[7]/GPI02[19]/CKSTOP_IN         J26         I/O         OVD            IRQ[7]/GPI02[19]/CKSTOP_IN         J26         I/O         OVD            IRQ[7]/GPI02[19]/CKSTOP_IN         J26         I/O         I/D            EC_MDC         Y24         O         LVDD1            EC_MDIO         Y26         I/O         LVDD1            EC_MDIO         Y26         I         LVDD1            EC_GTX_CLK125                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MPH0_PCTL0/DR_LINE_STATE0       | E21                                  | I/O        | OV <sub>DD</sub>  | —     |

| Programmable Interrupt Controller           MCP_OUT         E8         O         OVDD         2           IRQO/MCP_IN/GPIO2[12]         J28         I/O         OVDD            IRQ[1:5]/GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OVDD            IRQ[6]/GPIO2[18]/CKSTOP_OUT         G28         I/O         OVDD            IRQ[6]/GPIO2[19]/CKSTOP_IN         J26         I/O         OVDD            IRQ[7]/GPIO2[19]/CKSTOP_IN         J26         I/O         OVDD            EC_MDC         Y24         O         LVDD1            EC_MDDO         Y25         I/O         LVDD1         11           EC_GTX_CLK125         Y26         I         LVDD1            Three-Speet Ethernet Controller (Gigabit Ethernet I)         IVD         I            TSEC1_COL/GPIO2[20]         M26         I/O         OVDD            TSEC1_COL/GPIO2[21]         U25         I/O         LVDD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MPH0_PCTL1/DR_LINE_STATE1       | D21                                  | I/O        | OV <sub>DD</sub>  | —     |

| MCP_OUT         E8         O         OV <sub>DD</sub> 2           IRQO/MCP_IN/GPIO2[12]         J28         I/O         OV <sub>DD</sub> IRQ[1:5]/GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OV <sub>DD</sub> IRQ[6]/GPIO2[18]/CKSTOP_OUT         G28         I/O         OV <sub>DD</sub> IRQ[6]/GPIO2[19]/CKSTOP_IN         J26         I/O         OV <sub>DD</sub> IRQ[7]/GPIO2[19]/CKSTOP_IN         J26         I/O         OV <sub>DD</sub> EC_MDC         Y24         O         LV <sub>DD1</sub> 11           EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> 1           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MPH0_CLK/DR_RX_VALID            | C21                                  | I          | OV <sub>DD</sub>  | —     |

| IRQ         IRQ <td>Pro</td> <td>ogrammable Interrupt Controller</td> <td></td> <td></td> <td></td>                                                                                                                                                                                            | Pro                             | ogrammable Interrupt Controller      |            |                   |       |

| IRQ[1:5]/GPIO2[13:17]         K25, J25, H26, L24, G27         I/O         OV <sub>DD</sub> IRQ[6]/GPIO2[13]/CKSTOP_OUT         G28         I/O         OV <sub>DD</sub> IRQ[7]/GPIO2[19]/CKSTOP_IN         J26         I/O         OV <sub>DD</sub> EC_MDC         Ethernet Management Interface              EC_MDC         Y24         O         LV <sub>DD1</sub> EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           Gigabit Reference Clock           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Spec Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MCP_OUT                         | E8                                   | 0          | OV <sub>DD</sub>  | 2     |

| IRQ[6]/GPIO2[18]/CKSTOP_OUT         G28         I/O         OV <sub>DD</sub> IRQ[7]/GPIO2[19]/CKSTOP_IN         J26         I/O         OV <sub>DD</sub> Ethernet Management Interface           EC_MDC         Y24         O         LV <sub>DD1</sub> EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           Ethernet Clock           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speet Ethernet Controller (Gigabit Ethernet I)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IRQ0/MCP_IN/GPIO2[12]           | J28                                  | I/O        | OV <sub>DD</sub>  | —     |

| IRQ[7]/GPI02[19]/CKSTOP_IN         J26         I/O         OV <sub>DD</sub> EC_MDC         Y24         O         LV <sub>DD1</sub> EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> 1-           TSEC1_COL/GPI02[20]         M26         I         LV <sub>DD1</sub> TSEC1_CRS/GPI02[21]         M26         I/O         OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IRQ[1:5]/GPIO2[13:17]           | K25, J25, H26, L24, G27              | I/O        | OV <sub>DD</sub>  | —     |

| Ethernet Management Interface         O         LV <sub>DD1</sub> EC_MDC         Y24         O         LV <sub>DD1</sub> EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           Gigabit Reference Clock           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speet Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IRQ[6]/GPIO2[18]/CKSTOP_OUT     | G28                                  | I/O        | OV <sub>DD</sub>  | —     |

| EC_MDC         Y24         O         LV <sub>DD1</sub> EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           Gigabit Reference Clock           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speet Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IRQ[7]/GPIO2[19]/CKSTOP_IN      | J26                                  | I/O        | OV <sub>DD</sub>  | —     |

| EC_MDIO         Y25         I/O         LV <sub>DD1</sub> 11           Gigabit Reference Clock           EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speet Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | E                               | thernet Management Interface         |            |                   |       |

| Gigabit Reference Clock         I         LV <sub>DD1</sub> EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speed Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPI02[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPI02[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EC_MDC                          | Y24                                  | 0          | LV <sub>DD1</sub> | —     |

| EC_GTX_CLK125         Y26         I         LV <sub>DD1</sub> Three-Speed Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPI02[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPI02[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EC_MDIO                         | Y25                                  | I/O        | LV <sub>DD1</sub> | 11    |

| Three-Speed Ethernet Controller (Gigabit Ethernet 1)           TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 | Gigabit Reference Clock              | _ <b>I</b> | 1                 |       |

| TSEC1_COL/GPIO2[20]         M26         I/O         OV <sub>DD</sub> TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EC_GTX_CLK125                   | Y26                                  | I          | LV <sub>DD1</sub> | —     |

| TSEC1_CRS/GPIO2[21]         U25         I/O         LV <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Three-Speed                     | d Ethernet Controller (Gigabit Ether | net 1)     | •                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TSEC1_COL/GPIO2[20]             | M26                                  | I/O        | OV <sub>DD</sub>  | —     |

| TSEC1_GTX_CLK V24 O LV <sub>DD1</sub> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TSEC1_CRS/GPIO2[21]             | U25                                  | I/O        | LV <sub>DD1</sub> | —     |