Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Obsolete                                                       |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | OTP                                                            |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 8x10b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 14-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t600-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

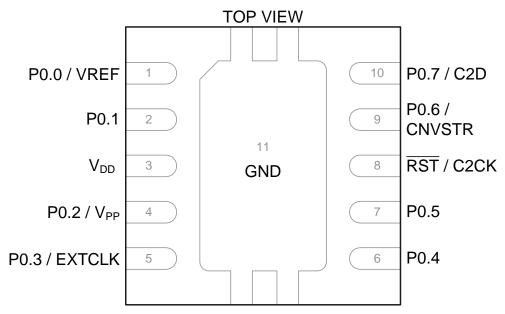

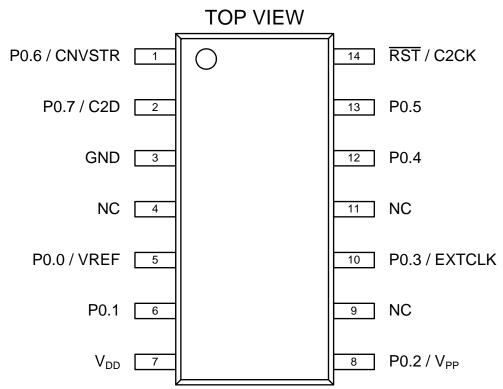

# 3. Pin Definitions

| Name            | QFN11<br>Pin | SOIC14<br>Pin | Туре             | Description                                                                                                                |

|-----------------|--------------|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 3            | 7             |                  | Power Supply Voltage.                                                                                                      |

| GND             | 11           | 3             |                  | Ground.                                                                                                                    |

| RST /           | 8            | 14            | D I/O            | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor.                                                       |

| C2CK            |              |               | D I/O            | Clock signal for the C2 Debug Interface.                                                                                   |

| P0.7 /          | 10           | 2             | D I/O or<br>A In | Port 0.7.                                                                                                                  |

| C2D             |              |               | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                     |

| P0.0 /          | 1            | 5             | D I/O or<br>A In | Port 0.0.                                                                                                                  |

| VREF            |              |               | A In             | External VREF input.                                                                                                       |

| P0.1            | 2            | 6             | D I/O or<br>A In | Port 0.1.                                                                                                                  |

| P0.2 /          | 4            | 8             | D I/O or<br>A In | Port 0.2.                                                                                                                  |

| V <sub>PP</sub> |              |               | A In             | V <sub>PP</sub> Programming Supply Voltage.                                                                                |

| P0.3 /          | 5            | 10            | D I/O or<br>A In | Port 0.3.                                                                                                                  |

| EXTCLK          |              |               | A I/O or<br>D In | External Clock Pin. This pin can be used as the external clock input for CMOS, capacitor, or RC oscillator configurations. |

| P0.4            | 6            | 12            | D I/O or<br>A In | Port 0.4.                                                                                                                  |

| P0.5            | 7            | 13            | D I/O or<br>A In | Port 0.5.                                                                                                                  |

| P0.6 /          | 9            | 1             | D I/O or<br>A In | Port 0.6.                                                                                                                  |

| CNVSTR          |              |               | D In             | ADC0 External Convert Start Input.                                                                                         |

| NC              | —            | 4,9,11        |                  | No Connection.                                                                                                             |

## Table 3.1. Pin Definitions for the C8051T600/1/2/3/4/5

Figure 3.1. C8051T600/1/2/3/4/5-GM QFN11 Pinout Diagram (Top View)

Figure 3.2. C8051T600/1/2/3/4/5-GS SOIC14 Pinout Diagram (Top View)

## **Table 8.2. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                                                                                                                       | Conditions | Min | Тур | Max | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|

| Tsysl (SYSCLK low time)                                                                                                                                         |            | 18  | _   |     | ns    |

| Tsysh (SYSCLK high time)                                                                                                                                        |            | 18  | _   | _   | ns    |

| <ul> <li>Notes:</li> <li>1. Analog performance is not guara</li> <li>2. SYSCLK must be at least 32 kH.</li> <li>3. Supply current parameters special</li> </ul> |            | d.  |     |     |       |

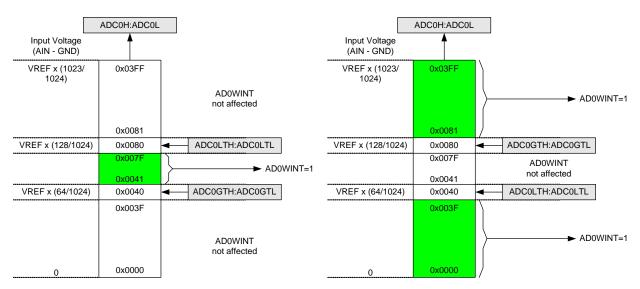

#### 9.4.1. Window Detector Example

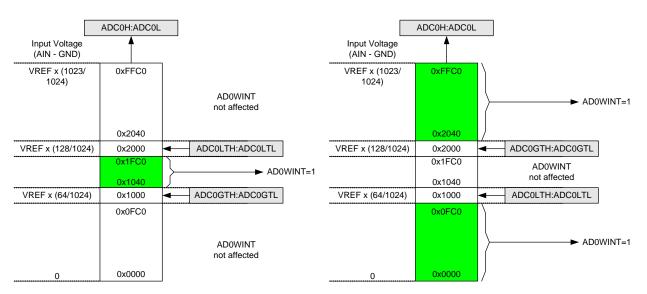

Figure 9.4 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 9.5 shows an example using left-justified data with the same comparison values.

Figure 9.4. ADC Window Compare Example: Right-Justified Data

Figure 9.5. ADC Window Compare Example: Left-Justified Data

# C8051T600/1/2/3/4/5/6

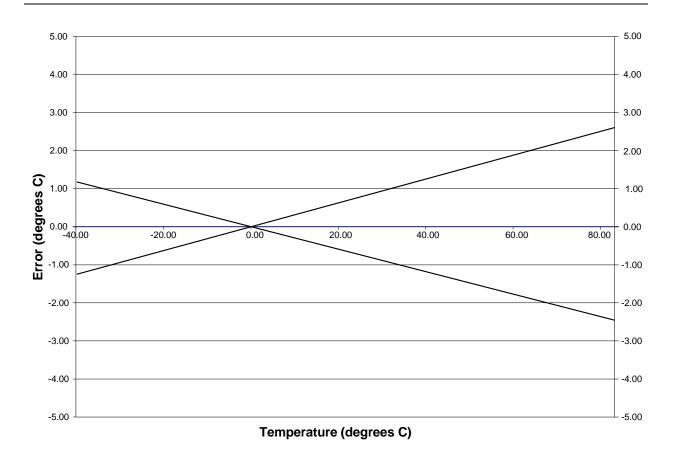

Figure 10.2. Temperature Sensor Error with 1-Point Calibration at 0 °C

# 11. Voltage Reference Options

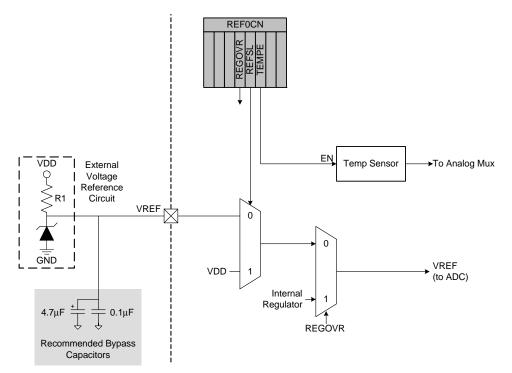

The voltage reference multiplexer for the ADC is configurable for use with an externally connected voltage reference, the unregulated power supply voltage ( $V_{DD}$ ), or the regulated 1.8 V internal supply (see Figure 11.1). The REFSL bit in the Reference Control register (REF0CN, SFR Definition 11.1) selects the reference source for the ADC. For an external source, REFSL should be set to 0 to select the VREF pin. To use  $V_{DD}$  as the reference source, REFSL should be set to 1. To override this selection and use the internal regulator as the reference source, the REGOVR bit can be set to 1. The electrical specifications for the voltage reference circuit are given in Section "8. Electrical Characteristics" on page 30.

**Important Note about the VREF Pin:** When using an external voltage reference, the VREF pin should be configured as an analog pin and skipped by the Digital Crossbar. Refer to Section "22. Port Input/Output" on page 106 for the location of the VREF pin, as well as details of how to configure the pin in analog mode and to be skipped by the crossbar.

Figure 11.1. Voltage Reference Functional Block Diagram

# C8051T600/1/2/3/4/5/6

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

## SFR Definition 13.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0xF8; Bit-Addressable

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0–.                                                    |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

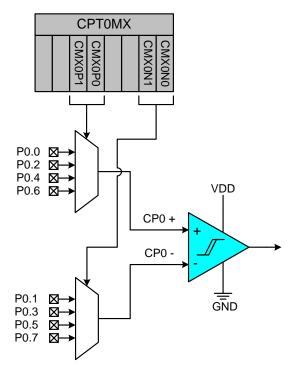

## 13.1. Comparator Multiplexer

C8051T600/1/2/3/4/5/6 devices include an analog input multiplexer to connect Port I/O pins to the comparator inputs. The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 13.3). The CMX-0P1–CMX0P0 bits select the Comparator0 positive input; the CMX0N1–CMX0N0 bits select the Comparator0 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "22.5. Special Function Registers for Accessing and Configuring Port I/O" on page 118).

Figure 13.3. Comparator Input Multiplexer Block Diagram

# SFR Definition 13.3. CPT0MX: Comparator0 MUX Selection

| Bit   | 7 | 6 | 5    | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|------|--------|---|---|------|--------|

| Name  |   |   | CMX0 | N[1:0] |   |   | CMX0 | P[1:0] |

| Туре  | R | R | R/   | R/W    |   | R | R/   | W      |

| Reset | 0 | 0 | 0    | 0      | 0 | 0 | 0    | 0      |

SFR Address = 0x9F

| Bit | Name       |                           | Function                                          |

|-----|------------|---------------------------|---------------------------------------------------|

| 7:6 | Unused     | Unused. Read = 00b        | ; Write = Don't Care.                             |

| 5:4 | CMX0N[1:0] | Comparator0 Negat         | tive Input MUX Selection.                         |

|     |            | 00:                       | P0.1                                              |

|     |            | 01:                       | P0.3                                              |

|     |            | 10:                       | P0.5                                              |

|     |            | 11:                       | P0.7                                              |

| 3:2 | Unused     | Unused. Read = 00b        | ; Write = Don't Care.                             |

| 1:0 | CMX0P[1:0] | <b>Comparator0</b> Positi | ive Input MUX Selection.                          |

|     |            | 00:                       | P0.0 (Available only on packages with 8 I/O pins) |

|     |            | 01:                       | P0.2                                              |

|     |            | 10:                       | P0.4                                              |

|     |            | 11:                       | P0.6 (Available only on packages with 8 I/O pins) |

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

# C8051T600/1/2/3/4/5/6

# SFR Definition 14.6. PSW: Program Status Word

| Bit   | 7          | 6                                                    | 5             | 4             | 3             | 2              | 1              | 0             |

|-------|------------|------------------------------------------------------|---------------|---------------|---------------|----------------|----------------|---------------|

| Nam   | e CY       | AC                                                   | F0            | RS            | 1:0]          | OV             | F1             | PARITY        |

| Туре  | R/W        | R/W                                                  | R/W           | R             | W             | R/W            | R/W            | R             |

| Rese  | t 0        | 0                                                    | 0             | 0             | 0             | 0              | 0              | 0             |

| SFR A | ddress = 0 | xD0; Bit-Addres                                      | sable         | I             | I             |                | I              |               |

| Bit   | Name       |                                                      |               |               | Function      |                |                |               |

| 7     | CY         | Carry Flag.                                          |               |               |               |                |                |               |

|       |            | This bit is set row (subtraction                     |               |               |               |                | •              | n) or a bor-  |

| 6     | AC         | Auxiliary Car                                        | ry Flag.      |               |               |                |                |               |

|       |            | This bit is set<br>borrow from (s<br>metic operation | subtraction)  |               |               |                |                |               |

| 5     | F0         | User Flag 0.                                         |               |               |               |                |                |               |

|       |            | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware cont   | rol.          |

| 4:3   | RS[1:0]    | Register Ban                                         | k Select.     |               |               |                |                |               |

|       |            | These bits sel                                       |               | -             | s used durin  | ig register ac | cesses.        |               |

|       |            | 00: Bank 0, A                                        |               |               |               |                |                |               |

|       |            | 01: Bank 1, A<br>10: Bank 2, A                       |               |               |               |                |                |               |

|       |            | 11: Bank 3, Ad                                       |               |               |               |                |                |               |

| 2     | OV         | Overflow Flag                                        | g.            |               |               |                |                |               |

|       |            | This bit is set                                      | to 1 under th | e following o | circumstance  | es:            |                |               |

|       |            | An ADD, A                                            |               |               |               |                |                |               |

|       |            | A MUL inst                                           |               |               | •             | -              | an 255).       |               |

|       |            | A DIV instr<br>The OV bit is                         |               | es a divide-b | -             |                | d DIV instru   | ctions in all |

|       |            | other cases.                                         |               | by the ADD,   | ADDC, 301     | DD, MOL, an    |                |               |

| 1     | F1         | User Flag 1.                                         |               |               |               |                |                |               |

|       |            | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware contr  | rol.          |

| 0     | PARITY     | Parity Flag.                                         |               |               |               |                |                |               |

|       |            | This bit is set t<br>if the sum is e                 | -             | ne sum of the | eight bits in | the accumu     | lator is odd a | and cleared   |

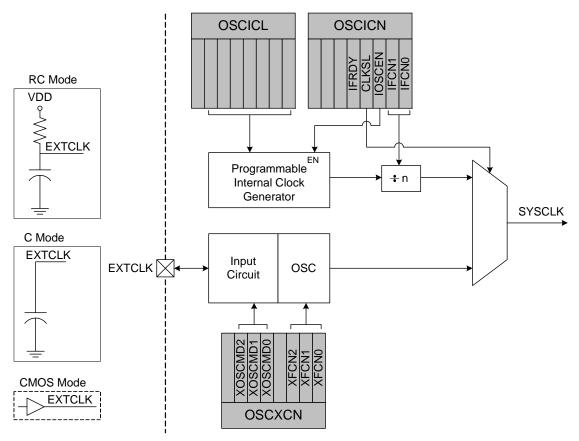

# 21. Oscillators and Clock Selection

C8051T600/1/2/3/4/5/6 devices include a programmable internal high-frequency oscillator and an external oscillator drive circuit. The internal high-frequency oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 21.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator (default). The internal oscillator offers a selectable post-scaling feature, which is initially set to divide the clock by 8.

Figure 21.1. Oscillator Options

## 21.1. System Clock Selection

The CLKSL bit in register OSCICN selects which oscillator source is used as the system clock. CLKSL must be set to 1 for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator and external oscillator, as long as the selected clock source is enabled and running.

The internal high-frequency oscillator requires little start-up time and may be selected as the system clock immediately following the register write, which enables the oscillator. The external RC and C modes also typically require no startup time.

## 22.5. Special Function Registers for Accessing and Configuring Port I/O

The Port I/O pins are accessed through the special function register P0, which is both byte addressable and bit addressable. When writing to this SFR, the value written is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target the Port 0 Latch register as the destination. The read-modify-write instructions include ANL, ORL, XRL, JBC, CPL, INC, DEC, or DJNZ for any usage. However, when the destination is an individual bit in P0, the read-modify-write instructions include MOV, CLR, or SETB. For all read-modify-write instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

The XBR0 register allows the individual Port pins to be assigned to digital functions or skipped by the crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions should have their XBR0 bit set to 1.

The Port input mode of the I/O pins is defined using the Port 0 Input Mode register (P0MDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers and is not automatic.

The output driver characteristics of the I/O pins are defined using the Port 0 Output Mode register (P0MD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the P0MDOUT settings.

## SFR Definition 22.4. P0: Port 0

| Bit   | 7 | 6               | 5 | 4   | 3    | 2 | 1 | 0 |  |  |

|-------|---|-----------------|---|-----|------|---|---|---|--|--|

| Name  |   |                 |   | P0[ | 7:0] |   |   |   |  |  |

| Туре  |   | R/W             |   |     |      |   |   |   |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |     |      |   |   |   |  |  |

#### SFR Address = 0x80; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

|     |         | Note: Bits 6 and 0 on the C8051                                                                                                               | T606 are read-only.                                                           |                                                                         |

|                              | Frequency: 24.5 MHz              |                      |                                |                       |                                                 |                  |                                  |  |  |  |  |

|------------------------------|----------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|--|

|                              | Target<br>Baud Rate<br>(bps)     | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |

|                              | 230400                           | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |  |  |

| ۰ ء                          | 115200                           | -0.32%               | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |  |  |  |  |

| SYSCLK from<br>Internal Osc. | 57600                            | 0.15%                | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |  |  |  |  |

| т<br>г<br>О                  | 28800                            | -0.32%               | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |  |  |  |

| CLK                          | 14400                            | 0.15%                | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |  |  |  |

| SYS(<br>Inter                | 9600                             | -0.32%               | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |  |  |  |

| s =                          | 2400                             | -0.32%               | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |  |  |  |

|                              | 1200                             | 0.15%                | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |  |  |  |

|                              | SCA1–SCA0 and<br>X = Don't care. | d T1M bit defini     | tions can be fo                | ound in Section 2     | 5.1.                                            |                  |                                  |  |  |  |  |

## Table 24.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

Table 24.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                              |                              |                      | Frequ                          | uency: 22.1184        | MHz                                             |                  |                                  |

|------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 96                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xD0                             |

| ب ع                          | 115200                       | 0.00%                | 192                            | SYSCLK                | XX                                              | 1                | 0xA0                             |

| from<br>Osc.                 | 57600                        | 0.00%                | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |

| K f<br>al O                  | 28800                        | 0.00%                | 768                            | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK from<br>External Osc. | 14400                        | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| YS<br>xte                    | 9600                         | 0.00%                | 2304                           | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| ίΩШ                          | 2400                         | 0.00%                | 9216                           | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|                              | 1200                         | 0.00%                | 18432                          | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| с.                           | 230400                       | 0.00%                | 96                             | EXTCLK/8              | 11                                              | 0                | 0xFA                             |

| from<br>Osc.                 | 115200                       | 0.00%                | 192                            | EXTCLK/8              | 11                                              | 0                | 0xF4                             |

| К<br>П<br>О                  | 57600                        | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

| CL                           | 28800                        | 0.00%                | 768                            | EXTCLK/8              | 11                                              | 0                | 0xD0                             |

| SYSCLK<br>Internal           | 14400                        | 0.00%                | 1536                           | EXTCLK/8              | 11                                              | 0                | 0xA0                             |

| s =                          | 9600                         | 0.00%                | 2304                           | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                       |                              |                      |                                | · · · · ·             |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

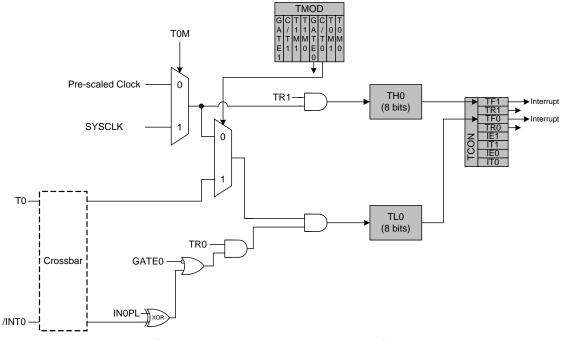

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0, and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1, or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

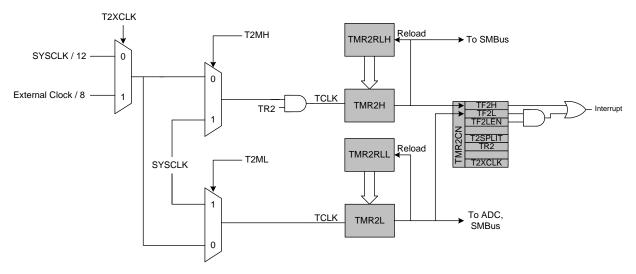

#### 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled, an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

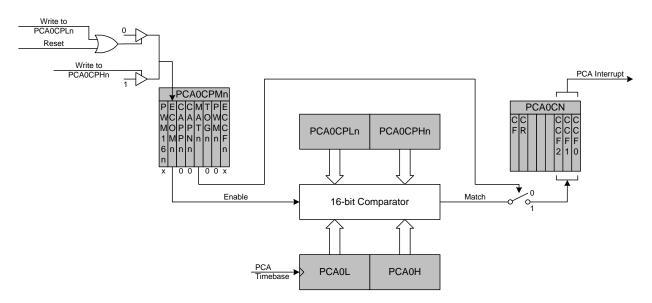

#### 26.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit Capture/Compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note about Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 26.5. PCA Software Timer Mode Diagram

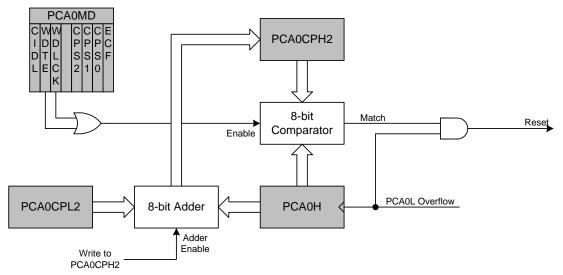

## 26.4. Watchdog Timer Mode

A programmable Watchdog Timer (WDT) function is available through the PCA Module 2. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH2) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE bit set in the PCA0MD register, Module 2 operates as a Watchdog Timer (WDT). The Module 2 high byte is compared to the PCA counter high byte; the Module 2 low byte holds the offset to be used when WDT updates are performed. The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled. The WDT will generate a reset shortly after code begins execution. To avoid this reset, the WDT should be explicitly disabled (and optionally re-configured and re-enabled if it is used in the system).

### 26.4.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2–CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 2 is forced into software timer mode.

- Writes to the Module 2 mode register (PCA0CPM2) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control bit (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH2 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH2. Upon a PCA0CPH2 write, PCA0H plus the offset held in PCA0CPL2 is loaded into PCA0CPH2 (See Figure 26.10).

Figure 26.10. PCA Module 2 with Watchdog Timer Enabled

# 26.5. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of the PCA.

## SFR Definition 26.1. PCA0CN: PCA Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

#### SFR Address = 0xD8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF     | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |

|     |        | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |

| 6   | CR     | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |

|     |        | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                                   |

|     |        | 0: PCA Counter/Timer disabled                                                                                                                                                                                                                                                                                      |

|     |        | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                                      |

| 5:3 | Unused | Unused. Read = 000b, Write = Don't care.                                                                                                                                                                                                                                                                           |

| 2   | CCF2   | PCA Module 2 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF2 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |

| 1   | CCF1   | PCA Module 1 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF1 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |

| 0   | CCF0   | PCA Module 0 Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |        | This bit is set by hardware when a match or capture occurs. When the CCF0 interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service rou-<br>tine. This bit is not automatically cleared by hardware and must be cleared by software.                                            |

# SFR Definition 26.4. PCA0L: PCA Counter/Timer Low Byte

| Bit   | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----------|-----|-----|-----|-----|-----|-----|

| Name  |     | PCA0[7:0] |     |     |     |     |     |     |

| Туре  | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xF9

| Bit   | Name                                                                                                                                                                                 | Function                                                                     |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| 7:0   | PCA0[7:0]                                                                                                                                                                            | PCA Counter/Timer Low Byte.                                                  |  |  |  |

|       |                                                                                                                                                                                      | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |  |  |  |

| Note: | <b>Note:</b> When the WDTE bit is set to 1, the PCA0L register cannot be modified by software. To change the contents the PCA0L register, the Watchdog Timer must first be disabled. |                                                                              |  |  |  |

## SFR Definition 26.5. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xFA

| Bit   | Name       | Function                                                                                                                                                                                                                                            |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | PCA0[15:8] | PCA Counter/Timer High Byte.                                                                                                                                                                                                                        |

|       |            | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer.<br>Reads of this register will read the contents of a "snapshot" register, whose contents<br>are updated only when the contents of PCA0L are read (see Section 26.1). |

| Note: |            | DTE bit is set to 1, the PCA0H register cannot be modified by software. To change the contents of egister, the Watchdog Timer must first be disabled.                                                                                               |