Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), UART/USART                                 |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | OTP                                                            |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 10-VFDFN Exposed Pad                                           |

| Supplier Device Package    | 11-QFN (3x3)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t601-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

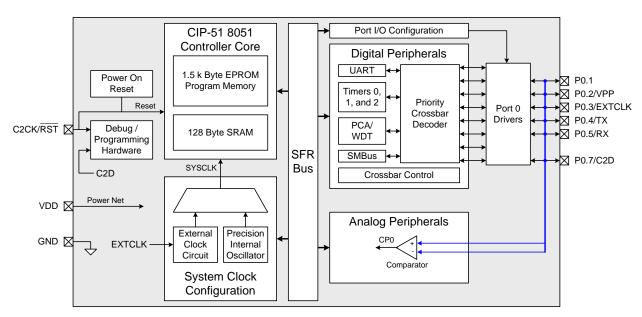

Figure 1.3. C8051T606 Block Diagram

Figure 3.5. C8051T606-ZM QFN10 Pinout Diagram (Top View)

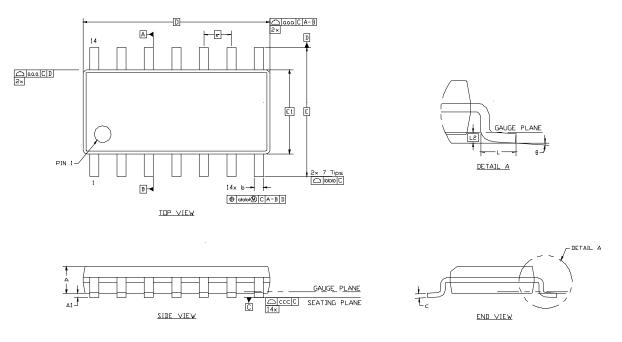

# 5. SOIC-14 Package Specifications

| Dimension | Min      | Nom      | Max  |  | Dimension | Min  | Nom      | Max  |

|-----------|----------|----------|------|--|-----------|------|----------|------|

| А         | _        | —        | 1.75 |  | L         | 0.40 | —        | 1.27 |

| A1        | 0.10     |          | 0.25 |  | L2        |      | 0.25 BSC |      |

| b         | 0.33     | —        | 0.51 |  | θ         | 0°   |          | 8°   |

| С         | 0.17     |          | 0.25 |  | aaa       |      | 0.10     |      |

| D         |          | 8.65 BSC |      |  | bbb       |      | 0.20     |      |

| E         | 6.00 BSC |          |      |  | CCC       |      | 0.10     |      |

| E1        | 3.90 BSC |          |      |  | ddd       |      | 0.25     |      |

| е         |          | 1.27 BSC |      |  |           |      |          |      |

## Table 5.1. SOIC-14 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS012, variation AB.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 8.2. Electrical Characteristics

### Table 8.2. Global Electrical Characteristics

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                                                  | Conditions                                                                                                                                                                                                                                      | Min        | Тур                        | Max                  | Units                |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|----------------------|----------------------|

| Supply Voltage (Note 1)                                                                    | Regulator in Normal Mode<br>Regulator in Bypass Mode                                                                                                                                                                                            | 1.8<br>1.7 | 3.0<br>1.8                 | 3.6<br>1.9           | V<br>V               |

| C8051T600/1/2/3/4/5 Digital Sup-<br>ply Current with CPU Active                            | $V_{DD} = 1.8 V$ , Clock = 25 MHz<br>$V_{DD} = 1.8 V$ , Clock = 1 MHz<br>$V_{DD} = 3.0 V$ , Clock = 25 MHz<br>$V_{DD} = 3.0 V$ , Clock = 1 MHz                                                                                                  |            | 4.3<br>2.0<br>5.0<br>2.4   | 6.0<br>—<br>6.0<br>— | mA<br>mA<br>mA<br>mA |

| C8051T600/1/2/3/4/5 Digital Sup-<br>ply Current with CPU Inactive (not<br>accessing EPROM) | $V_{DD} = 1.8 \text{ V}, \text{Clock} = 25 \text{ MHz} \\ V_{DD} = 1.8 \text{ V}, \text{Clock} = 1 \text{ MHz} \\ V_{DD} = 3.0 \text{ V}, \text{Clock} = 25 \text{ MHz} \\ V_{DD} = 3.0 \text{ V}, \text{Clock} = 1 \text{ MHz} \\ \end{cases}$ |            | 1.7<br>0.5<br>1.8<br>0.6   | 2.5<br>—<br>2.6<br>— | mA<br>mA<br>mA<br>mA |

| C8051T600/1/2/3/4/5 Digital Sup-<br>ply Current (shutdown)                                 | Oscillator not running (stop mode),<br>Internal Regulator Off                                                                                                                                                                                   | -          | 1                          | —                    | μA                   |

|                                                                                            | Oscillator not running (stop or sus-<br>pend mode), Internal Regulator On                                                                                                                                                                       | —          | 450                        | _                    | μA                   |

| C8051T606 Digital Supply Current with CPU Active                                           | $V_{DD} = 1.8 V$ , Clock = 25 MHz<br>$V_{DD} = 1.8 V$ , Clock = 1 MHz<br>$V_{DD} = 3.0 V$ , Clock = 25 MHz<br>$V_{DD} = 3.0 V$ , Clock = 1 MHz                                                                                                  |            | 4.6<br>1.9<br>5.0<br>1.9   | 6.0<br>—<br>6.0<br>— | mA<br>mA<br>mA<br>mA |

| C8051T606 Digital Supply Current<br>with CPU Inactive (not accessing<br>EPROM)             | $V_{DD} = 1.8 V$ , Clock = 25 MHz<br>$V_{DD} = 1.8 V$ , Clock = 1 MHz<br>$V_{DD} = 3.0 V$ , Clock = 25 MHz<br>$V_{DD} = 3.0 V$ , Clock = 1 MHz                                                                                                  |            | 1.7<br>0.35<br>1.8<br>0.36 | 2.5<br>—<br>2.6<br>— | mA<br>mA<br>mA<br>mA |

| C8051T606 Digital Supply Current (shutdown)                                                | Oscillator not running (stop mode),<br>Internal Regulator Off                                                                                                                                                                                   | —          | 1                          |                      | μA                   |

|                                                                                            | Oscillator not running (stop or suspend mode), Internal Regulator On                                                                                                                                                                            | —          | 300                        |                      | μA                   |

| Digital Supply RAM Data Retention<br>Voltage                                               |                                                                                                                                                                                                                                                 | _          | 1.5                        |                      | V                    |

| Specified Operating Temperature<br>Range                                                   |                                                                                                                                                                                                                                                 | -40        |                            | +85                  | °C                   |

| SYSCLK (system clock frequency)                                                            | (Note 2)                                                                                                                                                                                                                                        | 0          | —                          | 25                   | MHz                  |

Notes:

**1.** Analog performance is not guaranteed when  $V_{DD}$  is below 1.8 V.

2. SYSCLK must be at least 32 kHz to enable debugging.

3. Supply current parameters specified with Memory Power Controller enabled.

### Table 8.10. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL=0), -40 to +85 °C unless otherwise specified.

| Parameter                          | Conditions                      | Min       | Тур        | Max      | Units  |

|------------------------------------|---------------------------------|-----------|------------|----------|--------|

| DC Accuracy                        |                                 |           |            |          |        |

| Resolution                         |                                 |           | 10         |          | bits   |

| Integral Nonlinearity              |                                 | —         | ±0.5       | ±1       | LSB    |

| Differential Nonlinearity          | Guaranteed Monotonic            | —         | ±0.5       | ±1       | LSB    |

| Offset Error                       |                                 | -2        | 0          | 2        | LSB    |

| Full Scale Error                   |                                 | -2        | 0          | 2        | LSB    |

| Offset Temperature Coefficient     |                                 | —         | 45         | —        | ppm/°C |

| Dynamic performance (10 kHz s      | sine-wave single-ended input, ' | 1 dB belo | ow Full So | ale, 500 | ksps)  |

| Signal-to-Noise Plus Distortion    |                                 | 56        | 60         | —        | dB     |

| Total Harmonic Distortion          | Up to the 5th harmonic          | —         | 72         | —        | dB     |

| Spurious-Free Dynamic Range        |                                 | —         | -75        | —        | dB     |

| Conversion Rate                    |                                 | •         | L          |          |        |

| SAR Conversion Clock               |                                 | —         |            | 8.33     | MHz    |

| Conversion Time in SAR Clocks      | 10-bit Mode                     | 13        | —          | —        | clocks |

|                                    | 8-bit Mode                      | 11        | —          | —        | clocks |

| Track/Hold Acquisition Time        | $V_{DD} \ge 2.0 V$              | 300       |            | —        | ns     |

|                                    | V <sub>DD</sub> < 2.0 V         | 2.0       | —          | —        | μs     |

| Throughput Rate                    |                                 | —         | —          | 500      | ksps   |

| Analog Inputs                      |                                 | •         |            |          |        |

| ADC Input Voltage Range            |                                 | 0         |            | VREF     | V      |

| Sampling Capacitance               | 1x Gain                         | —         | 5          | —        | pF     |

|                                    | 0.5x Gain                       | —         | 3          | —        | pF     |

| Input Multiplexer Impedance        |                                 | —         | 5          | —        | kΩ     |

| Power Specifications               |                                 | •         | •          |          | •      |

| Power Supply Current               | Operating Mode, 500 ksps        | —         | 600        | 900      | μA     |

| (V <sub>DD</sub> supplied to ADC0) |                                 |           |            |          |        |

| Power Supply Rejection             |                                 | —         | -70        | —        | dB     |

## SFR Definition 13.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0       |

|-------|---|---|---|---|---|---|------|---------|

| Name  |   |   |   |   |   |   | CP0M | ID[1:0] |

| Туре  | R | R | R | R | R | R | R/   | W       |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 1    | 0       |

SFR Address = 0x9D

| Bit | Name   | Function                                                                                                                                                                                                                                                            |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Unused. Read = 000000b, Write = Don't Care.                                                                                                                                                                                                                         |

| 1:0 |        | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

| Mnemonic             | Description                              | Bytes | Clock<br>Cycles |

|----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operation | s                                        |       | 1               |

| ADD A, Rn            | Add register to A                        | 1     | 1               |

| ADD A, direct        | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri           | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data         | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn           | Add register to A with carry             | 1     | 1               |

| ADDC A, direct       | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri          | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data        | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn           | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct       | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri          | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data        | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                | Increment A                              | 1     | 1               |

| INC Rn               | Increment register                       | 1     | 1               |

| INC direct           | Increment direct byte                    | 2     | 2               |

| INC @Ri              | Increment indirect RAM                   | 1     | 2               |

| DEC A                | Decrement A                              | 1     | 1               |

| DEC Rn               | Decrement register                       | 1     | 1               |

| DEC direct           | Decrement direct byte                    | 2     | 2               |

| DEC @Ri              | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR             | Increment Data Pointer                   | 1     | 1               |

| MUL AB               | Multiply A and B                         | 1     | 4               |

| DIV AB               | Divide A by B                            | 1     | 8               |

| DA A                 | Decimal adjust A                         | 1     | 1               |

| Logical Operations   |                                          |       |                 |

| ANL A, Rn            | AND Register to A                        | 1     | 1               |

| ANL A, direct        | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri           | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data         | AND immediate to A                       | 2     | 2               |

| ANL direct, A        | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data    | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn            | OR Register to A                         | 1     | 1               |

| ORL A, direct        | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri           | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data         | OR immediate to A                        | 2     | 2               |

| ORL direct, A        | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data    | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn            | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct        | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri           | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data         | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A        | Exclusive-OR A to direct byte            | 2     | 2               |

Table 14.1. CIP-51 Instruction Set Summary

# SFR Definition 14.6. PSW: Program Status Word

| Bit   | 7          | 6                                                    | 5             | 4             | 3             | 2              | 1              | 0             |  |

|-------|------------|------------------------------------------------------|---------------|---------------|---------------|----------------|----------------|---------------|--|

| Nam   | e CY       | AC                                                   | F0            | RS            | 1:0]          | OV             | F1             | PARITY        |  |

| Туре  | R/W        | R/W                                                  | R/W           | R             | W             | R/W            | R/W            | R             |  |

| Rese  | t 0        | 0                                                    | 0 0 0 0 0 0 0 |               |               |                |                |               |  |

| SFR A | ddress = 0 | xD0; Bit-Addres                                      | sable         | I             | I             |                |                |               |  |

| Bit   | Name       |                                                      |               |               | Function      |                |                |               |  |

| 7     | CY         | Carry Flag.                                          |               |               |               |                |                |               |  |

|       |            | This bit is set row (subtraction                     |               |               |               |                | •              | n) or a bor-  |  |

| 6     | AC         | Auxiliary Car                                        | ry Flag.      |               |               |                |                |               |  |

|       |            | This bit is set<br>borrow from (s<br>metic operation | subtraction)  |               |               |                |                |               |  |

| 5     | F0         | User Flag 0.                                         |               |               |               |                |                |               |  |

|       |            | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware cont   | rol.          |  |

| 4:3   | RS[1:0]    | Register Ban                                         | k Select.     |               |               |                |                |               |  |

|       |            | These bits sel                                       |               | -             | s used durin  | ig register ac | cesses.        |               |  |

|       |            | 00: Bank 0, A                                        |               |               |               |                |                |               |  |

|       |            | 01: Bank 1, A<br>10: Bank 2, A                       |               |               |               |                |                |               |  |

|       |            | 11: Bank 3, Ad                                       |               |               |               |                |                |               |  |

| 2     | OV         | Overflow Flag                                        | g.            |               |               |                |                |               |  |

|       |            | This bit is set                                      | to 1 under th | e following o | circumstance  | es:            |                |               |  |

|       |            | An ADD, A                                            |               |               |               |                |                |               |  |

|       |            | A MUL inst                                           |               |               | •             | -              | an 255).       |               |  |

|       |            | A DIV instr<br>The OV bit is                         |               | es a divide-b | -             |                | d DIV instru   | ctions in all |  |

|       |            | other cases.                                         |               | by the ADD,   | ADDC, 301     | DD, MOL, an    |                |               |  |

| 1     | F1         | User Flag 1.                                         |               |               |               |                |                |               |  |

|       |            | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware contr  | rol.          |  |

| 0     | PARITY     | Parity Flag.                                         |               |               |               |                |                |               |  |

|       |            | This bit is set t<br>if the sum is e                 | -             | ne sum of the | eight bits in | the accumu     | lator is odd a | and cleared   |  |

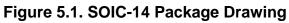

# **19. Reset Sources**

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 19.1. Reset Sources

## SFR Definition 19.1. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | MEMERR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                   | Read                                                                                                                                      |

|-------|------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                             | 0                                                                                                                                         |

| 6     | MEMERR     | EPROM Error Reset Flag.                                                                      | N/A                                                                                                                                                                     | Set to 1 if EPROM<br>read/write error caused<br>the last reset.                                                                           |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                           | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                   | Set to 1 if Comparator0 caused the last reset.                                                                                            |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a sys-<br>tem reset.                                                                                                                                 | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                              |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                     | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                          |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                          | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                   |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor and configures it as a reset source.<br>Writing 1 to this bit while the $V_{DD}$ monitor is disabled may cause a system reset. | Set to 1 any time a power-<br>on or $V_{DD}$ monitor reset<br>occurs.<br>When set to 1, all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                     | Set to 1 if RST pin caused the last reset.                                                                                                |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                              |                                                                                                                                           |

### 20.3. Program Memory CRC

A CRC engine is included on-chip, which provides a means of verifying EPROM contents once the device has been programmed. The CRC engine is available for EPROM verification even if the device is fully read and write locked, allowing for verification of code contents at any time.

The CRC engine is operated through the C2 debug and programming interface, and performs 16-bit CRCs on individual 256-byte blocks of program memory, or a 32-bit CRC the entire memory space. To prevent hacking and extrapolation of security-locked source code, the CRC engine will only allow CRCs to be performed on contiguous 256-byte blocks beginning on 256-byte boundaries (lowest 8-bits of address are 0x00). For example, the CRC engine can perform a CRC for locations 0x0400 through 0x04FF, but it cannot perform a CRC for locations 0x0401 through 0x0500, or on block sizes smaller or larger than 256 bytes.

### 20.3.1. Performing 32-bit CRCs on Full EPROM Content

A 32-bit CRC on the entire EPROM space is initiated by writing to the CRC1 byte over the C2 interface. The CRC calculation begins at address 0x0000 and ends at the end of user EPROM space. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 32-bit results will be available in the CRC3-0 registers. CRC3 is the MSB, and CRC0 is the LSB. The polynomial used for the 32-bit CRC calculation is 0x04C11DB7.

**Note**: If a 16-bit CRC has been performed since the last device reset, a device reset should be initiated before performing a 32-bit CRC operation.

#### 20.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks

A 16-bit CRC of individual 256-byte blocks of EPROM can be initiated by writing to the CRC0 byte over the C2 interface. The value written to CRC0 is the high byte of the beginning address for the CRC. For example, if CRC0 is written to 0x02, the CRC will be performed on the 256 bytes beginning at address 0x0200, and ending at address 0x2FF. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 16-bit results will be available in the CRC1-0 registers. CRC1 is the MSB, and CRC0 is the LSB. The polynomial for the 16-bit CRC calculation is 0x1021

# 21. Oscillators and Clock Selection

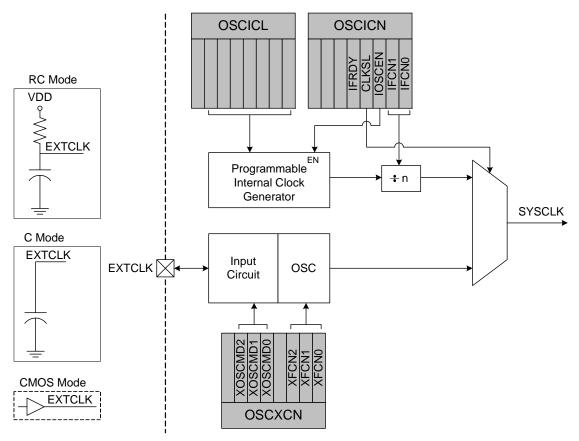

C8051T600/1/2/3/4/5/6 devices include a programmable internal high-frequency oscillator and an external oscillator drive circuit. The internal high-frequency oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 21.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator (default). The internal oscillator offers a selectable post-scaling feature, which is initially set to divide the clock by 8.

Figure 21.1. Oscillator Options

## 21.1. System Clock Selection

The CLKSL bit in register OSCICN selects which oscillator source is used as the system clock. CLKSL must be set to 1 for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator and external oscillator, as long as the selected clock source is enabled and running.

The internal high-frequency oscillator requires little start-up time and may be selected as the system clock immediately following the register write, which enables the oscillator. The external RC and C modes also typically require no startup time.

## SFR Definition 21.3. OSCXCN: External Oscillator Control

| Bit   | 7 | 6     | 5           | 4 | 3 | 2 | 1         | 0 |

|-------|---|-------|-------------|---|---|---|-----------|---|

| Name  |   | ×     | XOSCMD[2:0] |   |   |   | XFCN[2:0] |   |

| Туре  | R |       | R/W         |   |   |   | R/W       |   |

| Reset | 0 | 0 0 0 |             |   | 0 | 0 | 0         | 0 |

SFR Address = 0xB1

| Bit | Name        |         | Function                                    | ı               |  |  |  |  |

|-----|-------------|---------|---------------------------------------------|-----------------|--|--|--|--|

| 7   | Unused      | Read =  | Read = 0b; Write = Don't Care               |                 |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Select.                   |                 |  |  |  |  |

|     |             | 00x: Ex | ternal Oscillator circuit off.              |                 |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode.                     |                 |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode with divide          |                 |  |  |  |  |

|     |             |         | Coscillator Mode with divide by 2 stage     |                 |  |  |  |  |

|     |             |         | pacitor Oscillator Mode with divide by      | 2 stage.        |  |  |  |  |

|     |             | 11x: Re |                                             |                 |  |  |  |  |

| 3   | Unused      | Read =  | 0b; Write = Don't Care                      |                 |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa | al Oscillator Frequency Control Bits        | S.              |  |  |  |  |

|     |             | Set acc | ording to the desired frequency range       | for RC mode.    |  |  |  |  |

|     |             | Set acc | ording to the desired K Factor for C m      | iode.           |  |  |  |  |

|     |             | XFCN    | RC Mode                                     | C Mode          |  |  |  |  |

|     |             | 000     | f ≤ 25 kHz                                  | K Factor = 0.87 |  |  |  |  |

|     |             | 001     | 25 kHz < f ≤ 50 kHz                         | K Factor = 2.6  |  |  |  |  |

|     |             | 010     | 50 kHz < f ≤ 100 kHz                        | K Factor = 7.7  |  |  |  |  |

|     |             | 011     | 100 kHz < f ≤ 200 kHz                       | K Factor = 22   |  |  |  |  |

|     |             | 100     | 100 200 kHz < f $\le$ 400 kHz K Factor = 65 |                 |  |  |  |  |

|     |             | 101     | 400 kHz < f ≤ 800 kHz                       | K Factor = 180  |  |  |  |  |

|     |             | 110     | 800 kHz $<$ f $\leq$ 1.6 MHz                | K Factor = 664  |  |  |  |  |

|     |             | 111     | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$   | K Factor = 1590 |  |  |  |  |

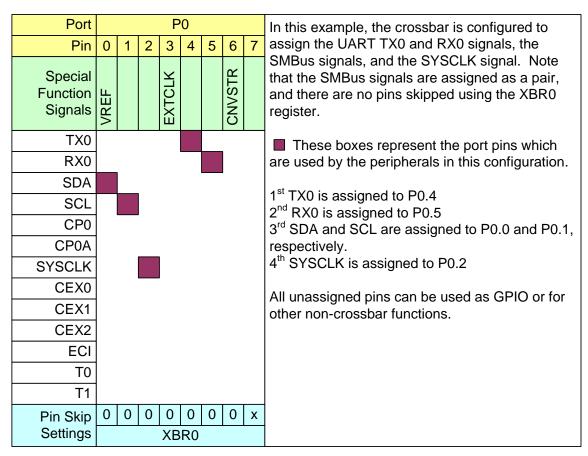

Figure 22.4. Priority Crossbar Decoder Example 1 - No Skipped Pins

## SFR Definition 22.5. P0MDIN: Port 0 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P0MDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xF1

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P0.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P0.n pin is not configured for analog mode.                                                |

|     |             | <b>Note:</b> Bits 6 and 0 on the C8051T606 are read-only.                                                   |

## SFR Definition 22.6. P0MDOUT: Port 0 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P0MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xA4

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull. |

|     |              | Note: Bits 6 and 0 on the C8051T606 are read-only.                                                                                                                          |

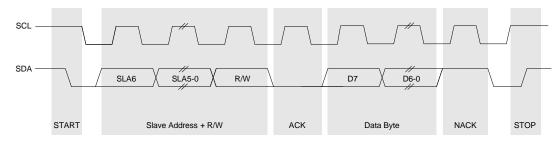

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time and waits for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data and waits for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 23.3 illustrates a typical SMBus transaction.

Figure 23.3. SMBus Transaction

### 23.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 23.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "23.3.5. SCL High (SMBus Free) Timeout" on page 123). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 23.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 23.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

## SFR Definition 24.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7             | 6                                                                                                                                                                                 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|

| Nam   | е             | SBUF0[7:0]                                                                                                                                                                        |   |   |   |   |   |   |  |

| Тур   | e             | R/W                                                                                                                                                                               |   |   |   |   |   |   |  |

| Rese  | et 0          | 0                                                                                                                                                                                 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0x9 | 9                                                                                                                                                                                 |   |   |   |   |   |   |  |

| Bit   | Name          | Function                                                                                                                                                                          |   |   |   |   |   |   |  |

| 7:0   | SBUF0[7:0]    | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                            |   |   |   |   |   |   |  |

|       |               | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for |   |   |   |   |   |   |  |

SBUF0 returns the contents of the receive latch.

serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of

## SFR Definition 25.2. TCON: Timer Control

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                                   | 6                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                       | 4                   | 3                             | 2   | 1   | 0   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|-----|-----|-----|--|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TF1                                 | TR1                                                                                                                                                                                                                                                                     | TF0                                                                                                                                                                                                                                     | TR0                 | IE1                           | IT1 | IE0 | IT0 |  |

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                 | R/W R/W R/W R/W R/W R                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                     |                               |     | R/W |     |  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th>0</th> <th>0</th> |                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                     |                               | 0   | 0   |     |  |

| SFR A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SFR Address = 0x88; Bit-Addressable |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Name                                | Function                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TF1                                 | Timer 1 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                                                                             | •                   |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                     | overflows. Ti<br>e CPU vecto  |     |     |     |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TR1                                 | Timer 1 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |                     |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | Timer 1 is e                                                                                                                                                                                                                                                            | nabled by se                                                                                                                                                                                                                            | etting this bit     | to 1.                         |     |     |     |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TF0                                 | Timer 0 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                                                                             |                     |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                           |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TR0                                 | Timer 0 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |                     |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | Timer 0 is e                                                                                                                                                                                                                                                            | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                            |                     |                               |     |     |     |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IE1                                 | External Interrupt 1.                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | can be clear                                                                                                                                                                                                                                                            | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode. |                     |                               |     |     |     |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IT1                                 | Interrupt 1 Type Select.                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive.<br>/INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 17.5).<br>0: /INT1 is level triggered.<br>1: /INT1 is edge triggered. |                                                                                                                                                                                                                                         |                     |                               |     |     |     |  |