Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                     |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | ОТР                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 11-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t601-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17.2. Interrupt Desciptor Descriptions                                                                                                                                | റ                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17.2. Interrupt Register Descriptions                                                                                                                                 |                                                                                                                                                                              |

| 17.3. INT0 and INT1 External Interrupt Sources                                                                                                                        |                                                                                                                                                                              |

| 18. Power Management Modes                                                                                                                                            |                                                                                                                                                                              |

| 18.1. Idle Mode                                                                                                                                                       |                                                                                                                                                                              |

| 18.2. Stop Mode                                                                                                                                                       |                                                                                                                                                                              |

| 19. Reset Sources                                                                                                                                                     |                                                                                                                                                                              |

| 19.1. Power-On Reset                                                                                                                                                  |                                                                                                                                                                              |

| 19.2. Power-Fail Reset/VDD Monitor                                                                                                                                    | 94                                                                                                                                                                           |

| 19.3. External Reset                                                                                                                                                  |                                                                                                                                                                              |

| 19.4. Missing Clock Detector Reset                                                                                                                                    | 94                                                                                                                                                                           |

| 19.5. Comparator0 Reset                                                                                                                                               | 94                                                                                                                                                                           |

| 19.6. PCA Watchdog Timer Reset                                                                                                                                        | 94                                                                                                                                                                           |

| 19.7. EPROM Error Reset                                                                                                                                               |                                                                                                                                                                              |

| 19.8. Software Reset                                                                                                                                                  | 95                                                                                                                                                                           |

| 20. EPROM Memory                                                                                                                                                      |                                                                                                                                                                              |

| 20.1. Programming and Reading the EPROM Memory                                                                                                                        |                                                                                                                                                                              |

| 20.1.1. EPROM Write Procedure                                                                                                                                         | 97                                                                                                                                                                           |

| 20.1.2. EPROM Read Procedure                                                                                                                                          |                                                                                                                                                                              |

| 20.2. Security Options                                                                                                                                                |                                                                                                                                                                              |

| 20.3. Program Memory CRC                                                                                                                                              | 90                                                                                                                                                                           |

| 20.3.1. Performing 32-bit CRCs on Full EPROM Content                                                                                                                  |                                                                                                                                                                              |

| 20.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks                                                                                                               |                                                                                                                                                                              |

| 21. Oscillators and Clock Selection                                                                                                                                   |                                                                                                                                                                              |

|                                                                                                                                                                       |                                                                                                                                                                              |

|                                                                                                                                                                       |                                                                                                                                                                              |

| 21.1. System Clock Selection                                                                                                                                          | 100                                                                                                                                                                          |

| 21.1. System Clock Selection<br>21.2. Programmable Internal High-Frequency (H-F) Oscillator                                                                           | 100<br>101                                                                                                                                                                   |

| 21.1. System Clock Selection<br>21.2. Programmable Internal High-Frequency (H-F) Oscillator<br>21.3. External Oscillator Drive Circuit                                | 100<br>101<br>103                                                                                                                                                            |

| <ul> <li>21.1. System Clock Selection</li> <li>21.2. Programmable Internal High-Frequency (H-F) Oscillator</li> <li>21.3. External Oscillator Drive Circuit</li></ul> | 100<br>101<br>103<br>105                                                                                                                                                     |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105                                                                                                                                              |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br><b> 106</b>                                                                                                                               |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br><b> 106</b><br>107                                                                                                                        |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br><b> 106</b><br>107<br>107                                                                                                                 |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107                                                                                                                  |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>108                                                                                                           |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br><b> 106</b><br>107<br>107<br>107<br>108<br>109                                                                                            |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>108<br>109<br>109                                                                                      |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>108<br>109<br>109<br>109                                                                               |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110                                                                        |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111                                                                 |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111<br>114                                                          |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111<br>114                                                          |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111<br>114<br>118<br><b> 120</b>                             |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111<br>114<br>118<br><b> 120</b>                             |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>110<br>111<br>114<br>118<br><b> 120</b><br>121        |

| <ul> <li>21.1. System Clock Selection</li></ul>                                                                                                                       | 100<br>101<br>103<br>105<br>105<br>105<br>107<br>107<br>107<br>107<br>107<br>107<br>107<br>107<br>109<br>109<br>109<br>109<br>110<br>111<br>114<br>118<br><b> 121</b><br>121 |

# List of Figures

| 1. | System Overview                                                           |            |

|----|---------------------------------------------------------------------------|------------|

|    | Figure 1.1. C8051T600/2/4 Block Diagram                                   | 14         |

|    | Figure 1.2. C8051T601/3/5 Block Diagram                                   | 14         |

|    | Figure 1.3. C8051T606 Block Diagram                                       |            |

| 2. | Ordering Information                                                      |            |

| 3. | Pin Definitions                                                           |            |

|    | Figure 3.1. C8051T600/1/2/3/4/5-GM QFN11 Pinout Diagram (Top View)        | 19         |

|    | Figure 3.2. C8051T600/1/2/3/4/5-GS SOIC14 Pinout Diagram (Top View)       | 19         |

|    | Figure 3.3. C8051T606-GM QFN11 Pinout Diagram (Top View)                  | 20         |

|    | Figure 3.4. C8051T606-GT MSOP10 Pinout Diagram (Top View)                 | 20         |

|    | Figure 3.5. C8051T606-ZM QFN10 Pinout Diagram (Top View)                  | 21         |

| 4. | QFN-11 Package Specifications                                             |            |

|    | Figure 4.1. QFN-11 Package Drawing                                        | 22         |

|    | Figure 4.2. QFN-11 PCB Land Pattern                                       | 23         |

| 5. | SOIC-14 Package Specifications                                            |            |

|    | Figure 5.1. SOIC-14 Package Drawing                                       |            |

|    | Figure 5.2. SOIC-14 Recommended PCB Land Pattern                          | 25         |

| 6. | MSOP-10 Package Specifications                                            |            |

|    | Figure 6.1. MSOP-10 Package Drawing                                       |            |

|    | Figure 6.2. MSOP-10 PCB Land Pattern                                      | 27         |

| 7. | QFN-10 Package Specifications                                             |            |

|    | Figure 7.1. QFN-10 Package Drawing                                        |            |

| _  | Figure 7.2. QFN-10 PCB Land Pattern                                       | 29         |

| 8. | Electrical Characteristics                                                |            |

|    | Figure 8.1. C8051T600/1/2/3/4/5 Normal Mode Supply Current vs. Frequency  | ~ ~        |

|    |                                                                           | 38         |

|    | Figure 8.2. C8051T606 Normal Mode Supply Current vs. Frequency (MPCE = 1) | 38         |

|    | Figure 8.3. C8051T600/1/2/3/4/5 Idle Mode Supply Current vs. Frequency    | ~~         |

|    | (MPCE = 1)                                                                |            |

| •  | Figure 8.4. C8051T606 Idle Mode Digital Current vs. Frequency (MPCE = 1)  | 39         |

| 9. | 10-Bit ADC (ADC0, C8051T600/2/4 only)                                     | 40         |

|    | Figure 9.1. ADC0 Functional Block Diagram                                 |            |

|    | Figure 9.2. 10-Bit ADC Track and Conversion Example Timing                |            |

|    | Figure 9.3. ADC0 Equivalent Input Circuits                                |            |

|    | Figure 9.4. ADC Window Compare Example: Right-Justified Data              |            |

|    | Figure 9.5. ADC Window Compare Example: Left-Justified Data               |            |

| 10 | Figure 9.6. ADC0 Multiplexer Block Diagram                                | 50         |

| IU | Figure 10.1. Temperature Sensor Transfer Function                         | <b>۲</b> 0 |

|    | Figure 10.2. Temperature Sensor Error with 1-Point Calibration at 0 °C    | 52         |

| 11 | . Voltage Reference Options                                               | 55         |

|    | Figure 11.1. Voltage Reference Functional Block Diagram                   | 55         |

| 12 | . Voltage Regulator (REG0)                                                | 55         |

| 12 |                                                                           |            |

| SFR Definition 25.1. CKCON: Clock Control                              |

|------------------------------------------------------------------------|

| SFR Definition 25.2. TCON: Timer Control                               |

| SFR Definition 25.3. TMOD: Timer Mode 152                              |

| SFR Definition 25.4. TL0: Timer 0 Low Byte 153                         |

| SFR Definition 25.5. TL1: Timer 1 Low Byte 153                         |

| SFR Definition 25.6. TH0: Timer 0 High Byte 154                        |

| SFR Definition 25.7. TH1: Timer 1 High Byte 154                        |

| SFR Definition 25.8. TMR2CN: Timer 2 Control 157                       |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte 158     |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte 158   |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte 158                      |

| SFR Definition 25.12. TMR2H Timer 2 High Byte 159                      |

| SFR Definition 26.1. PCA0CN: PCA Control                               |

| SFR Definition 26.2. PCA0MD: PCA Mode                                  |

| SFR Definition 26.3. PCA0CPMn: PCA Capture/Compare Mode                |

| SFR Definition 26.4. PCA0L: PCA Counter/Timer Low Byte                 |

| SFR Definition 26.5. PCA0H: PCA Counter/Timer High Byte                |

| SFR Definition 26.6. PCA0CPLn: PCA Capture Module Low Byte             |

| SFR Definition 26.7. PCA0CPHn: PCA Capture Module High Byte            |

| C2 Register Definition 27.1. C2ADD: C2 Address                         |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID                    |

| C2 Register Definition 27.3. REVID: C2 Revision ID                     |

| C2 Register Definition 27.4. DEVCTL: C2 Device Control                 |

| C2 Register Definition 27.5. EPCTL: EPROM Programming Control Register |

| C2 Register Definition 27.6. EPDAT: C2 EPROM Data                      |

| C2 Register Definition 27.7. EPSTAT: C2 EPROM Status                   |

| C2 Register Definition 27.8. EPADDRH: C2 EPROM Address High Byte       |

| C2 Register Definition 27.9. EPADDRL: C2 EPROM Address Low Byte        |

| C2 Register Definition 27.10. CRC0: CRC Byte 0                         |

| C2 Register Definition 27.11. CRC1: CRC Byte 1                         |

| C2 Register Definition 27.12. CRC2: CRC Byte 2                         |

| 02 Register Deminitor 21. 13. URUS. URU Dyle S                         |

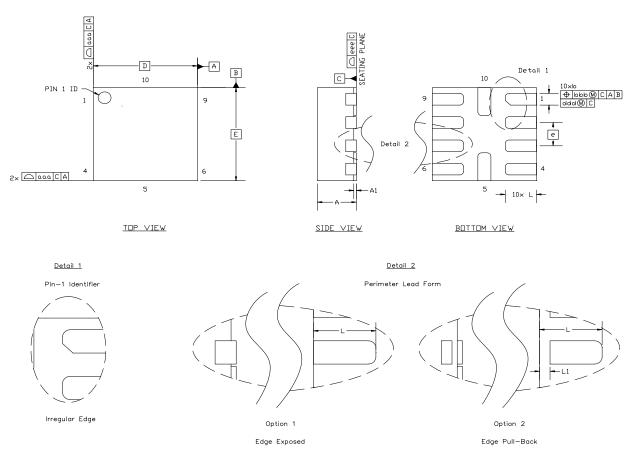

# 7. QFN-10 Package Specifications

# Figure 7.1. QFN-10 Package Drawing

| Dimension | Min       | Nom       | Max  | Dimension | Min  | Nom  | Max  |

|-----------|-----------|-----------|------|-----------|------|------|------|

| A         | 0.70      | 0.75      | 0.80 | L         | 0.55 | 0.60 | 0.65 |

| A1        | 0.00      |           | 0.05 | L1        |      | —    | 0.15 |

| b         | 0.18      | 0.25      | 0.30 | aaa       |      | —    | 0.10 |

| D         |           | 2.00 BSC. |      | bbb       | _    | —    | 0.10 |

| е         | 0.50 BSC. |           |      | CCC       | _    | —    | 0.05 |

| E         | 2.00 BSC. |           |      | ddd       |      | —    | 0.08 |

## Table 7.1. QFN-10 Package Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC outline MO-220, variation WCCD-5 except for feature L which is toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

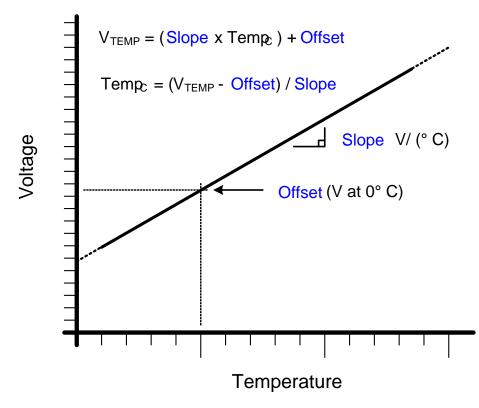

# 10. Temperature Sensor (C8051T600/2/4 only)

An on-chip temperature sensor is included on the C8051T600/2/4, which can be directly accessed via the ADC multiplexer. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 10.1. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 11.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 8.8 for the slope and offset parameters of the temperature sensor.

### 10.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 8.8 on page 35 for specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. A single-point offset measurement of the temperature sensor is performed on each device during production test. The registers TOFFH and TOFFL, shown in SFR Definition 10.1 and SFR Definition 10.2 represent the output of the ADC when reading the temperature sensor at 0 °C, and using the internal regulator as a voltage reference.

Figure 10.2 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C. Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.

# SFR Definition 11.1. REF0CN: Reference Control

| Bit   | 7 | 6 | 5 | 4      | 3     | 2     | 1 | 0 |

|-------|---|---|---|--------|-------|-------|---|---|

| Name  |   |   |   | REGOVR | REFSL | TEMPE |   |   |

| Туре  | R | R | R | R/W    | R/W   | R/W   | R | R |

| Reset | 0 | 0 | 0 | 0      | 0     | 0     | 0 | 0 |

SFR Address = 0xD1

| Bit | Name   | Function                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------|

| 7:5 | Unused | Unused. Read = 000b; Write = Don't Care.                                                                |

| 4   | REGOVR | Regulator Reference Override.                                                                           |

|     |        | This bit "overrides" the REFSL bit, and allows the internal regulator to be used as a reference source. |

|     |        | 0: The voltage reference source is selected by the REFSL bit.                                           |

|     |        | 1: The internal regulator is used as the voltage reference.                                             |

| 3   | REFSL  | Voltage Reference Select.                                                                               |

|     |        | This bit selects the ADCs voltage reference.                                                            |

|     |        | 0: V <sub>REF</sub> pin used as voltage reference.                                                      |

|     |        | 1: V <sub>DD</sub> used as voltage reference.                                                           |

| 2   | TEMPE  | Temperature Sensor Enable Bit.                                                                          |

|     |        | 0: Internal Temperature Sensor off.                                                                     |

|     |        | 1: Internal Temperature Sensor on.                                                                      |

| 1:0 | Unused | Unused. Read = 00b; Write = Don't Care.                                                                 |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

### 14.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 14.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 14.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

# SFR Definition 14.6. PSW: Program Status Word

| Bit               | 7                    | 6                                                    | 5             | 4             | 3             | 2              | 1              | 0             |  |  |

|-------------------|----------------------|------------------------------------------------------|---------------|---------------|---------------|----------------|----------------|---------------|--|--|

| Nam               | e CY                 | AC                                                   | F0            | RS            | 1:0]          | OV             | F1             | PARITY        |  |  |

| Туре              | R/W                  | R/W                                                  | R/W           | R             | W             | R/W            | R/W            | R             |  |  |

| Rese              | eset 0 0 0 0 0 0 0 0 |                                                      |               |               |               |                |                |               |  |  |

| SFR A             | ddress = 0           | I                                                    |               |               |               |                |                |               |  |  |

| Bit Name Function |                      |                                                      |               |               |               |                |                |               |  |  |

| 7                 | CY                   | Carry Flag.                                          |               |               |               |                |                |               |  |  |

|                   |                      | This bit is set row (subtraction                     |               |               |               |                | •              | n) or a bor-  |  |  |

| 6                 | AC                   | Auxiliary Car                                        | ry Flag.      |               |               |                |                |               |  |  |

|                   |                      | This bit is set<br>borrow from (s<br>metic operation | subtraction)  |               |               |                |                |               |  |  |

| 5                 | F0                   | User Flag 0.                                         |               |               |               |                |                |               |  |  |

|                   |                      | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware cont   | rol.          |  |  |

| 4:3               | RS[1:0]              | Register Ban                                         | k Select.     |               |               |                |                |               |  |  |

|                   |                      | These bits sel                                       |               | -             | s used durin  | ig register ac | cesses.        |               |  |  |

|                   |                      | 00: Bank 0, A                                        |               |               |               |                |                |               |  |  |

|                   |                      | 01: Bank 1, A<br>10: Bank 2, A                       |               |               |               |                |                |               |  |  |

|                   |                      | 11: Bank 3, Ad                                       |               |               |               |                |                |               |  |  |

| 2                 | OV                   | Overflow Flag                                        | g.            |               |               |                |                |               |  |  |

|                   |                      | This bit is set                                      | to 1 under th | e following o | circumstance  | es:            |                |               |  |  |

|                   |                      | An ADD, A                                            |               |               |               |                |                |               |  |  |

|                   |                      | A MUL inst                                           |               |               | •             | -              | an 255).       |               |  |  |

|                   |                      | A DIV instr<br>The OV bit is                         |               | es a divide-b | -             |                | d DIV instru   | ctions in all |  |  |

|                   |                      | other cases.                                         |               | by the ADD,   | ADDC, 301     | DD, MOL, an    |                |               |  |  |

| 1                 | F1                   | User Flag 1.                                         |               |               |               |                |                |               |  |  |

|                   |                      | This is a bit-ad                                     | ddressable, g | general purp  | ose flag for  | use under so   | oftware contr  | rol.          |  |  |

| 0                 | PARITY               | Parity Flag.                                         |               |               |               |                |                |               |  |  |

|                   |                      | This bit is set t<br>if the sum is e                 | -             | ne sum of the | eight bits in | the accumu     | lator is odd a | and cleared   |  |  |

# **15. Memory Organization**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types.

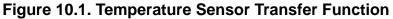

### 15.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051T600/1 implements 8192 bytes of this program memory space as in-system, Byte-Programmable EPROM, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Note that 512 bytes (0x1E00 – 0x1FFF) of this memory are reserved for factory use and are not available for user program storage. The C8051T602/3 implements 4096 bytes of EPROM program memory space; the C8051T604/5 implements 2048 bytes of EPROM program memory space, and the C8051T606 implement 1536 bytes of EPROM program memory space. C2 Register Definition 15.1 shows the program memory maps for C8051T600/1/2/3/4/5/6 devices.

Figure 15.1. Program Memory Map

Program memory is read-only from within firmware. Individual program memory bytes can be read using the MOVC instruction. This facilitates the use of EPROM space for constant storage.

# SFR Definition 17.2. IP: Interrupt Priority

| r     |   |   |     |     |     |     |     |     |

|-------|---|---|-----|-----|-----|-----|-----|-----|

| Bit   | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

| Name  |   |   | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 1 | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Unused. Read = 11b, Write = Don't Care.                                                                                                                                                                                                                        |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.                                                                                                                         |

|     |        | 1: Timer 2 interrupt set to high priority level.                                                                                                                                                                                                               |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                     |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                         |

| 2   | PX1    | <ul> <li>External Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 1 interrupt.</li> <li>0: External Interrupt 1 set to low priority level.</li> <li>1: External Interrupt 1 set to high priority level.</li> </ul> |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                         |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level.                                       |

# SFR Definition 17.5. IT01CF: INT0/INT1 Configuration

| Bit   | 7     | 6 | 5          | 4 | 3     | 2          | 1 | 0 |  |

|-------|-------|---|------------|---|-------|------------|---|---|--|

| Name  | IN1PL |   | IN1SL[2:0] |   | IN0PL | IN0SL[2:0] |   |   |  |

| Туре  | R/W   |   | R/W        |   | R/W   | R/W        |   |   |  |

| Reset | 0     | 0 | 0          | 0 | 0     | 0          | 0 | 1 |  |

SFR Address = 0xE4

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IN1PL      | INT1 Polarity.         0: INT1 input is active low.         1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6:4 | IN1SL[2:0] | INT1 Port Pin Selection Bits.         These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.         000: Select P0.0         001: Select P0.1         010: Select P0.2         011: Select P0.3         100: Select P0.4         101: Select P0.5         110: Select P0.7 |

| 3   | IN0PL      | INTO Polarity.         0: INTO input is active low.         1: INTO input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2:0 | IN0SL[2:0] | <b>INTO</b> Port Pin Selection Bits.<br>These bits select which Port pin is assigned to INTO. Note that this pin assignment is independent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>000: Select P0.0<br>001: Select P0.1<br>010: Select P0.2<br>011: Select P0.3<br>100: Select P0.4<br>101: Select P0.5<br>110: Select P0.7                                  |

# SFR Definition 18.1. PCON: Power Control

| Bit   | 7       | 6 | 5 | 4 | 3 | 2    | 1    | 0 |

|-------|---------|---|---|---|---|------|------|---|

| Name  | GF[5:0] |   |   |   |   | STOP | IDLE |   |

| Туре  | R/W R/W |   |   |   |   |      |      |   |

| Reset | 0       | 0 | 0 | 0 | 0 | 0    | 0    | 0 |

SFR Address = 0x87

| Bit | Name    | Function                                                                                                                                                                                                                                                         |  |  |  |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                       |  |  |  |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                  |  |  |  |

| 1   | STOP    | <ul> <li>Stop Mode Select.</li> <li>Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.</li> <li>1: CPU goes into Stop mode (internal oscillator stopped).</li> </ul>                                                        |  |  |  |

| 0   | IDLE    | Idle Mode Select.<br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts,<br>Serial Ports, and Analog Peripherals are still active.) |  |  |  |

## 19.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 19.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is disabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is enabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be enabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it has the potential to generate a system reset. The  $V_{DD}$  monitor is enabled and selected as a reset source by writing the PORSF flag in RSTSRC to 1.

See Figure 19.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 8.4 for complete electrical characteristics of the  $V_{DD}$  monitor.

### 19.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 8.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### **19.4. Missing Clock Detector Reset**

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the time specified in Section "8. Electrical Characteristics" on page 30, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

## 19.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 19.6. PCA Watchdog Timer Reset

The watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 170; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

## 21.3. External Oscillator Drive Circuit

The external oscillator circuit may drive an external capacitor or RC network. A CMOS clock may also provide a clock input. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the EXTCLK pin as shown in Figure 21.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 21.3).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as EXTCLK. The Port I/O Crossbar should be configured to skip the Port pin used by the oscillator circuit; see Section "22.3. Priority Crossbar Decoder" on page 111 for Crossbar configuration. Additionally, when using the external oscillator circuit in capacitor or RC mode, the associated Port pin should be configured as an **analog input**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "22.4. Port I/O Initialization" on page 114 for details on Port input mode selection.

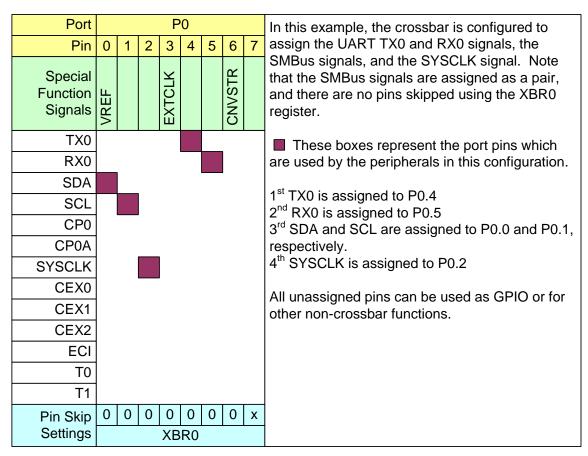

Figure 22.4. Priority Crossbar Decoder Example 1 - No Skipped Pins

### 23.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

### 23.2. SMBus Configuration

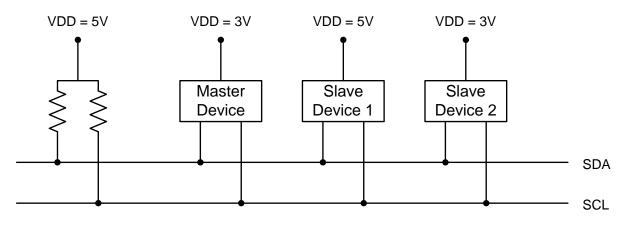

Figure 23.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 23.2. Typical SMBus Configuration

## 23.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device that transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 23.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

## 25. Timers

Each MCU includes three counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and one is a 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events, and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 offers 16-bit and split 8-bit timer functionality with auto-reload.

| Timer 0 and Timer 1 Modes:                 | Timer 2 Modes:                    |  |  |

|--------------------------------------------|-----------------------------------|--|--|

| 13-bit counter/timer                       | 16-bit timer with auto-reload     |  |  |

| 16-bit counter/timer                       |                                   |  |  |

| 8-bit counter/timer with<br>auto-reload    | Two 8-bit timers with auto-reload |  |  |

| Two 8-bit counter/timers<br>(Timer 0 only) |                                   |  |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (see SFR Definition 25.1 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

# SFR Definition 25.2. TCON: Timer Control

| Bit   | 7                         | 6                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                             | 4               | 3        | 2   | 1   | 0        |

|-------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----|-----|----------|

| Name  | TF1                       | TR1                                                                                                                                                                                                                                                                     | TF0                                                                                                                                                                           | TR0             | IE1      | IT1 | IE0 | IT0      |

| Туре  | R/W                       | R/W                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                           | R/W             | R/W      | R/W | R/W | R/W      |

| Rese  | t 0                       | 0                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                             | 0               | 0        | 0   | 0   | 0        |

| SFR A | ddress = 0x8              | 8; Bit-Addres                                                                                                                                                                                                                                                           | sable                                                                                                                                                                         |                 | I        |     | I   | <u> </u> |

| Bit   | Name                      |                                                                                                                                                                                                                                                                         |                                                                                                                                                                               |                 | Function |     |     |          |

| 7     | TF1                       | Timer 1 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                   | •               |          |     |     |          |

|       |                           |                                                                                                                                                                                                                                                                         | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine. |                 |          |     |     |          |

| 6     | TR1                       | Timer 1 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                    |                 |          |     |     |          |

|       |                           | Timer 1 is e                                                                                                                                                                                                                                                            | nabled by se                                                                                                                                                                  | etting this bit | to 1.    |     |     |          |

| 5     | TF0                       | Timer 0 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                   |                 |          |     |     |          |

|       |                           | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                           |                                                                                                                                                                               |                 |          |     |     |          |

| 4     | TR0                       | Timer 0 Run Control.                                                                                                                                                                                                                                                    |                                                                                                                                                                               |                 |          |     |     |          |

|       |                           | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                            |                                                                                                                                                                               |                 |          |     |     |          |

| 3     | IE1 External Interrupt 1. |                                                                                                                                                                                                                                                                         |                                                                                                                                                                               |                 |          |     |     |          |

|       |                           | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                                 |                                                                                                                                                                               |                 |          |     |     |          |

| 2     | IT1                       | Interrupt 1 Type Select.                                                                                                                                                                                                                                                |                                                                                                                                                                               |                 |          |     |     |          |

|       |                           | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive.<br>/INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 17.5).<br>0: /INT1 is level triggered.<br>1: /INT1 is edge triggered. |                                                                                                                                                                               |                 |          |     |     |          |

| 1     | IE0                       |                                                                                                                                                                                                                                                                         |                                                                                                                                                                               |                 |          |     |     |          |

|       |                           | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                                 |                                                                                                                                                                               |                 |          |     |     |          |

| 0     | IT0                       | Interrupt 0 Type Select.                                                                                                                                                                                                                                                |                                                                                                                                                                               |                 |          |     |     |          |

|       |                           | This bit selects whether the configured INTO interrupt will be edge or level sensitive.INTO is configured active low or high by the INOPL bit in register ITO1CF (see SFRDefinition 17.5).0: INTO is level triggered.1: INTO is edge triggered.                         |                                                                                                                                                                               |                 |          |     |     |          |

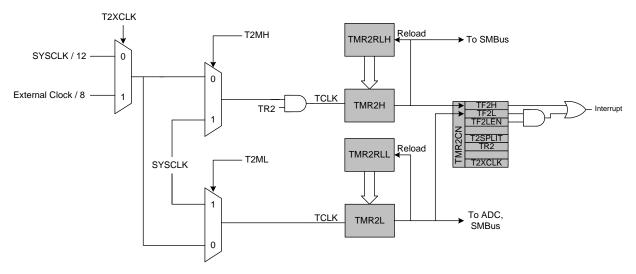

#### 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled, an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

The 8-bit offset held in PCA0CPH2 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.4, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL2) + (256 - PCA0L)$

## Equation 26.4. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH2 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF2 flag (PCA0CN.2) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- 1. Disable the WDT by writing a 0 to the WDTE bit.

- 2. Select the desired PCA clock source (with the CPS2–CPS0 bits).

- 3. Load PCA0CPL2 with the desired WDT update offset value.

- 4. Configure the PCA Idle Mode (set CIDL if the WDT should be suspended while the CPU is in Idle Mode).

- 5. Enable the WDT by setting the WDTE bit to 1.

- 6. Reset the WDT timer by writing to PCA0CPH2.

The PCA clock source and Idle Mode select cannot be changed while the WDT is enabled. The Watchdog Timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL2 defaults to 0x00. Using Equation 26.4, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.