Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                     |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | ОТР                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 11-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t602-gmr |

Email: info@E-XFL.COM

Details

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 3.5. C8051T606-ZM QFN10 Pinout Diagram (Top View)

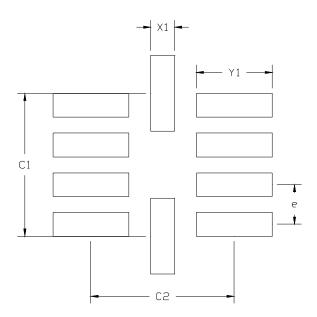

## Figure 7.2. QFN-10 PCB Land Pattern

### Table 7.2. QFN-10 PCB Land Pattern Dimensions

| Dimension | Dimension Min Max |      | Dimension | Min | Мах  |      |

|-----------|-------------------|------|-----------|-----|------|------|

| е         | 0.50 BSC.         |      |           | X1  | 0.20 | 0.30 |

| C1        | 1.70              | 1.80 |           | Y1  | 0.85 | 0.95 |

| C2        | 1.70              | 1.80 |           |     |      |      |

Notes: General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-782 guidelines.

- **4.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \,\mu$ m minimum, all the way around the pad.

Stencil Design

- **6.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

Card Assembly

- 9. A No-Clean, Type-3 solder paste is recommended.

- **10.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

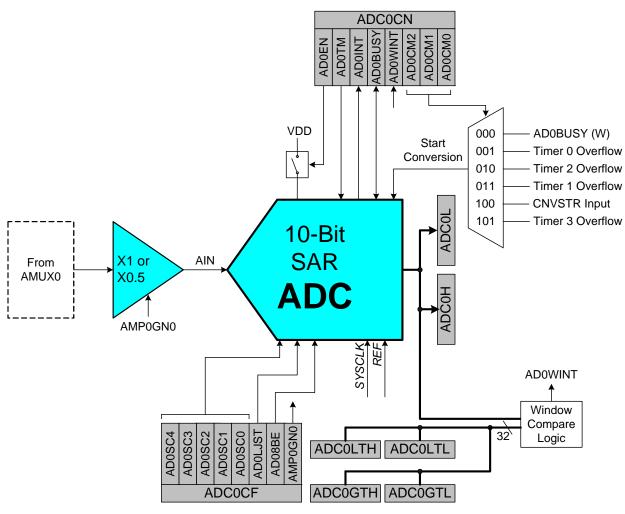

# 9. 10-Bit ADC (ADC0, C8051T600/2/4 only)

ADC0 on the C8051T600/2/4 is a 500 ksps, 10-bit successive-approximation-register (SAR) ADC with integrated track-and-hold, a gain stage programmable to 1x or 0.5x, and a programmable window detector. The ADC is fully configurable under software control via Special Function Registers. The ADC may be configured to measure various different signals using the analog multiplexer described in Section "9.5. ADC0 Analog Multiplexer (C8051T600/2/4 only)" on page 50. The voltage reference for the ADC is selected as described in Section "11. Voltage Reference Options" on page 55. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 9.1. ADC0 Functional Block Diagram

## SFR Definition 10.1. TOFFH: Temperature Offset Measurement High Byte

| Bit   | 7             | 6                                                                                                                                                                                                                                                                                                                                                                                                                        | 5          | 4            | 3           | 2      | 1      | 0      |  |  |  |  |

|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------------|--------|--------|--------|--|--|--|--|

| Nam   | e             |                                                                                                                                                                                                                                                                                                                                                                                                                          | 1          | TOF          | F[9:2]      |        |        | 1      |  |  |  |  |

| Туре  | 9             |                                                                                                                                                                                                                                                                                                                                                                                                                          |            | R            | /W          |        |        |        |  |  |  |  |

| Rese  | t Varies      | Varies                                                                                                                                                                                                                                                                                                                                                                                                                   | Varies     | Varies       | Varies      | Varies | Varies | Varies |  |  |  |  |

| SFR A | Address = 0xA | 13                                                                                                                                                                                                                                                                                                                                                                                                                       |            |              |             |        |        |        |  |  |  |  |

| Bit   | Name          |                                                                                                                                                                                                                                                                                                                                                                                                                          |            |              | Function    |        |        |        |  |  |  |  |

| 7:0   | TOFF[9:2]     | Temperatur                                                                                                                                                                                                                                                                                                                                                                                                               | e Sensor O | ffset High C | order Bits. |        |        |        |  |  |  |  |

|       |               | OFF[9:2]       Temperature Sensor Offset High Order Bits.         The temperature sensor offset registers represent the output of the ADC when measuring the temperature sensor at 0 °C, with the voltage reference set to the internal regulator. The temperature sensor offset information is left-justified. One LSB of this measurement is equivalent to one LSB of the ADC output under the measurement conditions. |            |              |             |        |        |        |  |  |  |  |

### SFR Definition 10.2. TOFFL: Temperature Offset Measurement Low Byte

| Bit   | 7 6           |        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|--------|---|---|---|---|---|---|

| Name  | TOFF          | -[1:0] |   |   |   |   |   |   |

| Туре  | R/            | W      | R | R | R | R | R | R |

| Reset | Varies Varies |        | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xA2

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | TOFF[1:0] | Temperature Sensor Offset Low Order Bits.                                                                                                                                                                                                                                                                                                                            |

|     |           | The temperature sensor offset registers represent the output of the ADC when mea-<br>suring the temperature sensor at 0 °C, with the voltage reference set to the internal<br>regulator. The temperature sensor offset information is left-justified. One LSB of this<br>measurement is equivalent to one LSB of the ADC output under the measurement<br>conditions. |

| 5:0 | Unused    | Unused. Read = 000000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                          |

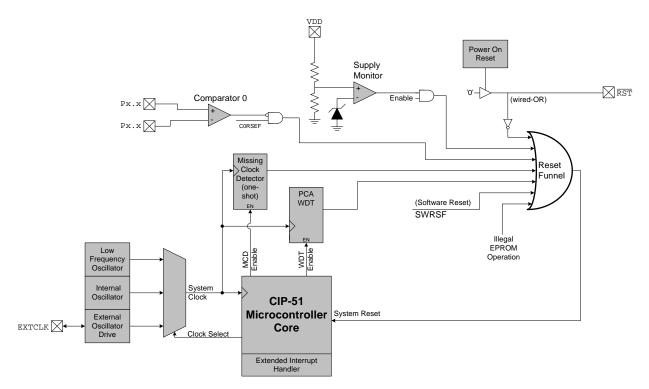

# **19. Reset Sources**

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 19.1. Reset Sources

#### 20.1.2. EPROM Read Procedure

- 1. Reset the device using the  $\overline{RST}$  pin.

- 2. Wait at least 20  $\mu s$  before sending the first C2 command.

- 3. Place the device in core reset: Write 0x04 to the DEVCTL register.

- 4. Write 0x00 to the EPCTL register.

- 5. Write the first EPROM address for reading to EPADDRH and EPADDRL.

- 6. Read a data byte from EPDAT. EPADDRH:L will increment by 1 after this read.

- 7. (Optional) Check the ERROR bit in register EPSTAT and abort the memory read operation if necessary.

- 8. If reading is not finished, return to Step 6 to read the next address in sequence, or return to Step 5 to select a new address.

- 9. Remove read mode (1st step): Write 0x40 to the EPCTL register.

- 10.Remove read mode (2nd step): Write 0x00 to the EPCTL register.

- 11. Reset the device: Write 0x02 and then 0x00 to the DEVCTL register.

### 20.2. Security Options

The C8051T600/1/2/3/4/5/6 devices provide security options to prevent unauthorized viewing of proprietary program code and constants. A security byte in EPROM address space can be used to lock the program memory from being read or written across the C2 interface. When read, the RDLOCK and WRLOCK bits in register EPSTAT will indicate the lock status of the location currently addressed by EPADDR. Table 20.1 shows the security byte decoding. See Section "15. Memory Organization" on page 74 for the security byte location and EPROM memory map.

Important Note: Once the security byte has been written, there are no means of unlocking the device. Locking memory from write access should be performed only after all other code has been successfully programmed to memory.

| Bits | Description                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------|

| 7–4  | Write Lock: Clearing any of these bits to logic 0 prevents all code memory from being written across the C2 interface.    |

| 3–0  | <b>Read Lock:</b> Clearing any of these bits to logic 0 prevents all code memory from being read across the C2 interface. |

### Table 20.1. Security Byte Decoding

#### 21.3.1. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 21.1, "RC Mode". The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 21.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

### **Equation 21.1. RC Mode Oscillator Frequency**

$$f = 1.23 \times 10^3 / (R \times C)$$

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>) / RC = 1.23(10<sup>3</sup>) / [246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 21.3, the required XFCN setting is 010b.

#### 21.3.2. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 21.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 21.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

#### Equation 21.2. C Mode Oscillator Frequency

$$f = (KF)/(R \times V_{DD})$$

For example: Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 21.3 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

## SFR Definition 22.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7            | 6                                                                 | 5                               | 4                            | 3             | 2             | 1         | 0          |  |  |  |  |

|-------|--------------|-------------------------------------------------------------------|---------------------------------|------------------------------|---------------|---------------|-----------|------------|--|--|--|--|

| Nam   | е            |                                                                   | XSKP[6:0]                       |                              |               |               |           |            |  |  |  |  |

| Тур   | e R          |                                                                   |                                 |                              | R/W           |               |           |            |  |  |  |  |

| Rese  | et 0         | 0*                                                                | 0                               | 0                            | 0             | 0             | 0         | 0*         |  |  |  |  |

| SFR A | Address = 0x | E1                                                                |                                 |                              |               |               |           |            |  |  |  |  |

| Bit   | Name         |                                                                   | Function                        |                              |               |               |           |            |  |  |  |  |

| 7     | Unused       | Unused. Read                                                      | d = 0; Write :                  | = Don't Care                 | •             |               |           |            |  |  |  |  |

| 6:0   | XSKP[6:0]    | Crossbar Ski<br>These bits sel<br>analog, specia<br>0: Correspond | ect port pins<br>al functions o | s to be skipp<br>or GPIO sho | uld be skippe | ed by the cro |           | s used for |  |  |  |  |

|       |              | 1: Correspond                                                     | ding P0.n pir                   | n is skipped l               | by the crosst | oar.          | e of '1'. |            |  |  |  |  |

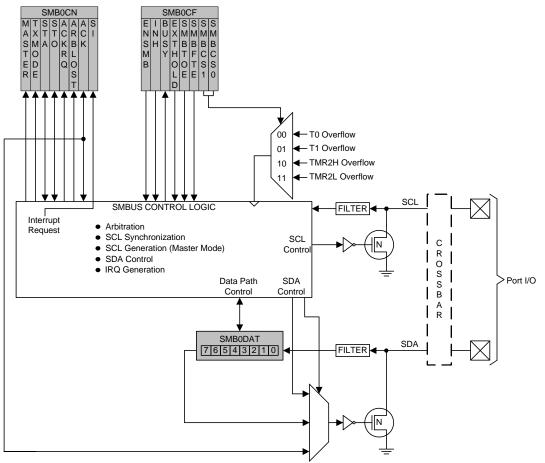

# 23. SMBus

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. A block diagram of the SMBus peripheral and the associated SFRs is shown in Figure 23.1.

Figure 23.1. SMBus Block Diagram

| SMBCS1 SMBCS0 SMBus Clock Source |   |                            |  |  |  |  |

|----------------------------------|---|----------------------------|--|--|--|--|

| 0                                | 0 | Timer 0 Overflow           |  |  |  |  |

| 0                                | 1 | Timer 1 Overflow           |  |  |  |  |

| 1                                | 0 | Timer 2 High Byte Overflow |  |  |  |  |

| 1                                | 1 | Timer 2 Low Byte Overflow  |  |  |  |  |

#### Table 23.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 23.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "25. Timers" on page 145.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 23.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 23.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 23.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

### Equation 23.2. Typical SMBus Bit Rate

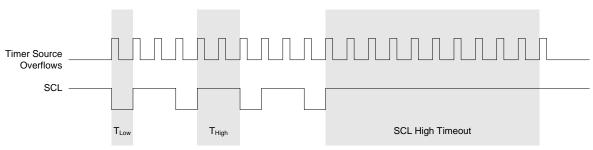

Figure 23.4 shows the typical SCL generation described by Equation 23.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by Equation 23.1.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                   | Cleared by Hardware When:                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| MASTER  | <ul> <li>A START is generated.</li> </ul>                                                                                                                                                                                                                                                               | <ul> <li>A STOP is generated.</li> </ul>                                       |

| WASTER  |                                                                                                                                                                                                                                                                                                         | <ul> <li>Arbitration is lost.</li> </ul>                                       |

|         | <ul> <li>START is generated.</li> </ul>                                                                                                                                                                                                                                                                 | <ul> <li>A START is detected.</li> </ul>                                       |

| TXMODE  | <ul> <li>SMB0DAT is written before the start of an</li> </ul>                                                                                                                                                                                                                                           | <ul> <li>Arbitration is lost.</li> </ul>                                       |

| TANODE  | SMBus frame.                                                                                                                                                                                                                                                                                            | <ul> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                                                    | Must be cleared by software.                                                   |

| STO     | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>                                                                                                                                                                                                                                  | A pending STOP is generated.                                                   |

|         | Arbitration is lost due to a detected STOP.                                                                                                                                                                                                                                                             |                                                                                |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                                                       | <ul> <li>After each ACK cycle.</li> </ul>                                      |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>         | <ul> <li>Each time SI is cleared.</li> </ul>                                   |

| ACK     | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul>      |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                               |

Table 23.3. Sources for Hardware Changes to SMB0CN

| â                 | V               | alu    | es F  | Rea     | d   |                                                                                             |                                                            |                                                            | lues<br>Vrit |     | tus<br>ected                   |      |

|-------------------|-----------------|--------|-------|---------|-----|---------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|--------------|-----|--------------------------------|------|

| Mode              | Status          | Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                                         | Typical Response Options                                   | STA                                                        | STO          | ACK | Next Status<br>Vector Expected |      |

| er                |                 |        | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0                                                          | 0            | Х   | 0001                           |      |

| smitte            | 010             | 00     | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0                                                          | 0            | Х   | 0100                           |      |

| Slave Transmitter |                 |        | 0     | 1       | х   | A slave byte was transmitted;<br>error detected.                                            | No action required (expecting Master to end transfer).     | 0                                                          | 0            | Х   | 0001                           |      |

| Slav              | 010             | 01     | 0     | х       | х   | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0                                                          | 0            | Х   | _                              |      |

|                   |                 |        |       |         |     |                                                                                             | If Write, Acknowledge received address                     | 0                                                          | 0            | 1   | 0000                           |      |

|                   | 1 0             |        |       |         | 0   | Х                                                                                           | A slave address + R/W was received; ACK requested.         | If Read, Load SMB0DAT with data byte; ACK received address | 0            | 0   | 1                              | 0100 |

|                   |                 |        |       |         |     |                                                                                             | NACK received address.                                     | 0                                                          | 0            | 0   | —                              |      |

|                   | 00 <sup>,</sup> | 10     |       |         |     |                                                                                             | If Write, Acknowledge received address                     | 0                                                          | 0            | 1   | 0000                           |      |

| eiver             |                 |        | 1     | 1       | х   | slave address + R/W received;                                                               | If Read, Load SMB0DAT with data byte; ACK received address | 0                                                          | 0            | 1   | 0100                           |      |

| lece              |                 |        |       |         |     | ACK requested.                                                                              | NACK received address.                                     | 0                                                          | 0            | 0   | _                              |      |

| Slave Receiver    |                 |        |       |         |     |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1                                                          | 0            | 0   | 1110                           |      |

| S                 | 000             | 01     | 0     | 0       | х   | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0                                                          | 0            | Х   | —                              |      |

|                   |                 |        | 1     | 1       | х   | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0                                                          | 0            | 0   | —                              |      |

|                   | 000             | 00     | 1     | 0       | х   | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0                                                          | 0            | 1   | 0000                           |      |

|                   |                 |        |       |         |     | Non requested.                                                                              | NACK received byte.                                        | 0                                                          | 0            | 0   | —                              |      |

| ion               | 00 <sup>.</sup> | 10     | 0     | 1       | х   | Lost arbitration while attempt-                                                             | Abort failed transfer.                                     | 0                                                          | 0            | Х   | _                              |      |

| ndit              |                 |        | č     |         |     | ing a repeated START.                                                                       | Reschedule failed transfer.                                | 1                                                          | 0            | Х   | 1110                           |      |

| Cor               | 000             | 01     | 0     | 1       | х   | Lost arbitration due to a                                                                   | Abort failed transfer.                                     | 0                                                          | 0            | Х   | —                              |      |

| Error Condition   |                 |        | Ĵ     |         |     | detected STOP.                                                                              | Reschedule failed transfer.                                | 1                                                          | 0            | Х   | 1110                           |      |

| S Eri             | 000             | 20     | 1     | 1       | х   | Lost arbitration while transmit-                                                            | Abort failed transfer.                                     | 0                                                          | 0            | 0   | —                              |      |

| Bus               | 000             |        | I     |         |     | ting a data byte as master.                                                                 | Reschedule failed transfer.                                | 1                                                          | 0            | 0   | 1110                           |      |

Table 23.4. SMBus Status Decoding

### 25.1. Timer 0 and Timer 1

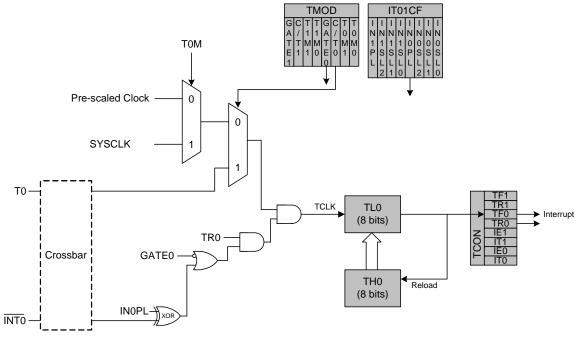

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "17.2. Interrupt Register Descriptions" on page 82); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "17.2. Interrupt Register (Section "17.2. Interrupt Register Descriptions" on page 82); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "17.2. Interrupt Register Descriptions" on page 82). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 25.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit in the TMOD register selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (refer to Section "22.3. Priority Crossbar Decoder" on page 111 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit in register CKCON. When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 25.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 17.5). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "17.2. Interrupt Register Descriptions" on page 82), facilitating pulse width measurements

| TR0                  | GATE0 | ΙΝΤΟ | Counter/Timer |  |  |  |  |  |  |

|----------------------|-------|------|---------------|--|--|--|--|--|--|

| 0                    | Х     | Х    | Disabled      |  |  |  |  |  |  |

| 1                    | 0     | Х    | Enabled       |  |  |  |  |  |  |

| 1                    | 1     | 0    | Disabled      |  |  |  |  |  |  |

| 1                    | 1     | 1    | Enabled       |  |  |  |  |  |  |

| Note: X = Don't Care |       |      |               |  |  |  |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT0 is used with Timer 1; the /INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 17.5).

#### 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 in the TCON register is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "17.3. INT0 and INT1 External Interrupt Sources" on page 87 for details on the external input signals INT0 and INT1).

Figure 25.2. T0 Mode 2 Block Diagram

## SFR Definition 25.4. TL0: Timer 0 Low Byte

| Bit   | 7            | 6                                                                                                | 5 | 4   | 3        | 2 | 1 | 0 |  |  |  |  |

|-------|--------------|--------------------------------------------------------------------------------------------------|---|-----|----------|---|---|---|--|--|--|--|

| Nam   | e            |                                                                                                  |   | TL0 | [7:0]    |   |   |   |  |  |  |  |

| Туре  | •            | R/W                                                                                              |   |     |          |   |   |   |  |  |  |  |

| Rese  | et 0         | 0                                                                                                | 0 | 0   | 0        | 0 | 0 | 0 |  |  |  |  |

| SFR A | ddress = 0x8 | A                                                                                                |   |     |          |   |   |   |  |  |  |  |

| Bit   | Name         |                                                                                                  |   |     | Function |   |   |   |  |  |  |  |

| 7:0   | TL0[7:0]     | TL0[7:0]       Timer 0 Low Byte.         The TL0 register is the low byte of the 16-bit Timer 0. |   |     |          |   |   |   |  |  |  |  |

## SFR Definition 25.5. TL1: Timer 1 Low Byte

| Bit                | 7          | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------------------|------------|----------|---|---|---|---|---|---|--|

| Name               | e TL1[7:0] |          |   |   |   |   |   |   |  |

| Туре               |            | R/W      |   |   |   |   |   |   |  |

| Reset              | t 0        | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x8B |            |          |   |   |   |   |   |   |  |

| Bit                | Name       | Function |   |   |   |   |   |   |  |

|                    |            |          |   |   |   |   |   |   |  |

| ы   | Name     | i uncuon                                                |  |

|-----|----------|---------------------------------------------------------|--|

| 7:0 | TL1[7:0] | Timer 1 Low Byte.                                       |  |

|     |          | The TL1 register is the low byte of the 16-bit Timer 1. |  |

## SFR Definition 25.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6             | 5                                                        | 4   | 3    | 2 | 1 | 0 |  |  |

|-------|--------------|---------------|----------------------------------------------------------|-----|------|---|---|---|--|--|

| Name  | e            | - 1           |                                                          | THO | 7:0] |   | L |   |  |  |

| Туре  | •            | R/W           |                                                          |     |      |   |   |   |  |  |

| Rese  | t 0          | 0             | 0                                                        | 0   | 0    | 0 | 0 | 0 |  |  |

| SFR A | ddress = 0x8 | 3C            |                                                          |     |      |   |   |   |  |  |

| Bit   | Name         | Name Function |                                                          |     |      |   |   |   |  |  |

| 7:0   | TH0[7:0]     | Timer 0 Hig   | Timer 0 High Byte.                                       |     |      |   |   |   |  |  |

|       |              | The TH0 rec   | The TH0 register is the high byte of the 16-bit Timer 0. |     |      |   |   |   |  |  |

## SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit                | 7                 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------------------|-------------------|-----|---|---|---|---|---|---|--|--|

| Name               | TH1[7:0]          |     |   |   |   |   |   |   |  |  |

| Туре               |                   | R/W |   |   |   |   |   |   |  |  |

| Reset              | 0                 | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR Address = 0x8D |                   |     |   |   |   |   |   |   |  |  |

| Di4                | Pit Name Eurotion |     |   |   |   |   |   |   |  |  |

| Bit | Name     | Function                                                 |

|-----|----------|----------------------------------------------------------|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |

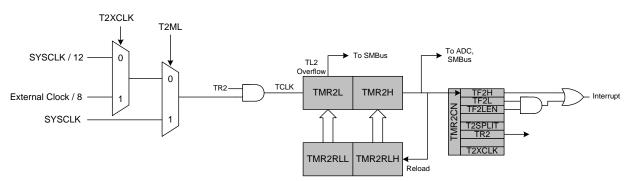

### 25.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by eight is synchronized with the system clock.

#### 25.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 25.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled, an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x000.

Figure 25.4. Timer 2 16-Bit Mode Block Diagram

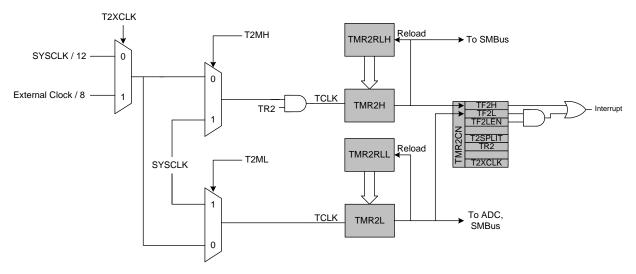

#### 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |  |  |

|------|--------|--------------------|--|--|

| 0    | 0      | SYSCLK / 12        |  |  |

| 0    | 1      | External Clock / 8 |  |  |

| 1    | Х      | SYSCLK             |  |  |

| T2ML | T2XCLK | TMR2L Clock Source |  |  |  |

|------|--------|--------------------|--|--|--|

| 0    | 0      | SYSCLK / 12        |  |  |  |

| 0    | 1      | External Clock / 8 |  |  |  |

| 1    | Х      | SYSCLK             |  |  |  |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled, an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

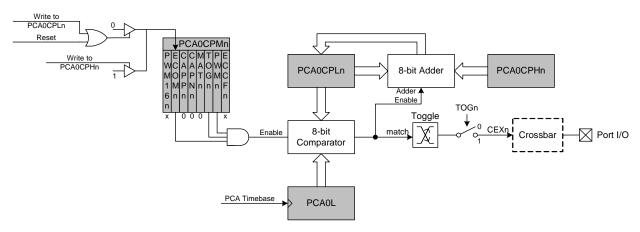

#### 26.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The Capture/Compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 26.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 26.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 26.7. PCA Frequency Output Mode

## C2 Register Definition 27.6. EPDAT: C2 EPROM Data

| Bit              | 7              | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------------|----------------|----------|---|---|---|---|---|---|--|

| Nam              | ame EPDAT[7:0] |          |   |   |   |   |   |   |  |

| Туре             | 9              | R/W      |   |   |   |   |   |   |  |

| Rese             | et O           | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

| C2 Address: 0xBF |                |          |   |   |   |   |   |   |  |

| Bit              | Name           | Function |   |   |   |   |   |   |  |

| 7.0              |                |          |   |   |   |   |   |   |  |

| Dit | Name       | i unction                                                            |

|-----|------------|----------------------------------------------------------------------|

| 7:0 | EPDAT[7:0] | C2 EPROM Data Register.                                              |

|     |            | This register is used to pass EPROM data during C2 EPROM operations. |

# C2 Register Definition 27.7. EPSTAT: C2 EPROM Status

| Bit   | 7           | 6                     | 5                                                                                    | 4              | 3             | 2            | 1 | 0     |  |  |

|-------|-------------|-----------------------|--------------------------------------------------------------------------------------|----------------|---------------|--------------|---|-------|--|--|

| Nam   | e WRLOCK    | RDLOCK                |                                                                                      |                |               |              |   | ERROR |  |  |

| Туре  | , R         | R                     | R                                                                                    | R              | R             | R            | R | R     |  |  |

| Rese  | -           | 0                     | 0                                                                                    | 0              | 0             | 0            | 0 | 0     |  |  |

| C2 Ad | dress: 0xB7 |                       |                                                                                      |                |               |              |   |       |  |  |

| Bit   | Name        | Function              |                                                                                      |                |               |              |   |       |  |  |

| 7     | WRLOCK      | Write Lock Indicator. |                                                                                      |                |               |              |   |       |  |  |

|       |             | Set to 1 if EF        | Set to 1 if EPADDR currently points to a write-locked address.                       |                |               |              |   |       |  |  |

| 6     | RDLOCK      | Read Lock             | Indicator.                                                                           |                |               |              |   |       |  |  |

|       |             | Set to 1 if EF        | PADDR curre                                                                          | ently points t | o a read-locl | ked address. |   |       |  |  |

| 5:1   | Unused      | Unused. Rea           | ad = Varies;                                                                         | Write = Don    | t Care.       |              |   |       |  |  |

| 0     | ERROR       | Error Indica          | itor.                                                                                |                |               |              |   |       |  |  |

|       |             | Set to 1 if las       | Set to 1 if last EPROM read or write operation failed due to a security restriction. |                |               |              |   |       |  |  |