Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                   |

| Program Memory Type        | ОТР                                                            |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 8x10b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 14-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t602-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition 9.1 | . ADC0CF: ADC0 Configuration                        | 44 |

|-----|----------------|-----------------------------------------------------|----|

| SFR | Definition 9.2 | 2. ADC0H: ADC0 Data Word MSB                        | 45 |

| SFR | Definition 9.3 | 3. ADC0L: ADC0 Data Word LSB                        | 45 |

|     |                | I. ADC0CN: ADC0 Control                             |    |

| SFR | Definition 9.5 | 5. ADC0GTH: ADC0 Greater-Than Data High Byte        | 47 |

| SFR | Definition 9.6 | 6. ADC0GTL: ADC0 Greater-Than Data Low Byte         | 47 |

|     |                | 7. ADC0LTH: ADC0 Less-Than Data High Byte           |    |

|     |                | 3. ADC0LTL: ADC0 Less-Than Data Low Byte            |    |

|     |                | 0. AMX0SL: AMUX0 Positive Channel Select            |    |

| SFR | Definition 10  | .1. TOFFH: Temperature Offset Measurement High Byte | 54 |

| SFR | Definition 10  | .2. TOFFL: Temperature Offset Measurement Low Byte  | 54 |

|     |                | 1. REF0CN: Reference Control                        |    |

|     |                | .1. REG0CN: Voltage Regulator Control               |    |

|     |                | .1. CPT0CN: Comparator0 Control                     |    |

|     |                | .2. CPT0MD: Comparator0 Mode Selection              |    |

| SFR | Definition 13  | .3. CPT0MX: Comparator0 MUX Selection               | 64 |

|     |                | .1. DPL: Data Pointer Low Byte                      |    |

|     |                | 2. DPH: Data Pointer High Byte                      |    |

|     |                | .3. SP: Stack Pointer                               |    |

|     |                | .4. ACC: Accumulator                                |    |

|     |                | .5. B: B Register                                   |    |

|     |                | .6. PSW: Program Status Word                        |    |

|     |                | .1. IE: Interrupt Enable                            |    |

|     |                | .2. IP: Interrupt Priority                          |    |

|     |                | .3. EIE1: Extended Interrupt Enable 1               |    |

|     |                | .4. EIP1: Extended Interrupt Priority 1             |    |

|     |                | .5. IT01CF: INT0/INT1 Configuration                 |    |

|     |                | .1. PCON: Power Control                             |    |

|     |                | .1. RSTSRC: Reset Source                            |    |

|     |                | .1. OSCICL: Internal H-F Oscillator Calibration     |    |

|     |                | .2. OSCICN: Internal H-F Oscillator Control 1       |    |

|     |                | .3. OSCXCN: External Oscillator Control1            |    |

|     |                | .1. XBR0: Port I/O Crossbar Register 01             |    |

|     |                | .2. XBR1: Port I/O Crossbar Register 11             |    |

|     |                | .3. XBR2: Port I/O Crossbar Register 21             |    |

| SFR | Definition 22  | .4. P0: Port 0 1                                    | 18 |

|     |                | .5. P0MDIN: Port 0 Input Mode 1                     |    |

|     |                | .6. P0MDOUT: Port 0 Output Mode 1                   |    |

|     |                | .1. SMB0CF: SMBus Clock/Configuration1              |    |

|     |                | .2. SMB0CN: SMBus Control 12                        |    |

|     |                | .3. SMB0DAT: SMBus Data 13                          |    |

|     |                | .1. SCON0: Serial Port 0 Control1                   |    |

| SFR | Definition 24  | .2. SBUF0: Serial (UART0) Port Data Buffer          | 43 |

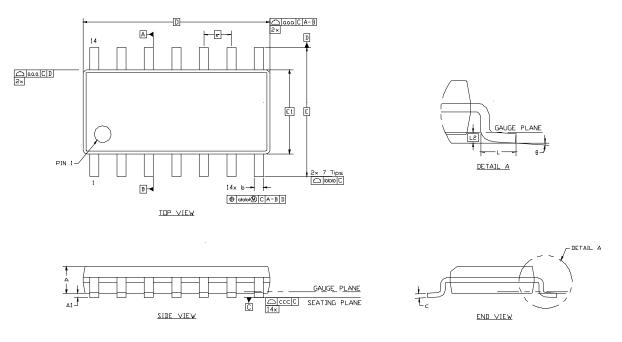

## 5. SOIC-14 Package Specifications

| Dimension | Min      | Nom      | Max  | Dimension | Min      | Nom  | Max  |

|-----------|----------|----------|------|-----------|----------|------|------|

| А         | _        | —        | 1.75 | L         | 0.40     | —    | 1.27 |

| A1        | 0.10     |          | 0.25 | L2        | 0.25 BSC |      |      |

| b         | 0.33     | —        | 0.51 | θ         | 0°       |      | 8°   |

| С         | 0.17     |          | 0.25 | aaa       |          | 0.10 |      |

| D         |          | 8.65 BSC |      | bbb       |          | 0.20 |      |

| E         |          | 6.00 BSC |      | CCC       |          | 0.10 |      |

| E1        | 3.90 BSC |          |      | ddd       |          | 0.25 |      |

| е         |          | 1.27 BSC |      |           |          |      |      |

#### Table 5.1. SOIC-14 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS012, variation AB.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 8.4. Reset Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter                                             | Conditions                                                                            | Min                    | Тур  | Max | Units    |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|------|-----|----------|

| RST Output Low Voltage                                | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                         | _                      |      | 0.6 | V        |

| RST Input High Voltage                                |                                                                                       | 0.75 x V <sub>DD</sub> | _    | _   | V        |

| RST Input Low Voltage                                 |                                                                                       | —                      | _    | 0.6 | $V_{DD}$ |

| RST Input Pullup Current                              | RST = 0.0 V                                                                           | —                      | 25   | 50  | μA       |

| V <sub>DD</sub> POR Ramp Time                         |                                                                                       | —                      | _    | 1   | ms       |

| V <sub>DD</sub> Monitor Threshold (V <sub>RST</sub> ) |                                                                                       | 1.7                    | 1.75 | 1.8 | V        |

| Missing Clock Detector<br>Timeout                     | Time from last system clock rising edge to reset initiation                           | 400                    | 625  | 900 | μs       |

| Reset Time Delay                                      | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                      |      | 60  | μs       |

| Minimum RST Low Time to<br>Generate a System Reset    |                                                                                       | 15                     |      | _   | μs       |

| V <sub>DD</sub> Monitor Turn-on Time                  | $V_{DD} = V_{RST} - 0.1 V$                                                            | —                      | 50   | —   | μs       |

| V <sub>DD</sub> Monitor Supply Current                |                                                                                       | —                      | 20   | 30  | μA       |

#### Table 8.5. Internal Voltage Regulator Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter           | Conditions  | Min | Тур | Max | Units |

|---------------------|-------------|-----|-----|-----|-------|

| Input Voltage Range |             | 1.8 | _   | 3.6 | V     |

| Bias Current        | Normal Mode |     | 30  | 50  | μA    |

#### **Table 8.6. EPROM Electrical Characteristics**

| Parameter                              | Conditions                                                                         | Min   | Тур | Max  | Units |  |  |

|----------------------------------------|------------------------------------------------------------------------------------|-------|-----|------|-------|--|--|

| EPROM Size                             | C8051T600/1                                                                        | 8192* |     | _    | bytes |  |  |

|                                        | C8051T602/3                                                                        | 4096  | _   | —    | bytes |  |  |

|                                        | C8051T604/5                                                                        | 2048  | —   |      | bytes |  |  |

|                                        | C8051T606                                                                          | 1536  | —   | —    | bytes |  |  |

| Write Cycle Time (per Byte)            |                                                                                    | 105   | 155 | 205  | μs    |  |  |

| Programming Voltage (V <sub>PP</sub> ) | C8051T600/1/2/3/4/5                                                                | 6.25  | 6.5 | 6.75 | V     |  |  |

| Programming Voltage (V <sub>PP</sub> ) | C8051T606                                                                          | 5.75  | 6.0 | 6.25 | V     |  |  |

| Note: 512 bytes at location 0x18       | Note: 512 bytes at location 0x1E00 to 0x1FFF are not available for program storage |       |     |      |       |  |  |

# Table 8.11. Comparator Electrical Characteristics $V_{DD}$ = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions            | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|-----------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV  | —     | 240  | —                      | ns    |

| Mode 0, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | —     | 240  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | —     | 400  | —                      | ns    |

| Mode 1, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | —     | 400  | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | —     | 650  | —                      | ns    |

| Mode 2, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | —     | 1100 | —                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | —     | 2000 | —                      | ns    |

| Mode 3, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV | —     | 5500 | —                      | ns    |

| Common-Mode Rejection Ratio                       |                       | —     | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00        | —     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01        | 2     | 5    | 8                      | mV    |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10        | 5     | 10   | 14                     | mV    |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11        | 11    | 20   | 28                     | mV    |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00        | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01        | 2     | 5    | 8                      | mV    |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10        | 5     | 10   | 14                     | mV    |

| Negative Hysteresis 4                             | CP0HYN1-0 = 11        | 11    | 20   | 28                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                       | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                       | -7.5  |      | 7.5                    | mV    |

| Power Specifications                              | •                     | •     |      |                        |       |

| Power Supply Rejection                            |                       | —     | 0.5  | —                      | mV/V  |

| Powerup Time                                      |                       | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                | —     | 26   | 50                     | μA    |

|                                                   | Mode 1                | —     | 10   | 20                     | μA    |

|                                                   | Mode 2                | —     | 3    | 6                      | μA    |

|                                                   | Mode 3                | —     | 0.5  | 2                      | μA    |

| Note: Vcm is the common-mode vo                   | Itage on CP0+ and CP0 |       |      |                        |       |

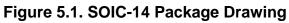

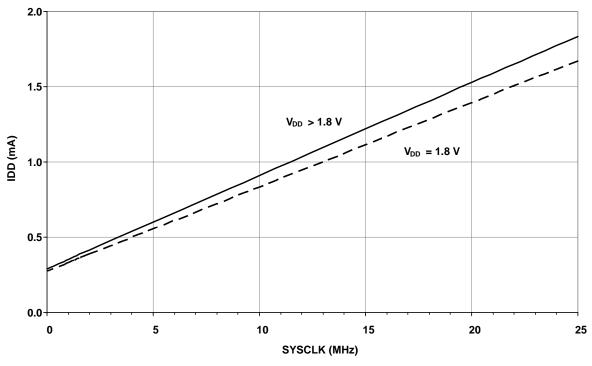

Figure 8.3. C8051T600/1/2/3/4/5 Idle Mode Supply Current vs. Frequency (MPCE = 1)

Figure 8.4. C8051T606 Idle Mode Digital Current vs. Frequency (MPCE = 1)

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4             |

| Program Branching    | ·                                                   |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16         | Long subroutine call                                | 3     | 4               |

| RET                  | Return from subroutine                              | 1     | 5               |

| RETI                 | Return from interrupt                               | 1     | 5               |

| AJMP addr11          | Absolute jump                                       | 2     | 3               |

| LJMP addr16          | Long jump                                           | 3     | 4               |

| SJMP rel             | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

## Table 14.1. CIP-51 Instruction Set Summary (Continued)

## **16. Special Function Registers**

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the C8051T600/1/2/3/4/5/6's resources and peripherals. The CIP-51 controller core duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the sub-systems unique to the C8051T600/1/2/3/4/5/6. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 16.1 lists the SFRs implemented in the C8051T600/1/2/3/4/5/6 device family.

The SFR registers are accessed any time the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 16.2, for a detailed description of each register.

| F8 | CPT0CN            | PCA0L         | PCA0H    | PCA0CPL0 | PCA0CPH0 |         |         |        |

|----|-------------------|---------------|----------|----------|----------|---------|---------|--------|

| F0 | В                 | P0MDIN        |          |          |          |         | EIP1    |        |

| E8 | ADC0CN            | PCA0CPL1      | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 |         |         | RSTSRC |

| E0 | ACC               | XBR0          | XBR1     | XBR2     | IT01CF   |         | EIE1    |        |

| D8 | PCA0CN            | PCA0MD        | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 |         |         |        |

| D0 | PSW               | <b>REF0CN</b> |          |          |          |         |         |        |

| C8 | TMR2CN            |               | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   |         |        |

| C0 | SMB0CN            | SMB0CF        | SMB0DAT  | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH | REG0CN |

| B8 | IP                |               |          | AMX0SL   | ADC0CF   | ADC0L   | ADC0H   |        |

| B0 |                   | OSCXCN        | OSCICN   | OSCICL   |          |         |         |        |

| A8 | IE                |               |          |          |          |         |         |        |

| A0 |                   |               | TOFFL    | TOFFH    | POMDOUT  |         |         |        |

| 98 | SCON0             | SBUF0         |          |          |          | CPT0MD  |         | CPT0MX |

| 90 |                   |               |          |          |          |         |         |        |

| 88 | TCON              | TMOD          | TL0      | TL1      | TH0      | TH1     | CKCON   |        |

| 80 | P0                | SP            | DPL      | DPH      |          |         |         | PCON   |

| Ī  | 0(8)              | 1(9)          | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)    | 7(F)   |

|    | (bit addressable) |               |          |          |          |         |         |        |

#### Table 16.1. Special Function Register (SFR) Memory Map

### Table 16.2. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                    | Page |

|----------|---------|--------------------------------|------|

| ACC      | 0xE0    | Accumulator                    | 72   |

| ADC0CF   | 0xBC    | ADC0 Configuration             | 44   |

| ADC0CN   | 0xE8    | ADC0 Control                   | 46   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Compare High | 47   |

#### 21.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051T600/1/2/3/4/5/6 devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 21.1.

On C8051T600/1/2/3/4/5/6 devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

#### SFR Definition 21.1. OSCICL: Internal H-F Oscillator Calibration

| Bit   | 7 | 6      | 5           | 4      | 3      | 2      | 1      | 0      |  |

|-------|---|--------|-------------|--------|--------|--------|--------|--------|--|

| Name  |   |        | OSCICL[6:0] |        |        |        |        |        |  |

| Туре  | R |        | R/W         |        |        |        |        |        |  |

| Reset | 0 | Varies | Varies      | Varies | Varies | Varies | Varies | Varies |  |

SFR Address = 0xB3

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                 |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused      | Unused. Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                     |

| 6:0 | OSCICL[6:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                    |

|     |             | These bits determine the internal oscillator period. When set to 0000000b, the H-F oscillator operates at its fastest setting. When set to 1111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

## 22. Port Input/Output

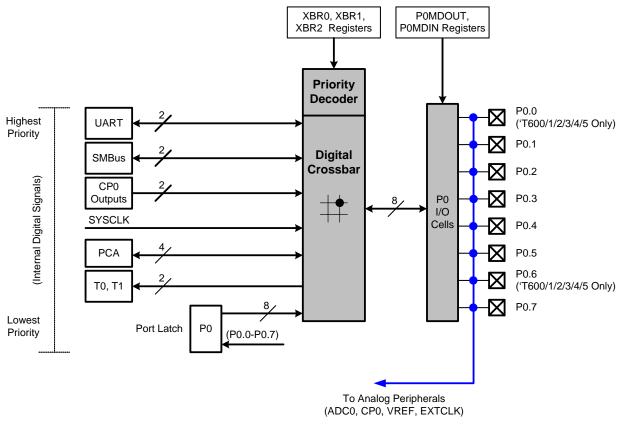

Digital and analog resources are available through eight I/O pins on the C8051T600/1/2/3/4/5, or six I/O pins on the C8051T606. Port pins P0.0-P0.7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 22.1. Port pin P0.7 is shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the P0 port latch, regardless of the crossbar settings.

The crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 22.3 and Figure 22.4). The registers XBR1 and XBR2, defined in SFR Definition 22.2 and SFR Definition 22.3, are used to select internal digital functions.

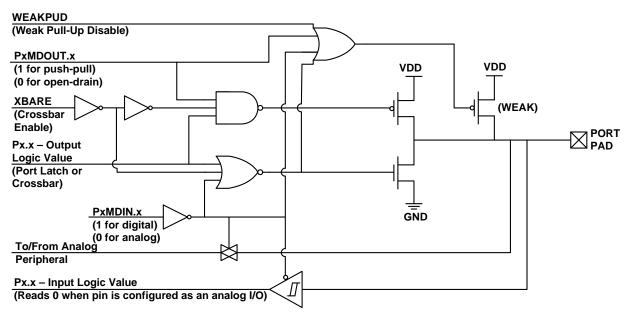

All Port I/Os are 5 V tolerant (refer to Figure 22.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (P0MDOUT). Complete Electrical Specifications for Port I/O are given in Section "8. Electrical Characteristics" on page 30.

Figure 22.1. Port I/O Functional Block Diagram

#### 22.1. Port I/O Modes of Operation

Port pins use the Port I/O cell shown in Figure 22.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the P0MDIN registers. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled until the crossbar is enabled (XBARE = 1).

#### 22.1.1. Port Pins Configured for Analog I/O

Any pins to be used as inputs to the comparator, ADC, external oscillator, or VREF should be configured for analog I/O (P0MDIN.n = 0). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. Port pins configured for analog I/O will always read back a value of 0.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 22.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SMBus, PCA, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (P0MDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the P0MDOUT registers.

Push-pull outputs (P0MDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high and low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

#### 22.5. Special Function Registers for Accessing and Configuring Port I/O

The Port I/O pins are accessed through the special function register P0, which is both byte addressable and bit addressable. When writing to this SFR, the value written is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target the Port 0 Latch register as the destination. The read-modify-write instructions include ANL, ORL, XRL, JBC, CPL, INC, DEC, or DJNZ for any usage. However, when the destination is an individual bit in P0, the read-modify-write instructions include MOV, CLR, or SETB. For all read-modify-write instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

The XBR0 register allows the individual Port pins to be assigned to digital functions or skipped by the crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions should have their XBR0 bit set to 1.

The Port input mode of the I/O pins is defined using the Port 0 Input Mode register (P0MDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers and is not automatic.

The output driver characteristics of the I/O pins are defined using the Port 0 Output Mode register (P0MD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the P0MDOUT settings.

#### SFR Definition 22.4. P0: Port 0

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P0[7:0]         |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

#### SFR Address = 0x80; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

|     |         | Note: Bits 6 and 0 on the C8051                                                                                                               | T606 are read-only.                                                           |                                                                         |

#### 23.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### 23.2. SMBus Configuration

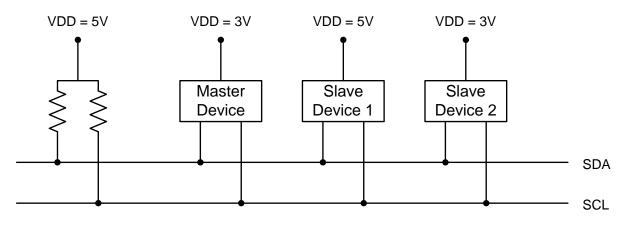

Figure 23.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 23.2. Typical SMBus Configuration

#### 23.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device that transmits a START and a slave address becomes the master for the duration of that transfer.

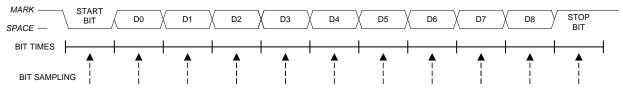

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 23.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

#### Table 23.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 23.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "25. Timers" on page 145.

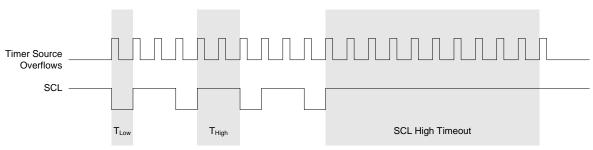

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 23.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 23.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 23.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 23.2. Typical SMBus Bit Rate

Figure 23.4 shows the typical SCL generation described by Equation 23.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by Equation 23.1.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable

| Bit     | Set by Hardware When:                                                                                                                                                                                                                                                                                   | Cleared by Hardware When:                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| MASTER  | <ul> <li>A START is generated.</li> </ul>                                                                                                                                                                                                                                                               | <ul> <li>A STOP is generated.</li> </ul>                                       |

| WASTER  |                                                                                                                                                                                                                                                                                                         | <ul> <li>Arbitration is lost.</li> </ul>                                       |

|         | <ul> <li>START is generated.</li> </ul>                                                                                                                                                                                                                                                                 | <ul> <li>A START is detected.</li> </ul>                                       |

| TXMODE  | <ul> <li>SMB0DAT is written before the start of an</li> </ul>                                                                                                                                                                                                                                           | <ul> <li>Arbitration is lost.</li> </ul>                                       |

| TANODE  | SMBus frame.                                                                                                                                                                                                                                                                                            | <ul> <li>SMB0DAT is not written before the start of an SMBus frame.</li> </ul> |

| STA     | <ul> <li>A START followed by an address byte is received.</li> </ul>                                                                                                                                                                                                                                    | Must be cleared by software.                                                   |

| STO     | <ul> <li>A STOP is detected while addressed as a<br/>slave.</li> </ul>                                                                                                                                                                                                                                  | A pending STOP is generated.                                                   |

|         | Arbitration is lost due to a detected STOP.                                                                                                                                                                                                                                                             |                                                                                |

| ACKRQ   | <ul> <li>A byte has been received and an ACK<br/>response value is needed (only when<br/>hardware ACK is not enabled).</li> </ul>                                                                                                                                                                       | <ul> <li>After each ACK cycle.</li> </ul>                                      |

| ARBLOST | <ul> <li>A repeated START is detected as a<br/>MASTER when STA is low (unwanted<br/>repeated START).</li> <li>SCL is sensed low while attempting to<br/>generate a STOP or repeated START<br/>condition.</li> <li>SDA is sensed low while transmitting a 1<br/>(excluding ACK bits).</li> </ul>         | <ul> <li>Each time SI is cleared.</li> </ul>                                   |

| ACK     | <ul> <li>The incoming ACK value is low<br/>(ACKNOWLEDGE).</li> </ul>                                                                                                                                                                                                                                    | <ul> <li>The incoming ACK value is high<br/>(NOT ACKNOWLEDGE).</li> </ul>      |

| SI      | <ul> <li>A START has been generated.</li> <li>Lost arbitration.</li> <li>A byte has been transmitted and an ACK/NACK received.</li> <li>A byte has been received.</li> <li>A START or repeated START followed by a slave address + R/W has been received.</li> <li>A STOP has been received.</li> </ul> | <ul> <li>Must be cleared by software.</li> </ul>                               |

Table 23.3. Sources for Hardware Changes to SMB0CN

#### 24.2.2. 9-Bit UART

The 9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

Figure 24.5. 9-Bit UART Timing Diagram

### SFR Definition 24.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit         7         6         5         4         3         2 |               |                                                                                                                                                                                   |   |   |          | 2 | 1 | 0 |  |

|-----------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----------|---|---|---|--|

| Nam                                                             | SBUF0[7:0]    |                                                                                                                                                                                   |   |   |          |   |   |   |  |

| Тур                                                             | e R/W         |                                                                                                                                                                                   |   |   |          |   |   |   |  |

| Rese                                                            | et 0          | 0                                                                                                                                                                                 | 0 | 0 | 0        | 0 | 0 | 0 |  |

| SFR A                                                           | Address = 0x9 | 9                                                                                                                                                                                 |   |   |          |   |   |   |  |

| Bit                                                             | Name          |                                                                                                                                                                                   |   |   | Function |   |   |   |  |

| 7:0                                                             | SBUF0[7:0]    | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                            |   |   |          |   |   |   |  |

|                                                                 |               | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for |   |   |          |   |   |   |  |

SBUF0 returns the contents of the receive latch.

serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of

|                              |                                  |                      | Fre                            | quency: 24.5 M        | IHz                                             |                  |                                  |

|------------------------------|----------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps)     | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                           | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |

| ۰ ء                          | 115200                           | -0.32%               | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |

| SYSCLK from<br>Internal Osc. | 57600                            | 0.15%                | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |

| т<br>г<br>О                  | 28800                            | -0.32%               | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |

| CLK                          | 14400                            | 0.15%                | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |

| SYS(<br>Inter                | 9600                             | -0.32%               | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |

| s =                          | 2400                             | -0.32%               | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |

|                              | 1200                             | 0.15%                | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |

|                              | SCA1–SCA0 and<br>X = Don't care. | d T1M bit defini     | tions can be fo                | ound in Section 2     | 5.1.                                            |                  |                                  |

#### Table 24.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

Table 24.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                              |                              |                      | Frequ                          | uency: 22.1184        | MHz                                             |                  |                                  |

|------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 96                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xD0                             |

| ب ع                          | 115200                       | 0.00%                | 192                            | SYSCLK                | XX                                              | 1                | 0xA0                             |

| from<br>Osc.                 | 57600                        | 0.00%                | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |

| K f<br>al O                  | 28800                        | 0.00%                | 768                            | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK from<br>External Osc. | 14400                        | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| YS<br>xte                    | 9600                         | 0.00%                | 2304                           | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| ίΩШ                          | 2400                         | 0.00%                | 9216                           | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|                              | 1200                         | 0.00%                | 18432                          | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| с.                           | 230400                       | 0.00%                | 96                             | EXTCLK/8              | 11                                              | 0                | 0xFA                             |

| from<br>Osc.                 | 115200                       | 0.00%                | 192                            | EXTCLK/8              | 11                                              | 0                | 0xF4                             |

| К<br>П<br>О                  | 57600                        | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

| CL                           | 28800                        | 0.00%                | 768                            | EXTCLK/8              | 11                                              | 0                | 0xD0                             |

| SYSCLK<br>Internal           | 14400                        | 0.00%                | 1536                           | EXTCLK/8              | 11                                              | 0                | 0xA0                             |

| s =                          | 9600                         | 0.00%                | 2304                           | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                       |                              |                      |                                | · · · · ·             |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

### SFR Definition 25.8. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4   | 3       | 2   | 1 | 0      |

|-------|------|------|--------|-----|---------|-----|---|--------|

| Name  | TF2H | TF2L | TF2LEN |     | T2SPLIT | TR2 |   | T2XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0   | 0       | 0   | 0 | 0      |

#### SFR Address = 0xC8; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2H    | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                               |

| 6   | TF2L    | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                            |

| 5   | TF2LEN  | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | When set to 1, this bit enables Timer 2 low byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                                                                                                                                                       |

| 4   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | T2SPLIT | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | <ul> <li>When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.</li> <li>0: Timer 2 operates in 16-bit auto-reload mode.</li> <li>1: Timer 2 operates as two 8-bit auto-reload timers.</li> </ul>                                                                                                                                                                                                                                                                                           |

| 2   | TR2     | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | T2XCLK  | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | <ul> <li>This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: Timer 2 clock is the system clock divided by 12.</li> <li>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

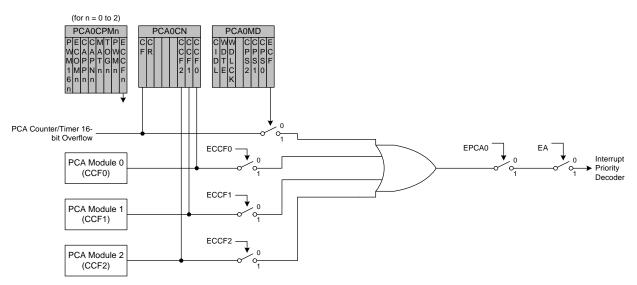

#### 26.2. PCA0 Interrupt Sources

Figure 26.3 shows a diagram of the PCA interrupt tree. There are four independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter, and the individual flags for each PCA channel (CCF0, CCF1, and CCF2), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 26.3. PCA Interrupt Block Diagram

### C2 Register Definition 27.6. EPDAT: C2 EPROM Data

| Bit   | 7                | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------------|---------------|---|---|---|---|---|---|--|

| Nam   | me EPDAT[7:0]    |               |   |   |   |   |   |   |  |

| Туре  | 9                | R/W           |   |   |   |   |   |   |  |

| Rese  | et O             | 0             | 0 | 0 | 0 | 0 | 0 | 0 |  |

| C2 Ac | C2 Address: 0xBF |               |   |   |   |   |   |   |  |

| Bit   | Name             | Name Function |   |   |   |   |   |   |  |

| 7.0   |                  |               |   |   |   |   |   |   |  |

| Dit | Name       | i diction                                                            |

|-----|------------|----------------------------------------------------------------------|

| 7:0 | EPDAT[7:0] | C2 EPROM Data Register.                                              |

|     |            | This register is used to pass EPROM data during C2 EPROM operations. |

## C2 Register Definition 27.7. EPSTAT: C2 EPROM Status

| Bit   | 7           | 6               | 5                                                                                    | 4              | 3             | 2            | 1 | 0     |  |  |

|-------|-------------|-----------------|--------------------------------------------------------------------------------------|----------------|---------------|--------------|---|-------|--|--|

| Nam   | e WRLOCK    | RDLOCK          |                                                                                      |                |               |              |   | ERROR |  |  |

| Туре  | , R         | R               | R                                                                                    | R              | R             | R            | R | R     |  |  |

| Rese  | -           | 0               | 0                                                                                    | 0              | 0             | 0            | 0 | 0     |  |  |

| C2 Ad | dress: 0xB7 |                 |                                                                                      |                |               |              |   |       |  |  |

| Bit   | Name        | Function        |                                                                                      |                |               |              |   |       |  |  |

| 7     | WRLOCK      | Write Lock      | Indicator.                                                                           |                |               |              |   |       |  |  |

|       |             | Set to 1 if EF  | PADDR curre                                                                          | ently points t | o a write-loc | ked address  |   |       |  |  |

| 6     | RDLOCK      | Read Lock       | Indicator.                                                                           |                |               |              |   |       |  |  |

|       |             | Set to 1 if EF  | PADDR curre                                                                          | ently points t | o a read-locl | ked address. |   |       |  |  |

| 5:1   | Unused      | Unused. Rea     | ad = Varies;                                                                         | Write = Don    | t Care.       |              |   |       |  |  |

| 0     | ERROR       | Error Indica    | Error Indicator.                                                                     |                |               |              |   |       |  |  |

|       |             | Set to 1 if las | Set to 1 if last EPROM read or write operation failed due to a security restriction. |                |               |              |   |       |  |  |