Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                     |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                    |

| Program Memory Type        | OTP                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 11-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t604-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 23.3.2. Arbitration                                     | 122 |

|---------------------------------------------------------|-----|

| 23.3.3. Clock Low Extension                             |     |

| 23.3.4. SCL Low Timeout                                 |     |

| 23.3.5. SCL High (SMBus Free) Timeout                   |     |

| 23.4. Using the SMBus                                   |     |

| 23.4.1. SMBus Configuration Register                    |     |

| 23.4.2. SMB0CN Control Register                         |     |

| 23.4.3. Data Register                                   |     |

| 23.5. SMBus Transfer Modes                              |     |

| 23.5.1. Write Sequence (Master)                         |     |

| 23.5.2. Read Sequence (Master)                          |     |

| 23.5.3. Write Sequence (Slave)                          |     |

| 23.5.4. Read Sequence (Slave)                           |     |

| 23.6. SMBus Status Decoding                             |     |

| 23.0. Smbus Status Decounty                             |     |

| 24.1. Enhanced Baud Rate Generation                     | -   |

| 24.1. Enhanced Badd Nate Generation                     |     |

| 24.2. Operational modes                                 |     |

| 24.2.1. 0-Bit UART                                      |     |

| 24.2.2. 9-bit OANT                                      |     |

| 24.3. Multiprocessor Communications                     |     |

| 25.1. Timer 0 and Timer 1                               |     |

| 25.1. 1inter 0 and 1inter 1                             |     |

| 25.1.2. Mode 1: 16-bit Counter/Timer                    |     |

| 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

| 25.2. Timer 2                                           |     |

| 25.2.1. 16-bit Timer with Auto-Reload                   |     |

| 25.2.2. 8-bit Timers with Auto-Reload                   |     |

| 26. Programmable Counter Array                          |     |

| 26.1. PCA Counter/Timer                                 |     |

| 26.2. PCA0 Interrupt Sources                            |     |

| 26.3. Capture/Compare Modules                           |     |

| 26.3.1. Edge-triggered Capture Mode                     | 164 |

| 26.3.2. Software Timer (Compare) Mode                   |     |

| 26.3.3. High-Speed Output Mode                          |     |

| 26.3.4. Frequency Output Mode                           |     |

| 26.3.5. 8-bit Pulse Width Modulator Mode                | 168 |

| 26.3.6. 16-Bit Pulse Width Modulator Mode               |     |

| 26.4. Watchdog Timer Mode                               |     |

| 26.4.1. Watchdog Timer Operation                        |     |

| 26.4.2. Watchdog Timer Operation                        |     |

| 26.5. Register Descriptions for PCA0                    |     |

| 27. C2 Interface                                        |     |

| 27.02 Interface Registers                               |     |

| 21.1. OZ IIIGIIAGE NEGISIEIS                            | 170 |

# List of Figures

| 1. | System Overview                                                           |            |

|----|---------------------------------------------------------------------------|------------|

|    | Figure 1.1. C8051T600/2/4 Block Diagram                                   | 14         |

|    | Figure 1.2. C8051T601/3/5 Block Diagram                                   | 14         |

|    | Figure 1.3. C8051T606 Block Diagram                                       |            |

| 2. | Ordering Information                                                      |            |

| 3. | Pin Definitions                                                           |            |

|    | Figure 3.1. C8051T600/1/2/3/4/5-GM QFN11 Pinout Diagram (Top View)        | 19         |

|    | Figure 3.2. C8051T600/1/2/3/4/5-GS SOIC14 Pinout Diagram (Top View)       | 19         |

|    | Figure 3.3. C8051T606-GM QFN11 Pinout Diagram (Top View)                  | 20         |

|    | Figure 3.4. C8051T606-GT MSOP10 Pinout Diagram (Top View)                 | 20         |

|    | Figure 3.5. C8051T606-ZM QFN10 Pinout Diagram (Top View)                  | 21         |

| 4. | QFN-11 Package Specifications                                             |            |

|    | Figure 4.1. QFN-11 Package Drawing                                        | 22         |

|    | Figure 4.2. QFN-11 PCB Land Pattern                                       | 23         |

| 5. | SOIC-14 Package Specifications                                            |            |

|    | Figure 5.1. SOIC-14 Package Drawing                                       |            |

|    | Figure 5.2. SOIC-14 Recommended PCB Land Pattern                          | 25         |

| 6. | MSOP-10 Package Specifications                                            |            |

|    | Figure 6.1. MSOP-10 Package Drawing                                       |            |

|    | Figure 6.2. MSOP-10 PCB Land Pattern                                      | 27         |

| 7. | QFN-10 Package Specifications                                             |            |

|    | Figure 7.1. QFN-10 Package Drawing                                        |            |

| _  | Figure 7.2. QFN-10 PCB Land Pattern                                       | 29         |

| 8. | Electrical Characteristics                                                |            |

|    | Figure 8.1. C8051T600/1/2/3/4/5 Normal Mode Supply Current vs. Frequency  | ~ ~        |

|    |                                                                           | 38         |

|    | Figure 8.2. C8051T606 Normal Mode Supply Current vs. Frequency (MPCE = 1) | 38         |

|    | Figure 8.3. C8051T600/1/2/3/4/5 Idle Mode Supply Current vs. Frequency    | ~~         |

|    | (MPCE = 1)                                                                |            |

| •  | Figure 8.4. C8051T606 Idle Mode Digital Current vs. Frequency (MPCE = 1)  | 39         |

| 9. | 10-Bit ADC (ADC0, C8051T600/2/4 only)                                     | 40         |

|    | Figure 9.1. ADC0 Functional Block Diagram                                 |            |

|    | Figure 9.2. 10-Bit ADC Track and Conversion Example Timing                |            |

|    | Figure 9.3. ADC0 Equivalent Input Circuits                                |            |

|    | Figure 9.4. ADC Window Compare Example: Right-Justified Data              |            |

|    | Figure 9.5. ADC Window Compare Example: Left-Justified Data               |            |

| 10 | Figure 9.6. ADC0 Multiplexer Block Diagram                                | 50         |

| IU | Figure 10.1. Temperature Sensor Transfer Function                         | <b>۲</b> 0 |

|    | Figure 10.2. Temperature Sensor Error with 1-Point Calibration at 0 °C    | 52         |

| 11 | . Voltage Reference Options                                               | 55         |

|    | Figure 11.1. Voltage Reference Functional Block Diagram                   | 55         |

| 12 | . Voltage Regulator (REG0)                                                | 55         |

| 12 |                                                                           |            |

| 18. Power Management Modes                                                       |

|----------------------------------------------------------------------------------|

| 19. Reset Sources                                                                |

| 20. EPROM Memory                                                                 |

| Table 20.1. Security Byte Decoding                                               |

| 21. Oscillators and Clock Selection                                              |

| 22. Port Input/Output                                                            |

| Table 22.1. Port I/O Assignment for Analog Functions 109                         |

| Table 22.2. Port I/O Assignment for Digital Functions 109                        |

| Table 22.3. Port I/O Assignment for External Digital Event Capture Functions 110 |

| 23. SMBus                                                                        |

| Table 23.1. SMBus Clock Source Selection 124                                     |

| Table 23.2. Minimum SDA Setup and Hold Times 125                                 |

| Table 23.3. Sources for Hardware Changes to SMB0CN 129                           |

| Table 23.4. SMBus Status Decoding 135                                            |

| 24. UART0                                                                        |

| Table 24.1. Timer Settings for Standard Baud Rates                               |

| Using The Internal 24.5 MHz Oscillator 144                                       |

| Table 24.2. Timer Settings for Standard Baud Rates                               |

| Using an External 22.1184 MHz Oscillator 144                                     |

| 25. Timers                                                                       |

| 26. Programmable Counter Array                                                   |

| Table 26.1. PCA Timebase Input Options                                           |

| Table 26.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules                 |

| Table 26.3. Watchdog Timer Timeout Intervals1 172                                |

| 27. C2 Interface                                                                 |

Figure 3.5. C8051T606-ZM QFN10 Pinout Diagram (Top View)

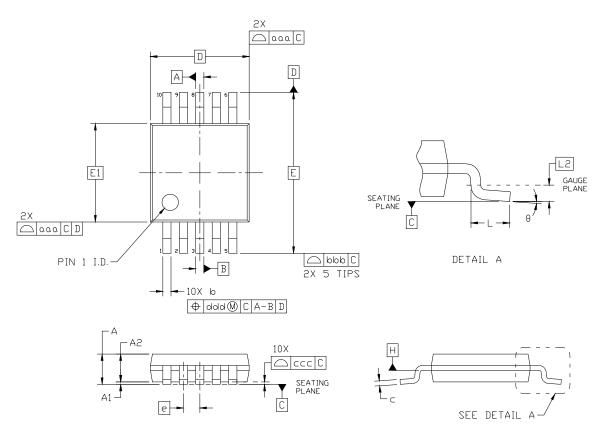

# 6. MSOP-10 Package Specifications

Figure 6.1. MSOP-10 Package Drawing

| Dimension | Min      | Nom  | Max  | Dimension | Min      | Nom  | Max  |

|-----------|----------|------|------|-----------|----------|------|------|

| A         | _        | —    | 1.10 | е         | 0.50 BSC |      |      |

| A1        | 0.00     | —    | 0.15 | L         | 0.40     | 0.60 | 0.80 |

| A2        | 0.75     | 0.85 | 0.95 | L2        | 0.25 BSC |      |      |

| b         | 0.17     | —    | 0.33 | θ         | 0°       |      | 8°   |

| С         | 0.08     |      | 0.23 | aaa       | _        | —    | 0.20 |

| D         | 3.00 BSC |      |      | bbb       |          | —    | 0.25 |

| E         | 4.90 BSC |      |      | CCC       |          | —    | 0.10 |

| E1        | 3.00 BSC |      |      | ddd       | _        | —    | 0.08 |

# Table 6.1. MSOP-10 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-187, Variation "BA".

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Table 8.7. Internal High-Frequency Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| <u> </u>                                          |                                                 |     |       |     |        |

|---------------------------------------------------|-------------------------------------------------|-----|-------|-----|--------|

| Parameter                                         | Conditions                                      | Min | Тур   | Max | Units  |

| Oscillator Frequency                              | IFCN = 11b                                      | 24  | 24.5  | 25  | MHz    |

| Oscillator Supply Current (from V <sub>DD</sub> ) | 25 °C, V <sub>DD</sub> = 3.0 V,<br>OSCICN.2 = 1 | —   | 450   | 700 | μA     |

| Power Supply Variance                             | Constant Temperature                            |     | ±0.02 |     | %/V    |

| Temperature Variance                              | Constant Supply                                 |     | ±20   |     | ppm/°C |

## Table 8.8. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                                             | Min | Тур  | Max | Units |  |  |  |  |

|--------------------------|--------------------------------------------------------|-----|------|-----|-------|--|--|--|--|

| Linearity                |                                                        | —   | ±0.5 | —   | °C    |  |  |  |  |

| Slope                    |                                                        | —   | 3.2  | —   | mV/°C |  |  |  |  |

| Slope Error*             |                                                        | —   | ±80  | —   | µV/°C |  |  |  |  |

| Offset                   | Temp = 0 °C                                            |     | 903  | _   | mV    |  |  |  |  |

| Offset Error*            | Temp = 0 °C                                            |     | ±10  |     | mV    |  |  |  |  |

| Note: Represents one sta | Note: Represents one standard deviation from the mean. |     |      |     |       |  |  |  |  |

### Table 8.9. Voltage Reference Electrical Characteristics

$V_{DD}$  = 3.0 V; -40 to +85 °C unless otherwise specified.

| Parameter           | Conditions                           | Min | Тур | Max             | Units |

|---------------------|--------------------------------------|-----|-----|-----------------|-------|

| Input Voltage Range |                                      | 0   | —   | V <sub>DD</sub> | V     |

| Input Current       | Sample Rate = 500 ksps; VREF = 2.5 V |     | 12  |                 | μA    |

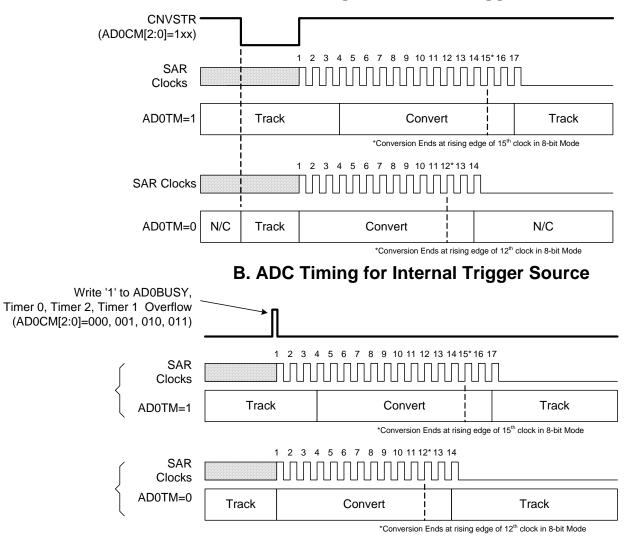

#### 9.3.2. Tracking Modes

The AD0TM bit in register ADC0CN enables "delayed conversions", and will delay the actual conversion start by three SAR clock cycles, during which time the ADC will continue to track the input. If AD0TM is left at logic 0, a conversion will begin immediately, without the extra tracking time. For internal start-of-conversion sources, the ADC will track anytime it is not performing a conversion. When the CNVSTR signal is used to initiate conversions, ADC0 will track either when AD0TM is logic 1, or when AD0TM is logic 0 and CNVSTR is held low. See Figure 9.2 for track and convert timing details. Delayed conversion mode is useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "9.3.3. Settling Time Requirements" on page 43.

A. ADC Timing for External Trigger Source

Figure 9.2. 10-Bit ADC Track and Conversion Example Timing

# SFR Definition 9.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|

| Name  | ADC0H[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xBE

| Bit | Name       | Function                                                                                                     |

|-----|------------|--------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                              |

|     |            | For AD0LJST = 0: Bits 7–2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word. |

|     |            | For AD0LJST = 1: Bits 7–0 are the most-significant bits of the 10-bit ADC0 Data Word.                        |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word.                          |

# SFR Definition 9.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|

| Name  | ADC0L[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xBD

| Bit | Name       | Function                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                                      |

|     |            | For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.                             |

|     |            | For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will read 000000b. |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0L will read back 0000000b.                   |

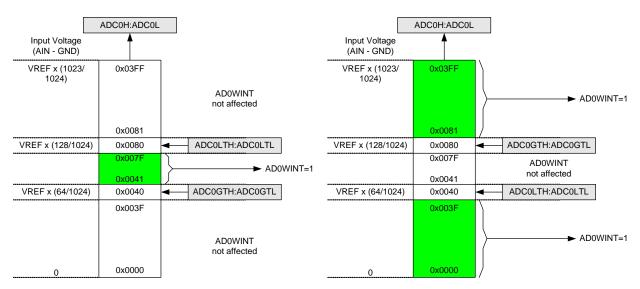

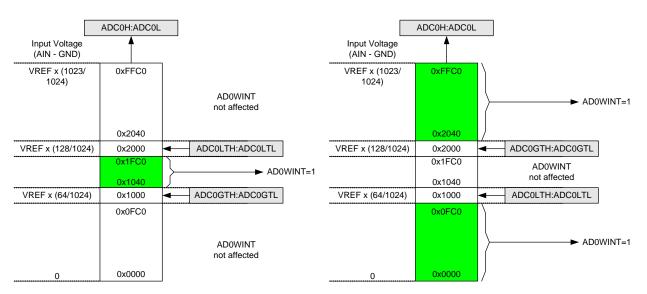

#### 9.4.1. Window Detector Example

Figure 9.4 shows two example window comparisons for right-justified data. with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 9.5 shows an example using left-justified data with the same comparison values.

Figure 9.4. ADC Window Compare Example: Right-Justified Data

Figure 9.5. ADC Window Compare Example: Left-Justified Data

## 19.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 19.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is disabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is enabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be enabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it has the potential to generate a system reset. The  $V_{DD}$  monitor is enabled and selected as a reset source by writing the PORSF flag in RSTSRC to 1.

See Figure 19.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 8.4 for complete electrical characteristics of the  $V_{DD}$  monitor.

### 19.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 8.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### **19.4. Missing Clock Detector Reset**

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the time specified in Section "8. Electrical Characteristics" on page 30, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

## 19.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 19.6. PCA Watchdog Timer Reset

The watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 170; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

# SFR Definition 19.1. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | MEMERR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF

| Bit   | Name       | Description                                                                                  | Write                                                                                                                                                                   | Read                                                                                                                                      |

|-------|------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                      | Don't care.                                                                                                                                                             | 0                                                                                                                                         |

| 6     | MEMERR     | EPROM Error Reset Flag.                                                                      | N/A                                                                                                                                                                     | Set to 1 if EPROM<br>read/write error caused<br>the last reset.                                                                           |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                           | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                   | Set to 1 if Comparator0 caused the last reset.                                                                                            |

| 4     | SWRSF      | Software Reset Force and Flag.                                                               | Writing a 1 forces a sys-<br>tem reset.                                                                                                                                 | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                              |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                   | N/A                                                                                                                                                                     | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                          |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                   | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                          | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                   |

| 1     | PORSF      | Power-On/V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor and configures it as a reset source.<br>Writing 1 to this bit while the $V_{DD}$ monitor is disabled may cause a system reset. | Set to 1 any time a power-<br>on or $V_{DD}$ monitor reset<br>occurs.<br>When set to 1, all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                           | N/A                                                                                                                                                                     | Set to 1 if RST pin caused the last reset.                                                                                                |

| Note: | Do not use | read-modify-write operations on this                                                         | s register                                                                                                                                                              | •                                                                                                                                         |

#### 20.1.2. EPROM Read Procedure

- 1. Reset the device using the  $\overline{RST}$  pin.

- 2. Wait at least 20 µs before sending the first C2 command.

- 3. Place the device in core reset: Write 0x04 to the DEVCTL register.

- 4. Write 0x00 to the EPCTL register.

- 5. Write the first EPROM address for reading to EPADDRH and EPADDRL.

- 6. Read a data byte from EPDAT. EPADDRH:L will increment by 1 after this read.

- 7. (Optional) Check the ERROR bit in register EPSTAT and abort the memory read operation if necessary.

- 8. If reading is not finished, return to Step 6 to read the next address in sequence, or return to Step 5 to select a new address.

- 9. Remove read mode (1st step): Write 0x40 to the EPCTL register.

- 10.Remove read mode (2nd step): Write 0x00 to the EPCTL register.

- 11. Reset the device: Write 0x02 and then 0x00 to the DEVCTL register.

### 20.2. Security Options

The C8051T600/1/2/3/4/5/6 devices provide security options to prevent unauthorized viewing of proprietary program code and constants. A security byte in EPROM address space can be used to lock the program memory from being read or written across the C2 interface. When read, the RDLOCK and WRLOCK bits in register EPSTAT will indicate the lock status of the location currently addressed by EPADDR. Table 20.1 shows the security byte decoding. See Section "15. Memory Organization" on page 74 for the security byte location and EPROM memory map.

Important Note: Once the security byte has been written, there are no means of unlocking the device. Locking memory from write access should be performed only after all other code has been successfully programmed to memory.

| Bits | Description                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------|

| 7–4  | Write Lock: Clearing any of these bits to logic 0 prevents all code memory from being written across the C2 interface.    |

| 3–0  | <b>Read Lock:</b> Clearing any of these bits to logic 0 prevents all code memory from being read across the C2 interface. |

Table 20.1. Security Byte Decoding

## 21.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051T600/1/2/3/4/5/6 devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 21.1.

On C8051T600/1/2/3/4/5/6 devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

#### SFR Definition 21.1. OSCICL: Internal H-F Oscillator Calibration

| Bit   | 7 | 6      | 5           | 4      | 3      | 2      | 1      | 0      |  |

|-------|---|--------|-------------|--------|--------|--------|--------|--------|--|

| Name  |   |        | OSCICL[6:0] |        |        |        |        |        |  |

| Туре  | R |        | R/W         |        |        |        |        |        |  |

| Reset | 0 | Varies | Varies      | Varies | Varies | Varies | Varies | Varies |  |

SFR Address = 0xB3

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                 |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused      | Unused. Read = 0; Write = Don't Care                                                                                                                                                                                                                                                                     |

| 6:0 | OSCICL[6:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                    |

|     |             | These bits determine the internal oscillator period. When set to 0000000b, the H-F oscillator operates at its fastest setting. When set to 1111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

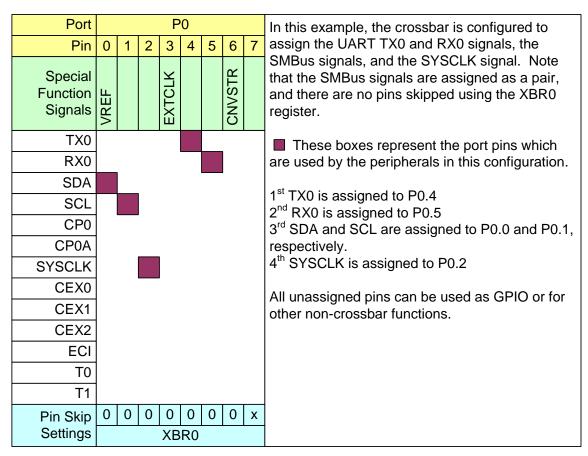

Figure 22.4. Priority Crossbar Decoder Example 1 - No Skipped Pins

#### 22.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (POMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (P0MDOUT).

- 3. Select any pins to be skipped by the I/O crossbar using the XBR0 register.

- 4. Assign Port pins to desired peripherals.

- 5. Enable the crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the crossbar (accomplished by setting the associated bits in XBR0). Port input mode is set in the POMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 22.5 for the POMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode register (P0MD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the P0MDOUT settings. When the WEAKPUD bit in XBR2 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 to avoid unnecessary power dissipation.

Registers XBR1 and XBR2 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR2 to 1 enables the crossbar. Until the crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table. An alternative is to use the Configuration Wizard utility available on the Silicon Laboratories web site to determine the Port I/O pin-assignments based on the XBRn Register settings.

The crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the crossbar is disabled.

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

#### Table 23.1. SMBus Clock Source Selection

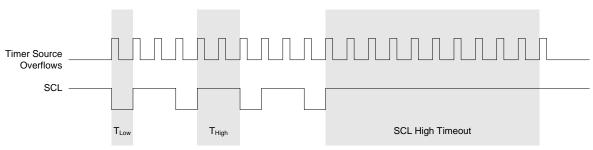

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 23.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "25. Timers" on page 145.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 23.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 23.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 23.2.

$$BitRate = \frac{f_{ClockSourceOverflow}}{3}$$

### Equation 23.2. Typical SMBus Bit Rate

Figure 23.4 shows the typical SCL generation described by Equation 23.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by Equation 23.1.

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable

## 24.2. Operational Modes

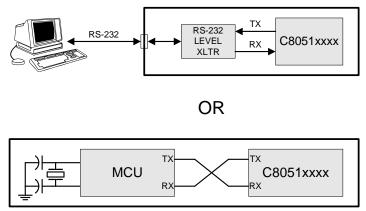

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 24.3.

Figure 24.3. UART Interconnect Diagram

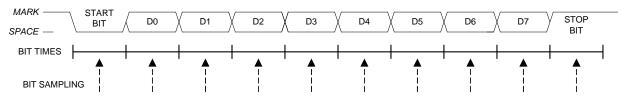

#### 24.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 24.4. 8-Bit UART Timing Diagram

# SFR Definition 25.2. TCON: Timer Control

| Bit                                 | 7    | 6                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                       | 4               | 3     | 2   | 1   | 0        |  |

|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----|-----|----------|--|

| Name                                | TF1  | TR1                                                                                                                                                                                                                                                                     | TF0                                                                                                                                                                                                                                     | TR0             | IE1   | IT1 | IE0 | IT0      |  |

| Туре                                | R/W  | R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |                 |       |     |     |          |  |

| Rese                                | t 0  | 0                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                       | 0               | 0     | 0   | 0   | 0        |  |

| SFR Address = 0x88; Bit-Addressable |      |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                 |       |     | I   | <u> </u> |  |

| Bit                                 | Name | Function                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                         |                 |       |     |     |          |  |

| 7                                   | TF1  | Timer 1 Ov                                                                                                                                                                                                                                                              | Timer 1 Overflow Flag.                                                                                                                                                                                                                  |                 |       |     |     |          |  |

|                                     |      |                                                                                                                                                                                                                                                                         | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                           |                 |       |     |     |          |  |

| 6                                   | TR1  | Timer 1 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |                 |       |     |     |          |  |

|                                     |      | Timer 1 is e                                                                                                                                                                                                                                                            | nabled by se                                                                                                                                                                                                                            | etting this bit | to 1. |     |     |          |  |

| 5                                   | TF0  | Timer 0 Ov                                                                                                                                                                                                                                                              | erflow Flag                                                                                                                                                                                                                             |                 |       |     |     |          |  |

|                                     |      |                                                                                                                                                                                                                                                                         | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                           |                 |       |     |     |          |  |

| 4                                   | TR0  | Timer 0 Ru                                                                                                                                                                                                                                                              | n Control.                                                                                                                                                                                                                              |                 |       |     |     |          |  |

|                                     |      | Timer 0 is e                                                                                                                                                                                                                                                            | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                            |                 |       |     |     |          |  |

| 3                                   | IE1  | External Int                                                                                                                                                                                                                                                            | terrupt 1.                                                                                                                                                                                                                              |                 |       |     |     |          |  |

|                                     |      | can be clear                                                                                                                                                                                                                                                            | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode. |                 |       |     |     |          |  |

| 2                                   | IT1  | Interrupt 1                                                                                                                                                                                                                                                             | Type Select                                                                                                                                                                                                                             | t.              |       |     |     |          |  |

|                                     |      | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive.<br>/INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see<br>SFR Definition 17.5).<br>0: /INT1 is level triggered.<br>1: /INT1 is edge triggered. |                                                                                                                                                                                                                                         |                 |       |     |     |          |  |

| 1                                   | IE0  | External Int                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                       |                 |       |     |     |          |  |

|                                     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                                 |                                                                                                                                                                                                                                         |                 |       |     |     |          |  |

| 0                                   | IT0  | Interrupt 0                                                                                                                                                                                                                                                             | ••                                                                                                                                                                                                                                      |                 |       |     |     |          |  |

|                                     |      | This bit selects whether the configured INT0 interrupt will be edge or level sensitive.<br>INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 17.5).<br>0: INT0 is level triggered.<br>1: INT0 is edge triggered.            |                                                                                                                                                                                                                                         |                 |       |     |     |          |  |

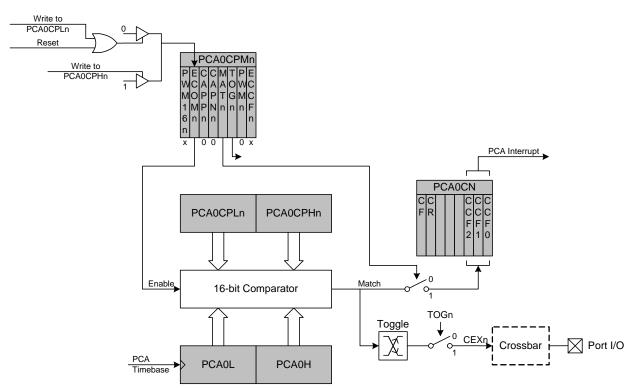

#### 26.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit Capture/Compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note about Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 26.6. PCA High-Speed Output Mode Diagram

The 8-bit offset held in PCA0CPH2 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.4, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL2) + (256 - PCA0L)$

## Equation 26.4. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH2 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF2 flag (PCA0CN.2) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- 1. Disable the WDT by writing a 0 to the WDTE bit.

- 2. Select the desired PCA clock source (with the CPS2–CPS0 bits).

- 3. Load PCA0CPL2 with the desired WDT update offset value.

- 4. Configure the PCA Idle Mode (set CIDL if the WDT should be suspended while the CPU is in Idle Mode).

- 5. Enable the WDT by setting the WDTE bit to 1.

- 6. Reset the WDT timer by writing to PCA0CPH2.

The PCA clock source and Idle Mode select cannot be changed while the WDT is enabled. The Watchdog Timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL2 defaults to 0x00. Using Equation 26.4, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.