Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                     |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                    |

| Program Memory Type        | OTP                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 11-QFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t605-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 25.1. CKCON: Clock Control                              |

|------------------------------------------------------------------------|

| SFR Definition 25.2. TCON: Timer Control                               |

| SFR Definition 25.3. TMOD: Timer Mode 152                              |

| SFR Definition 25.4. TL0: Timer 0 Low Byte 153                         |

| SFR Definition 25.5. TL1: Timer 1 Low Byte 153                         |

| SFR Definition 25.6. TH0: Timer 0 High Byte 154                        |

| SFR Definition 25.7. TH1: Timer 1 High Byte 154                        |

| SFR Definition 25.8. TMR2CN: Timer 2 Control 157                       |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte 158     |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte 158   |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte 158                      |

| SFR Definition 25.12. TMR2H Timer 2 High Byte 159                      |

| SFR Definition 26.1. PCA0CN: PCA Control                               |

| SFR Definition 26.2. PCA0MD: PCA Mode                                  |

| SFR Definition 26.3. PCA0CPMn: PCA Capture/Compare Mode                |

| SFR Definition 26.4. PCA0L: PCA Counter/Timer Low Byte                 |

| SFR Definition 26.5. PCA0H: PCA Counter/Timer High Byte                |

| SFR Definition 26.6. PCA0CPLn: PCA Capture Module Low Byte             |

| SFR Definition 26.7. PCA0CPHn: PCA Capture Module High Byte            |

| C2 Register Definition 27.1. C2ADD: C2 Address                         |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID                    |

| C2 Register Definition 27.3. REVID: C2 Revision ID                     |

| C2 Register Definition 27.4. DEVCTL: C2 Device Control                 |

| C2 Register Definition 27.5. EPCTL: EPROM Programming Control Register |

| C2 Register Definition 27.6. EPDAT: C2 EPROM Data                      |

| C2 Register Definition 27.7. EPSTAT: C2 EPROM Status                   |

| C2 Register Definition 27.8. EPADDRH: C2 EPROM Address High Byte       |

| C2 Register Definition 27.9. EPADDRL: C2 EPROM Address Low Byte        |

| C2 Register Definition 27.10. CRC0: CRC Byte 0                         |

| C2 Register Definition 27.11. CRC1: CRC Byte 1                         |

| C2 Register Definition 27.12. CRC2: CRC Byte 2                         |

| 02 Register Deminitor 21. 13. URUS. URU Dyle S                         |

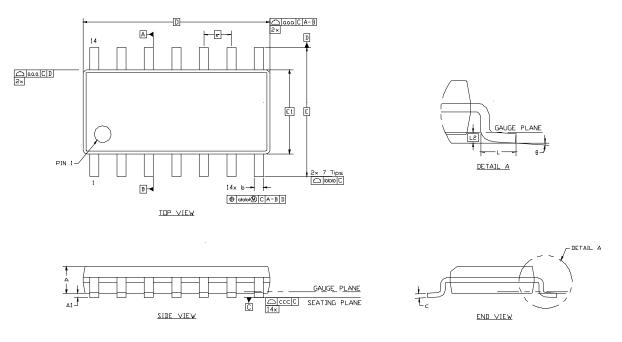

## 5. SOIC-14 Package Specifications

| Dimension | Min      | Nom      | Max  | Dimension | Min      | Nom  | Max  |

|-----------|----------|----------|------|-----------|----------|------|------|

| А         | _        | —        | 1.75 | L         | 0.40     | —    | 1.27 |

| A1        | 0.10     |          | 0.25 | L2        | 0.25 BSC |      |      |

| b         | 0.33     | —        | 0.51 | θ         | 0°       |      | 8°   |

| С         | 0.17     |          | 0.25 | aaa       |          | 0.10 |      |

| D         |          | 8.65 BSC |      | bbb       |          | 0.20 |      |

| E         |          | 6.00 BSC |      | CCC       |          | 0.10 |      |

| E1        | 3.90 BSC |          |      | ddd       |          | 0.25 |      |

| е         |          | 1.27 BSC |      |           |          |      |      |

### Table 5.1. SOIC-14 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS012, variation AB.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

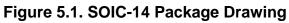

## 6. MSOP-10 Package Specifications

Figure 6.1. MSOP-10 Package Drawing

| Dimension | Min  | Nom      | Max  | Dimension | Min  | Nom      | Max  |

|-----------|------|----------|------|-----------|------|----------|------|

| A         | _    | —        | 1.10 | е         |      | 0.50 BSC |      |

| A1        | 0.00 | —        | 0.15 | L         | 0.40 | 0.60     | 0.80 |

| A2        | 0.75 | 0.85     | 0.95 | L2        |      | 0.25 BSC |      |

| b         | 0.17 | —        | 0.33 | θ         | 0°   |          | 8°   |

| С         | 0.08 |          | 0.23 | aaa       | _    | —        | 0.20 |

| D         |      | 3.00 BSC |      | bbb       |      | —        | 0.25 |

| E         |      | 4.90 BSC |      | CCC       |      | —        | 0.10 |

| E1        |      | 3.00 BSC |      | ddd       | _    | —        | 0.08 |

## Table 6.1. MSOP-10 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm).

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-187, Variation "BA".

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

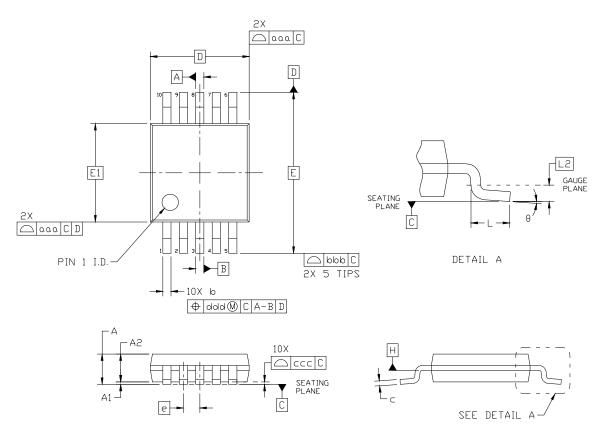

## 7. QFN-10 Package Specifications

## Figure 7.1. QFN-10 Package Drawing

| Dimension | Min  | Nom       | Max  | Dimension | Min  | Nom  | Max  |

|-----------|------|-----------|------|-----------|------|------|------|

| A         | 0.70 | 0.75      | 0.80 | L         | 0.55 | 0.60 | 0.65 |

| A1        | 0.00 |           | 0.05 | L1        |      | —    | 0.15 |

| b         | 0.18 | 0.25      | 0.30 | aaa       |      | —    | 0.10 |

| D         |      | 2.00 BSC. |      | bbb       | _    | —    | 0.10 |

| е         |      | 0.50 BSC. |      | CCC       | _    | —    | 0.05 |

| E         |      | 2.00 BSC. |      | ddd       |      | —    | 0.08 |

### Table 7.1. QFN-10 Package Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC outline MO-220, variation WCCD-5 except for feature L which is toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

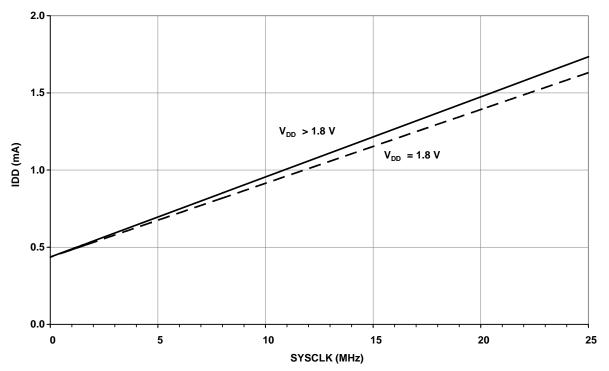

Figure 8.3. C8051T600/1/2/3/4/5 Idle Mode Supply Current vs. Frequency (MPCE = 1)

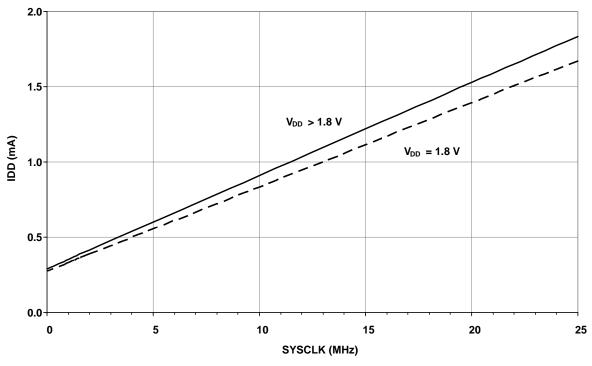

Figure 8.4. C8051T606 Idle Mode Digital Current vs. Frequency (MPCE = 1)

## SFR Definition 9.4. ADC0CN: ADC0 Control

| Bit   | 7     | 6     | 5      | 4       | 3       | 2          | 1   | 0 |

|-------|-------|-------|--------|---------|---------|------------|-----|---|

| Name  | AD0EN | AD0TM | AD0INT | AD0BUSY | AD0WINT | AD0CM[2:0] |     |   |

| Туре  | R/W   | R/W   | R/W    | R/W     | R/W     |            | R/W |   |

| Reset | 0     | 0     | 0      | 0       | 0       | 0          | 0   | 0 |

#### SFR Address = 0xE8; Bit-Addressable

| Bit | Name       | Func                                                                                                                                                                                 | tion                                     |  |  |  |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|--|--|

| 7   | AD0EN      | ADC0 Enable Bit.                                                                                                                                                                     |                                          |  |  |  |  |  |  |  |

|     |            | : ADC0 Disabled. ADC0 is in low-power shutdown.                                                                                                                                      |                                          |  |  |  |  |  |  |  |

|     |            | 1: ADC0 Enabled. ADC0 is active and read                                                                                                                                             | y for data conversions.                  |  |  |  |  |  |  |  |

| 6   | AD0TM      | ADC0 Track Mode Bit.                                                                                                                                                                 |                                          |  |  |  |  |  |  |  |

|     |            | <ul> <li>0: Normal Track Mode: When ADC0 is enal version is in progress. Conversion begins ir as defined by AD0CM[2:0].</li> <li>1: Delayed Track Mode: When ADC0 is enal</li> </ul> | nmediately on start-of-conversion event, |  |  |  |  |  |  |  |

|     |            | is not in progress. A start-of-conversion sign<br>tracking, and then begins the conversion.                                                                                          |                                          |  |  |  |  |  |  |  |

| 5   | AD0INT     | ADC0 Conversion Complete Interrupt Flag                                                                                                                                              | ag.                                      |  |  |  |  |  |  |  |

|     |            | 0: ADC0 has not completed a data convers                                                                                                                                             |                                          |  |  |  |  |  |  |  |

|     |            | 1: ADC0 has completed a data conversion.                                                                                                                                             |                                          |  |  |  |  |  |  |  |

| 4   | AD0BUSY    | ADC0 Busy Bit. Read:                                                                                                                                                                 | Write:                                   |  |  |  |  |  |  |  |

|     |            | 0: ADC0 conversion is<br>progress.<br>1: ADC0 conversion is<br>ress.                                                                                                                 | 1: Initiates ADC0 Conversion if          |  |  |  |  |  |  |  |

| 3   | AD0WINT    | ADC0 Window Compare Interrupt Flag.                                                                                                                                                  |                                          |  |  |  |  |  |  |  |

|     |            | 0: ADC0 Window Comparison Data match<br>cleared.<br>1: ADC0 Window Comparison Data match                                                                                             | -                                        |  |  |  |  |  |  |  |

| 2:0 | AD0CM[2:0] | ADC0 Start of Conversion Mode Select.                                                                                                                                                |                                          |  |  |  |  |  |  |  |

|     |            | 000: ADC0 start-of-conversion source is wr                                                                                                                                           |                                          |  |  |  |  |  |  |  |

|     |            | 001: ADC0 start-of-conversion source is ov                                                                                                                                           |                                          |  |  |  |  |  |  |  |

|     |            | 010: ADC0 start-of-conversion source is ov<br>011: ADC0 start-of-conversion source is ov                                                                                             |                                          |  |  |  |  |  |  |  |

|     |            | 100: ADC0 start-of-conversion source is ov                                                                                                                                           |                                          |  |  |  |  |  |  |  |

|     |            | 101: ADC0 start-of-conversion source is ov                                                                                                                                           | 5 S                                      |  |  |  |  |  |  |  |

|     |            | 11x: Reserved.                                                                                                                                                                       |                                          |  |  |  |  |  |  |  |

## 10. Temperature Sensor (C8051T600/2/4 only)

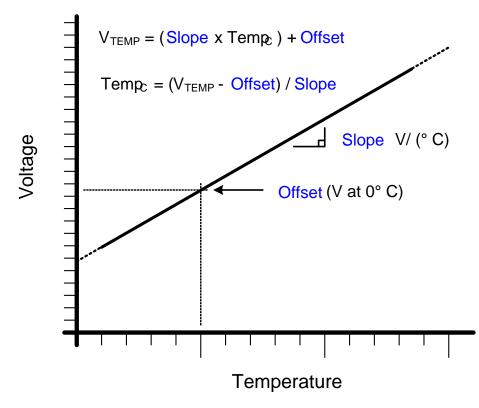

An on-chip temperature sensor is included on the C8051T600/2/4, which can be directly accessed via the ADC multiplexer. To use the ADC to measure the temperature sensor, the ADC mux channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 10.1. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the ADC multiplexer is set correctly. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 11.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 8.8 for the slope and offset parameters of the temperature sensor.

#### 10.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 8.8 on page 35 for specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. A single-point offset measurement of the temperature sensor is performed on each device during production test. The registers TOFFH and TOFFL, shown in SFR Definition 10.1 and SFR Definition 10.2 represent the output of the ADC when reading the temperature sensor at 0 °C, and using the internal regulator as a voltage reference.

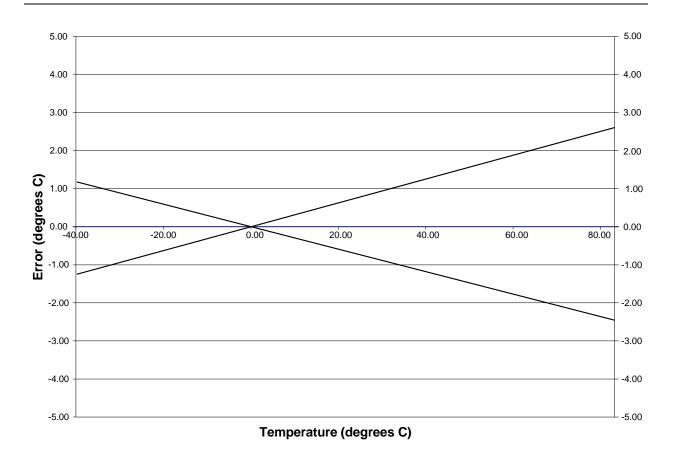

Figure 10.2 shows the typical temperature sensor error assuming a 1-point calibration at 0 °C. Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.

Figure 10.2. Temperature Sensor Error with 1-Point Calibration at 0 °C

## SFR Definition 12.1. REG0CN: Voltage Regulator Control

| Bit   | 7           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                    | 4                                                                                                                         | 3                                                                     | 2                                            | 1                                                       | 0                                |  |  |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|----------------------------------|--|--|

| Nam   | e STOPC     | F BYPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                      |                                                                                                                           |                                                                       |                                              |                                                         | MPCE                             |  |  |

| Туре  | e R/W       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                                                                                                  | R/W                                                                                                                       | R/W                                                                   | R/W                                          | R/W                                                     | R/W                              |  |  |

| Rese  | et O        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                    | 0                                                                                                                         | 0                                                                     | 0                                            | 0                                                       | 0                                |  |  |

| SFR A | Address = 0 | xC7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      |                                                                                                                           |                                                                       |                                              |                                                         |                                  |  |  |

| Bit   | Name        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Function                                                                                                                                                                                                                                                             |                                                                                                                           |                                                                       |                                              |                                                         |                                  |  |  |

| 7     | STOPCF      | Stop Mode Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | onfiguratio                                                                                                                                                                                                                                                          | n.                                                                                                                        |                                                                       |                                              |                                                         |                                  |  |  |

|       |             | 0: Regulator is device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset |                                                                                                                           |                                                                       |                                              |                                                         |                                  |  |  |

| 6     | BYPASS      | Bypass Interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nal Regulat                                                                                                                                                                                                                                                          | or.                                                                                                                       |                                                                       |                                              |                                                         |                                  |  |  |

|       |             | This bit places<br>core to run dir<br>0: Normal Moo<br>1: Bypass Moo<br>the V <sub>DD</sub> supply<br><b>IMPORTANT:</b><br>voltage only.<br>voltage is gre<br>may cause po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ectly from the<br>de—Regular<br>de—Regular<br>y voltage.<br>Bypass mo<br>Never plac<br>eater than the<br>ermanent d                                                                                                                                                  | ne V <sub>DD</sub> suppl<br>tor is on.<br>tor is off, and<br>ode is for us<br>e the regula<br>he specifica<br>amage to th | y pin.<br>I the microco<br>e with an e<br>tor in bypas<br>tions given | ontroller core<br>xternal regu<br>ss mode wh | e operates d<br>Ilator as the<br>en the V <sub>DD</sub> | irectly from<br>supply<br>supply |  |  |

| 5:1   | Reserved    | Reserved. Mu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                      |                                                                                                                           |                                                                       |                                              |                                                         |                                  |  |  |

| 0     | MPCE        | <ul> <li>Memory Power Controller Enable.</li> <li>This bit can help the system save power at slower system clock frequencies (about 2.0 MHz or less) by automatically shutting down the EPROM memory between clocks when information is not being fetched from the EPROM memory.</li> <li>0: Normal Mode—Memory power controller disabled (EPROM memory is always on)</li> <li>1: Low Power Mode—Memory power controller enabled (EPROM memory turns on/o as needed).</li> <li>Note: If an external clock source is used with the Memory Power Controller enabled, and the clock frequency changes from slow (&lt;2.0 MHz) to fast (&gt; 2.0 MHz), the EPROM power will turn on, and up to 20 clocks may be "skipped" to ensure that the EPROM power is stable before reading memory.</li> </ul> |                                                                                                                                                                                                                                                                      |                                                                                                                           |                                                                       |                                              |                                                         |                                  |  |  |

### 20.3. Program Memory CRC

A CRC engine is included on-chip, which provides a means of verifying EPROM contents once the device has been programmed. The CRC engine is available for EPROM verification even if the device is fully read and write locked, allowing for verification of code contents at any time.

The CRC engine is operated through the C2 debug and programming interface, and performs 16-bit CRCs on individual 256-byte blocks of program memory, or a 32-bit CRC the entire memory space. To prevent hacking and extrapolation of security-locked source code, the CRC engine will only allow CRCs to be performed on contiguous 256-byte blocks beginning on 256-byte boundaries (lowest 8-bits of address are 0x00). For example, the CRC engine can perform a CRC for locations 0x0400 through 0x04FF, but it cannot perform a CRC for locations 0x0401 through 0x0500, or on block sizes smaller or larger than 256 bytes.

#### 20.3.1. Performing 32-bit CRCs on Full EPROM Content

A 32-bit CRC on the entire EPROM space is initiated by writing to the CRC1 byte over the C2 interface. The CRC calculation begins at address 0x0000 and ends at the end of user EPROM space. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 32-bit results will be available in the CRC3-0 registers. CRC3 is the MSB, and CRC0 is the LSB. The polynomial used for the 32-bit CRC calculation is 0x04C11DB7.

**Note**: If a 16-bit CRC has been performed since the last device reset, a device reset should be initiated before performing a 32-bit CRC operation.

#### 20.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks

A 16-bit CRC of individual 256-byte blocks of EPROM can be initiated by writing to the CRC0 byte over the C2 interface. The value written to CRC0 is the high byte of the beginning address for the CRC. For example, if CRC0 is written to 0x02, the CRC will be performed on the 256 bytes beginning at address 0x0200, and ending at address 0x2FF. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 16-bit results will be available in the CRC1-0 registers. CRC1 is the MSB, and CRC0 is the LSB. The polynomial for the 16-bit CRC calculation is 0x1021

#### 22.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (XBR0 = 1) and pins in use by the crossbar (XBR0 = 0). External digital event capture functions cannot be used on pins configured for analog I/O. Table 22.3 shows all available external digital event capture functions.

#### Table 22.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function     | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment |

|----------------------|----------------------------------|-------------------------------|

| External Interrupt 0 | P0.0-P0.7                        | IT01CF                        |

| External Interrupt 1 | P0.0–P0.7                        | IT01CF                        |

## SFR Definition 23.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                               | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                              | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                        | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                         | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                          | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                             | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                      | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                        | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | SMBus Interrupt Flag.<br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

#### 23.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 23.3. SMB0DAT: SMBus Data

| Bit   | 7              | 6                                                         | 5                                                                                   | 4                                                                                                 | 3                                                                | 2                                                             | 1                                                               | 0                                                            |  |  |  |  |

|-------|----------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Nam   | e              | SMB0DAT[7:0]                                              |                                                                                     |                                                                                                   |                                                                  |                                                               |                                                                 |                                                              |  |  |  |  |

| Туре  | •              | R/W                                                       |                                                                                     |                                                                                                   |                                                                  |                                                               |                                                                 |                                                              |  |  |  |  |

| Rese  | et 0           | 0 0 0 0 0 0 0 0                                           |                                                                                     |                                                                                                   |                                                                  |                                                               |                                                                 |                                                              |  |  |  |  |

| SFR A | Address = 0xC2 |                                                           |                                                                                     |                                                                                                   |                                                                  |                                                               |                                                                 |                                                              |  |  |  |  |

| Bit   | Name           |                                                           |                                                                                     |                                                                                                   | Function                                                         |                                                               |                                                                 |                                                              |  |  |  |  |

| 7:0   | SMB0DAT[7:0]   | The SMB<br>serial inte<br>The CPU<br>(SMB0CN<br>as the SI | 0DAT register<br>offace or a by<br>can read fro<br>J.0) is set to<br>flag is set. V | er contains a<br>/te that has j<br>om or write to<br>logic 1. The<br>Vhen the SI f<br>and the CPL | ust been rec<br>this register<br>serial data in<br>lag is not se | eived on the<br>whenever the<br>the register<br>t, the system | SMBus seri<br>ne SI serial in<br>r remains sta<br>n may be in t | al interface.<br>hterrupt flag<br>able as long<br>he process |  |  |  |  |

### SFR Definition 24.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit      | 7               | 6                                                                                                                                                                                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| Nam      | lame SBUF0[7:0] |                                                                                                                                                                                   |   |   |   |   |   |   |  |  |

| Type R/W |                 |                                                                                                                                                                                   |   |   |   |   |   |   |  |  |

| Rese     | et 0            | 0                                                                                                                                                                                 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A    | Address = 0x9   | 9                                                                                                                                                                                 |   |   |   |   |   |   |  |  |

| Bit      | Name            | Name Function                                                                                                                                                                     |   |   |   |   |   |   |  |  |

| 7:0      | SBUF0[7:0]      | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                            |   |   |   |   |   |   |  |  |

|          |                 | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for |   |   |   |   |   |   |  |  |

SBUF0 returns the contents of the receive latch.

serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of

## SFR Definition 25.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6                           | 5                                                        | 4 | 3        | 2 | 1 | 0 |  |  |  |  |  |

|-------|--------------|-----------------------------|----------------------------------------------------------|---|----------|---|---|---|--|--|--|--|--|

| Name  | e            | TH0[7:0]<br>R/W             |                                                          |   |          |   |   |   |  |  |  |  |  |

| Туре  | •            |                             |                                                          |   |          |   |   |   |  |  |  |  |  |

| Rese  | t 0          | 0                           | 0                                                        | 0 | 0        | 0 | 0 | 0 |  |  |  |  |  |

| SFR A | ddress = 0x8 | 3C                          |                                                          |   |          |   |   |   |  |  |  |  |  |

| Bit   | Name         |                             |                                                          |   | Function |   |   |   |  |  |  |  |  |

| 7:0   | TH0[7:0]     | TH0[7:0] Timer 0 High Byte. |                                                          |   |          |   |   |   |  |  |  |  |  |

|       |              | The TH0 rec                 | The TH0 register is the high byte of the 16-bit Timer 0. |   |          |   |   |   |  |  |  |  |  |

### SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit                | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------------------|----------|---|---|---|---|---|---|---|--|

| Name               | TH1[7:0] |   |   |   |   |   |   |   |  |

| Туре               | R/W      |   |   |   |   |   |   |   |  |

| Reset              | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x8D |          |   |   |   |   |   |   |   |  |

| Di4                | Nome     |   |   |   |   |   |   |   |  |

| Bit | Name     | Function                                                 |  |  |  |  |  |  |

|-----|----------|----------------------------------------------------------|--|--|--|--|--|--|

| 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |  |  |  |  |  |  |

|     |          | The TH1 register is the high byte of the 16-bit Timer 1. |  |  |  |  |  |  |

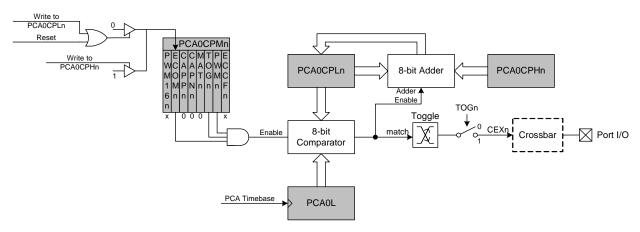

#### 26.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The Capture/Compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 26.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 26.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

Figure 26.7. PCA Frequency Output Mode

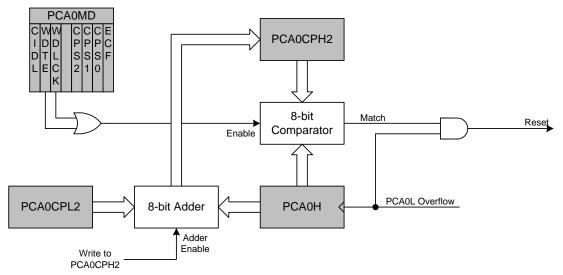

#### 26.4. Watchdog Timer Mode

A programmable Watchdog Timer (WDT) function is available through the PCA Module 2. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH2) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE bit set in the PCA0MD register, Module 2 operates as a Watchdog Timer (WDT). The Module 2 high byte is compared to the PCA counter high byte; the Module 2 low byte holds the offset to be used when WDT updates are performed. The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled. The WDT will generate a reset shortly after code begins execution. To avoid this reset, the WDT should be explicitly disabled (and optionally re-configured and re-enabled if it is used in the system).

#### 26.4.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2–CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 2 is forced into software timer mode.

- Writes to the Module 2 mode register (PCA0CPM2) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control bit (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH2 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH2. Upon a PCA0CPH2 write, PCA0H plus the offset held in PCA0CPL2 is loaded into PCA0CPH2 (See Figure 26.10).

Figure 26.10. PCA Module 2 with Watchdog Timer Enabled

## C2 Register Definition 27.2. DEVICEID: C2 Device ID

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|---|---|---|---|---|---|---|--|

| Name  | DEVICEID[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W           |   |   |   |   |   |   |   |  |

| Reset | 0             | 0 | 0 | 1 | 0 | 1 | 1 | 1 |  |

C2 Address: 0x00

| Bit | Name          | Function                                                                                               |

|-----|---------------|--------------------------------------------------------------------------------------------------------|

| 7:0 | DEVICEID[7:0] | Device ID.                                                                                             |

|     |               | This read-only register returns the 8-bit device ID:<br>0x10 = C8051T600/1/2/3/4/5<br>0x1B = C8051T606 |

### C2 Register Definition 27.3. REVID: C2 Revision ID

| Bit   | 7                | 6                                                                                      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |  |

|-------|------------------|----------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|--|--|

| Nam   | е                | REVID[7:0]                                                                             |        |        |        |        |        |        |  |  |  |  |  |

| Туре  | e                | R/W                                                                                    |        |        |        |        |        |        |  |  |  |  |  |

| Rese  | et Varies        | Varies                                                                                 | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |  |  |

| C2 Ac | C2 Address: 0x01 |                                                                                        |        |        |        |        |        |        |  |  |  |  |  |

| Bit   | Name             | Name Function                                                                          |        |        |        |        |        |        |  |  |  |  |  |

| 7:0   | REVID[7:0]       | Revision ID.                                                                           |        |        |        |        |        |        |  |  |  |  |  |

|       |                  | This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |        |        |        |        |        |        |  |  |  |  |  |

## **DOCUMENT CHANGE LIST**

## **Revision 0.5 to Revision 1.0**

- Updated electrical specification tables based on test, characterization, and qualification data.

- Updated with new formatting standards.

- Corrected minor typographical errors throughout document.

- Updated wording from "OTP EPROM" to "EPROM" throughout document.

- Added information on C2 EPSTAT Register.

- Updated EPROM programming sequence.

- Added Note about 100% Tin (Sn) lead finish to ordering information table.

Updated packaging information to include JEDEC-standard drawings for package and land diagram.

## **Revision 1.0 to Revision 1.1**

Added C8051T606 device information.

## **Revision 1.1 to Revision 1.2**

Updated Table 8.4 on page 34.

186

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories and "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

#### http://www.silabs.com