#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details |

|---------|

|---------|

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                              |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                          |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-VFBGA                                                              |

| Supplier Device Package    | 48-BGA (4x4)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg225f32-bga48 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1.11 Universal Synchronous/Asynchronous Receiver/Transmitter (US-ART)

The Universal Synchronous Asynchronous serial Receiver and Transmitter (USART) is a very flexible serial I/O module. It supports full duplex asynchronous UART communication as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with ISO7816 SmartCards, IrDA and I2S devices.

#### 2.1.12 Pre-Programmed UART Bootloader

The bootloader presented in application note AN0003 is pre-programmed in the device at factory. Autobaud and destructive write are supported. The autobaud feature, interface and commands are described further in the application note.

# 2.1.13 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

#### 2.1.14 Timer/Counter (TIMER)

The 16-bit general purpose Timer has 3 compare/capture channels for input capture and compare/Pulse-Width Modulation (PWM) output.

#### 2.1.15 Real Time Counter (RTC)

The Real Time Counter (RTC) contains a 24-bit counter and is clocked either by a 32.768 kHz crystal oscillator, or a 32.768 kHz RC oscillator. In addition to energy modes EM0 and EM1, the RTC is also available in EM2. This makes it ideal for keeping track of time since the RTC is enabled in EM2 where most of the device is powered down.

#### 2.1.16 Low Energy Timer (LETIMER)

The unique LETIMER<sup>TM</sup>, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. It is also connected to the Real Time Counter (RTC), and can be configured to start counting on compare matches from the RTC.

#### 2.1.17 Pulse Counter (PCNT)

The Pulse Counter (PCNT) can be used for counting pulses on a single input or to decode quadrature encoded inputs. It runs off either the internal LFACLK or the PCNTn\_S0IN pin as external clock source. The module may operate in energy mode EM0 - EM3.

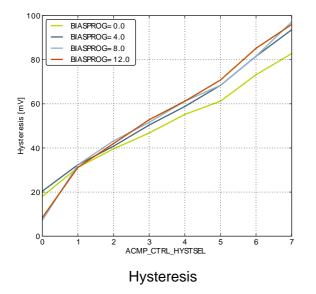

#### 2.1.18 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs can either be one of the selectable internal references or from external pins. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

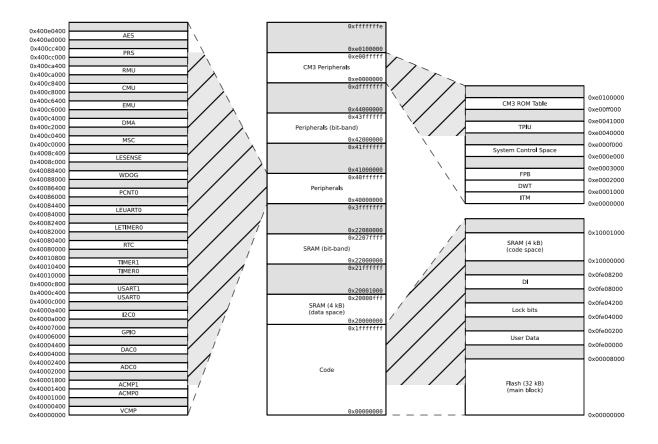

#### Figure 2.2. EFM32TG225 Memory Map with largest RAM and Flash sizes

# **3.4 Current Consumption**

#### Table 3.3. Current Consumption

| Symbol           | Parameter                                                     | Condition                                                                                                          | Min | Тур  | Max   | Unit       |

|------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                      |     | 157  |       | µA/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 150  | 170   | μΑ/<br>MHz |

|                  | EM0 current. No prescaling. Running                           | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 153  | 172   | μΑ/<br>MHz |

| I <sub>EM0</sub> | prime number cal-<br>culation code from<br>Flash. (Production | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 155  | 175   | µA/<br>MHz |

|                  | test condition = 14<br>MHz)                                   | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 157  | 178   | μΑ/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 162  | 183   | μΑ/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 200  | 240   | μΑ/<br>MHz |

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                      |     | 53   |       | μΑ/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 51   | 57    | μΑ/<br>MHz |

|                  | EM1 current (Pro-<br>duction test condi-<br>tion = 14 MHz)    | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 55   | 59    | µA/<br>MHz |

| I <sub>EM1</sub> |                                                               | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 56   | 61    | µA/<br>MHz |

|                  | ,                                                             | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 58   | 63    | µA/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 63   | 68    | µA/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO. all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 100  | 122   | µA/<br>MHz |

|                  | EM2 ourrest                                                   | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =25°C |     | 1.0  | 1.2   | μA         |

| I <sub>EM2</sub> | EM2 current                                                   | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C               |     | 2.4  | 5.0   | μΑ         |

| I=               | EM3 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.59 | 1.0   | μA         |

| I <sub>EM3</sub> | EWIS CUTIENT                                                  | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 2.0  | 4.5   | μA         |

| 1                | EM4 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.02 | 0.055 | μA         |

| I <sub>EM4</sub> |                                                               | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 0.25 | 0.70  | μA         |

# **3.5 Transition between Energy Modes**

The transition times are measured from the trigger to the first clock edge in the CPU.

Table 3.4. Energy Modes Transitions

| Symbol            | Parameter                       | Min | Тур | Max | Unit                          |

|-------------------|---------------------------------|-----|-----|-----|-------------------------------|

| t <sub>EM10</sub> | Transition time from EM1 to EM0 |     | 0   |     | HF-<br>CORE-<br>CLK<br>cycles |

| t <sub>EM20</sub> | Transition time from EM2 to EM0 |     | 2   |     | μs                            |

| t <sub>EM30</sub> | Transition time from EM3 to EM0 |     | 2   |     | μs                            |

| t <sub>EM40</sub> | Transition time from EM4 to EM0 |     | 163 |     | μs                            |

### **3.6 Power Management**

The EFM32TG requires the AVDD\_x, VDD\_DREG and IOVDD\_x pins to be connected together (with optional filter) at the PCB level. For practical schematic recommendations, please see the application note, "AN0002 EFM32 Hardware Design Considerations".

#### Table 3.5. Power Management

| Symbol                   | Parameter                                                                   | Condition                                                              | Min  | Тур  | Max  | Unit |

|--------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| V <sub>BODextthr</sub> - | BOD threshold on falling external supply voltage                            |                                                                        | 1.74 |      | 1.96 | V    |

| V <sub>BODextthr+</sub>  | BOD threshold on<br>rising external sup-<br>ply voltage                     |                                                                        |      | 1.85 | 1.98 | V    |

| V <sub>PORthr+</sub>     | Power-on Reset<br>(POR) threshold on<br>rising external sup-<br>ply voltage |                                                                        |      |      | 1.98 | V    |

| t <sub>RESET</sub>       | Delay from reset<br>is released until<br>program execution<br>starts        | Applies to Power-on Reset,<br>Brown-out Reset and pin reset.           |      | 163  |      | μs   |

| C <sub>DECOUPLE</sub>    | Voltage regulator decoupling capaci-<br>tor.                                | X5R capacitor recommended.<br>Apply between DECOUPLE pin<br>and GROUND |      | 1    |      | μF   |

## 3.9 Oscillators

#### 3.9.1 LFXO

#### Table 3.8. LFXO

| Symbol              | Parameter                                                      | Condition                                                                                                      | Min            | Тур    | Max | Unit |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--------|-----|------|

| f <sub>LFXO</sub>   | Supported nominal crystal frequency                            |                                                                                                                |                | 32.768 |     | kHz  |

| ESR <sub>LFXO</sub> | Supported crystal<br>equivalent series re-<br>sistance (ESR)   |                                                                                                                |                | 30     | 120 | kOhm |

| C <sub>LFXOL</sub>  | Supported crystal external load range                          |                                                                                                                | X <sup>1</sup> |        | 25  | pF   |

| I <sub>LFXO</sub>   | Current consump-<br>tion for core and<br>buffer after startup. | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>LFXOBOOST in CMU_CTRL is<br>1                                           |                | 190    |     | nA   |

| t <sub>LFXO</sub>   | Start- up time.                                                | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>40% - 60% duty cycle has<br>been reached, LFXOBOOST in<br>CMU_CTRL is 1 |                | 400    |     | ms   |

<sup>1</sup>See Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup in energyAware Designer in Simplicity Studio

For safe startup of a given crystal, the energyAware Designer in Simplicity Studio contains a tool to help users configure both load capacitance and software settings for using the LFXO. For details regarding the crystal configuration, the reader is referred to application note "AN0016 EFM32 Oscillator Design Consideration".

#### 3.9.2 HFXO

#### Table 3.9. HFXO

| Symbol                    | Parameter                                                                       | Condition                                                                            | Min | Тур | Max  | Unit |

|---------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>HFXO</sub>         | Supported nominal crystal Frequency                                             |                                                                                      | 4   |     | 32   | MHz  |

| 500                       | Supported crystal                                                               | Crystal frequency 32 MHz                                                             |     | 30  | 60   | Ohm  |

| ESR <sub>HFXO</sub>       | equivalent series re-<br>sistance (ESR)                                         | Crystal frequency 4 MHz                                                              |     | 400 | 1500 | Ohm  |

| <b>g</b> <sub>mHFXO</sub> | The transconduc-<br>tance of the HFXO<br>input transistor at<br>crystal startup | HFXOBOOST in CMU_CTRL<br>equals 0b11                                                 | 20  |     |      | mS   |

| C <sub>HFXOL</sub>        | Supported crystal external load range                                           |                                                                                      | 5   |     | 25   | pF   |

| I <sub>HFXO</sub>         | Current consump-<br>tion for HFXO after<br>startup                              | 4 MHz: ESR=400 Ohm,<br>C <sub>L</sub> =20 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11   |     | 85  |      | μA   |

|                           |                                                                                 | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals $0b11$ |     | 165 |      | μΑ   |

| t <sub>HFXO</sub>         | Startup time                                                                    | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11   |     | 400 |      | μs   |

#### 3.10.1 Typical performance

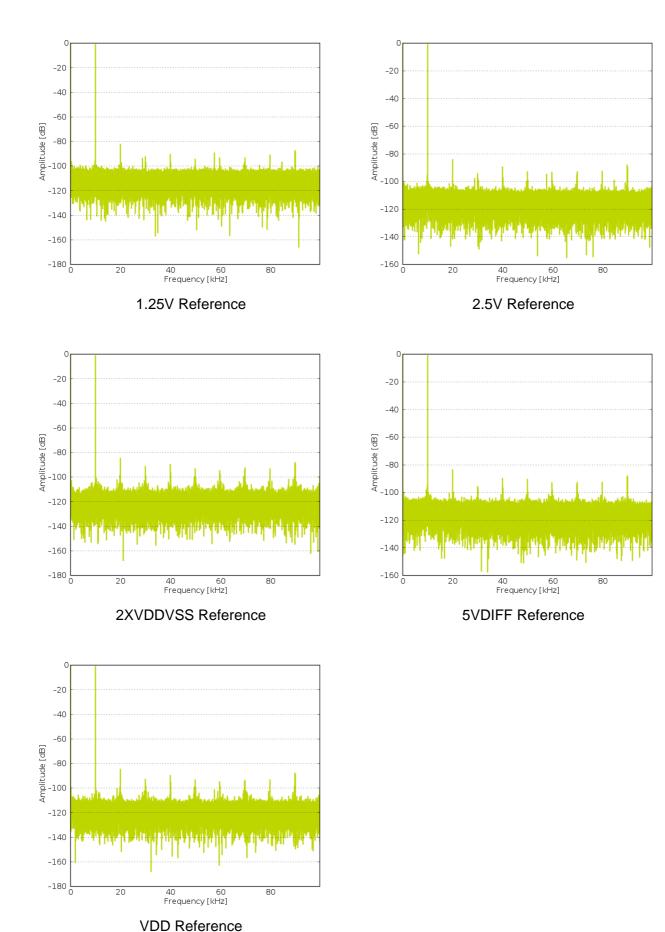

#### Figure 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

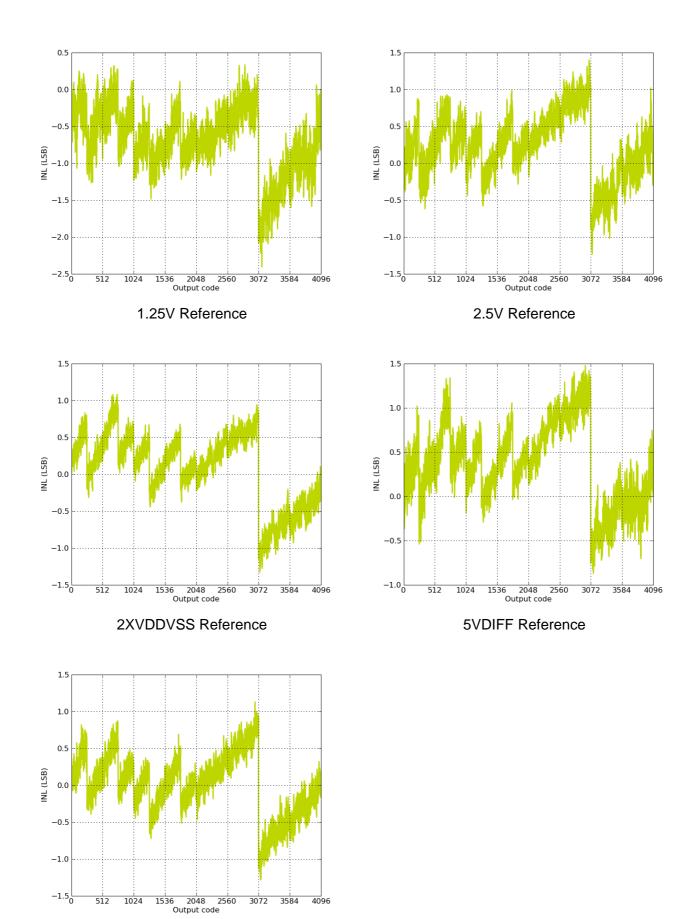

#### Figure 3.20. ADC Integral Linearity Error vs Code, Vdd = 3V, Temp = 25°C

**VDD** Reference

| Symbol                    | Parameter                     | Condition                                                                            | Min             | Тур   | Мах                  | Unit  |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|-------|----------------------|-------|

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 16.36 |                      | MHz   |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 0.81  |                      | MHz   |

|                           | Gain Bandwidth                | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.11  |                      | MHz   |

| GBW <sub>OPAMP</sub>      | Product                       | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 2.11  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 0.72  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.09  |                      | MHz   |

|                           |                               | BIASPROG=0xF,<br>HALFBIAS=0x0, C <sub>L</sub> =75 pF                                 |                 | 64    |                      | o     |

| PM <sub>OPAMP</sub>       | Phase Margin                  | BIASPROG=0x7,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | 0     |

|                           |                               | BIASPROG=0x0,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | o     |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100   |                      | Mohm  |

| 5                         | Load Resistance               | OPA0/OPA1                                                                            | 200             |       |                      | Ohm   |

| R <sub>LOAD</sub>         |                               | OPA2                                                                                 | 2000            |       |                      | Ohm   |

|                           | Load Current                  | OPA0/OPA1                                                                            |                 |       | 11                   | mA    |

| I <sub>LOAD_DC</sub>      |                               | OPA2                                                                                 |                 |       | 1.5                  | mA    |

| M                         |                               | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

| V <sub>INPUT</sub>        | Input Voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub> -1.2 | V     |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

| М                         | Input Offect Veltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     |                 | 6     |                      | mV    |

| V <sub>OFFSET</sub>       | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1     |                      | mV    |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |       | 0.02                 | mV/°C |

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 46.11 |                      | V/µs  |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 1.21  |                      | V/µs  |

| <b>CD</b>                 |                               | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.16  |                      | V/µs  |

| SR <sub>OPAMP</sub>       | Slew Rate                     | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 4.43  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 1.30  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.16  |                      | V/µs  |

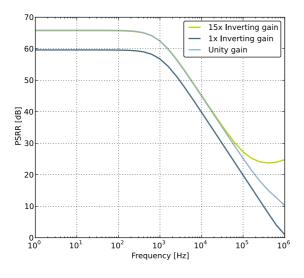

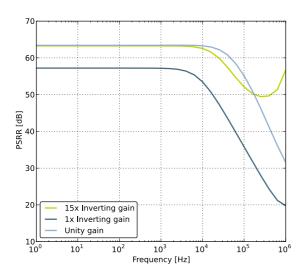

Figure 3.25. OPAMP Positive Power Supply Rejection Ratio

Figure 3.26. OPAMP Negative Power Supply Rejection Ratio

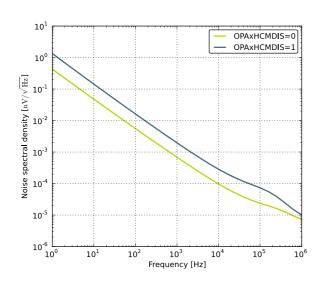

Figure 3.27. OPAMP Voltage Noise Spectral Density (Unity Gain) Vout=1V

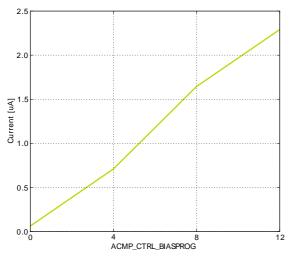

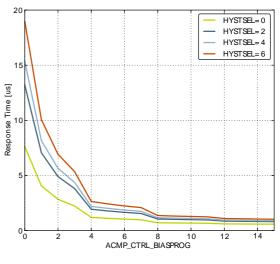

Figure 3.29. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

Current consumption, HYSTSEL = 4

Response time , V<sub>cm</sub> = 1.25V, CP+ to CP- = 100mV

#### Table 3.20. I2C Fast-mode (Fm)

| Symbol              | Parameter                                        | Min | Тур | Max                | Unit |

|---------------------|--------------------------------------------------|-----|-----|--------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   |     | 400 <sup>1</sup>   | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 1.3 |     |                    | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.6 |     |                    | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 100 |     |                    | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8   |     | 900 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.6 |     |                    | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.6 |     |                    | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.6 |     |                    | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 1.3 |     |                    | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32TG Reference Manual. <sup>2</sup>The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ). <sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((900\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

#### Table 3.21. I2C Fast-mode Plus (Fm+)

| Symbol              | Parameter                                        | Min  | Тур | Max               | Unit |

|---------------------|--------------------------------------------------|------|-----|-------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0    |     | 1000 <sup>1</sup> | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 0.5  |     |                   | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.26 |     |                   | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 50   |     |                   | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8    |     |                   | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.26 |     |                   | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.26 |     |                   | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.26 |     |                   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 0.5  |     |                   | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode Plus, see the I2C chapter in the EFM32TG Reference Manual.

# **3.16 Digital Peripherals**

#### Table 3.22. Digital Peripherals

| Symbol               | Parameter       | Condition                               | Min | Тур  | Max | Unit       |

|----------------------|-----------------|-----------------------------------------|-----|------|-----|------------|

| I <sub>USART</sub>   | USART current   | USART idle current, clock en-<br>abled  |     | 7.5  |     | μΑ/<br>MHz |

| I <sub>LEUART</sub>  | LEUART current  | LEUART idle current, clock en-<br>abled |     | 150  |     | nA         |

| I <sub>I2C</sub>     | I2C current     | I2C idle current, clock enabled         |     | 6.25 |     | μΑ/<br>MHz |

| I <sub>TIMER</sub>   | TIMER current   | TIMER_0 idle current, clock enabled     |     | 8.75 |     | μΑ/<br>MHz |

| I <sub>LETIMER</sub> | LETIMER current | LETIMER idle current, clock enabled     |     | 75   |     | nA         |

| I <sub>PCNT</sub>    | PCNT current    | PCNT idle current, clock en-<br>abled   |     | 60   |     | nA         |

#### ...the world's most energy friendly microcontrollers

| Symbol            | Parameter    | Condition                             | Min | Тур  | Max | Unit       |

|-------------------|--------------|---------------------------------------|-----|------|-----|------------|

| I <sub>RTC</sub>  | RTC current  | RTC idle current, clock enabled       |     | 40   |     | nA         |

| I <sub>AES</sub>  | AES current  | AES idle current, clock enabled       |     | 2.5  |     | μΑ/<br>MHz |

| I <sub>GPIO</sub> | GPIO current | GPIO idle current, clock en-<br>abled |     | 5.31 |     | µA/<br>MHz |

| I <sub>PRS</sub>  | PRS current  | PRS idle current                      |     | 2.81 |     | µA/<br>MHz |

| I <sub>DMA</sub>  | DMA current  | Clock enable                          |     | 8.12 |     | µA/<br>MHz |

|       | BGA48 Pin#<br>and Name | Pin Alternate Functionality / Description      |                                             |                                              |                                         |  |  |  |

|-------|------------------------|------------------------------------------------|---------------------------------------------|----------------------------------------------|-----------------------------------------|--|--|--|

| Pin # | Pin Name               | Analog                                         | Timers                                      | Communication                                | Other                                   |  |  |  |

| A3    | PE11                   |                                                | TIM1_CC1 #1                                 | US0_RX #0                                    | LES_ALTEX5 #0<br>BOOT_RX                |  |  |  |

| A4    | PF5                    |                                                |                                             |                                              | PRS_CH2 #1                              |  |  |  |

| A5    | PF3                    |                                                |                                             |                                              | PRS_CH0 #1                              |  |  |  |

| A6    | PC14                   | ACMP1_CH6<br>DAC0_OUT1ALT #2/<br>OPAMP_OUT1ALT | TIM1_CC1 #0<br>PCNT0_S1IN #0                | US0_CS #3                                    | LES_CH14 #0                             |  |  |  |

| A7    | PC15                   | ACMP1_CH7<br>DAC0_OUT1ALT #3/<br>OPAMP_OUT1ALT | TIM1_CC2 #0                                 | US0_CLK #3                                   | LES_CH15 #0<br>DBG_SWO #1               |  |  |  |

| B1    | PA1                    |                                                | TIM0_CC1 #0/1                               | I2C0_SCL #0                                  | CMU_CLK1 #0<br>PRS_CH1 #0               |  |  |  |

| B2    | PA0                    |                                                | TIM0_CC0 #0/1/4                             | LEU0_RX #4<br>I2C0_SDA #0                    | PRS_CH0 #0<br>GPIO_EM4WU0               |  |  |  |

| B3    | PE10                   |                                                | TIM1_CC0 #1                                 | US0_TX #0                                    | BOOT_TX                                 |  |  |  |

| B4    | PF4                    |                                                |                                             |                                              | PRS_CH1 #1                              |  |  |  |

| B5    | PF2                    |                                                | TIM0_CC2 #5                                 | LEU0_TX #4                                   | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4 |  |  |  |

| B6    | PC11                   | ACMP1_CH3                                      |                                             | US0_TX #2                                    | LES_CH11 #0                             |  |  |  |

| B7    | PC13                   | ACMP1_CH5<br>DAC0_OUT1ALT #1/<br>OPAMP_OUT1ALT | TIM1_CC0 #0<br>TIM1_CC2 #4<br>PCNT0_S0IN #0 |                                              | LES_CH13 #0                             |  |  |  |

| C1    | PC0                    | ACMP0_CH0<br>DAC0_OUT0ALT #0/<br>OPAMP_OUT0ALT | TIM0_CC1 #4<br>PCNT0_S0IN #2                | US0_TX #5<br>US1_TX #0<br>I2C0_SDA #4        | LES_CH0 #0<br>PRS_CH2 #0                |  |  |  |

| C2    | PA2                    |                                                | TIM0_CC2 #0/1                               |                                              | CMU_CLK0 #0                             |  |  |  |

| C3    | VSS                    | Ground.                                        |                                             |                                              |                                         |  |  |  |

| C4    | IOVDD_5                | Digital IO power supply 5.                     |                                             |                                              |                                         |  |  |  |

| C5    | PF1                    |                                                | TIM0_CC1 #5<br>LETIM0_OUT1 #2               | US1_CS #2<br>LEU0_RX #3<br>I2C0_SCL #5       | DBG_SWDIO #0/1<br>GPIO_EM4WU3           |  |  |  |

| C6    | PC9                    | ACMP1_CH1                                      |                                             | US0_CLK #2                                   | LES_CH9 #0<br>GPIO_EM4WU2               |  |  |  |

| C7    | PC10                   | ACMP1_CH2                                      |                                             | US0_RX #2                                    | LES_CH10 #0                             |  |  |  |

| D1    | PC1                    | ACMP0_CH1<br>DAC0_OUT0ALT #1/<br>OPAMP_OUT0ALT | TIM0_CC2 #4<br>PCNT0_S1IN #2                | US0_RX #5<br>US1_RX #0<br>I2C0_SCL #4        | LES_CH1 #0<br>PRS_CH3 #0                |  |  |  |

| D2    | PC3                    | ACMP0_CH3<br>DAC0_OUT0ALT #3/<br>OPAMP_OUT0ALT |                                             |                                              | LES_CH3 #0                              |  |  |  |

| D3    | IOVDD_0                | Digital IO power supply 0.                     |                                             |                                              |                                         |  |  |  |

| D5    | PF0                    |                                                | TIM0_CC0 #5<br>LETIM0_OUT0 #2               | US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5      | DBG_SWCLK #0/1                          |  |  |  |

| D6    | PC8                    | ACMP1_CH0                                      |                                             | US0_CS #2                                    | LES_CH8 #0                              |  |  |  |

| D7    | DECOUPLE               | Decouple output for on-chip vo                 | ltage regulator. An external capa           | citance of size C <sub>DECOUPLE</sub> is req | uired at this pin.                      |  |  |  |

| E1    | PC2                    | ACMP0_CH2<br>DAC0_OUT0ALT #2/<br>OPAMP_OUT0ALT |                                             |                                              | LES_CH2 #0                              |  |  |  |

| E2    | PC4                    | ACMP0_CH4<br>DAC0_P0 /                         | LETIM0_OUT0 #3                              |                                              | LES_CH4 #0                              |  |  |  |

#### Table 4.2. Alternate functionality overview

| Alternate                       | e LOCATION |      |      |      |   |   |                                                  |                                                                                                    |

|---------------------------------|------------|------|------|------|---|---|--------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Functionality                   | 0          | 1    | 2    | 3    | 4 | 5 | 6                                                | Description                                                                                        |

| ACMP0_CH0                       | PC0        |      |      |      |   |   |                                                  | Analog comparator ACMP0, channel 0.                                                                |

| ACMP0_CH1                       | PC1        |      |      |      |   |   |                                                  | Analog comparator ACMP0, channel 1.                                                                |

| ACMP0_CH2                       | PC2        |      |      |      |   |   |                                                  | Analog comparator ACMP0, channel 2.                                                                |

| ACMP0_CH3                       | PC3        |      |      |      |   |   |                                                  | Analog comparator ACMP0, channel 3.                                                                |

| ACMP0_CH4                       | PC4        |      |      |      |   |   |                                                  | Analog comparator ACMP0, channel 4.                                                                |

| ACMP0_O                         | PE13       |      | PD6  |      |   |   |                                                  | Analog comparator ACMP0, digital output.                                                           |

| ACMP1_CH0                       | PC8        |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 0.                                                                |

| ACMP1_CH1                       | PC9        |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 1.                                                                |

| ACMP1_CH2                       | PC10       |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 2.                                                                |

| ACMP1_CH3                       | PC11       |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 3.                                                                |

| ACMP1_CH5                       | PC13       |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 5.                                                                |

| ACMP1_CH6                       | PC14       |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 6.                                                                |

| ACMP1_CH7                       | PC15       |      |      |      |   |   |                                                  | Analog comparator ACMP1, channel 7.                                                                |

| ACMP1_O                         | PF2        |      | PD7  |      |   |   |                                                  | Analog comparator ACMP1, digital output.                                                           |

| ADC0_CH4                        | PD4        |      |      |      |   |   |                                                  | Analog to digital converter ADC0, input channel number 4.                                          |

| ADC0_CH5                        | PD5        |      |      |      |   |   |                                                  | Analog to digital converter ADC0, input channel number 5.                                          |

| ADC0_CH6                        | PD6        |      |      |      |   |   |                                                  | Analog to digital converter ADC0, input channel number 6.                                          |

| ADC0_CH7                        | PD7        |      |      |      |   |   |                                                  | Analog to digital converter ADC0, input channel number 7.                                          |

| BOOT_RX                         | PE11       |      |      |      |   |   |                                                  | Bootloader RX.                                                                                     |

| BOOT_TX                         | PE10       |      |      |      |   |   |                                                  | Bootloader TX.                                                                                     |

| CMU_CLK0                        | PA2        |      | PD7  |      |   |   |                                                  | Clock Management Unit, clock output number 0.                                                      |

| CMU_CLK1                        | PA1        |      | PE12 |      |   |   |                                                  | Clock Management Unit, clock output number 1.                                                      |

| DAC0_N1 /<br>OPAMP_N1           | PD7        |      |      |      |   |   |                                                  | Operational Amplifier 1 external negative input.                                                   |

| DAC0_OUT0 /<br>OPAMP_OUT0       | PB11       |      |      |      |   |   |                                                  | Digital to Analog Converter DAC0_OUT0 /<br>OPAMP output channel number 0.                          |

| DAC0_OUT0ALT /<br>OPAMP_OUT0ALT | PC0        | PC1  | PC2  | PC3  |   |   |                                                  | Digital to Analog Converter DAC0_OUT0ALT /<br>OPAMP alternative output for channel 0.              |

| DAC0_OUT1ALT /<br>OPAMP_OUT1ALT |            | PC13 | PC14 | PC15 |   |   |                                                  | Digital to Analog Converter DAC0_OUT1ALT / OPAMP alternative output for channel 1.                 |

| OPAMP_OUT2                      | PD5        |      |      |      |   |   |                                                  | Operational Amplifier 2 output.                                                                    |

| DAC0_P0 /<br>OPAMP_P0           | PC4        |      |      |      |   |   |                                                  | Operational Amplifier 0 external positive input.                                                   |

| DAC0_P1 /<br>OPAMP_P1           | PD6        |      |      |      |   |   |                                                  | Operational Amplifier 1 external positive input.                                                   |

| OPAMP_P2                        | PD4        |      |      |      |   |   |                                                  | Operational Amplifier 2 external positive input.                                                   |

|                                 |            |      |      |      |   |   |                                                  | Debug-interface Serial Wire clock input.                                                           |

| DBG_SWCLK                       | PF0        | PF0  |      |      |   |   |                                                  | Note that this function is enabled to pin out of reset, and has a built-in pull down.              |

|                                 |            |      |      |      |   |   | Debug-interface Serial Wire data input / output. |                                                                                                    |

| DBG_SWDIO                       | PF1        | PF1  |      |      |   |   |                                                  | Note that this function is enabled to pin out of reset, and has a built-in pull up.                |

|                                 |            |      |      |      |   |   |                                                  | Debug-interface Serial Wire viewer Output.                                                         |

| DBG_SWO                         | PF2        | PC15 |      |      |   |   |                                                  | Note that this function is not enabled after reset, and must be<br>enabled by software to be used. |

# **5 PCB Layout and Soldering**

## 5.1 Recommended PCB Layout

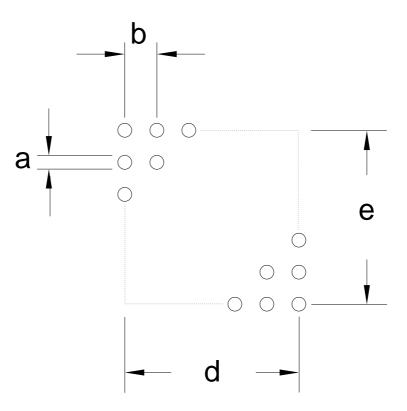

#### Figure 5.1. BGA48 PCB Land Pattern

Table 5.1. BGA48 PCB Land Pattern Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Row name and column number |

|--------|-----------|--------|----------------------------|

| а      | 0.25      | r1     | А                          |

| b      | 0.50      | rn     | G                          |

| d      | 3.00      | c1     | 1                          |

| е      | 3.00      | cn     | 7                          |

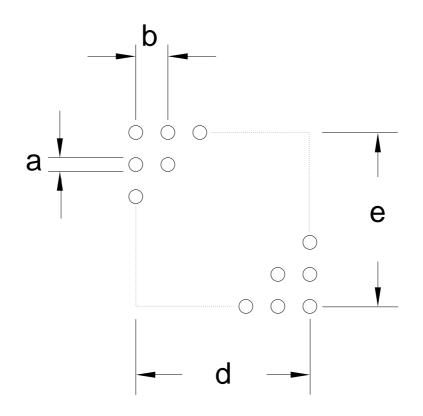

#### Figure 5.2. BGA48 PCB Solder Mask

Table 5.2. BGA48 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| a      | 0.28      |

| b      | 0.50      |

| d      | 3.00      |

| e      | 3.00      |

Initial preliminary release.

# **B** Contact Information

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

# List of Equations

| 3.1. | Total ACMP Active Current                         | 40 |

|------|---------------------------------------------------|----|

|      | VCMP Trigger Level as a Function of Level Setting |    |

# silabs.com