Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFL

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 118                                                                              |

| Program Memory Size        | 448KB (448K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2285m56f80laafxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XC2287M, XC2286M, XC2285M XC2000 Family / Base Line

| Pin | Symbol            | Ctrl.      | Туре | Function                                                                                                                                                                           |  |  |

|-----|-------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8   | P7.0              | O0 / I     | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                      |  |  |

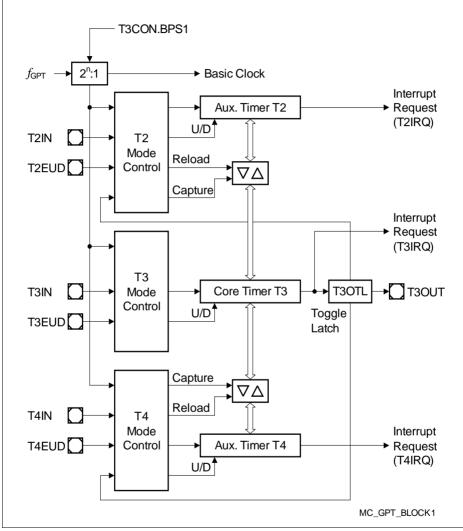

|     | T3OUT             | 01         | St/B | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                |  |  |

|     | T6OUT             | 02         | St/B | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                |  |  |

|     | TDO_A             | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 0 or 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |

|     | ESR2_1            | I          | St/B | ESR2 Trigger Input 1                                                                                                                                                               |  |  |

|     | RxDC4B            | I          | St/B | CAN Node 4 Receive Data Input                                                                                                                                                      |  |  |

| 9   | P7.3              | O0 / I     | St/B | Bit 3 of Port 7, General Purpose Input/Output                                                                                                                                      |  |  |

|     | EMUX1             | 01         | St/B | External Analog MUX Control Output 1 (ADC1)                                                                                                                                        |  |  |

|     | U0C1_DOUT         | 02         | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                  |  |  |

|     | U0C0_DOUT         | O3         | St/B | USIC0 Channel 0 Shift Data Output                                                                                                                                                  |  |  |

|     | CCU62_CCP<br>OS1A | I          | St/B | CCU62 Position Input 1                                                                                                                                                             |  |  |

|     | TMS_C             | IH         | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it.                  |  |  |

|     | U0C1_DX0F         | I          | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                   |  |  |

| 10  | P8.2              | O0 / I     | St/B | Bit 2 of Port 8, General Purpose Input/Output                                                                                                                                      |  |  |

|     | CCU60_CC6<br>2    | 01         | St/B | CCU60 Channel 2 Output                                                                                                                                                             |  |  |

|     | TxDC1             | O2         | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                    |  |  |

|     | U1C1_DOUT         | O3         | St/B | USIC1 Channel 1 Shift Data output                                                                                                                                                  |  |  |

|     | CCU60_CC6<br>2INB | I          | St/B | CCU60 Channel 2 Input                                                                                                                                                              |  |  |

| 11  | P7.1              | O0 / I     | St/B | Bit 1 of Port 7, General Purpose Input/Output                                                                                                                                      |  |  |

|     | EXTCLK            | 01         | St/B | Programmable Clock Signal Output                                                                                                                                                   |  |  |

|     | TXDC4             | 02         | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                    |  |  |

|     | CCU62_CTR<br>APA  | I          | St/B | CCU62 Emergency Trap Input                                                                                                                                                         |  |  |

|     | BRKIN_C           | 1          | St/B | OCDS Break Signal Input                                                                                                                                                            |  |  |

# XC2287M, XC2286M, XC2285M XC2000 Family / Base Line

| Table 6         Pin Definitions and Functions (cont'd) |                  |       |      |                                                   |  |

|--------------------------------------------------------|------------------|-------|------|---------------------------------------------------|--|

| Pin                                                    | Symbol           | Ctrl. | Туре | Function                                          |  |

| 39                                                     | P5.4             | I     | In/A | Bit 4 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH4         | I     | In/A | Analog Input Channel 4 for ADC0                   |  |

|                                                        | CCU63_T12<br>HRB | I     | In/A | External Run Control Input for T12 of CCU63       |  |

|                                                        | T3EUDA           | I     | In/A | GPT12E Timer T3 External Up/Down Control Input    |  |

|                                                        | TMS_A            | I     | In/A | JTAG Test Mode Selection Input                    |  |

| 40                                                     | P5.5             | I     | In/A | Bit 5 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH5         | I     | In/A | Analog Input Channel 5 for ADC0                   |  |

|                                                        | CCU60_T12<br>HRB | I     | In/A | External Run Control Input for T12 of CCU60       |  |

| 41                                                     | P5.6             | I     | In/A | Bit 6 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH6         | I     | In/A | Analog Input Channel 6 for ADC0                   |  |

| 42                                                     | P5.7             | I     | In/A | Bit 7 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH7         | I     | In/A | Analog Input Channel 7 for ADC0                   |  |

| 43                                                     | P5.8             | I     | In/A | Bit 8 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH8         | I     | In/A | Analog Input Channel 8 for ADC0                   |  |

|                                                        | ADC1_CH8         | I     | In/A | Analog Input Channel 8 for ADC1                   |  |

|                                                        | CCU6x_T12H<br>RC | I     | In/A | External Run Control Input for T12 of CCU60/1/2/3 |  |

|                                                        | CCU6x_T13H<br>RC | I     | In/A | External Run Control Input for T13 of CCU60/1/2/3 |  |

|                                                        | U2C0_DX0F        | I     | In/A | USIC2 Channel 0 Shift Data Input                  |  |

| 44                                                     | P5.9             | I     | In/A | Bit 9 of Port 5, General Purpose Input            |  |

|                                                        | ADC0_CH9         | I     | In/A | Analog Input Channel 9 for ADC0                   |  |

|                                                        | ADC1_CH9         | I     | In/A | Analog Input Channel 9 for ADC1                   |  |

|                                                        | CC2_T7IN         | I     | In/A | CAPCOM2 Timer T7 Count Input                      |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                |  |

|-------|--------------------------------------------------------|------------|------|------------------------------------------------|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                       |  |

| 56    | P2.1                                                   | O0 / I     | St/B | Bit 1 of Port 2, General Purpose Input/Output  |  |

|       | TxDC0                                                  | 01         | St/B | CAN Node 0 Transmit Data Output                |  |

|       | CCU63_CC6<br>1                                         | O2         | St/B | CCU63 Channel 1 Output                         |  |

|       | AD14                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 14    |  |

|       | RxDC5C                                                 | I          | St/B | CAN Node 5 Receive Data Input                  |  |

|       | CCU63_CC6<br>1INB                                      | I          | St/B | CCU63 Channel 1 Input                          |  |

|       | T5EUDB                                                 | I          | St/B | GPT12E Timer T5 External Up/Down Control Input |  |

|       | ESR1_5                                                 | I          | St/B | ESR1 Trigger Input 5                           |  |

| 57    | P11.4                                                  | O0 / I     | St/B | Bit 4 of Port 11, General Purpose Input/Output |  |

|       | CCU61_CC6<br>2                                         | 01         | St/B | CCU61 Channel 2 Output                         |  |

|       | U3C1_DOUT                                              | 02         | St/B | USIC3 Channel 1 Shift Data Output              |  |

|       | RxDC5B                                                 | I          | St/B | CAN Node 5 Receive Data Input                  |  |

|       | CCU61_CC6<br>2INB                                      | I          | St/B | CCU61 Channel 2 Input                          |  |

|       | U3C1_DX0B                                              | I          | St/B | USIC3 Channel 1 Shift Data Input               |  |

| 58    | P2.2                                                   | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output  |  |

|       | TxDC1                                                  | 01         | St/B | CAN Node 1 Transmit Data Output                |  |

|       | CCU63_CC6<br>2                                         | O2         | St/B | CCU63 Channel 2 Output                         |  |

|       | AD15                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15    |  |

|       | CCU63_CC6<br>2INB                                      | I          | St/B | CCU63 Channel 2 Input                          |  |

|       | ESR2_5                                                 | I          | St/B | ESR2 Trigger Input 5                           |  |

|       | 1                                                      |            |      | 1                                              |  |

# XC2287M, XC2286M, XC2285M XC2000 Family / Base Line

# **General Device Information**

| Table 6Pin Definitions and Functions (cont'd) |                  |            |      |                                                |

|-----------------------------------------------|------------------|------------|------|------------------------------------------------|

| Pin                                           | Symbol           | Ctrl.      | Туре | Function                                       |

| 101                                           | P3.5             | O0 / I     | St/B | Bit 5 of Port 3, General Purpose Input/Output  |

|                                               | U2C1_SCLK<br>OUT | O1         | St/B | USIC2 Channel 1 Shift Clock Output             |

|                                               | U2C0_SELO<br>2   | O2         | St/B | USIC2 Channel 0 Select/Control 2 Output        |

|                                               | U0C0_SELO<br>5   | O3         | St/B | USIC0 Channel 0 Select/Control 5 Output        |

|                                               | U2C1_DX1A        | I          | St/B | USIC2 Channel 1 Shift Clock Input              |

| 102                                           | P0.6             | O0 / I     | St/B | Bit 6 of Port 0, General Purpose Input/Output  |

|                                               | U1C1_DOUT        | 01         | St/B | USIC1 Channel 1 Shift Data Output              |

|                                               | TxDC1            | O2         | St/B | CAN Node 1 Transmit Data Output                |

|                                               | CCU61_COU<br>T63 | O3         | St/B | CCU61 Channel 3 Output                         |

|                                               | A6               | ОН         | St/B | External Bus Interface Address Line 6          |

|                                               | U1C1_DX0A        | Ι          | St/B | USIC1 Channel 1 Shift Data Input               |

|                                               | CCU61_CTR<br>APA | I          | St/B | CCU61 Emergency Trap Input                     |

|                                               | U1C1_DX1B        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |

| 103                                           | P10.6            | O0 / I     | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|                                               | U0C0_DOUT        | O1         | St/B | USIC0 Channel 0 Shift Data Output              |

|                                               | TxDC4            | 02         | St/B | CAN Node 4 Transmit Data Output                |

|                                               | U1C0_SELO<br>0   | O3         | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|                                               | AD6              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 6     |

|                                               | U0C0_DX0C        | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|                                               | U1C0_DX2D        | I          | St/B | USIC1 Channel 0 Shift Control Input            |

|                                               | CCU60_CTR<br>APA | 1          | St/B | CCU60 Emergency Trap Input                     |

# XC2287M, XC2286M, XC2285M XC2000 Family / Base Line

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                   |  |  |

|-------|--------------------------------------------------------|--------|------|---------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                          |  |  |

| 107   | P3.7                                                   | O0 / I | St/B | Bit 7 of Port 3, General Purpose Input/Output     |  |  |

|       | U2C1_DOUT                                              | 01     | St/B | USIC2 Channel 1 Shift Data Output                 |  |  |

|       | U2C0_SELO<br>3                                         | O2     | St/B | USIC2 Channel 0 Select/Control 3 Output           |  |  |

|       | U0C0_SELO<br>7                                         | O3     | St/B | USIC0 Channel 0 Select/Control 7 Output           |  |  |

|       | U2C1_DX0B                                              | I      | St/B | USIC2 Channel 1 Shift Data Input                  |  |  |

| 111   | P1.0                                                   | O0 / I | St/B | Bit 0 of Port 1, General Purpose Input/Output     |  |  |

|       | U1C0_MCLK<br>OUT                                       | O1     | St/B | USIC1 Channel 0 Master Clock Output               |  |  |

|       | U1C0_SELO<br>4                                         | O2     | St/B | USIC1 Channel 0 Select/Control 4 Output           |  |  |

|       | A8                                                     | ОН     | St/B | External Bus Interface Address Line 8             |  |  |

|       | ESR1_3                                                 | I      | St/B | ESR1 Trigger Input 3                              |  |  |

|       | CCU62_CTR<br>APB                                       | I      | St/B | CCU62 Emergency Trap Input                        |  |  |

|       | T6INB                                                  | I      | St/B | GPT12E Timer T6 Count/Gate Input                  |  |  |

| 112   | P9.0                                                   | O0 / I | St/B | Bit 0 of Port 9, General Purpose Input/Output     |  |  |

|       | CCU63_CC6<br>0                                         | O1     | St/B | CCU63 Channel 0 Output                            |  |  |

|       | CCU63_CC6<br>0INA                                      | I      | St/B | CCU63 Channel 0 Input                             |  |  |

|       | T6EUDB                                                 | I      | St/B | GPT12E Timer T6 External Up/Down Control<br>Input |  |  |

# **General Device Information**

| Table 6         Pin Definitions and Functions (cont'd) |                   |        |      |                                                 |  |

|--------------------------------------------------------|-------------------|--------|------|-------------------------------------------------|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                        |  |

| 126                                                    | P9.5              | O0 / I | St/B | Bit 5 of Port 9, General Purpose Input/Output   |  |

|                                                        | CCU63_COU<br>T62  | O1     | St/B | CCU63 Channel 2 Output                          |  |

|                                                        | U2C0_DOUT         | 02     | St/B | USIC2 Channel 0 Shift Data Output               |  |

|                                                        | CCU62_COU<br>T62  | O3     | St/B | CCU62 Channel 2 Output                          |  |

|                                                        | U2C0_DX0E         | I      | St/B | USIC2 Channel 0 Shift Data Input                |  |

|                                                        | CCU60_CCP<br>OS2B | I      | St/B | CCU60 Position Input 2                          |  |

| 128                                                    | P10.14            | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output |  |

|                                                        | U1C0_SELO<br>1    | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output         |  |

|                                                        | U0C1_DOUT         | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |

|                                                        | U3C0_SCLK<br>OUT  | O3     | St/B | USIC3 Channel 0 Shift Clock Output              |  |

|                                                        | RD                | ОН     | St/B | External Bus Interface Read Strobe Output       |  |

|                                                        | ESR2_2            | I      | St/B | ESR2 Trigger Input 2                            |  |

|                                                        | U0C1_DX0C         | I      | St/B | USIC0 Channel 1 Shift Data Input                |  |

|                                                        | RxDC3C            | I      | St/B | CAN Node 3 Receive Data Input                   |  |

|                                                        | U3C0_DX1A         | I      | St/B | USIC3 Channel 0 Shift Clock Input               |  |

| 129                                                    | P1.4              | O0 / I | St/B | Bit 4 of Port 1, General Purpose Input/Output   |  |

|                                                        | CCU62_COU<br>T61  | 01     | St/B | CCU62 Channel 1 Output                          |  |

|                                                        | U1C1_SELO<br>4    | O2     | St/B | USIC1 Channel 1 Select/Control 4 Output         |  |

|                                                        | U2C0_SELO<br>5    | O3     | St/B | USIC2 Channel 0 Select/Control 5 Output         |  |

|                                                        | A12               | ОН     | St/B | External Bus Interface Address Line 12          |  |

|                                                        | U2C0_DX2B         | I      | St/B | USIC2 Channel 0 Shift Control Input             |  |

|                                                        | RxDC5A            | I      | St/B | CAN Node 5 Receive Data Input                   |  |

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2** × **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC2000 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

**The on-chip Flash memory** stores code, constant data, and control data. The on-chip Flash memory consists of 1 module of 64 Kbytes (preferably for data storage) and modules with a maximum capacity of 256 Kbytes each. Each module is organized in sectors of 4 Kbytes.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.5.

### Memory Content Protection

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

# 3.2 External Bus Controller

All external memory access operations are performed by a special on-chip External Bus Controller (EBC). The EBC also controls access to resources connected to the on-chip LXBus (MultiCAN and the USIC modules). The LXBus is an internal representation of the external bus that allows access to integrated peripherals and modules in the same way as to external components.

The EBC can be programmed either to Single Chip Mode, when no external memory is required, or to an external bus mode with the following selections<sup>1)</sup>:

- Address Bus Width with a range of 0 ... 24-bit

- Data Bus Width 8-bit or 16-bit

- Bus Operation Multiplexed or Demultiplexed

The bus interface uses Port 10 and Port 2 for addresses and data. In the demultiplexed bus modes, the lower addresses are output separately on Port 0 and Port 1. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines shall be assigned to Port 2.

External  $\overline{CS}$  signals (address windows plus default) can be generated and output on Port 4 in order to save external glue logic. External modules can be directly connected to the common address/data bus and their individual select lines.

A HOLD/HLDA protocol is available for bus arbitration; this allows the sharing of external resources with other bus masters. The bus arbitration is enabled by software, after which pins P3.0 ... P3.2 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. In Slave Mode pin HLDA is switched to be an input. This allows the direct connection of the slave controller to another master controller without glue logic.

Important timing characteristics of the external bus interface are programmable (with registers TCONCSx/FCONCSx) to allow the user to adapt it to a wide range of different types of memories and external peripherals.

Access to very slow memories or modules with varying access times is supported by a special 'Ready' function. The active level of the control input signal is selectable.

In addition, up to four independent address windows may be defined (using registers ADDRSELx) to control access to resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these four address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is based on the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

# 3.6 Interrupt System

The architecture of the XC228xM supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Where in a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC228xM has eight PEC channels, each whith fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC228xM can react quickly to the occurrence of non-deterministic events.

### Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

### External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

### Trap Processing

The XC228xM provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

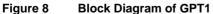

# 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XC228xM can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

# Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

| Table 11 In | struction Set Summary (cont'd)                                                           |       |  |  |

|-------------|------------------------------------------------------------------------------------------|-------|--|--|

| Mnemonic    | Description                                                                              | Bytes |  |  |

| ROL/ROR     | Rotate left/right direct word GPR                                                        | 2     |  |  |

| ASHR        | Arithmetic (sign bit) shift right direct word GPR                                        | 2     |  |  |

| MOV(B)      | Move word (byte) data                                                                    | 2/4   |  |  |

| MOVBS/Z     | Move byte operand to word op. with sign/zero extension                                   | 2/4   |  |  |

| JMPA/I/R    | Jump absolute/indirect/relative if condition is met                                      | 4     |  |  |

| JMPS        | Jump absolute to a code segment                                                          | 4     |  |  |

| JB(C)       | Jump relative if direct bit is set (and clear bit)                                       | 4     |  |  |

| JNB(S)      | Jump relative if direct bit is not set (and set bit)                                     | 4     |  |  |

| CALLA/I/R   | Call absolute/indirect/relative subroutine if condition is met                           | 4     |  |  |

| CALLS       | Call absolute subroutine in any code segment                                             | 4     |  |  |

| PCALL       | Push direct word register onto system stack and call absolute subroutine                 |       |  |  |

| TRAP        | Call interrupt service routine via immediate trap number                                 | 2     |  |  |

| PUSH/POP    | Push/pop direct word register onto/from system stack                                     | 2     |  |  |

| SCXT        | Push direct word register onto system stack and update register with word operand        |       |  |  |

| RET(P)      | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |  |  |

| RETS        | Return from inter-segment subroutine                                                     | 2     |  |  |

| RETI        | Return from interrupt service subroutine                                                 | 2     |  |  |

| SBRK        | Software Break                                                                           | 2     |  |  |

| SRST        | Software Reset                                                                           | 4     |  |  |

| IDLE        | Enter Idle Mode                                                                          | 4     |  |  |

| PWRDN       | Unused instruction <sup>1)</sup>                                                         | 4     |  |  |

| SRVWDT      | Service Watchdog Timer                                                                   | 4     |  |  |

| DISWDT/ENWD | T Disable/Enable Watchdog Timer                                                          | 4     |  |  |

| EINIT       | End-of-Initialization Register Lock                                                      | 4     |  |  |

| ATOMIC      | Begin ATOMIC sequence                                                                    | 2     |  |  |

| EXTR        | Begin EXTended Register sequence                                                         | 2     |  |  |

| EXTP(R)     | Begin EXTended Page (and Register) sequence                                              | 2/4   |  |  |

| EXTS(R)     | Begin EXTended Segment (and Register) sequence                                           | 2/4   |  |  |

#### Table 11 Instruction Cat Cummany (cont'd)

|              | Table II instruction bet building (conta) |       |  |  |  |  |

|--------------|-------------------------------------------|-------|--|--|--|--|

| Mnemonic     | Description                               | Bytes |  |  |  |  |

| NOP          | Null operation                            | 2     |  |  |  |  |

| CoMUL/CoMAC  | Multiply (and accumulate)                 | 4     |  |  |  |  |

| CoADD/CoSUB  | Add/Subtract                              | 4     |  |  |  |  |

| Co(A)SHR     | (Arithmetic) Shift right                  | 4     |  |  |  |  |

| CoSHL        | Shift left                                | 4     |  |  |  |  |

| CoLOAD/STORE | Load accumulator/Store MAC register       | 4     |  |  |  |  |

| CoCMP        | Compare                                   | 4     |  |  |  |  |

| CoMAX/MIN    | Maximum/Minimum                           | 4     |  |  |  |  |

| CoABS/CoRND  | Absolute value/Round accumulator          | 4     |  |  |  |  |

| CoMOV        | Data move                                 | 4     |  |  |  |  |

| CoNEG/NOP    | Negate accumulator/Null operation         | 4     |  |  |  |  |

|              |                                           |       |  |  |  |  |

### Table 11 Instruction Set Summary (cont'd)

1) The Enter Power Down Mode instruction is not used in the XC228xM, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

# 4.3 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance. *Note: Operating Conditions apply.*

### Table 18ADC Parameters

| Parameter                                       | Symbol                     |      | Value | S    | Unit     | Note /                                             |

|-------------------------------------------------|----------------------------|------|-------|------|----------|----------------------------------------------------|

|                                                 |                            | Min. | Тур.  | Max. |          | Test Condition                                     |

| Switched capacitance at an analog input         | C <sub>AINSW</sub><br>CC   | -    | 4     | 5    | pF       | not subject to<br>production<br>test <sup>1)</sup> |

| Total capacitance at an analog input            | $C_{AINT}$ CC              | _    | 10    | 12   | pF       | not subject to production test <sup>1)</sup>       |

| Switched capacitance at the reference input     | C <sub>AREFSW</sub><br>CC  | _    | 7     | 9    | pF       | not subject to production test <sup>1)</sup>       |

| Total capacitance at the reference input        | C <sub>AREFT</sub><br>CC   | _    | 13    | 15   | pF       | not subject to production test <sup>1)</sup>       |

| Differential Non-Linearity<br>Error             | EA <sub>DNL</sub>  <br>CC  | -    | 0.8   | 1.0  | LSB      | not subject to<br>production test                  |

| Gain Error                                      | EA <sub>GAIN</sub>  <br>CC | -    | 0.4   | 0.8  | LSB      | not subject to<br>production test                  |

| Integral Non-Linearity                          | EA <sub>INL</sub>  <br>CC  | -    | 0.8   | 1.2  | LSB      | not subject to<br>production test                  |

| Offset Error                                    | EA <sub>OFF</sub>  <br>CC  | -    | 0.5   | 0.8  | LSB      | not subject to<br>production test                  |

| Analog clock frequency                          | $f_{\rm ADCI}{\rm SR}$     | 0.5  | -     | 20   | MHz      | Upper voltage range                                |

|                                                 |                            | 0.5  | -     | 16.5 | MHz      | Lower voltage range                                |

| Input resistance of the selected analog channel | R <sub>AIN</sub> CC        | -    | -     | 2    | kOh<br>m | not subject to production test <sup>1)</sup>       |

| Input resistance of the reference input         | R <sub>AREF</sub><br>CC    | -    | -     | 2    | kOh<br>m | not subject to production test <sup>1)</sup>       |

# 4.5 Flash Memory Parameters

The XC228xM is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XC228xM's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                 | Symbol               | Values |                 |                 | Unit       | Note /                                                                    |

|-------------------------------------------|----------------------|--------|-----------------|-----------------|------------|---------------------------------------------------------------------------|

|                                           |                      | Min.   | Тур.            | Max.            |            | Test Condition                                                            |

| Parallel Flash module program/erase limit | $N_{\rm PP}{ m SR}$  | -      | -               | 4 <sup>1)</sup> |            | $N_{\text{FL}_{\text{RD}}} \le 1,$<br>$f_{\text{SYS}} \le 80 \text{ MHz}$ |

| depending on Flash read activity          |                      | -      | -               | 1 <sup>2)</sup> |            | $N_{\rm FL_RD}$ > 1                                                       |

| Flash erase endurance for security pages  | $N_{\rm SEC}{ m SR}$ | 10     | -               | -               | cycle<br>s | $t_{RET} \ge 20$ years                                                    |

| Flash wait states3)                       | $N_{\rm WSFLAS}$     | 1      | -               | -               |            | $f_{SYS} \le 8 \text{ MHz}$                                               |

|                                           | <sub>н</sub> SR      | 2      | -               | -               |            | $f_{SYS} \le 13 \text{ MHz}$                                              |

|                                           |                      | 3      | -               | -               |            | $f_{\rm SYS} \le 17 \ \rm MHz$                                            |

|                                           |                      | 4      | -               | -               |            | $f_{\rm SYS}$ > 17 MHz                                                    |

| Erase time per<br>sector/page             | t <sub>ER</sub> CC   | -      | 7 <sup>4)</sup> | 8.0             | ms         |                                                                           |

| Programming time per page                 | t <sub>PR</sub> CC   | -      | 34)             | 3.5             | ms         |                                                                           |

| Data retention time                       | t <sub>RET</sub> CC  | 20     | -               | -               | year<br>s  | $N_{\rm Er} \le 1\ 000$ cycles                                            |

| Drain disturb limit                       | $N_{\rm DD}{ m SR}$  | 32     | -               | -               | cycle<br>s |                                                                           |

#### Table 23 Flash Parameters

Table 27 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtyp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

| Table 27 Standard Pad Parameters for Lower Voltage Rang | Standard Pad Parameter | s for Lower Voltage Range |

|---------------------------------------------------------|------------------------|---------------------------|

|---------------------------------------------------------|------------------------|---------------------------|

| Parameter                                                    | Symbol                  | Values |      |                                          | Unit | Note /                        |

|--------------------------------------------------------------|-------------------------|--------|------|------------------------------------------|------|-------------------------------|

|                                                              |                         | Min.   | Тур. | Max.                                     | 1    | Test Condition                |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 10                                       | mA   | Strong driver                 |

|                                                              |                         | _      | -    | 2.5                                      | mA   | Medium driver                 |

|                                                              |                         | -      | -    | 0.5                                      | mA   | Weak driver                   |

| Nominal output driver                                        | I <sub>Onom</sub><br>CC | -      | -    | 2.5                                      | mA   | Strong driver                 |

| current (absolute value)                                     |                         | _      | -    | 1.0                                      | mA   | Medium driver                 |

|                                                              |                         | -      | -    | 0.1                                      | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)                           | t <sub>RF</sub> CC      | -      | -    | 6.2 +<br>0.24 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Sharp edge  |

|                                                              |                         | -      | -    | 24 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Medium edge |

|                                                              |                         | -      | -    | 34 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Slow edge   |

|                                                              |                         | -      | -    | 37 +<br>0.65 x<br><i>C</i> <sub>L</sub>  | ns   | Medium driver                 |

|                                                              |                         | -      | -    | 500 +<br>2.5 x<br>C <sub>L</sub>         | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

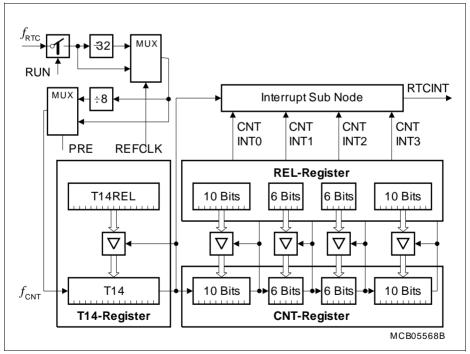

# 4.6.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

# XC2287M, XC2286M, XC2285M XC2000 Family / Base Line

### **Electrical Parameters**

Figure 25 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

# 4.6.5.2 External Bus Arbitration

If the arbitration signals are enabled, the XC228xM makes its external resources available in response to an arbitration request.

Note: Operating Conditions apply.

| Table 32 | Bus Arbitration Timing for Upper Voltage Range |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

| Parameter                              | Symbol                    | Values |      |      | Unit | Note /         |

|----------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                        |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| Input setup time<br>HOLD input         | <i>t</i> <sub>40</sub> SR | 23     |      | -    | ns   |                |

| Output delay rising edge<br>HLDA, BREQ | <i>t</i> <sub>41</sub> CC | -1     |      | 13   | ns   |                |

| Output delay falling edge<br>HLDA      | <i>t</i> <sub>42</sub> CC | -2     |      | 14   | ns   |                |

| Table 33 | Bus Arbitration Timing for Lower Voltage Range |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

| Parameter                              | Symbol                    | Values |      |      | Unit | Note /         |

|----------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                        |                           | Min.   | Тур. | Max. |      | Test Condition |

| Input setup time<br>HOLD input         | <i>t</i> <sub>40</sub> SR | 28     |      | -    | ns   |                |

| Output delay rising edge<br>HLDA, BREQ | <i>t</i> <sub>41</sub> CC | -1     |      | 19   | ns   |                |

| Output delay falling edge<br>HLDA      | <i>t</i> <sub>42</sub> CC | -2     |      | 21   | ns   |                |

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. | 1    | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | -    | -    | ns   | 2)             |

| TCK high time                                                            | $t_2$ SR                  | 16               | -    | _    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | _    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 32   | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 32   | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 32   | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

# Table 41 JTAG Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.