## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 66MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 118                                                                              |

| Program Memory Size        | 576KB (576K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2286m72f66laahxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                            | Summary of Features         7           Basic Device Types         9           Special Device Types         10           Definition of Feature Variants         11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                                   | General Device Information13Pin Configuration and Definition14Identification Registers52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.20 | Functional Description         53           Memory Subsystem and Organization         54           External Bus Controller         57           Central Processing Unit (CPU)         58           Memory Protection Unit (MPU)         60           Memory Checker Module (MCHK)         60           Interrupt System         61           On-Chip Debug Support (OCDS)         62           Capture/Compare Unit (CAPCOM2)         63           Capture/Compare Units CCU6x         66           General Purpose Timer (GPT12E) Unit         68           Real Time Clock         72           A/D Converters         74           Universal Serial Interface Channel Modules (USIC)         75           MultiCAN Module         77           System Timer         78           Watchdog Timer         79           Clock Generation         79           Parallel Ports         80           Power Management         81           Instruction Set Summary         82 |

|                                                                                                                                                          | Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3                                                                                                               | Electrical Parameters85General Parameters85Absolut Maximum Rating Conditions85Operating Conditions86Pad Timing Definition88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.1.3<br>4.1.4<br>4.2                                                                                                                                    | Parameter Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2<br>4.2.1<br>4.2.2                                                                                                                                    | DC Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2.3<br>4.3                                                                                                                                             | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## **Summary of Features**

## 1.3 Definition of Feature Variants

The XC228xM types are offered with several Flash memory sizes. **Table 3** describes the location of the available memory areas for each Flash memory size.

Table 3 Flash Memory Allocation

| Total Flash Size | Flash Area A <sup>1)</sup>                   | Flash Area B                                 | Flash Area C         |

|------------------|----------------------------------------------|----------------------------------------------|----------------------|

| 832 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>CC'FFFF <sub>H</sub> | n.a.                 |

| 576 Kbytes       | C0'0000 <sub>H</sub>                         | C1'0000 <sub>H</sub>                         | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>                         | C7'FFFF <sub>H</sub>                         | CC'FFFF <sub>H</sub> |

| 448 Kbytes       | C0'0000 <sub>H</sub>                         | C1'0000 <sub>H</sub>                         | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>                         | C5'FFFF <sub>H</sub>                         | CC'FFFF <sub>H</sub> |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

Table 4 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 | Flash 2 | Flash 3 |

|------------------|-----------------------|---------|---------|---------|

| 832 Kbytes       | 256                   | 256     | 256     | 64      |

| 576 Kbytes       | 256                   | 256     |         | 64      |

| 448 Kbytes       | 256                   | 128     |         | 64      |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XC228xM types are offered with different interface options. **Table 5** lists the available channels for each option.

Table 5 Interface Channel Association

| Total Number     | Available Channels                                        |  |

|------------------|-----------------------------------------------------------|--|

| 16 ADC0 channels | CH0 CH15                                                  |  |

| 8 ADC0 channels  | CH0 CH7                                                   |  |

| 8 ADC1 channels  | CH0 CH7 (overlay: CH8 CH11)                               |  |

| 6 CAN nodes      | CAN0, CAN1, CAN2, CAN3, CAN4, CAN5<br>256 message objects |  |

| 3 CAN nodes      | CAN0, CAN1, CAN2<br>64 message objects                    |  |

| 2 CAN nodes      | CAN0, CAN1<br>64 message objects                          |  |

## **Summary of Features**

Table 5 Interface Channel Association (cont'd)

| Total Number      | Available Channels                             |

|-------------------|------------------------------------------------|

| 8 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1, U3C0, U3C1 |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1                         |

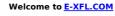

The XC228xM types are offered with several SRAM memory sizes. Figure 1 shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

## **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |  |  |

|-----|------------------|--------|------|------------------------------------------------|--|--|

| 45  | P5.10            | I      | In/A | Bit 10 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH10        | I      | In/A | Analog Input Channel 10 for ADC0               |  |  |

|     | ADC1_CH10        | I      | In/A | Analog Input Channel 10 for ADC1               |  |  |

|     | BRKIN_A          | I      | In/A | OCDS Break Signal Input                        |  |  |

|     | U2C1_DX0F        | I      | In/A | USIC2 Channel 1 Shift Data Input               |  |  |

|     | CCU61_T13<br>HRA | I      | In/A | External Run Control Input for T13 of CCU61    |  |  |

| 46  | P5.11            | I      | In/A | Bit 11 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH11        | I      | In/A | Analog Input Channel 11 for ADC0               |  |  |

|     | ADC1_CH11        | I      | In/A | Analog Input Channel 11 for ADC1               |  |  |

| 47  | P5.12            | I      | In/A | Bit 12 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH12        | I      | In/A | Analog Input Channel 12 for ADC0               |  |  |

| 48  | P5.13            | I      | In/A | Bit 13 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH13        | I      | In/A | Analog Input Channel 13 for ADC0               |  |  |

|     | CCU63_T13<br>HRF | I      | In/A | External Run Control Input for T13 of CCU63    |  |  |

| 49  | P5.14            | I      | In/A | Bit 14 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH14        | I      | In/A | Analog Input Channel 14 for ADC0               |  |  |

| 50  | P5.15            | I      | In/A | Bit 15 of Port 5, General Purpose Input        |  |  |

|     | ADC0_CH15        | I      | In/A | Analog Input Channel 15 for ADC0               |  |  |

|     | RxDC2F           | I      | In/A | CAN Node 2 Receive Data Input                  |  |  |

| 51  | P2.12            | O0 / I | St/B | Bit 12 of Port 2, General Purpose Input/Output |  |  |

|     | U0C0_SELO<br>4   | O1     | St/B | USIC0 Channel 0 Select/Control 4 Output        |  |  |

|     | U0C1_SELO<br>3   | O2     | St/B | USIC0 Channel 1 Select/Control 3 Output        |  |  |

|     | TXDC2            | О3     | St/B | CAN Node 2 Transmit Data Output                |  |  |

|     | READY            | IH     | St/B | External Bus Interface READY Input             |  |  |

## **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                       |

|-----|------------------|------------|------|------------------------------------------------|

| 98  | P10.4            | O0 / I     | St/B | Bit 4 of Port 10, General Purpose Input/Output |

|     | U0C0_SELO<br>3   | O1         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CCU60_COU<br>T61 | O2         | St/B | CCU60 Channel 1 Output                         |

|     | U3C0_DOUT        | О3         | St/B | USIC3 Channel 0 Shift Data Output              |

|     | AD4              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 4     |

|     | U0C0_DX2B        | I          | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2B        | I          | St/B | USIC0 Channel 1 Shift Control Input            |

|     | ESR1_9           | I          | St/B | ESR1 Trigger Input 9                           |

| 99  | P3.4             | O0 / I     | St/B | Bit 4 of Port 3, General Purpose Input/Output  |

|     | U2C1_SELO<br>0   | O1         | St/B | USIC2 Channel 1 Select/Control 0 Output        |

|     | U2C0_SELO<br>1   | O2         | St/B | USIC2 Channel 0 Select/Control 1 Output        |

|     | U0C0_SELO<br>4   | О3         | St/B | USIC0 Channel 0 Select/Control 4 Output        |

|     | U2C1_DX2A        | I          | St/B | USIC2 Channel 1 Shift Control Input            |

|     | RxDC4A           | I          | St/B | CAN Node 4 Receive Data Input                  |

| 100 | P10.5            | O0 / I     | St/B | Bit 5 of Port 10, General Purpose Input/Output |

|     | U0C1_SCLK<br>OUT | O1         | St/B | USIC0 Channel 1 Shift Clock Output             |

|     | CCU60_COU<br>T62 | O2         | St/B | CCU60 Channel 2 Output                         |

|     | U2C0_DOUT        | О3         | St/B | USIC2 Channel 0 Shift Data Output              |

|     | AD5              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 5     |

|     | U0C1_DX1B        | I          | St/B | USIC0 Channel 1 Shift Clock Input              |

## **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                      |

|-----|-------------------|--------|------|-----------------------------------------------|

| 133 | P1.6              | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output |

|     | CCU62_CC6<br>1    | O1 / I | St/B | CCU62 Channel 1 Output                        |

|     | U1C1_SELO<br>2    | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output       |

|     | U2C0_DOUT         | О3     | St/B | USIC2 Channel 0 Shift Data Output             |

|     | A14               | ОН     | St/B | External Bus Interface Address Line 14        |

|     | U2C0_DX0D         | I      | St/B | USIC2 Channel 0 Shift Data Input              |

|     | CCU62_CC6<br>1INA | I      | St/B | CCU62 Channel 1 Input                         |

| 134 | P9.7              | O0 / I | St/B | Bit 7 of Port 9, General Purpose Input/Output |

|     | CCU62_COU<br>T60  | O1     | St/B | CCU62 Channel 0 Output                        |

|     | CCU62_COU<br>T63  | O2     | St/B | CCU62 Channel 3 Output                        |

|     | CCU63_CTR<br>APB  | I      | St/B | CCU63 Emergency Trap Input                    |

|     | U2C0_DX1D         | I      | St/B | USIC2 Channel 0 Shift Clock Input             |

|     | CCU60_CCP<br>OS0B | I      | St/B | CCU60 Position Input 0                        |

| 135 | P1.7              | O0 / I | St/B | Bit 7 of Port 1, General Purpose Input/Output |

|     | CCU62_CC6         | O1     | St/B | CCU62 Channel 0 Output                        |

|     | U1C1_MCLK<br>OUT  | O2     | St/B | USIC1 Channel 1 Master Clock Output           |

|     | U2C0_SCLK<br>OUT  | О3     | St/B | USIC2 Channel 0 Shift Clock Output            |

|     | A15               | ОН     | St/B | External Bus Interface Address Line 15        |

|     | U2C0_DX1C         | I      | St/B | USIC2 Channel 0 Shift Clock Input             |

|     | CCU62_CC6<br>0INA | I      | St/B | CCU62 Channel 0 Input                         |

|     | RxDC4E            | I      | St/B | CAN Node 4 Receive Data Input                 |

| 136 | XTAL2             | 0      | Sp/M | Crystal Oscillator Amplifier Output           |

## **Functional Description**

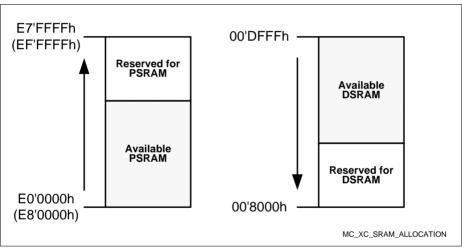

Figure 6 CAPCOM2 Unit Block Diagram

Data Sheet 65 V2.1, 2011-07

## **Functional Description**

## 3.9 Capture/Compare Units CCU6x

The XC228xM types feature the CCU60, CCU61, CCU62 and CCU63 unit(s).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- · Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

## **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

#### **Additional Features**

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

## **Functional Description**

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

## **Functional Description**

#### 3.18 Parallel Ports

The XC228xM provides up to 119 I/O lines which are organized into 11 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 10**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

Table 10 Summary of the XC228xM's Ports

| Port | Width | I/O | Connected Modules                                                            |

|------|-------|-----|------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0),<br>CCU6, USIC, CAN                                               |

| P1   | 8     | I/O | EBC (A15A8),<br>CCU6, USIC                                                   |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13), CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P3   | 8     | I/O | CAN, USIC                                                                    |

| P4   | 8     | I/O | EBC (CS3CS0),<br>CC2, CAN, GPT12E, USIC                                      |

| P5   | 16    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                   |

| P6   | 4     | I/O | ADC, CAN, GPT12E                                                             |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                  |

| P8   | 7     | I/O | CCU6, DAP/JTAG, USIC                                                         |

| P9   | 8     | I/O | CCU6, DAP/JTAG, CAN                                                          |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                 |

| P11  | 6     | I/O | CCU6, USIC, CAN                                                              |

| P15  | 8     | I   | Analog Inputs, GPT12E                                                        |

## **Functional Description**

# 3.20 Instruction Set Summary

Table 11 lists the instructions of the XC228xM.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 11 Instruction Set Summary

| Mnemonic      | Description                                                                                             | Bytes |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|-------|--|--|

| ADD(B)        | Add word (byte) operands                                                                                | 2/4   |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                                     | 2/4   |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                           | 2/4   |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                                | 2/4   |  |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                             | 2     |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                               | 2     |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                               | 2     |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                       | 2     |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                           | 2     |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                       |       |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                        | 2/4   |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                              | 2/4   |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                                    | 2     |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                                 |       |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                                   | 4     |  |  |

| BCMP          | Compare direct bit to direct bit                                                                        | 4     |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data           | 4     |  |  |

| CMP(B)        | Compare word (byte) operands                                                                            | 2/4   |  |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                       |       |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                       |       |  |  |

| PRIOR         | PRIOR Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR |       |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                        | 2     |  |  |

#### **Electrical Parameters**

Table 14 DC Characteristics for Upper Voltage Range (cont'd)

| Parameter                        | Symbol     |      | Values |      | Unit | Note /                      |

|----------------------------------|------------|------|--------|------|------|-----------------------------|

|                                  |            | Min. | Тур.   | Max. |      | Test Condition              |

| Output Low Voltage <sup>8)</sup> | $V_{OL}CC$ | -    | _      | 1.0  | V    | $I_{OL} \leq I_{OLmax}$     |

|                                  |            | _    | _      | 0.4  | V    | $I_{OL} \le I_{OLnom}^{9)}$ |

- 1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

- 2) Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing  $(V_{\rm IN} < V_{\rm SS})$  or supply ripple  $(V_{\rm IN} > V_{\rm DDP})$ , a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current  $(I_{\rm INJ})$  will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CIV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (T<sub>J</sub> = junction temperature [°C]): I<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ->)</sup> [μΑ]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 μA. Leakage derating depending on voltage level (DV = V<sub>DDP</sub> · V<sub>PIN</sub> [V]): I<sub>OZ</sub> = I<sub>OZtempmax</sub> (1.6 x DV) (μA]. This voltage derating formula is an approximation which applies for maximum temperature.

- 5) Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> ≤ V<sub>II max</sub> for a pullup; V<sub>PIN</sub> ≥ V<sub>II+min</sub> for a pulldown.

- 6) These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

- 7) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> ≥ V<sub>IHmin</sub> for a pullup; V<sub>PIN</sub> ≤ V<sub>ILmax</sub> for a pulldown.

- 8) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 9) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{\rm OL}$ -> $V_{\rm SS}$ ,  $V_{\rm OH}$ -> $V_{\rm DDP}$ ). However, only the levels for nominal output currents are verified.

Data Sheet 92 V2.1, 2011-07

## **Electrical Parameters**

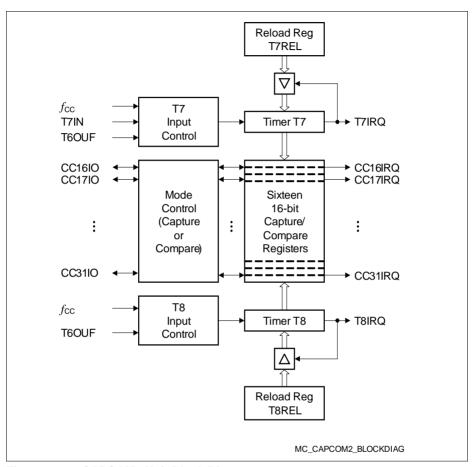

Figure 14 Supply Current in Active Mode as a Function of Frequency

Note: Operating Conditions apply.

#### **Electrical Parameters**

Sample time and conversion time of the XC228xM's A/D converters are programmable. The timing above can be calculated using **Table 19**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

Table 19 A/D Converter Computation Table

| GLOBCTR.5-0<br>(DIVA) | A/D Converter Analog Clock $f_{\mathrm{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup> |

|-----------------------|------------------------------------------------|---------------------|---------------------------|

| 000000 <sub>B</sub>   | $f_{	extsf{SYS}}$                              | 00 <sub>H</sub>     | $t_{ADCI} \times 2$       |

| 000001 <sub>B</sub>   | $f_{\rm SYS}$ / 2                              | 01 <sub>H</sub>     | $t_{ADCI} \times 3$       |

| 000010 <sub>B</sub>   | $f_{\rm SYS}$ / 3                              | 02 <sub>H</sub>     | $t_{ADCI} \times 4$       |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                       | :                   | $t_{ADCI} \times (STC+2)$ |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                          | FE <sub>H</sub>     | $t_{ADCI} \times 256$     |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                          | FF <sub>H</sub>     | $t_{ADCI} \times 257$     |

<sup>1)</sup> The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

## **Converter Timing Example A:**

Assumptions:  $f_{SYS} = 80 \text{ MHz}$  (i.e.  $t_{SYS} = 12.5 \text{ ns}$ ), DIVA =  $03_H$ , STC =  $00_H$

Analog clock  $f_{ADCI} = f_{SYS} / 4 = 20 \text{ MHz}$ , i.e.  $t_{ADCI} = 50 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 2 = 100 \text{ ns}$

Conversion 10-bit:

$t_{\text{C10}} = 13 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 13 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.675 \text{ }\mu\text{s}$

Conversion 8-bit:

$t_{\text{C8}} = 11 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 11 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.575 \text{ }\mu\text{s}$

## Converter Timing Example B:

Assumptions:  $f_{SYS} = 40 \text{ MHz}$  (i.e.  $t_{SYS} = 25 \text{ ns}$ ), DIVA =  $02_H$ , STC =  $03_H$

Analog clock  $f_{ADCI} = f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e.  $t_{ADCI} = 75 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 5 = 375 \text{ ns}$

Conversion 10-bit:

$t_{\rm C10} = 16 \times t_{\rm ADCI} + 2 \times t_{\rm SYS} = 16 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.25 \text{ }\mu\text{s}$

Conversion 8-bit:

$t_{\text{C8}} = 14 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 14 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.10 \text{ }\mu\text{s}$

Data Sheet 103 V2.1, 2011-07

#### **Electrical Parameters**

# 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC228xM into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 20 Various System Parameters

| Parameter                                                             | Symbol                 | Values                                |          |                                             | Unit | Note /                            |  |

|-----------------------------------------------------------------------|------------------------|---------------------------------------|----------|---------------------------------------------|------|-----------------------------------|--|

|                                                                       |                        | Min. Typ.                             |          | Max.                                        |      | <b>Test Condition</b>             |  |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | $\Delta f_{INT}$ CC    | -1                                    | _        | 1                                           | %    | <i>∆T</i> <sub>J</sub> ≤ 10 °C    |  |

| Internal clock source frequency                                       | $f_{INT}CC$            | 4.8                                   | 5.0      | 5.2                                         | MHz  |                                   |  |

| Wakeup clock source                                                   | f <sub>wu</sub> CC     | 400                                   | _        | 700                                         | kHz  | FREQSEL= 00                       |  |

| frequency <sup>2)</sup>                                               |                        | 210                                   | _        | 390                                         | kHz  | FREQSEL= 01                       |  |

|                                                                       |                        | 140                                   | _        | 260                                         | kHz  | FREQSEL= 10                       |  |

|                                                                       |                        | 110                                   | _        | 200                                         | kHz  | FREQSEL= 11                       |  |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.8                                   | 2.2      | 2.7                                         | ms   | $f_{\rm WU}$ = 500 kHz            |  |

| Startup time from standby mode with code execution from Flash         | t <sub>SSB</sub> CC    | 2.9                                   | 3.9      | 4.6                                         | ms   | $f_{\rm WU}$ = 140 kHz            |  |

|                                                                       |                        | 1.8                                   | 2.2      | 2.8                                         | ms   | $f_{\rm WU}$ = 500 kHz            |  |

| Startup time from stopover mode with code execution from PSRAM        | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup> | -        | 12 /<br>f <sub>WU</sub> <sup>3)</sup>       | μS   |                                   |  |

| Core voltage (PVC) supervision level                                  | $V_{PVC}CC$            | V <sub>LV</sub> - 0.03                | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.07 <sub>4)</sub> | V    | 5)                                |  |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub> - 0.10 <sup>6)</sup>  | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.15               | V    | Lower voltage range <sup>5)</sup> |  |

|                                                                       |                        | V <sub>LV</sub> - 0.15                | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.15               | V    | Upper voltage range <sup>5)</sup> |  |

#### **Electrical Parameters**

## PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

Table 24 System PLL Parameters

| Parameter            | Symbol              |      | Values | 5    | Unit | Note /                   |

|----------------------|---------------------|------|--------|------|------|--------------------------|

|                      |                     | Min. | Тур.   | Max. |      | Test Condition           |

| VCO output frequency | $f_{\text{VCO}}$ CC | 50   | _      | 110  | MHz  | VCOSEL = 00 <sub>B</sub> |

| (VCO controlled)     |                     | 100  | _      | 160  | MHz  | VCOSEL = 01 <sub>B</sub> |

| VCO output frequency | $f_{\sf VCO}$ CC    | 10   | _      | 40   | MHz  | VCOSEL = 00 <sub>B</sub> |

| (VCO free-running)   |                     | 20   | _      | 80   | MHz  | VCOSEL = 01 <sub>B</sub> |

## 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$$f_{SYS} = f_{WU}$$

.

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

# 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

#### **Electrical Parameters**

Table 31 EBC External Bus Timing for Lower Voltage Range

| Parameter                                                                                   | Symbol                    | Values |      |      | Unit | Note /         |

|---------------------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                             |                           | Min.   | Тур. | Max. |      | Test Condition |

| Output valid delay for RD, WR(L/H)                                                          | t <sub>10</sub> CC        | _      | 11   | 20   | ns   |                |

| Output valid delay for BHE, ALE                                                             | <i>t</i> <sub>11</sub> CC | _      | 10   | 21   | ns   |                |

| Address output valid delay for A23 A0                                                       | t <sub>12</sub> CC        | _      | 11   | 22   | ns   |                |

| Address output valid delay for AD15 AD0 (MUX mode)                                          | t <sub>13</sub> CC        | _      | 10   | 22   | ns   |                |

| Output valid delay for CS                                                                   | t <sub>14</sub> CC        | _      | 10   | 13   | ns   |                |

| Data output valid delay for AD15 AD0 (write data, MUX mode)                                 | t <sub>15</sub> CC        | -      | 10   | 22   | ns   |                |

| Data output valid delay for D15 D0 (write data, DEMUX mode)                                 | t <sub>16</sub> CC        | -      | 10   | 22   | ns   |                |

| Output hold time for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>20</sub> CC        | -2     | 8    | 10   | ns   |                |

| Output hold time for BHE, ALE                                                               | t <sub>21</sub> CC        | -2     | 8    | 10   | ns   |                |

| Address output hold time for AD15 AD0                                                       | t <sub>23</sub> CC        | -3     | 8    | 10   | ns   |                |

| Output hold time for CS                                                                     | t <sub>24</sub> CC        | -3     | 8    | 11   | ns   |                |

| Data output hold time for D15 D0 and AD15 AD0                                               | t <sub>25</sub> CC        | -3     | 8    | 10   | ns   |                |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                          | t <sub>30</sub> SR        | 29     | 17   | -    | ns   |                |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                                    | <i>t</i> <sub>31</sub> SR | 0      | -9   | -    | ns   |                |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge

of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can

change after the rising edge of RD.

#### **Electrical Parameters**

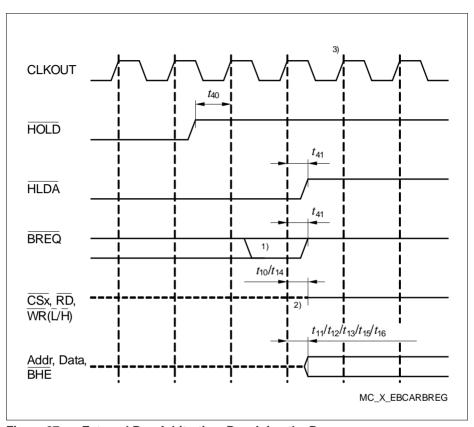

Figure 27 External Bus Arbitration, Regaining the Bus

#### **Notes**

- 1. This is the last chance for BREQ to trigger the indicated regain sequence.

Even if BREQ is activated earlier, the regain sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the XC228xM requesting the bus.

- The control outputs will be resistive high (pull-up) before being driven inactive (ALE will be low).

- 3. The next XC228xM-driven bus cycle may start here.

#### **Electrical Parameters**

Table 37 USIC SSC Slave Mode Timing for Lower Voltage Range

| Parameter                                                                   | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                             |                           | Min.   | Тур. | Max. |      | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup> | t <sub>10</sub> SR        | 7      | _    | _    | ns   |                |

| Select input DX2 hold after last clock input DX1 receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup time to shift clock receive edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | _    | _    | ns   |                |

| Data input DX0 hold time from clock input DX1 receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                 | t <sub>14</sub> CC        | 8      | _    | 41   | ns   |                |

<sup>1)</sup> These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

Data Sheet 134 V2.1, 2011-07

#### **Electrical Parameters**

## **Debug via JTAG**

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_i$  = 20 pF.

Table 40 JTAG Interface Timing for Upper Voltage Range

| Parameter                                                                | Symbol             | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|--------------------|------------------|------|------|------|----------------|

|                                                                          |                    | Min.             | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR  | 50 <sup>1)</sup> | _    | _    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR  | 16               | _    | _    | ns   |                |

| TCK low time                                                             | $t_3$ SR           | 16               | _    | _    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR  | _                | _    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR  | _                | _    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR  | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR  | 6                | _    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC  | _                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC  | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | t <sub>10</sub> CC | _                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | t <sub>18</sub> CC | 5                | _    | _    | ns   |                |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

<sup>2)</sup> Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

<sup>3)</sup> The falling edge on TCK is used to generate the TDO timing.

<sup>4)</sup> The setup time for TDO is given implicitly by the TCK cycle time.