Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                        |

| Number of LABs/CLBs            | 18625                                                                           |

| Number of Logic Elements/Cells | 149000                                                                          |

| Total RAM Bits                 | 7014400                                                                         |

| Number of I/O                  | 380                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                              |

| Package / Case                 | 672-BBGA                                                                        |

| Supplier Device Package        | 672-FPBGA (27x27)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-150ea-7fn672itw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

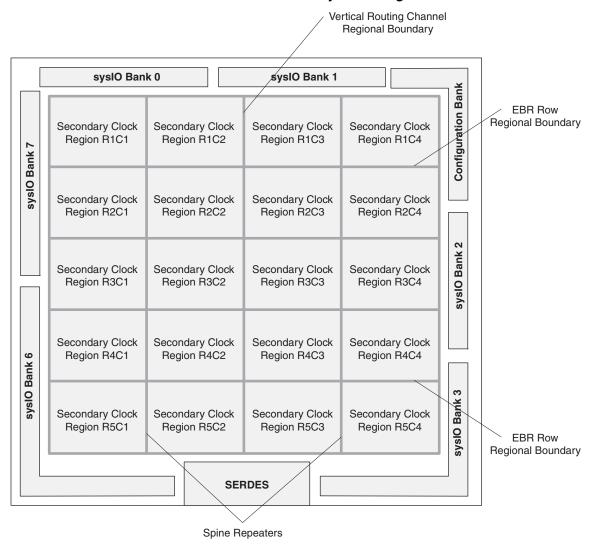

Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Figure 2-15. LatticeECP3-70 and LatticeECP3-95 Secondary Clock Regions

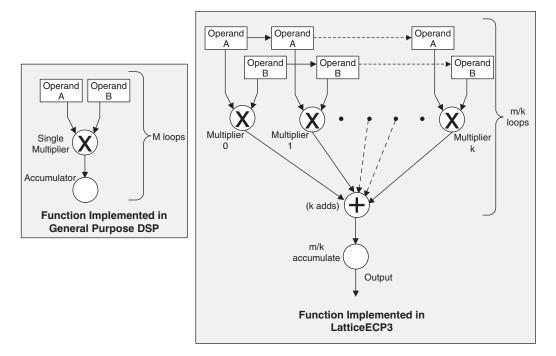

This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-23 compares the fully serial implementation to the mixed parallel and serial implementation.

Figure 2-23. Comparison of General DSP and LatticeECP3 Approaches

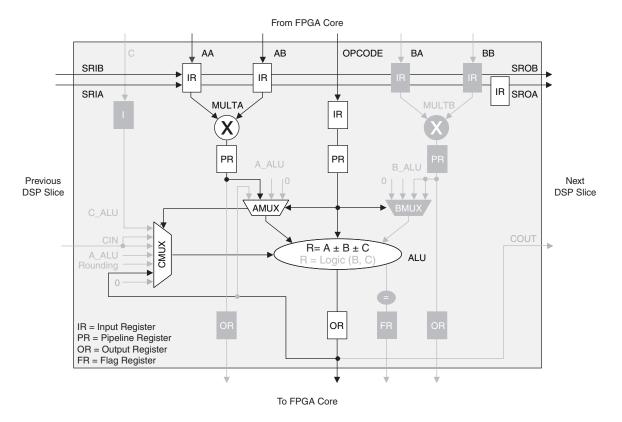

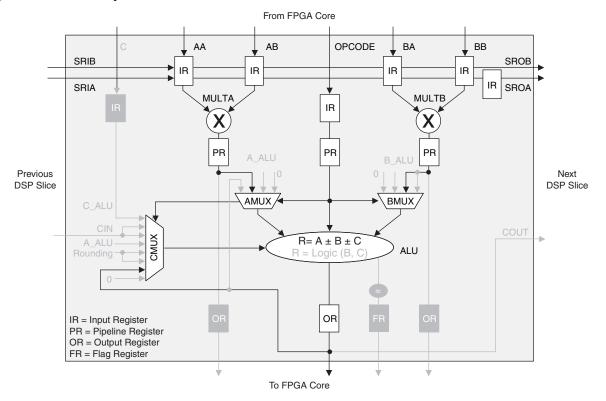

## LatticeECP3 sysDSP Slice Architecture Features

The LatticeECP3 sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The LatticeECP3 sysDSP Slice supports many functions that include the following:

- Multiply (one 18 x 36, two 18 x 18 or four 9 x 9 Multiplies per Slice)

- Multiply (36 x 36 by cascading across two sysDSP slices)

- Multiply Accumulate (up to 18 x 36 Multipliers feeding an Accumulator that can have up to 54-bit resolution)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18 x 18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such

#### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

#### **MMAC DSP Element**

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

Figure 2-28. MMAC sysDSP Element

#### **ALU Flags**

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- Equal to one with mask (EQOM)

- · Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- · Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

#### **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

#### Resources Available in the LatticeECP3 Family

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

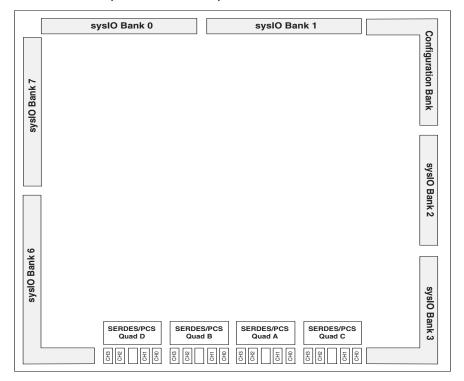

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                     | Data Rate<br>(Mbps)                                             | Number of<br>General/Link Width | Encoding Style |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------|

| PCI Express 1.1                                                              | 2500                                                            | x1, x2, x4                      | 8b10b          |

| Gigabit Ethernet                                                             | 1250, 2500                                                      | x1                              | 8b10b          |

| SGMII                                                                        | 1250                                                            | x1                              | 8b10b          |

| XAUI                                                                         | 3125                                                            | x4                              | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                                          | x1, x4                          | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | x1                              | 8b10b          |

| SD-SDI<br>(259M, 344M)                                                       | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | x1                              | NRZI/Scrambled |

| HD-SDI<br>(292M)                                                             | 1483.5,<br>1485                                                 | x1                              | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                             | 2967,<br>2970                                                   | x1                              | NRZI/Scrambled |

| SONET-STS-3 <sup>2</sup>                                                     | 155.52                                                          | x1                              | N/A            |

| SONET-STS-12 <sup>2</sup>                                                    | 622.08                                                          | x1                              | N/A            |

| SONET-STS-48 <sup>2</sup>                                                    | 2488                                                            | x1                              | N/A            |

<sup>1.</sup> For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

<sup>2.</sup> The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

## **DC Electrical Characteristics**

| Symbol                                            | Parameter                                | Condition                                                                                                                                                   | Min.           | Тур. | Max.                  | Units |

|---------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2 \text{ V})$                                                                                                               | _              | _    | 10                    | μΑ    |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                | $(V_{CCIO} - 0.2 \text{ V}) < V_{IN} \le 3.6 \text{ V}$                                                                                                     | _              | _    | 150                   | μΑ    |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                                                                                             | -30            | _    | -210                  | μΑ    |

| $I_{PD}$                                          | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{CCIO}$                                                                                                                      | 30             | _    | 210                   | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                     | 30             | _    | _                     | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                                     | -30            | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | _              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | _              | _    | -210                  | μΑ    |

| $V_{BHT}$                                         | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                                                                                             | $V_{IL}$ (MAX) | _    | V <sub>IH</sub> (MIN) | >     |

| C1                                                | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _              | 5    | 8                     | pf    |

| C2                                                | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _              | 5    | 7                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup>  $T_A$  25 °C, f = 1.0 MHz.

Applicable to general purpose I/Os in top and bottom banks.

When used as V<sub>REF</sub> maximum leakage= 25 μA.

# SERDES Power Supply Requirements<sup>1, 2, 3</sup>

| Symbol               | Description                            | Тур. | Max. | Units |

|----------------------|----------------------------------------|------|------|-------|

| Standby (Power I     | Down)                                  |      | •    | •     |

| I <sub>CCA-SB</sub>  | V <sub>CCA</sub> current (per channel) | 3    | 5    | mA    |

| I <sub>CCIB-SB</sub> | Input buffer current (per channel)     | _    | _    | mA    |

| I <sub>CCOB-SB</sub> | Output buffer current (per channel)    | _    | _    | mA    |

| Operating (Data I    | Rate = 3.2 Gbps)                       |      | •    | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 68   | 77   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 5    | 7    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 19   | 25   | mA    |

| Operating (Data I    | Rate = 2.5 Gbps)                       |      | •    | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 66   | 76   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA    |

| Operating (Data I    | Rate = 1.25 Gbps)                      |      |      |       |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 62   | 72   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA    |

| Operating (Data I    | Rate = 250 Mbps)                       |      | •    | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 14   | 17   | mA    |

| Operating (Data I    | Rate = 150 Mbps)                       | •    | •    | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| І <sub>ССОВ-ОР</sub> | Output buffer current (per channel)    | 14   | 17   | mA    |

<sup>1.</sup> Equalization enabled, pre-emphasis disabled.

<sup>2.</sup> One quarter of the total quad power (includes contribution from common circuits, all channels in the quad operating, pre-emphasis disabled, equalization enabled).

<sup>3.</sup> Pre-emphasis adds 20 mA to ICCA-OP data.

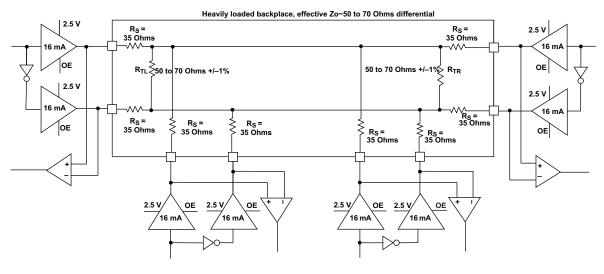

#### MLVDS25

The LatticeECP3 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Figure 3-5. MLVDS25 (Multipoint Low Voltage Differential Signaling)

Table 3-5. MLVDS25 DC Conditions1

|                   |                                  | Тур            | ical           |       |

|-------------------|----------------------------------|----------------|----------------|-------|

| Parameter         | Description                      | <b>Zo=50</b> Ω | <b>Zo=70</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%) | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)     | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 0.98           | 0.90           | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                | 21.74          | 20.00          | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

## **Over Recommended Commercial Operating Conditions**

|                       |                                 |                                         | _        | -8                   | -       | -7 -6                 |        | -6   |          |

|-----------------------|---------------------------------|-----------------------------------------|----------|----------------------|---------|-----------------------|--------|------|----------|

| Parameter             | Description                     | Device                                  | Min.     | Max.                 | Min.    | Max.                  | Min.   | Max. | Units    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA                          | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-35EA                               | 683      | _                    | 688     | _                     | 690    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-35EA                               | 683      | _                    | 688     | _                     | 690    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                               | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-17EA                               | 683      | _                    | 688     | _                     | 690    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                               | 683      | _                    | 688     | _                     | 690    | _    | ps       |

| f <sub>MAX GDDR</sub> | DDRX1 Clock Frequency           | ECP3-17EA                               | _        | 250                  | -       | 250                   | _      | 250  | MHz      |

| Generic DDRX1 O       | utput with Clock and Data Aligi | ned at Pin (GDDRX1_TX.                  | SCLK.Ali | igned) <sup>10</sup> | l       |                       | l      | l    | 1        |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | ECP3-150EA                              | _        | 335                  | _       | 338                   | _      | 341  | ps       |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-150EA                              | _        | 335                  | _       | 338                   | _      | 341  | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                              | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | ECP3-70EA/95EA                          | _        | 339                  | _       | 343                   | _      | 347  | ps       |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-70EA/95EA                          | _        | 339                  | _       | 343                   | _      | 347  | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA                          | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | ECP3-35EA                               | _        | 322                  | _       | 320                   | _      | 321  | ps       |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-35EA                               | _        | 322                  | _       | 320                   | _      | 321  | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                               | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | ECP3-17EA                               | _        | 322                  | _       | 320                   | _      | 321  | ps       |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-17EA                               | _        | 322                  | _       | 320                   | _      | 321  | ps       |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                               | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

|                       | output with Clock and Data (<10 | Bits Wide) Centered at I                | Pin (GDD | RX1 TX.              | DQS.Cer | ntered) <sup>10</sup> |        |      |          |

| Left and Right Sig    |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |          |                      |         | ,                     |        |      |          |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-150EA                              | 670      | I —                  | 670     | _                     | 670    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-150EA                              | 670      | _                    | 670     | _                     | 670    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                              | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-70EA/95EA                          | 657      | _                    | 652     | _                     | 650    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-70EA/95EA                          | 657      | _                    | 652     | _                     | 650    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA                          | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-35EA                               | 670      | _                    | 675     | _                     | 676    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-35EA                               | 670      | _                    | 675     | _                     | 676    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                               | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-17EA                               | 670      | _                    | 670     | _                     | 670    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                               | 670      | _                    | 670     | _                     | 670    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-17EA                               | _        | 250                  | _       | 250                   | _      | 250  | MHz      |

|                       | output with Clock and Data (>10 | Bits Wide) Aligned at Pi                | n (GDDR  | X2_TX.A              | ligned) | l                     | I      |      | <u> </u> |

| Left and Right Sic    | les                             | <u> </u>                                |          |                      |         |                       |        |      |          |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | All ECP3EA Devices                      | _        | 200                  | _       | 210                   | _      | 220  | ps       |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | All ECP3EA Devices                      | _        | 200                  | _       | 210                   | _      | 220  | ps       |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices                      | _        | 500                  | _       | 420                   | _      | 375  | MHz      |

|                       | output with Clock and Data (>10 |                                         |          |                      | L (GDDF |                       | QSDLL. |      |          |

| Left and Right Sic    | <u> </u>                        | ,                                       |          | -                    | `       |                       |        |      |          |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | All ECP3EA Devices                      | 400      | _                    | 400     | _                     | 431    | _    | ps       |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | All ECP3EA Devices                      |          | _                    | 400     | _                     | 432    | _    | ps       |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices                      |          | 400                  | _       | 400                   | _      | 375  | MHz      |

| INIAV_GDDU            |                                 | 1 = 5 : 52, : 2 5 : 1000                | l        |                      |         |                       | L      |      |          |

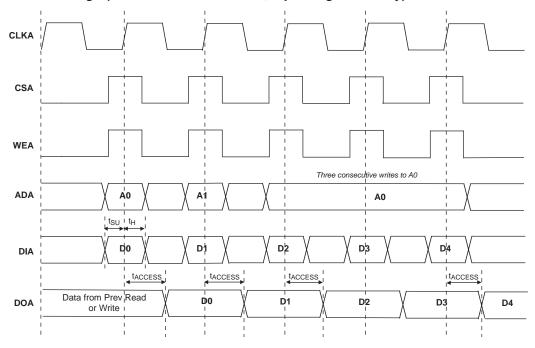

Figure 3-11. Write Through (SP Read/Write on Port A, Input Registers Only)

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup> (Continued)

#### **Over Recommended Commercial Operating Conditions**

| Buffer Type   | Description                            | -8    | -7    | -6    | Units |

|---------------|----------------------------------------|-------|-------|-------|-------|

| LVCMOS15_4mA  | LVCMOS 1.5 4 mA drive, fast slew rate  | 0.21  | 0.25  | 0.29  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8 mA drive, fast slew rate  | 0.05  | 0.07  | 0.09  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2 mA drive, fast slew rate  | 0.43  | 0.51  | 0.59  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6 mA drive, fast slew rate  | 0.23  | 0.28  | 0.33  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4 mA drive, slow slew rate  | 1.44  | 1.58  | 1.72  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8 mA drive, slow slew rate  | 0.98  | 1.10  | 1.22  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12 mA drive, slow slew rate | 0.67  | 0.77  | 0.86  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16 mA drive, slow slew rate | 0.97  | 1.09  | 1.21  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20 mA drive, slow slew rate | 0.67  | 0.76  | 0.85  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4 mA drive, slow slew rate  | 1.48  | 1.63  | 1.78  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8 mA drive, slow slew rate  | 1.02  | 1.14  | 1.27  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12 mA drive, slow slew rate | 0.74  | 0.84  | 0.94  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16 mA drive, slow slew rate | 1.02  | 1.14  | 1.26  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20 mA drive, slow slew rate | 0.74  | 0.83  | 0.93  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4 mA drive, slow slew rate  | 1.60  | 1.77  | 1.93  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8 mA drive, slow slew rate  | 1.11  | 1.25  | 1.38  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12 mA drive, slow slew rate | 0.87  | 0.98  | 1.09  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16 mA drive, slow slew rate | 0.86  | 0.97  | 1.07  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4 mA drive, slow slew rate  | 1.71  | 1.89  | 2.08  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8 mA drive, slow slew rate  | 1.20  | 1.34  | 1.48  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2 mA drive, slow slew rate  | 1.37  | 1.56  | 1.74  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6 mA drive, slow slew rate  | 1.11  | 1.27  | 1.43  | ns    |

| PCI33         | PCI, VCCIO = 3.3 V                     | -0.12 | -0.13 | -0.14 | ns    |

<sup>1.</sup> Timing adders are characterized but not tested on every device.

<sup>2.</sup> LVCMOS timing measured with the load specified in Switching Test Condition table.

<sup>3.</sup> All other standards tested according to the appropriate specifications.

<sup>4.</sup> Not all I/O standards and drive strengths are supported for all banks. See the Architecture section of this data sheet for details.

<sup>5.</sup> Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

<sup>6.</sup> This data does not apply to the LatticeECP3-17EA device.

<sup>7.</sup> For details on –9 speed grade devices, please contact your Lattice Sales Representative.

# LatticeECP3 Maximum I/O Buffer Speed $^{1, 2, 3, 4, 5, 6}$

| Buffer                                | Description                                    | Max.     | Units |

|---------------------------------------|------------------------------------------------|----------|-------|

| Maximum Input Frequency               |                                                | <b> </b> | I     |

| LVDS25                                | LVDS, V <sub>CCIO</sub> = 2.5 V                | 400      | MHz   |

| MLVDS25                               | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 400      | MHz   |

| BLVDS25                               | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 400      | MHz   |

| PPLVDS                                | Point-to-Point LVDS                            | 400      | MHz   |

| TRLVDS                                | Transition-Reduced LVDS                        | 612      | MHz   |

| Mini LVDS                             | Mini LVDS                                      | 400      | MHz   |

| LVPECL33                              | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V    | 400      | MHz   |

| HSTL18 (all supported classes)        | HSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 400      | MHz   |

| HSTL15                                | HSTL_15 class I, V <sub>CCIO</sub> = 1.5 V     | 400      | MHz   |

| SSTL33 (all supported classes)        | SSTL_3 class I, II, V <sub>CCIO</sub> = 3.3 V  | 400      | MHz   |

| SSTL25 (all supported classes)        | SSTL_2 class I, II, V <sub>CCIO</sub> = 2.5 V  | 400      | MHz   |

| SSTL18 (all supported classes)        | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 400      | MHz   |

| LVTTL33                               | LVTTL, V <sub>CCIO</sub> = 3.3 V               | 166      | MHz   |

| LVCMOS33                              | LVCMOS, V <sub>CCIO</sub> = 3.3 V              | 166      | MHz   |

| LVCMOS25                              | LVCMOS, V <sub>CCIO</sub> = 2.5 V              | 166      | MHz   |

| LVCMOS18                              | LVCMOS, V <sub>CCIO</sub> = 1.8 V              | 166      | MHz   |

| LVCMOS15                              | LVCMOS 1.5, V <sub>CCIO</sub> = 1.5 V          | 166      | MHz   |

| LVCMOS12                              | LVCMOS 1.2, V <sub>CCIO</sub> = 1.2 V          | 166      | MHz   |

| PCI33                                 | PCI, V <sub>CCIO</sub> = 3.3 V                 | 66       | MHz   |

| Maximum Output Frequency              |                                                | •        | •     |

| LVDS25E                               | LVDS, Emulated, V <sub>CCIO</sub> = 2.5 V      | 300      | MHz   |

| LVDS25                                | LVDS, V <sub>CCIO</sub> = 2.5 V                | 612      | MHz   |

| MLVDS25                               | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 300      | MHz   |

| RSDS25                                | RSDS, Emulated, V <sub>CCIO</sub> = 2.5 V      | 612      | MHz   |

| BLVDS25                               | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 300      | MHz   |

| PPLVDS                                | Point-to-point LVDS                            | 612      | MHz   |

| LVPECL33                              | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V    | 612      | MHz   |

| Mini-LVDS                             | Mini LVDS                                      | 612      | MHz   |

| HSTL18 (all supported classes)        | HSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 200      | MHz   |

| HSTL15 (all supported classes)        | HSTL_15 class I, V <sub>CCIO</sub> = 1.5 V     | 200      | MHz   |

| SSTL33 (all supported classes)        | SSTL_3 class I, II, V <sub>CCIO</sub> = 3.3 V  | 233      | MHz   |

| SSTL25 (all supported classes)        | SSTL_2 class I, II, V <sub>CCIO</sub> = 2.5 V  | 233      | MHz   |

| SSTL18 (all supported classes)        | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 266      | MHz   |

| LVTTL33                               | LVTTL, V <sub>CCIO</sub> = 3.3 V               | 166      | MHz   |

| LVCMOS33 (For all drives)             | LVCMOS, 3.3 V                                  | 166      | MHz   |

| LVCMOS25 (For all drives)             | LVCMOS, 2.5 V                                  | 166      | MHz   |

| LVCMOS18 (For all drives)             | LVCMOS, 1.8 V                                  | 166      | MHz   |

| LVCMOS15 (For all drives)             | LVCMOS, 1.5 V                                  | 166      | MHz   |

| LVCMOS12 (For all drives except 2 mA) | LVCMOS, V <sub>CCIO</sub> = 1.2 V              | 166      | MHz   |

| LVCMOS12 (2 mA drive)                 | LVCMOS, V <sub>CCIO</sub> = 1.2 V              | 100      | MHz   |

|                                       | •                                              |          |       |

# **DLL Timing**

| Parameter                       | Description                                                                                              | Condition               | Min. | Тур. | Max.   | Units  |

|---------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------|------|--------|--------|

| f <sub>REF</sub>                | Input reference clock frequency (on-chip or off-chip)                                                    |                         | 133  | _    | 500    | MHz    |

| f <sub>FB</sub>                 | Feedback clock frequency (on-chip or off-chip)                                                           |                         | 133  | _    | 500    | MHz    |

| f <sub>CLKOP</sub> 1            | Output clock frequency, CLKOP                                                                            |                         | 133  | _    | 500    | MHz    |

| f <sub>CLKOS</sub> <sup>2</sup> | Output clock frequency, CLKOS                                                                            |                         | 33.3 | _    | 500    | MHz    |

| t <sub>PJIT</sub>               | Output clock period jitter (clean input)                                                                 |                         |      | _    | 200    | ps p-p |

|                                 | Output clock duty cycle (at 50% levels, 50% duty                                                         | Edge Clock              | 40   |      | 60     | %      |

| <sup>t</sup> DUTY               | cycle input clock, 50% duty cycle circuit turned off, time reference delay mode)                         | Primary Clock           | 30   |      | 70     | %      |

|                                 | Output clock duty cycle (at 50% levels, arbitrary                                                        | Primary Clock < 250 MHz | 45   |      | 55     | %      |

| t <sub>DUTYTRD</sub>            | duty cycle input clock, 50% duty cycle circuit                                                           | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                 | enabled, time reference delay mode)                                                                      | Edge Clock              | 45   |      | 55     | %      |

|                                 | Output clock duty cycle (at 50% levels, arbitrary                                                        | Primary Clock < 250 MHz | 40   |      | 60     | %      |

| t <sub>DUTYCIR</sub>            | duty cycle input clock, 50% duty cycle circuit enabled, clock injection removal mode) with DLL cascading | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                 |                                                                                                          | Edge Clock              | 45   |      | 55     | %      |

| t <sub>SKEW</sub> 3             | Output clock to clock skew between two outputs with the same phase setting                               |                         | _    | _    | 100    | ps     |

| t <sub>PHASE</sub>              | Phase error measured at device pads between off-chip reference clock and feedback clocks                 |                         | _    | _    | +/-400 | ps     |

| t <sub>PWH</sub>                | Input clock minimum pulse width high (at 80% level)                                                      |                         | 550  | _    | _      | ps     |

| t <sub>PWL</sub>                | Input clock minimum pulse width low (at 20% level)                                                       |                         | 550  | _    | _      | ps     |

| t <sub>INSTB</sub>              | Input clock period jitter                                                                                |                         | _    | _    | 500    | ps     |

| t <sub>LOCK</sub>               | DLL lock time                                                                                            |                         | 8    | _    | 8200   | cycles |

| t <sub>RSWD</sub>               | Digital reset minimum pulse width (at 80% level)                                                         |                         | 3    | _    | _      | ns     |

| t <sub>DEL</sub>                | Delay step size                                                                                          |                         | 27   | 45   | 70     | ps     |

| t <sub>RANGE1</sub>             | Max. delay setting for single delay block (64 taps)                                                      |                         | 1.9  | 3.1  | 4.4    | ns     |

| t <sub>RANGE4</sub>             | Max. delay setting for four chained delay blocks                                                         |                         | 7.6  | 12.4 | 17.6   | ns     |

<sup>1.</sup> CLKOP runs at the same frequency as the input clock.

<sup>2.</sup> CLKOS minimum frequency is obtained with divide by 4.

<sup>3.</sup> This is intended to be a "path-matching" design guideline and is not a measurable specification.

## **SERDES High Speed Data Receiver**

Table 3-9. Serial Input Data Specifications

| Symbol                 | Description                                                                                        | Min.    | Тур.      | Max.                               | Units   |      |  |

|------------------------|----------------------------------------------------------------------------------------------------|---------|-----------|------------------------------------|---------|------|--|

| RX-CID <sub>S</sub>    |                                                                                                    | 3.125 G | _         | _                                  | 136     | Bits |  |

|                        | Stream of nontransitions <sup>1</sup> (CID = Consecutive Identical Digits) @ 10 <sup>-12</sup> BER | 2.5 G   | _         | _                                  | 144     |      |  |

|                        |                                                                                                    | 1.485 G | _         | _                                  | 160     |      |  |

|                        |                                                                                                    | 622 M   | _         | _                                  | 204     | Dits |  |

|                        |                                                                                                    | 270 M   | _         | _                                  | 228     |      |  |

|                        |                                                                                                    | 150 M   | _         | _                                  | 296     |      |  |

| V <sub>RX-DIFF-S</sub> | Differential input sensitivity                                                                     | 150     | _         | 1760                               | mV, p-p |      |  |

| $V_{RX-IN}$            | Input levels                                                                                       | 0       | _         | V <sub>CCA</sub> +0.5 <sup>4</sup> | V       |      |  |

| V <sub>RX-CM-DC</sub>  | Input common mode range (DC coupled)                                                               | 0.6     | _         | $V_{CCA}$                          | V       |      |  |

| V <sub>RX-CM-AC</sub>  | Input common mode range (AC coupled) <sup>3</sup>                                                  | 0.1     | _         | V <sub>CCA</sub> +0.2              | V       |      |  |

| T <sub>RX-RELOCK</sub> | SCDR re-lock time <sup>2</sup>                                                                     | _       | 1000      | _                                  | Bits    |      |  |

| Z <sub>RX-TERM</sub>   | Input termination 50/75 Ohm/High Z                                                                 | -20%    | 50/75/HiZ | +20%                               | Ohms    |      |  |

| RL <sub>RX-RL</sub>    | Return loss (without package)                                                                      | 10      | _         | _                                  | dB      |      |  |

<sup>1.</sup> This is the number of bits allowed without a transition on the incoming data stream when using DC coupling.

#### **Input Data Jitter Tolerance**

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

Table 3-10. Receiver Total Jitter Tolerance Specification

| Description   | Frequency                            | Condition                       | Min. | Тур. | Max. | Units   |

|---------------|--------------------------------------|---------------------------------|------|------|------|---------|

| Deterministic |                                      | 600 mV differential eye         | _    | _    | 0.47 | UI, p-p |

| Random        | 3.125 Gbps                           | 600 mV differential eye         | _    | _    | 0.18 | UI, p-p |

| Total         |                                      | 600 mV differential eye         | _    | _    | 0.65 | UI, p-p |

| Deterministic |                                      | 600 mV differential eye         | _    | _    | 0.47 | UI, p-p |

| Random        | 2.5 Gbps                             | .5 Gbps 600 mV differential eye |      | _    | 0.18 | UI, p-p |

| Total         |                                      | 600 mV differential eye         | _    | _    | 0.65 | UI, p-p |

| Deterministic |                                      | 600 mV differential eye         | _    | _    | 0.47 | UI, p-p |

| Random        | om 1.25 Gbps 600 mV differential eye |                                 | _    | _    | 0.18 | UI, p-p |

| Total         | 7                                    | 600 mV differential eye         | _    | _    | 0.65 | UI, p-p |

| Deterministic |                                      | 600 mV differential eye         | _    | _    | 0.47 | UI, p-p |

| Random        | 622 Mbps                             | 600 mV differential eye         | _    | _    | 0.18 | UI, p-p |

| Total         | 1                                    | 600 mV differential eye         | _    | _    | 0.65 | UI, p-p |

Note: Values are measured with CJPAT, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

<sup>2.</sup> This is the typical number of bit times to re-lock to a new phase or frequency within +/- 300 ppm, assuming 8b10b encoded data.

<sup>3.</sup> AC coupling is used to interface to LVPECL and LVDS. LVDS interfaces are found in laser drivers and Fibre Channel equipment. LVDS interfaces are generally found in 622 Mbps SERDES devices.

<sup>4.</sup> Up to 1.76 V.

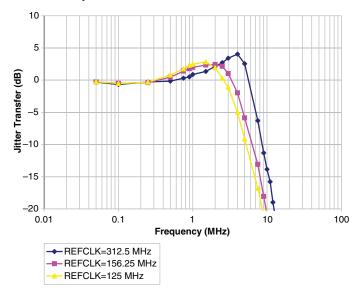

Figure 3-14. Jitter Transfer – 3.125 Gbps

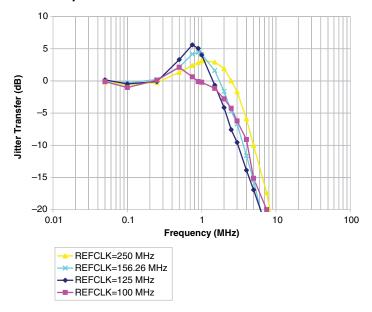

Figure 3-15. Jitter Transfer – 2.5 Gbps

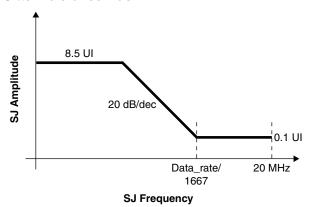

Figure 3-18. XAUI Sinusoidal Jitter Tolerance Mask

Note: The sinusoidal jitter tolerance is measured with at least 0.37 Ulpp of Deterministic jitter (Dj) and the sum of Dj and Rj (random jitter) is at least 0.55 Ulpp. Therefore, the sum of Dj, Rj and Sj (sinusoidal jitter) is at least 0.65 Ulpp (Dj = 0.37, Rj = 0.18, Sj = 0.1).

# **LatticeECP3 sysCONFIG Port Timing Specifications**

| Parameter            | Description                                                                                                                                    | Min.                               | Max. | Units    |            |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|----------|------------|

| POR, Confi           | guration Initialization, and Wakeup                                                                                                            |                                    |      |          |            |

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode                        | _    | 23       | ms         |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode                         | _    | 6        | ms         |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           |                                    | _    | 5        | μs         |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       |                                    | 25   | _        | ns         |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                                    | _    | 10       | ns         |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                                    | _    | 37       | ns         |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       |                                    | _    | 37       | ns         |

| t <sub>DINIT</sub> 1 | PROGRAMN High to INITN High Delay                                                                                                              |                                    | _    | 1        | ms         |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                                    | 100  | 500      | cycles     |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                                    | _    | 300      | ns         |

| t <sub>IODISS</sub>  | User I/O Disable from PROGRAMN Low                                                                                                             |                                    | _    | 100      | ns         |

| t <sub>IOENSS</sub>  | User I/O Enabled Time from CCLK Edge During Wake-up Sequer                                                                                     | nce                                | _    | 100      | ns         |

| All Configu          | ration Modes                                                                                                                                   |                                    |      |          |            |

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                                    | 5    | _        | ns         |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                                    | 1    | _        | ns         |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          | -0.2                               | 12   | ns       |            |

| Slave Seria          | I                                                                                                                                              |                                    |      |          |            |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        | 5                                  | _    | ns       |            |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                    | 5    | _        | ns         |

|                      | CCLIV Francisco                                                                                                                                | Without encryption                 | _    | 33       | MHz        |

| TCCLK                | CCLK Frequency                                                                                                                                 | With encryption                    | _    | 20       | MHz        |

| Master and           | Slave Parallel                                                                                                                                 | •                                  |      |          |            |

| t <sub>SUCS</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                                    | 7    | _        | ns         |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                                    |      | _        | ns         |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                                    |      | _        | ns         |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                                    |      | _        | ns         |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                                    |      | 12       | ns         |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      | _                                  | 12   | ns       |            |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        | 6                                  | _    | ns       |            |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                    |      | _        | ns         |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                                    |      | _        | ns         |

| f <sub>CCLK</sub>    | CCLK/MCLK Frequency                                                                                                                            | Without encryption With encryption | _    | 33<br>20 | MHz<br>MHz |

| Master and           | L<br>Slave SPI                                                                                                                                 |                                    |      |          |            |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                                    |      | 80       | ns         |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       | 0.2                                | 2    | μs       |            |

| t <sub>SOCDO</sub>   | MCLK Low to Output Valid                                                                                                                       |                                    |      | 15       | ns         |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  |                                    |      |          | μs         |

|                      |                                                                                                                                                | Without encryption                 | 0.3  | 33       | MHz        |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption                    |      | 20       | MHz        |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                    | 5    | _        | ns         |

# LatticeECP3 Family Data Sheet Pinout Information

March 2015 Data Sheet DS1021

# **Signal Descriptions**

| Signal Name                                | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| General Purpose                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                            | edge designations are L (Left), B (Bottom), R (Right), T (Top)  [Row/Column Number] indicates the PFU row or the column of which the PIC exists. When Edge is T (Top) or B (Bottom), on ify Column Number. When Edge is L (Left) or R (Right), only is Row Number.  I/O  [A/B] indicates the PIO within the PIC to which the pad is consistent these user-programmable pins are shared with special function pins, when not used as special purpose pins, can be programmable logic. During configuration the user-programmable I/Os with an internal pull-up resistor enabled. If any pin is not used to a package pin), it is also tri-stated with an internal pull-up rafter configuration. | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Diff data I [Data/Oakussa Nursaka al IA/D] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Column Number. When Edge is L (Left) or R (Right), only need to specify                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| P[Edge] [Row/Column Number]_[A/B]          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |  |  |  |  |  |

| P[Edge][Row Number]E_[A/B/C/D]             | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | These general purpose signals are input-only pins and are located near the PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GSRN                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| NC                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| RESERVED                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | This pin is reserved and should not be connected to anything on the board.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GND                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| V <sub>CC</sub>                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V <sub>CCAUX</sub>                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |