# E. Attice Semiconductor Corporation - LFE3-150EA-8FN1156C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                         |

|--------------------------------|--------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 18625                                                                          |

| Number of Logic Elements/Cells | 149000                                                                         |

| Total RAM Bits                 | 7014400                                                                        |

| Number of I/O                  | 586                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 1156-BBGA                                                                      |

| Supplier Device Package        | 1156-FPBGA (35x35)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-150ea-8fn1156c |

|                                |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Introduction

The LatticeECP3<sup>™</sup> (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>™</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

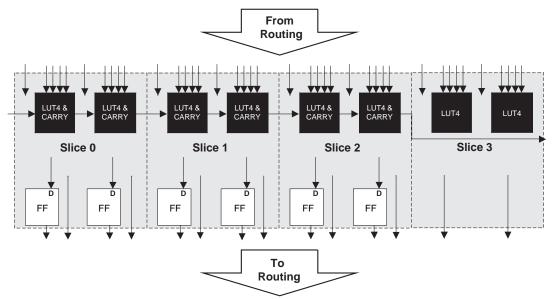

### Figure 2-2. PFU Diagram

### Slice

Slice 0 through Slice 2 contain two LUT4s feeding two registers, whereas Slice 3 contains two LUT4s only. For PFUs, Slice 0 through Slice 2 can be configured as distributed memory, a capability not available in the PFF. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

|         | PFU                     | PFF Block               |                         |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Slices 0, 1 and 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 10 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

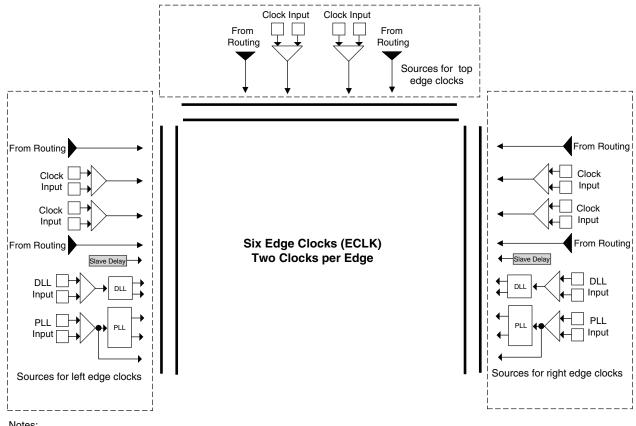

### **Edge Clock Sources**

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs, DLLs, Slave Delay and clock dividers as shown in Figure 2-19.

Notes:

1. Clock inputs can be configured in differential or single ended mode.

2. The two DLLs can also drive the two top edge clocks.

3. The top left and top right PLL can also drive the two top edge clocks.

# Edge Clock Routing

LatticeECP3 devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are six edge clocks per device: two edge clocks on each of the top, left, and right edges. Different PLL and DLL outputs are routed to the two muxes on the left and right sides of the device. In addition, the CLKINDEL signal (generated from the DLL Slave Delay Line block) is routed to all the edge clock muxes on the left and right sides of the device. Figure 2-20 shows the selection muxes for these clocks.

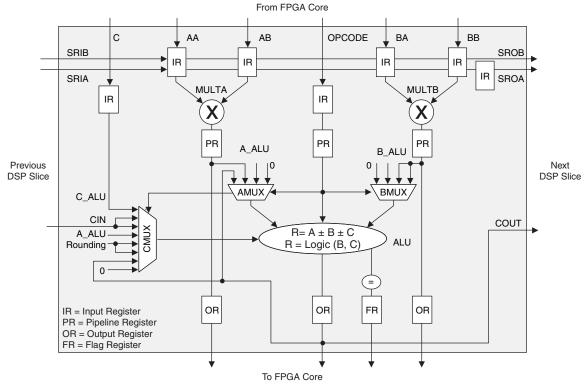

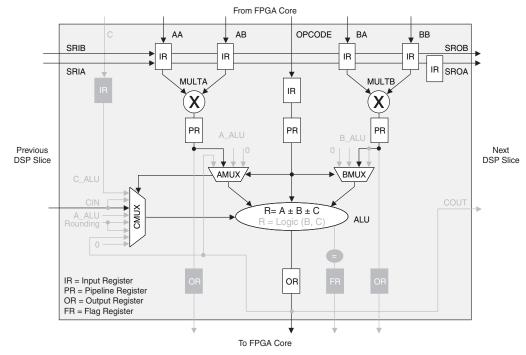

### Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | x9                    | x18 | x36 |

|-------------------|-----------------------|-----|-----|

| MULT              | 4                     | 2   | 1/2 |

| MAC               | 1                     | 1   | _   |

| MULTADDSUB        | 2                     | 1   | _   |

| MULTADDSUBSUM     | <b>1</b> <sup>1</sup> | 1/2 | _   |

1. One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

### Figure 2-31. MULTADDSUBSUM Slice 1

# Advanced sysDSP Slice Features

### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

### Addition

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- Rounding to infinity (RTI)

- Dynamic rounding

- Random rounding

- Convergent rounding

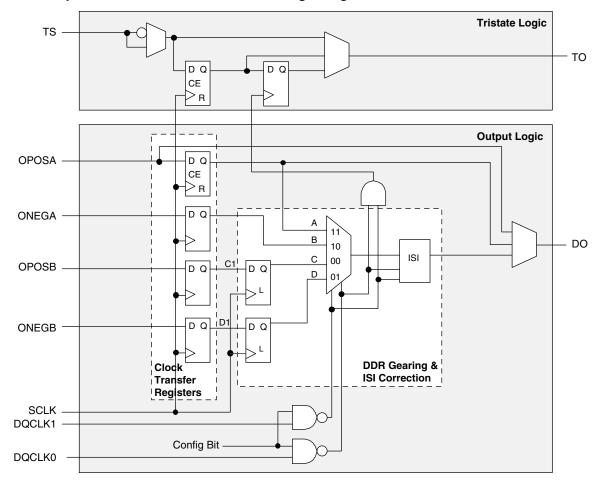

Figure 2-34. Output and Tristate Block for Left and Right Edges

## Tristate Register Block

The tristate register block registers tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional register for DDR operation.

In SDR and non-gearing DDR modes, TS input feeds one of the flip-flops that then feeds the output. In DDRX2 mode, the register TS input is fed into another register that is clocked using the DQCLK0 and DQCLK1 signals. The output of this register is used as a tristate control.

## **ISI** Calibration

The setting for Inter-Symbol Interference (ISI) cancellation occurs in the output register block. ISI correction is only available in the DDRX2 modes. ISI calibration settings exist once per output register block, so each I/O in a DQS-12 group may have a different ISI calibration setting.

The ISI block extends output signals at certain times, as a function of recent signal history. So, if the output pattern consists of a long strings of 0's to long strings of 1's, there are no delays on output signals. However, if there are quick, successive transitions from 010, the block will stretch out the binary 1. This is because the long trail of 0's will cause these symbols to interfere with the logic 1. Likewise, if there are quick, successive transitions from 101, the block will stretch out the binary 0. This block is controlled by a 3-bit delay control that can be set in the DQS control logic block.

For more information about this topic, please see the list of technical documentation at the end of this data sheet.

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on DDR Memory interface implementation in LatticeECP3.

# sysl/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

### sysl/O Buffer Banks

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , which allow it to be completely independent from the others. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

# LatticeECP3 External Switching Characteristics <sup>1, 2, 3, 13</sup>

|                            |                                                                   |                     | -         | -8              | •    | -7         | -6   |            | I     |

|----------------------------|-------------------------------------------------------------------|---------------------|-----------|-----------------|------|------------|------|------------|-------|

| Parameter                  | Description                                                       | Device              | Min.      | -8<br>Max.      | Min. | -7<br>Max. | Min. | -о<br>Max. | Units |

| Clocks                     | Description                                                       | Device              | Min.      | wax.            | win. | wax.       | MIN. | wax.       | Units |

| Primary Clock <sup>6</sup> |                                                                   |                     |           |                 |      |            |      |            |       |

|                            | Frequency for Primary Clock Tree                                  | ECP3-150EA          | _         | 500             |      | 420        | _    | 375        | MHz   |

| t <sub>MAX_PRI</sub>       | Clock Pulse Width for Primary                                     |                     |           | 000             |      | 420        |      | 0/0        |       |

| t <sub>W_PRI</sub>         | Clock                                                             | ECP3-150EA          | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-150EA          | -         | 300             | —    | 330        | —    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-150EA          | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-70EA/95EA      | -         | 500             | —    | 420        | -    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-70EA/95EA      | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-70EA/95EA      | _         | 360             | _    | 370        | _    | 380        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-70EA/95EA      | —         | 310             | —    | 320        | —    | 330        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-35EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-35EA           | 0.8       | —               | 0.9  |            | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-35EA           | -         | 300             | —    | 330        | _    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-35EA           | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-17EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-17EA           | 0.8       | _               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-17EA           | _         | 310             | —    | 340        | —    | 370        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-17EA           | _         | 220             | —    | 230        | —    | 240        | ps    |

| Edge Clock <sup>6</sup>    | •                                                                 |                     | •         |                 |      | •          | •    | •          |       |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-150EA          | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-150EA          | 0.9       | —               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-150EA          | -         | 200             | —    | 210        | _    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-70EA/95EA      | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-70EA/95EA      | 0.9       | _               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-70EA/95EA      | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-35EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-35EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| <sup>t</sup> skew_edge_dqs | Edge Clock Skew Within an Edge of the Device                      | ECP3-35EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-17EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-17EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| tskew_edge_dqs             | Edge Clock Skew Within an Edge of the Device                      | ECP3-17EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| Generic SDR                | •                                                                 |                     | •         | •               |      | •          | •    | •          | ·     |

| General I/O Pin Pa         | arameters Using Dedicated Clock In                                | put Primary Clock V | Vithout P | LL <sup>2</sup> |      |            |      |            |       |

| t <sub>CO</sub>            | Clock to Output - PIO Output<br>Register                          | ECP3-150EA          | _         | 3.9             | —    | 4.3        | —    | 4.7        | ns    |

| t <sub>SU</sub>            | Clock to Data Setup - PIO Input<br>Register                       | ECP3-150EA          | 0.0       | _               | 0.0  |            | 0.0  | _          | ns    |

| t <sub>H</sub>             | Clock to Data Hold - PIO Input<br>Register                        | ECP3-150EA          | 1.5       | _               | 1.7  |            | 2.0  |            | ns    |

| t <sub>SU_DEL</sub>        | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-150EA          | 1.3       | —               | 1.5  | _          | 1.7  |            | ns    |

### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                         |                                |                           | _        | -8       | -        | -7         | - 1           | -6    | r –   |

|-------------------------|--------------------------------|---------------------------|----------|----------|----------|------------|---------------|-------|-------|

| Parameter               | Description                    | Device                    | Min.     | Max.     | Min.     | Max.       | Min.          | Max.  | Units |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | All ECP3EA Devices        | 0.775    | _        | 0.775    | _          | 0.775         | _     | UI    |

| f <sub>MAX</sub> GDDR   | DDRX1 Clock Frequency          | All ECP3EA Devices        | _        | 250      | _        | 250        | _             | 250   | MHz   |

|                         | nputs with Clock and Data (>10 |                           | in (GDDF |          | ECLK Ce  |            | l<br>Isina PC |       |       |

| Input                   |                                |                           | in (abbi |          |          | intered) e | Joing TO      |       |       |

| Left and Right Si       | des                            |                           |          |          |          |            |               |       |       |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-150EA                | 321      | —        | 403      | —          | 471           |       | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-150EA                | 321      | _        | 403      | —          | 471           | —     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                | _        | 405      | _        | 325        | —             | 280   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-70EA/95EA            | 321      | _        | 403      | —          | 535           | _     | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-70EA/95EA            | 321      | _        | 403      | —          | 535           | _     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            |          | 405      | —        | 325        | —             | 250   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-35EA                 | 335      | _        | 425      |            | 535           |       | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-35EA                 | 335      | —        | 425      | —          | 535           | —     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 | _        | 405      | —        | 325        | —             | 250   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-17EA                 | 335      | _        | 425      | —          | 535           | —     | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-17EA                 | 335      |          | 425      |            | 535           |       | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 |          | 405      |          | 325        | —             | 250   | MHz   |

| Generic DDRX2 I         | nputs with Clock and Data (>10 | Bits Wide) Aligned at Pin | (GDDR)   | (2_RX.EC | CLK.Alig | ned)       |               |       |       |

| Left and Right Si       | de Using DLLCLKIN Pin for Clo  | ck Input                  |          |          |          |            |               |       |       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-150EA                |          | 0.225    |          | 0.225      | _             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-150EA                | 0.775    | —        | 0.775    | —          | 0.775         | _     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                | _        | 460      |          | 385        | —             | 345   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-70EA/95EA            | _        | 0.225    | —        | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-70EA/95EA            | 0.775    | —        | 0.775    | —          | 0.775         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            |          | 460      |          | 385        | —             | 311   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-35EA                 | _        | 0.210    | _        | 0.210      | _             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-35EA                 | 0.790    | —        | 0.790    | —          | 0.790         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 | —        | 460      | —        | 385        | —             | 311   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-17EA                 | _        | 0.210    | —        | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-17EA                 | 0.790    | _        | 0.790    |            | 0.790         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 | —        | 460      | —        | 385        | —             | 311   | MHz   |

| Top Side Using P        | CLK Pin for Clock Input        |                           |          |          |          |            |               |       |       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-150EA                |          | 0.225    |          | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-150EA                | 0.775    |          | 0.775    |            | 0.775         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                |          | 235      |          | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-70EA/95EA            |          | 0.225    |          | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-70EA/95EA            | 0.775    |          | 0.775    |            | 0.775         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            | —        | 235      | —        | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-35EA                 | —        | 0.210    |          | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-35EA                 | 0.790    |          | 0.790    |            | 0.790         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 |          | 235      | —        | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-17EA                 |          | 0.210    |          | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-17EA                 | 0.790    | —        | 0.790    | —          | 0.790         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 | _        | 235      | _        | 170        | _             | 130   | MHz   |

### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                         |                                                 |                                  | _          | -8       | -        | -7        | _        | 6         |           |

|-------------------------|-------------------------------------------------|----------------------------------|------------|----------|----------|-----------|----------|-----------|-----------|

| Parameter               | Description                                     | Device                           | Min.       | Max.     | Min.     | Max.      | Min.     | Max.      | Units     |

|                         | nputs with Clock and Data (>10bi                | its wide) are Aligned at I       | Pin (GDD   | RX2_RX   | ECLK.A   | ligned)   |          |           |           |

| (No CLKDIV)             | des Using DLLCLKPIN for Clock                   | Innut                            |            |          |          |           |          |           |           |

|                         | Data Setup Before CLK                           | ECP3-150EA                       | _          | 0.225    | _        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVACLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | 0.225    | 0.775    | 0.225     | 0.775    | 0.225     | UI        |

|                         | DDRX2 Clock Frequency                           | ECP3-150EA                       | 0.775      | 460      | 0.775    | 385       | 0.775    | 345       | MHz       |

| <sup>†</sup> MAX_GDDR   | Data Setup Before CLK                           |                                  | _          |          | _        |           | _        |           | UI        |

|                         | -                                               | ECP3-70EA/95EA                   | 0.775      | 0.225    |          | 0.225     |          | 0.225     |           |

| <sup>I</sup> DVECLKGDDR | Data Hold After CLK                             | ECP3-70EA/95EA<br>ECP3-70EA/95EA | 0.775      |          | 0.775    |           | 0.775    |           | UI<br>MHz |

| fMAX_GDDR               | DDRX2 Clock Frequency                           |                                  | —          | 460      |          | 385       | —        | 311       |           |

|                         | Data Setup Before CLK                           | ECP3-35EA                        | - 700      | 0.210    | -        | 0.210     | -        | 0.210     |           |

|                         | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | -        | 0.790    | -         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 460      | _        | 385       | _        | 311       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK<br>(Left and Right Sides) | ECP3-17EA                        | _          | 0.210    | _        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | —        | 0.790    | —         | 0.790    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 460      |          | 385       |          | 311       | MHz       |

| Top Side Using P        | CLK Pin for Clock Input                         |                                  |            |          |          |           |          |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-150EA                       |            | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | —        | 0.775    | —         | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-150EA                       | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-70EA/95EA                   | _          | 0.225    |          | 0.225     |          | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-70EA/95EA                   | 0.775      |          | 0.775    |           | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-70EA/95EA                   | _          | 235      |          | 170       |          | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-35EA                        |            | 0.210    | —        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | —        | 0.790    | —         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-17EA                        | _          | 0.210    | —        | 0.210     | —        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | _        | 0.790    | _         | 0.790    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 235      | _        | 170       |          | 130       | MHz       |

| -                       | nputs with Clock and Data (<10 E                | Bits Wide) Centered at Pi        | in (GDDF   | X2_RX.   | DQS.Cen  | tered) U  | sing DQ  | S Pin for | Clock     |

| Left and Right Sid      | des                                             |                                  |            |          |          |           |          |           |           |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK                           | All ECP3EA Devices               | 330        | _        | 330      | _         | 352      |           | ps        |

| t <sub>HOGDDR</sub>     | Data Hold After CLK                             | All ECP3EA Devices               | 330        | _        | 330      | —         | 352      | _         | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | _        | 400       | _        | 375       | MHz       |

|                         | nputs with Clock and Data (<10 E                | Bits Wide) Aligned at Pin        | (GDDR)     | (2 RX.D0 | QS.Align | ed) Usin  | g DQS Pi | n for Clo | ck Input  |

| Left and Right Sid      |                                                 | <b>J J J J J J J J J J</b>       | <b>1</b> - | _        | <b>J</b> | ,         | <b>J</b> |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | All ECP3EA Devices               | —          | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | All ECP3EA Devices               | 0.775      | _        | 0.775    | _         | 0.775    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | _        | 400       | _        | 375       | MHz       |

|                         | Output with Clock and Data (>10 I               | Bits Wide) Centered at P         | in (GDD    | RX1_TX.  | SCLK.Ce  | ntered)10 | )        |           | 1         |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-150EA                       | 670        | —        | 670      | _         | 670      |           | ps        |

| t <sub>DVAGDDR</sub>    | Data Valid After CLK                            | ECP3-150EA                       | 670        |          | 670      |           | 670      |           | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX1 Clock Frequency                           | ECP3-150EA                       |            | 250      |          | 250       |          | 250       | MHz       |

|                         |                                                 |                                  | 666        |          | CCE      |           | 664      |           |           |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-70EA/95EA                   | 666        |          | 665      |           | 664      |           | ps        |

# Over Recommended Commercial Operating Conditions

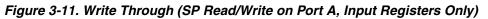

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# XAUI/Serial Rapid I/O Type 3/CPRI LV E.30 Electrical and Timing Characteristics

### **AC and DC Characteristics**

Table 3-13. Transmit

### **Over Recommended Operating Conditions**

| Symbol                                   | Description                      | <b>Test Conditions</b> | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|------------------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%                |      | 80   | _    | ps    |

| 17_0111_00                               | Differential impedance           |                        | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>2, 3, 4</sup>   | Output data deterministic jitter |                        | _    | _    | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total output data jitter         |                        | _    | _    | 0.35 | UI    |

1. Total jitter includes both deterministic jitter and random jitter.

2. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Values are measured at 2.5 Gbps.

### Table 3-14. Receive and Jitter Tolerance

### **Over Recommended Operating Conditions**

| Symbol                                | Description                                   | Test Conditions              | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------|------------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | _    | _    | dB    |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    | —    | —    | dB    |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           |                              | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) |                              | —    | —    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        |                              | —    | —    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    |                              | —    | —    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         |                              | —    | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          |                              | 0.35 | —    | —    | UI    |

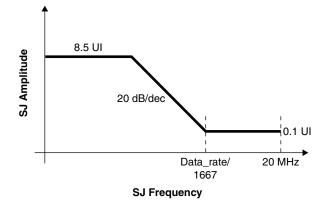

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Jitter tolerance parameters are characterized when Full Rx Equalization is enabled.

5. Values are measured at 2.5 Gbps.

# Figure 3-18. XAUI Sinusoidal Jitter Tolerance Mask

Note: The sinusoidal jitter tolerance is measured with at least 0.37 UIpp of Deterministic jitter (Dj) and the sum of Dj and Rj (random jitter) is at least 0.55 UIpp. Therefore, the sum of Dj, Rj and Sj (sinusoidal jitter) is at least 0.65 UIpp (Dj = 0.37, Rj = 0.18, Sj = 0.1).

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII/CPRI LV E.12 Electrical and Timing Characteristics

## AC and DC Characteristics

### Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 | _    | _    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | _    | _    | 0.24 | UI    |

1. Rise and fall times measured with board trace, connector and approximately 2.5 pf load.

2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

3. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

5. Values are measured at 1.25 Gbps.

### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |      |      | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | _    | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100  | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          | —    |      | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          | —    | _    | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | —    | _    | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    |      | 0.71 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                          | 0.29 |      |      | UI    |

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

5. Values are measured at 1.25 Gbps.

# SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics

### AC and DC Characteristics

### Table 3-19. Transmit

| Symbol                                  | Description                     | Test Conditions | Min. | Тур. | Max. | Units |

|-----------------------------------------|---------------------------------|-----------------|------|------|------|-------|

| BR <sub>SDO</sub>                       | Serial data rate                |                 | 270  | —    | 2975 | Mbps  |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 270 Mbps        | —    | —    | 0.20 | UI    |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 1485 Mbps       | —    | —    | 0.20 | UI    |

| T <sub>JALIGNMENT</sub> <sup>1, 2</sup> | Serial output jitter, alignment | 2970Mbps        | —    | —    | 0.30 | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 270 Mbps        | —    | —    | 0.20 | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 1485 Mbps       | —    | —    | 1.0  | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 2970 Mbps       | —    | —    | 2.0  | UI    |

Notes:

Timing jitter is measured in accordance with SMPTE RP 184-1996, SMPTE RP 192-1996 and the applicable serial data transmission standard, SMPTE 259M-1997 or SMPTE 292M (proposed). A color bar test pattern is used. The value of f<sub>SCLK</sub> is 270 MHz or 360 MHz for SMPTE 259M, 540 MHz for SMPTE 344M or 1485 MHz for SMPTE 292M serial data rates. See the Timing Jitter Bandpass section.

2. Jitter is defined in accordance with SMPTE RP1 184-1996 as: jitter at an equipment output in the absence of input jitter.

3. All Tx jitter is measured at the output of an industry standard cable driver; connection to the cable driver is via a 50 Ohm impedance differential signal from the Lattice SERDES device.

4. The cable driver drives: RL=75 Ohm, AC-coupled at 270, 1485, or 2970 Mbps, RREFLVL=RREFPRE=4.75 kOhm 1%.

### Table 3-20. Receive

| Symbol            | Description                                                  | Test Conditions | Min.                                           | Тур. | Max. | Units |

|-------------------|--------------------------------------------------------------|-----------------|------------------------------------------------|------|------|-------|

| BR <sub>SDI</sub> | Serial input data rate                                       |                 | 270                                            | —    | 2970 | Mbps  |

| CID               | Stream of non-transitions<br>(=Consecutive Identical Digits) |                 | 7(3G)/26(SMPTE<br>Triple rates)<br>@ 10-12 BER | _    | _    | Bits  |

### Table 3-21. Reference Clock

| Symbol            | Description                  | Test Conditions | Min. | Тур. | Max.  | Units |

|-------------------|------------------------------|-----------------|------|------|-------|-------|

| F <sub>VCLK</sub> | Video output clock frequency |                 | 27   | _    | 74.25 | MHz   |

| DCV               | Duty cycle, video clock      |                 | 45   | 50   | 55    | %     |

# **Package Pinout Information**

Package pinout information can be found under "Data Sheets" on the LatticeECP3 product pages on the Lattice website at http://www.latticesemi.com/Products/FPGAandCPLD/LatticeECP3 and in the Diamond or ispLEVER software tools. To create pinout information from within ispLEVER Design Planner, select **Tools > Spreadsheet View**. Then select **Select File > Export** and choose a type of output file. To create a pin information file from within Diamond select **Tools > Spreadsheet View** or **Tools >Package View**; then, select **File > Export** and choose a type of output file. See Diamond or ispLEVER Help for more information.

# **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

## For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- Power Calculator tool included with the Diamond and ispLEVER design tools, or as a standalone download from www.latticesemi.com/software

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Date          | Version | Section                             | Change Summary                                                                                                                                              |

|---------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Frequency to 150 Mbps in Table 3-11 Periodic Receiver Jitter Tolerance Specification                                                                |

| December 2010 | 01.7EA  | Multiple                            | Data sheet made final. Removed "preliminary" headings.                                                                                                      |

|               |         |                                     | Removed data for 70E and 95E devices. A separate data sheet is available for these specific devices.                                                        |

|               |         |                                     | Updated for Lattice Diamond design software.                                                                                                                |

|               |         | Introduction                        | Corrected number of user I/Os                                                                                                                               |

|               |         | Architecture                        | Corrected the package type in Table 2-14 Available SERDES Quad per LatticeECP3 Devices.                                                                     |

|               |         |                                     | Updated description of General Purpose PLL                                                                                                                  |

|               |         |                                     | Added additional information in the Flexible Quad SERDES Architecture section.                                                                              |

|               |         |                                     | Added footnotes and corrected the information in Table 2-16 Selectable master Clock (MCCLK) Frequencies During Configuration (Nominal).                     |

|               |         |                                     | Updated Figure 2-16, Per Region Secondary Clock Selection.                                                                                                  |

|               |         |                                     | Updated description for On-Chip Programmable Termination.                                                                                                   |

|               |         |                                     | Added information about number of rows of DSP slices.                                                                                                       |

|               |         |                                     | Updated footnote 2 for Table 2-12, On-Chip Termination Options for Input Modes.                                                                             |

|               |         |                                     | Updated information for sysIO buffer pairs.                                                                                                                 |

|               |         |                                     | Corrected minimum number of General Purpose PLLs (was 4, now 2).                                                                                            |

|               |         | DC and Switching<br>Characteristics | Regenerated sysCONFIG Port Timing figure.                                                                                                                   |

|               |         |                                     | Added $t_W$ (clock pulse width) in External Switching Characteristics table.                                                                                |

|               |         |                                     | Corrected units, revised and added data, and corrected footnote 1 in External Switching Characteristics table.                                              |

|               |         |                                     | Added Jitter Transfer figures in SERDES External Reference Clock section.                                                                                   |

|               |         |                                     | Corrected capacitance information in the DC Electrical Characteristics table.                                                                               |

|               |         |                                     | Corrected data in the Register-to-Register Performance table.                                                                                               |

|               |         |                                     | Corrected GDDR Parameter name HOGDDR.                                                                                                                       |

|               |         |                                     | Corrected RSDS25 -7 data in Family Timing Adders table.                                                                                                     |

|               |         |                                     | Added footnotes 10-12 to DDR data information in the External Switching Characteristics table.                                                              |

|               |         |                                     | Corrected titles for Figures 3-7 (DDR/DDR2/DDR3 Parameters) and 3-8 (Generic DDR/DDRX2 Parameters).                                                         |

|               |         |                                     | Updated titles for Figures 3-5 (MLVDS25 (Multipoint Low Voltage Differential Signaling)) and 3-6 (Generic DDRX1/DDRX2 (With Clock and Data Edges Aligned)). |

|               |         |                                     | Updated Supply Current table.                                                                                                                               |

|               |         |                                     | Added GDDR interface information to the External Switching and Characteristics table.                                                                       |

|               |         |                                     | Added footnote to sysIO Recommended Operating Conditions table.                                                                                             |

|               |         |                                     | Added footnote to LVDS25 table.                                                                                                                             |

|               |         |                                     | Corrected DDR section footnotes and references.                                                                                                             |

|               |         |                                     | Corrected Hot Socketing support from "top and bottom banks" to "top and bottom I/O pins".                                                                   |

|               | ·       | Pinout Information                  | Updated description for VTTx.                                                                                                                               |

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                           |

|---------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                                   |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                                 |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                                           |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                                             |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                                  |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                               |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added SERDES/PCS Block Latency Breakdown table.                                                                                                                                                                                                                                                                                                          |

|               |         |                                     | External Reference Clock Specifications table, added footnote 4, add symbol name vREF-IN-DIFF.                                                                                                                                                                                                                                                           |

|               |         |                                     | Added SERDES External Reference Clock Waveforms.                                                                                                                                                                                                                                                                                                         |

|               |         |                                     | Updated Serial Output Timing and Levels table.                                                                                                                                                                                                                                                                                                           |

|               |         |                                     | Pin-to-pin performance table, changed "typically 3% slower" to "typically slower".                                                                                                                                                                                                                                                                       |

|               |         |                                     | Updated timing information                                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Updated SERDES minimum frequency.                                                                                                                                                                                                                                                                                                                        |

|               |         |                                     | Added data to the following tables: External Switching Characteristics,<br>Internal Switching Characteristics, Family Timing Adders, Maximum I/O<br>Buffer Speed, DLL Timing, High Speed Data Transmitter, Channel Out-<br>put Jitter, Typical Building Block Function Performance, Register-to-<br>Register Performance, and Power Supply Requirements. |

|               |         |                                     | Updated Serial Input Data Specifications table.                                                                                                                                                                                                                                                                                                          |

|               |         |                                     | Updated Transmit table, Serial Rapid I/O Type 2 Electrical and Timing Characteristics section.                                                                                                                                                                                                                                                           |

|               |         | Pinout Information                  | Updated Signal Description tables.                                                                                                                                                                                                                                                                                                                       |

|               |         |                                     | Updated Pin Information Summary tables and added footnote 1.                                                                                                                                                                                                                                                                                             |

| February 2009 | 01.0    | —                                   | Initial release.                                                                                                                                                                                                                                                                                                                                         |