# E: Lattice Semiconductor Corporation - LFE3-150EA-8FN672C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 18625                                                                         |

| Number of Logic Elements/Cells | 149000                                                                        |

| Total RAM Bits                 | 7014400                                                                       |

| Number of I/O                  | 380                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 672-BBGA                                                                      |

| Supplier Device Package        | 672-FPBGA (27x27)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-150ea-8fn672c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

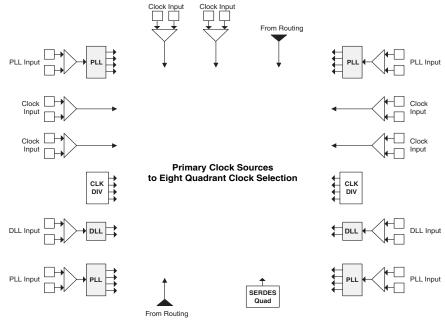

#### Figure 2-10. Primary Clock Sources for LatticeECP3-35

Note: Clock inputs can be configured in differential or single-ended mode.

#### Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

Note: Clock inputs can be configured in differential or single-ended mode.

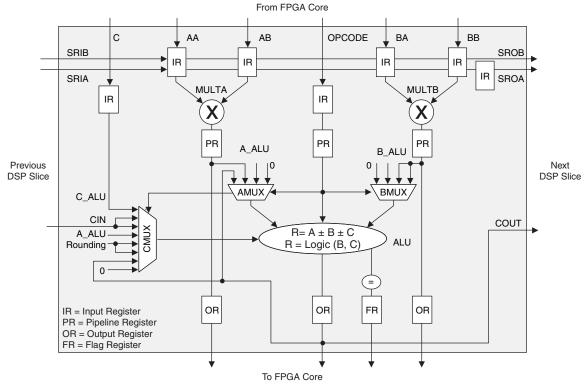

#### Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | x9                    | x18 | x36 |

|-------------------|-----------------------|-----|-----|

| MULT              | 4                     | 2   | 1/2 |

| MAC               | 1                     | 1   | _   |

| MULTADDSUB        | 2                     | 1   | _   |

| MULTADDSUBSUM     | <b>1</b> <sup>1</sup> | 1/2 | _   |

1. One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### MMAC DSP Element

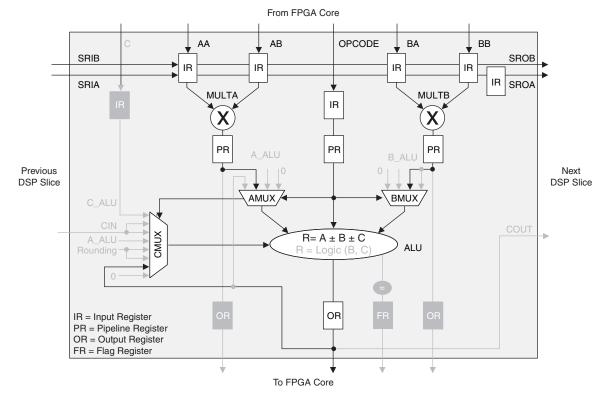

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

#### Figure 2-28. MMAC sysDSP Element

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on DDR Memory interface implementation in LatticeECP3.

#### sysl/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

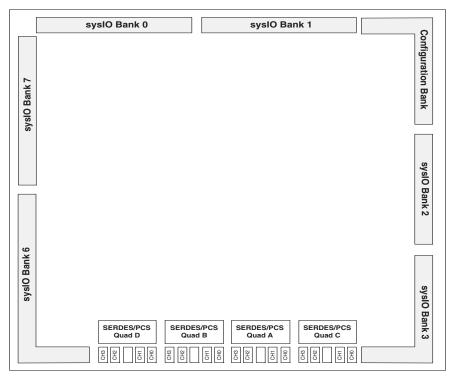

#### sysl/O Buffer Banks

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , which allow it to be completely independent from the others. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

#### Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                     | Data Rate<br>(Mbps)                                             | Number of<br>General/Link Width | Encoding Style |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------|

| PCI Express 1.1                                                              | 2500                                                            | x1, x2, x4                      | 8b10b          |

| Gigabit Ethernet                                                             | 1250, 2500                                                      | x1                              | 8b10b          |

| SGMII                                                                        | 1250                                                            | x1                              | 8b10b          |

| XAUI                                                                         | 3125                                                            | x4                              | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                                          | x1, x4                          | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | x1                              | 8b10b          |

| SD-SDI<br>(259M, 344M)                                                       | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | x1                              | NRZI/Scrambled |

| HD-SDI<br>(292M)                                                             | 1483.5,<br>1485                                                 | x1                              | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                             | 2967,<br>2970                                                   | x1                              | NRZI/Scrambled |

| SONET-STS-3 <sup>2</sup>                                                     | 155.52                                                          | x1                              | N/A            |

| SONET-STS-12 <sup>2</sup>                                                    | 622.08                                                          | x1                              | N/A            |

| SONET-STS-48 <sup>2</sup>                                                    | 2488                                                            | x1                              | N/A            |

1. For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

2. The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

# LatticeECP3 Family Data Sheet DC and Switching Characteristics

#### April 2014

Data Sheet DS1021

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V_{CC}                                                        |

|------------------------------------------------------------------------------|

| Supply Voltage V_{CCAUX} $\ldots \ldots \ldots \ldots -0.5$ V to 3.75 V      |

| Supply Voltage V_{CCJ} $\ldots \ldots \ldots \ldots \ldots -0.5$ V to 3.75 V |

| Output Supply Voltage V_{CCIO} –0.5 V to 3.75 V                              |

| Input or I/O Tristate Voltage Applied $^4.$ –0.5 V to 3.75 V                 |

| Storage Temperature (Ambient) $\ldots \ldots65$ V to 150 $^{\circ}\text{C}$  |

| Junction Temperature $(T_J)$                                                 |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

# **Recommended Operating Conditions**<sup>1</sup>

| Symbol                             | Parameter                                                                      | Min.  | Max.   | Units |

|------------------------------------|--------------------------------------------------------------------------------|-------|--------|-------|

| V <sub>CC<sup>2</sup></sub>        | Core Supply Voltage                                                            | 1.14  | 1.26   | V     |

| V <sub>CCAUX</sub> <sup>2, 4</sup> | Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES) | 3.135 | 3.465  | V     |

| V <sub>CCPLL</sub>                 | PLL Supply Voltage                                                             | 3.135 | 3.465  | V     |

| V <sub>CCIO<sup>2, 3</sup></sub>   | I/O Driver Supply Voltage                                                      | 1.14  | 3.465  | V     |

| V <sub>CCJ<sup>2</sup></sub>       | Supply Voltage for IEEE 1149.1 Test Access Port                                | 1.14  | 3.465  | V     |

| $V_{REF1}$ and $V_{REF2}$          | Input Reference Voltage                                                        | 0.5   | 1.7    | V     |

| V <sub>TT</sub> ⁵                  | Termination Voltage                                                            | 0.5   | 1.3125 | V     |

| t <sub>јсом</sub>                  | Junction Temperature, Commercial Operation                                     | 0     | 85     | °C    |

| t <sub>JIND</sub>                  | Junction Temperature, Industrial Operation                                     | -40   | 100    | °C    |

| SERDES External P                  | ower Supply <sup>6</sup>                                                       | •     | •      |       |

|                                    | Input Buffer Power Supply (1.2 V)                                              | 1.14  | 1.26   | V     |

| V <sub>CCIB</sub>                  | Input Buffer Power Supply (1.5 V)                                              | 1.425 | 1.575  | V     |

|                                    | Output Buffer Power Supply (1.2 V)                                             | 1.14  | 1.26   | V     |

| V <sub>ССОВ</sub>                  | Output Buffer Power Supply (1.5 V)                                             | 1.425 | 1.575  | V     |

| V <sub>CCA</sub>                   | Transmit, Receive, PLL and Reference Clock Buffer Power Supply                 | 1.14  | 1.26   | V     |

1. For correct operation, all supplies except V<sub>REF</sub> and V<sub>TT</sub> must be held in their valid operation range. This is true independent of feature usage.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC.</sub> If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3 V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. V<sub>CCAUX</sub> ramp rate must not exceed 30 mV/µs during power-up when transitioning between 0 V and 3.3 V.

5. If not used, V<sub>TT</sub> should be left floating.

6. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for information on board considerations for SERDES power supplies.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol  | Parameter                                    | Condition                                 | Min. | Тур. | Max. | Units |

|---------|----------------------------------------------|-------------------------------------------|------|------|------|-------|

| IDK_HS⁴ | Input or I/O Leakage Current                 | $0 \le V_{IN} \le V_{IH}$ (Max.)          | -    |      | +/-1 | mA    |

| ו⊓א₂    | DK <sup>×</sup> Unput or I/O Leakage Current | $0 \le V_{IN} < V_{CCIO}$                 | -    |      | +/-1 | mA    |

|         |                                              | $V_{CCIO} \le V_{IN} \le V_{CCIO} + 0.5V$ | _    | 18   | _    | mA    |

1.  $V_{CC},\,V_{CCAUX}$  and  $V_{CCIO}$  should rise/fall monotonically.

2.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

3. LVCMOS and LVTTL only.

4. Applicable to general purpose I/O pins located on the top and bottom sides of the device.

5. Applicable to general purpose I/O pins located on the left and right sides of the device.

# Hot Socketing Requirements<sup>1, 2</sup>

| Description                                                                     | Min. | Тур. | Max. | Units |

|---------------------------------------------------------------------------------|------|------|------|-------|

| Input current per SERDES I/O pin when device is powered down and inputs driven. | _    | -    | 8    | mA    |

1. Assumes the device is powered down, all supplies grounded, both P and N inputs driven by CML driver with maximum allowed VCCOB (1.575 V), 8b10b data, internal AC coupling.

2. Each P and N input must have less than the specified maximum input current. For a 16-channel device, the total input current would be 8 mA\*16 channels \*2 input pins per channel = 256 mA

## **ESD** Performance

Please refer to the LatticeECP3 Product Family Qualification Summary for complete qualification data, including ESD performance.

# **DC Electrical Characteristics**

| Symbol                          | Parameter                                | Condition                                                                                                                                                   | Min.           | Тур. | Max.                  | Units |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| $I_{\rm IL}, I_{\rm IH}^{1, 4}$ | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2 \text{ V})$                                                                                                               | —              |      | 10                    | μA    |

| I <sub>IH</sub> <sup>1, 3</sup> | Input or I/O High Leakage                | $(V_{CCIO} - 0.2 \text{ V}) < V_{IN} \le 3.6 \text{ V}$                                                                                                     | —              | _    | 150                   | μA    |

| I <sub>PU</sub>                 | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                                                                                             | -30            |      | -210                  | μΑ    |

| I <sub>PD</sub>                 | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                                                                                                  | 30             |      | 210                   | μΑ    |

| I <sub>BHLS</sub>               | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                     | 30             |      | —                     | μΑ    |

| I <sub>BHHS</sub>               | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                                     | -30            | _    | —                     | μΑ    |

| I <sub>BHLO</sub>               | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>               | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | -210                  | μA    |

| V <sub>BHT</sub>                | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                                                                                             | $V_{IL}$ (MAX) | —    | V <sub>IH</sub> (MIN) | V     |

| C1                              | I/O Capacitance <sup>2</sup>             |                                                                                                                                                             | —              | 5    | 8                     | pf    |

| C2                              | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | —              | 5    | 7                     | pf    |

#### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

3. Applicable to general purpose I/Os in top and bottom banks. 4. When used as  $V_{REF}$  maximum leakage= 25  $\mu$ A.

Units V

Ω

Ω

Ω

Ω

٧

٧

V

V

mΑ

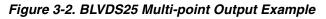

#### **BLVDS25**

The LatticeECP3 devices support the BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

#### Table 3-2. BLVDS25 DC Conditions<sup>1</sup>

V<sub>CCIO</sub>

ZOUT

R<sub>S</sub>

R<sub>TL</sub>

$\mathsf{R}_{\mathsf{TR}}$ V<sub>OH</sub>

VOL

VOD

V<sub>CM</sub>

|                   | · · · · ·                     | -                |                  |  |

|-------------------|-------------------------------|------------------|------------------|--|

|                   |                               | Тур              | ical             |  |

| Parameter         | Description                   | <b>Ζο = 45</b> Ω | <b>Ζο = 90</b> Ω |  |

| / <sub>CCIO</sub> | Output Driver Supply (+/– 5%) | 2.50             | 2.50             |  |

|                   |                               |                  |                  |  |

10.00

90.00

45.00

45.00

1.38

1.12

0.25

1.25

11.24

10.00

90.00

90.00

90.00

1.48

1.02

0.46

1.25

10.20

**Over Recommended Operating Conditions**

$I_{DC}$ 1. For input buffer, see LVDS table.

**Driver Impedance**

**Output High Voltage**

Output Low Voltage

**DC Output Current**

Output Differential Voltage

Output Common Mode Voltage

Driver Series Resistor (+/- 1%)

Driver Parallel Resistor (+/- 1%)

Receiver Termination (+/- 1%)

# **Typical Building Block Function Performance**

### Pin-to-Pin Performance (LVCMOS25 12 mA Drive)<sup>1, 2, 3</sup>

| Function        | –8 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions | ł         |       |

| 16-bit Decoder  | 4.7       | ns    |

| 32-bit Decoder  | 4.7       | ns    |

| 64-bit Decoder  | 5.7       | ns    |

| 4:1 MUX         | 4.1       | ns    |

| 8:1 MUX         | 4.3       | ns    |

| 16:1 MUX        | 4.7       | ns    |

| 32:1 MUX        | 4.8       | ns    |

1. These functions were generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

#### Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                                                   | –8 Timing | Units |

|----------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                            |           |       |

| 16-bit Decoder                                                             | 500       | MHz   |

| 32-bit Decoder                                                             | 500       | MHz   |

| 64-bit Decoder                                                             | 500       | MHz   |

| 4:1 MUX                                                                    | 500       | MHz   |

| 8:1 MUX                                                                    | 500       | MHz   |

| 16:1 MUX                                                                   | 500       | MHz   |

| 32:1 MUX                                                                   | 445       | MHz   |

| 8-bit adder                                                                | 500       | MHz   |

| 16-bit adder                                                               | 500       | MHz   |

| 64-bit adder                                                               | 305       | MHz   |

| 16-bit counter                                                             | 500       | MHz   |

| 32-bit counter                                                             | 460       | MHz   |

| 64-bit counter                                                             | 320       | MHz   |

| 64-bit accumulator                                                         | 315       | MHz   |

| Embedded Memory Functions                                                  | · · ·     |       |

| 512x36 Single Port RAM, EBR Output Registers                               | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, EBR Output Registers) | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers        | 130       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, PLC Output Registers) | 245       | MHz   |

| Distributed Memory Functions                                               | <b>i</b>  |       |

| 16x4 Pseudo-Dual Port RAM (One PFU)                                        | 500       | MHz   |

| 32x4 Pseudo-Dual Port RAM                                                  | 500       | MHz   |

| 64x8 Pseudo-Dual Port RAM                                                  | 400       | MHz   |

| DSP Function                                                               | · · ·     |       |

| 18x18 Multiplier (All Registers)                                           | 400       | MHz   |

| 9x9 Multiplier (All Registers)                                             | 400       | MHz   |

| 36x36 Multiply (All Registers)                                             | 260       | MHz   |

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                       |                                                                   |                      | _          | -8        | -          | -7      | -          | -6   |       |

|-----------------------|-------------------------------------------------------------------|----------------------|------------|-----------|------------|---------|------------|------|-------|

| Parameter             | Description                                                       | Device               | Min.       | Max.      | Min.       | Max.    | Min.       | Max. | Units |

| t <sub>H_DEL</sub>    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-150EA           | 0.0        | —         | 0.0        | _       | 0.0        | —    | ns    |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU<br>Register                        | ECP3-150EA           | -          | 500       | —          | 420     | —          | 375  | MHz   |

| t <sub>CO</sub>       | Clock to Output - PIO Output<br>Register                          | ECP3-70EA/95EA       | -          | 3.8       | —          | 4.2     | —          | 4.6  | ns    |

| t <sub>SU</sub>       | Clock to Data Setup - PIO Input<br>Register                       | ECP3-70EA/95EA       | 0.0        | _         | 0.0        | _       | 0.0        | —    | ns    |

| t <sub>H</sub>        | Clock to Data Hold - PIO Input<br>Register                        | ECP3-70EA/95EA       | 1.4        | _         | 1.6        | _       | 1.8        | —    | ns    |

| t <sub>SU_DEL</sub>   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-70EA/95EA       | 1.3        | _         | 1.5        | _       | 1.7        | —    | ns    |

|                       | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-70EA/95EA       | 0.0        | _         | 0.0        | _       | 0.0        | —    | ns    |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU<br>Register                        | ECP3-70EA/95EA       | _          | 500       | _          | 420     | _          | 375  | MHz   |

| t <sub>co</sub>       | Clock to Output - PIO Output<br>Register                          | ECP3-35EA            | _          | 3.7       | _          | 4.1     | _          | 4.5  | ns    |

| t <sub>SU</sub>       | Clock to Data Setup - PIO Input<br>Register                       | ECP3-35EA            | 0.0        | —         | 0.0        | —       | 0.0        | —    | ns    |

| t <sub>H</sub>        | Clock to Data Hold - PIO Input<br>Register                        | ECP3-35EA            | 1.2        | —         | 1.4        | —       | 1.6        | —    | ns    |

| t <sub>SU_DEL</sub>   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-35EA            | 1.3        | _         | 1.4        | _       | 1.5        | —    | ns    |

| t <sub>H_DEL</sub>    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-35EA            | 0.0        | _         | 0.0        | _       | 0.0        | —    | ns    |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU<br>Register                        | ECP3-35EA            | —          | 500       | _          | 420     | _          | 375  | MHz   |

| t <sub>co</sub>       | Clock to Output - PIO Output<br>Register                          | ECP3-17EA            | _          | 3.5       | _          | 3.9     | —          | 4.3  | ns    |

| t <sub>SU</sub>       | Clock to Data Setup - PIO Input<br>Register                       | ECP3-17EA            | 0.0        | —         | 0.0        | _       | 0.0        | —    | ns    |

| t <sub>H</sub>        | Clock to Data Hold - PIO Input<br>Register                        | ECP3-17EA            | 1.3        | —         | 1.5        | _       | 1.6        | —    | ns    |

| t <sub>SU_DEL</sub>   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-17EA            | 1.3        | —         | 1.4        | _       | 1.5        | —    | ns    |

|                       | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-17EA            | 0.0        | —         | 0.0        | _       | 0.0        | —    | ns    |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU<br>Register                        | ECP3-17EA            | —          | 500       | —          | 420     | —          | 375  | MHz   |

| General I/O Pin P     | arameters Using Dedicated Clock I                                 | nput Primary Clock v | vith PLL v | with Cloc | k Injectio | on Remo | val Settii | າg²  |       |

| t <sub>COPLL</sub>    | Clock to Output - PIO Output<br>Register                          | ECP3-150EA           | —          | 3.3       | —          | 3.6     | —          | 39   | ns    |

| t <sub>SUPLL</sub>    | Clock to Data Setup - PIO Input<br>Register                       | ECP3-150EA           | 0.7        | —         | 0.8        | —       | 0.9        | —    | ns    |

| t <sub>HPLL</sub>     | Clock to Data Hold - PIO Input<br>Register                        | ECP3-150EA           | 0.8        | —         | 0.9        | —       | 1.0        | —    | ns    |

|                       | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-150EA           | 1.6        | —         | 1.8        | —       | 2.0        | —    | ns    |

| t <sub>H_DELPLL</sub> | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-150EA           | -          | 0.0       | —          | 0.0     | —          | 0.0  | ns    |

| t <sub>COPLL</sub>    | Clock to Output - PIO Output<br>Register                          | ECP3-70EA/95EA       | _          | 3.3       | _          | 3.5     | _          | 3.8  | ns    |

| tSUPLL                | Clock to Data Setup - PIO Input<br>Register                       | ECP3-70EA/95EA       | 0.7        | _         | 0.8        | _       | 0.9        | _    | ns    |

#### Over Recommended Commercial Operating Conditions

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                               | ·8                                                             | _                                                                                                           | -7                                                  | _                                                                                                       | -6                                                                      |                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min.                                                                            | Max.                                                           | Min.                                                                                                        | Max.                                                | Min.                                                                                                    | Max.                                                                    | Units                                                                                     |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                        | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.6                                                                             |                                                                | 1.8                                                                                                         |                                                     | 2.0                                                                                                     |                                                                         | ns                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                          | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                       | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.2                                                            | _                                                                                                           | 3.4                                                 | _                                                                                                       | 3.6                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                       | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                        | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             |                                                                | 0.3                                                                                                         |                                                     | 0.4                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             |                                                                | 1.7                                                                                                         |                                                     | 1.8                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                       | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.0                                                            | _                                                                                                           | 3.3                                                 | _                                                                                                       | 3.5                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                       | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                        | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                   | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             | _                                                              | 1.7                                                                                                         | _                                                   | 1.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             | _                                                              | 0.0                                                                                                         | _                                                   | 0.0                                                                                                     | _                                                                       | ns                                                                                        |

| Input                                                                                                                                                                                                                                                                                                                                                                                                                    | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SUGDDR</sub>                                                                                                                                                                                                                                                                                                                                                                                                      | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             |                                                                | 480                                                                                                         |                                                     | 480                                                                                                     |                                                                         | ps                                                                                        |

| t <sub>HOGDDR</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 480                                                                             |                                                                | 480                                                                                                         |                                                     |                                                                                                         |                                                                         |                                                                                           |