Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                        |

| Number of LABs/CLBs            | 18625                                                                           |

| Number of Logic Elements/Cells | 149000                                                                          |

| Total RAM Bits                 | 7014400                                                                         |

| Number of I/O                  | 380                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 672-BBGA                                                                        |

| Supplier Device Package        | 672-FPBGA (27x27)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-150ea-8fn672ctw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Architecture

June 2013 Data Sheet DS1021

## **Architecture Overview**

Each LatticeECP3 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM™ Embedded Block RAM (EBR) and rows of sysDSP™ Digital Signal Processing slices, as shown in Figure 2-1. The LatticeECP3-150 has four rows of DSP slices; all other LatticeECP3 devices have two rows of DSP slices. In addition, the LatticeECP3 family contains SERDES Quads on the bottom of the device.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional Unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

The LatticeECP3 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18Kbit fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, LatticeECP3 devices contain up to two rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The LatticeECP3 devices feature up to 16 embedded 3.2 Gbps SERDES (Serializer / Deserializer) channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of four SERDES channels, along with its Physical Coding Sub-layer (PCS) block, creates a quad. The functionality of the SERDES/PCS quads can be controlled by memory cells set during device configuration or by registers that are addressable during device operation. The registers in every quad can be programmed via the SERDES Client Interface (SCI). These quads (up to four) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysl/O buffers. The sysl/O buffers of the LatticeECP3 devices are arranged in seven banks, allowing the implementation of a wide variety of I/O standards. In addition, a separate I/O bank is provided for the programming interfaces. 50% of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3.

The LatticeECP3 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

Other blocks provided include PLLs, DLLs and configuration functions. The LatticeECP3 architecture provides two Delay Locked Loops (DLLs) and up to ten Phase Locked Loops (PLLs). The PLL and DLL blocks are located at the end of the EBR/DSP rows.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located toward the center of this EBR row. Every device in the LatticeECP3 family supports a sysCONFIG™ port located in the corner between banks one and two, which allows for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The LatticeECP3 devices use 1.2 V as their core voltage.

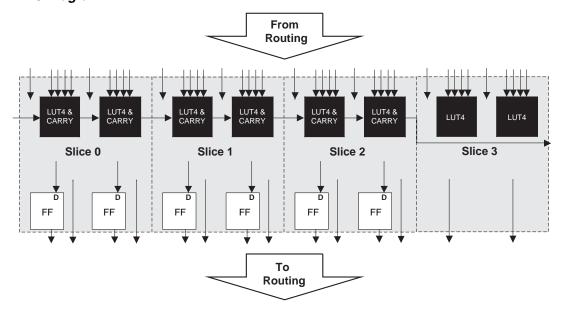

Figure 2-2. PFU Diagram

### Slice

Slice 0 through Slice 2 contain two LUT4s feeding two registers, whereas Slice 3 contains two LUT4s only. For PFUs, Slice 0 through Slice 2 can be configured as distributed memory, a capability not available in the PFF. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions.

Table 2-1. Resources and Modes Available per Slice

|         | PFU E                   | BLock                   | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Slices 0, 1 and 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 10 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

# **Modes of Operation**

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

### **Logic Mode**

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- · Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- · Up counter 2-bit

- · Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- · Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals. A 16x2-bit pseudo dual port RAM (PDPR) memory is created by using one Slice as the read-write port and the other companion slice as the read-only port.

LatticeECP3 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in LatticeECP3 devices, please see TN1179, LatticeECP3 Memory Usage Guide.

Table 2-3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

## **PLL/DLL Cascading**

LatticeECP3 devices have been designed to allow certain combinations of PLL and DLL cascading. The allowable combinations are:

- PLL to PLL supported

- · PLL to DLL supported

The DLLs in the LatticeECP3 are used to shift the clock in relation to the data for source synchronous inputs. PLLs are used for frequency synthesis and clock generation for source synchronous interfaces. Cascading PLL and DLL blocks allows applications to utilize the unique benefits of both DLLs and PLLs.

For further information about the DLL, please see the list of technical documentation at the end of this data sheet.

## **PLL/DLL PIO Input Pin Connections**

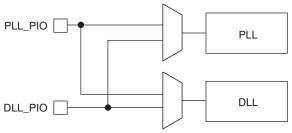

All LatticeECP3 devices contains two DLLs and up to ten PLLs, arranged in quadrants. If a PLL and a DLL are next to each other, they share input pins as shown in the Figure 2-7.

Figure 2-7. Sharing of PIO Pins by PLLs and DLLs in LatticeECP3 Devices

Note: Not every PLL has an associated DLL.

# **Clock Dividers**

LatticeECP3 devices have two clock dividers, one on the left side and one on the right side of the device. These are intended to generate a slower-speed system clock from a high-speed edge clock. The block operates in a ÷2, ÷4 or ÷8 mode and maintains a known phase relationship between the divided down clock and the high-speed clock based on the release of its reset signal. The clock dividers can be fed from selected PLL/DLL outputs, the Slave Delay lines, routing or from an external clock input. The clock divider outputs serve as primary clock sources and feed into the clock distribution network. The Reset (RST) control signal resets input and asynchronously forces all outputs to low. The RELEASE signal releases outputs synchronously to the input clock. For further information on clock dividers, please see TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide. Figure 2-8 shows the clock divider connections.

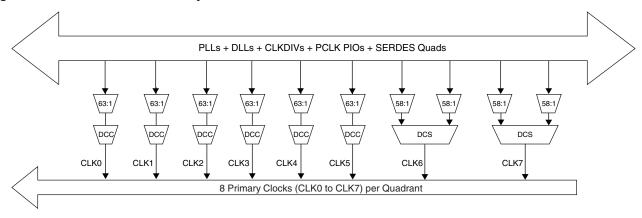

## **Primary Clock Routing**

The purpose of the primary clock routing is to distribute primary clock sources to the destination quadrants of the device. A global primary clock is a primary clock that is distributed to all quadrants. The clock routing structure in LatticeECP3 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-12 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

Figure 2-12. Per Quadrant Primary Clock Selection

# **Dynamic Clock Control (DCC)**

The DCC (Quadrant Clock Enable/Disable) feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, all the logic fed by that clock does not toggle, reducing the overall power consumption of the device.

# Dynamic Clock Select (DCS)

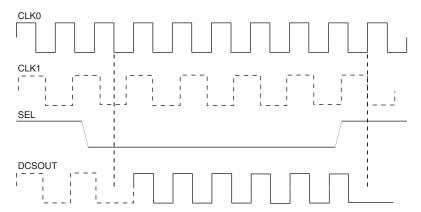

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved regardless of when the select signal is toggled. There are two DCS blocks per quadrant; in total, there are eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-12).

Figure 2-13 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, please see the list of technical documentation at the end of this data sheet.

Figure 2-13. DCS Waveforms

## **Secondary Clock/Control Sources**

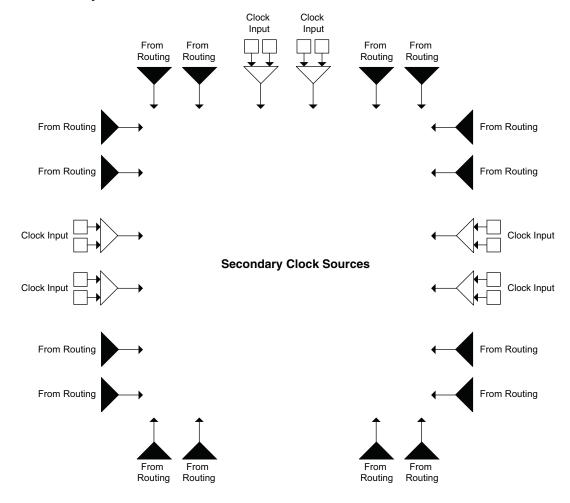

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for the clock.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7.

Figure 2-14. Secondary Clock Sources

Note: Clock inputs can be configured in differential or single-ended mode.

# Secondary Clock/Control Routing

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight secondary clock resources per region (SC0 to SC7). The same secondary clock routing can be used for control signals.

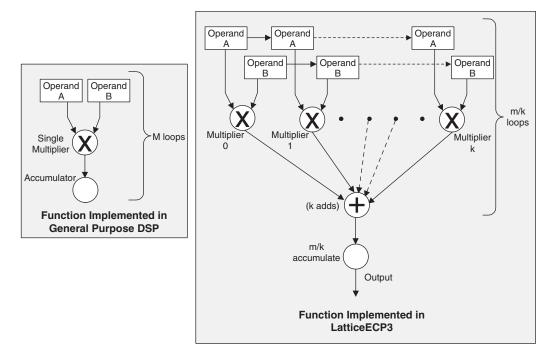

This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-23 compares the fully serial implementation to the mixed parallel and serial implementation.

Figure 2-23. Comparison of General DSP and LatticeECP3 Approaches

# LatticeECP3 sysDSP Slice Architecture Features

The LatticeECP3 sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The LatticeECP3 sysDSP Slice supports many functions that include the following:

- Multiply (one 18 x 36, two 18 x 18 or four 9 x 9 Multiplies per Slice)

- Multiply (36 x 36 by cascading across two sysDSP slices)

- Multiply Accumulate (up to 18 x 36 Multipliers feeding an Accumulator that can have up to 54-bit resolution)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18 x 18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such

There are some restrictions to be aware of when using spread spectrum. When a quad shares a PCI Express x1 channel with a non-PCI Express channel, ensure that the reference clock for the quad is compatible with all protocols within the quad. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications because of tight CTC ppm requirements.

While the LatticeECP3 architecture will allow the mixing of a PCI Express channel and a Gigabit Ethernet, Serial RapidIO or SGMII channel within the same quad, using a PCI Express spread spectrum clocking as the transmit reference clock will cause a violation of the Gigabit Ethernet, Serial RapidIO and SGMII transmit jitter specifications.

For further information on SERDES, please see TN1176, LatticeECP3 SERDES/PCS Usage Guide.

# **IEEE 1149.1-Compliant Boundary Scan Testability**

All LatticeECP3 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage  $V_{CCI}$  and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards.

For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

# **Device Configuration**

All LatticeECP3 devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. The sysCONFIG port includes seven I/Os used as dedicated pins with the remaining pins used as dual-use pins. See TN1169, LatticeECP3 sysCONFIG Usage Guide for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure a LatticeECP3 device:

- 1. JTAG

- 2. Standard Serial Peripheral Interface (SPI and SPIm modes) interface to boot PROM memory

- 3. System microprocessor to drive a x8 CPU port (PCM mode)

- 4. System microprocessor to drive a serial slave SPI port (SSPI mode)

- 5. Generic byte wide flash with a MachXO™ device, providing control and addressing

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

LatticeECP3 devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

# Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                             | –8 Timing | Units |

|------------------------------------------------------|-----------|-------|

| 18x18 Multiply/Accumulate (Input & Output Registers) | 200       | MHz   |

| 18x18 Multiply-Add/Sub (All Registers)               | 400       | MHz   |

- 1. These timing numbers were generated using ispLEVER tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

- 2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

- 3. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

# **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond and ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond and ispLEVER design tools can provide logic timing numbers at a particular temperature and voltage.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

# **Over Recommended Commercial Operating Conditions**

|                              | -8 -7 -6                                                          |                        |         |         |          |           |          |           |           |

|------------------------------|-------------------------------------------------------------------|------------------------|---------|---------|----------|-----------|----------|-----------|-----------|

| Parameter                    | Description                                                       | Device                 | Min.    | Max.    | Min.     | Max.      | Min.     | Max.      | Units     |

| t <sub>HPLL</sub>            | Clock to Data Hold - PIO Input<br>Register                        | ECP3-70EA/95EA         | 0.7     | _       | 0.7      | _         | 0.8      | _         | ns        |

| t <sub>SU_DELPLL</sub>       | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-70EA/95EA         | 1.6     | _       | 1.8      | _         | 2.0      | _         | ns        |

| t <sub>H_DELPLL</sub>        | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-70EA/95EA         | 0.0     | _       | 0.0      | _         | 0.0      | _         | ns        |

| t <sub>COPLL</sub>           | Clock to Output - PIO Output<br>Register                          | ECP3-35EA              | _       | 3.2     | _        | 3.4       | _        | 3.6       | ns        |

| t <sub>SUPLL</sub>           | Clock to Data Setup - PIO Input<br>Register                       | ECP3-35EA              | 0.6     | _       | 0.7      | _         | 0.8      | _         | ns        |

| t <sub>HPLL</sub>            | Clock to Data Hold - PIO Input<br>Register                        | ECP3-35EA              | 0.3     | _       | 0.3      | _         | 0.4      | _         | ns        |

| t <sub>SU_DELPLL</sub>       | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-35EA              | 1.6     | _       | 1.7      | _         | 1.8      | _         | ns        |

| t <sub>H_DELPLL</sub>        | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-35EA              | 0.0     | _       | 0.0      | _         | 0.0      | _         | ns        |

| †COPLL                       | Clock to Output - PIO Output<br>Register                          | ECP3-17EA              | _       | 3.0     | _        | 3.3       | _        | 3.5       | ns        |

| tsupll                       | Clock to Data Setup - PIO Input<br>Register                       | ECP3-17EA              | 0.6     | _       | 0.7      | _         | 0.8      | _         | ns        |

| t <sub>HPLL</sub>            | Clock to Data Hold - PIO Input<br>Register                        | ECP3-17EA              | 0.3     | _       | 0.3      | _         | 0.4      | _         | ns        |

| t <sub>SU_DELPLL</sub>       | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-17EA              | 1.6     | _       | 1.7      | _         | 1.8      | _         | ns        |

| t <sub>H_DELPLL</sub>        | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | ECP3-17EA              | 0.0     | _       | 0.0      | _         | 0.0      | _         | ns        |

| Generic DDRX1 Input          | Inputs with Clock and Data (>10 Bit                               | s Wide) Centered at Pi | n (GDDF | RX1_RX. | SCLK.Ce  | ntered) l | Jsing PC | LK Pin fo | r Clock   |

| t <sub>SUGDDR</sub>          | Data Setup Before CLK                                             | All ECP3EA Devices     | 480     | _       | 480      | _         | 480      | _         | ps        |

| t <sub>HOGDDR</sub>          | Data Hold After CLK                                               | All ECP3EA Devices     | 480     | _       | 480      | _         | 480      | _         | ps        |

| f <sub>MAX GDDR</sub>        | DDRX1 Clock Frequency                                             | All ECP3EA Devices     | _       | 250     | _        | 250       | _        | 250       | MHz       |

| Generic DDRX1 Clock Input    | Inputs with Clock and Data (>10 Bit                               | s Wide) Aligned at Pin | (GDDR)  | (1_RX.S | CLK.PLL  | .Aligned) | Using P  | LLCLKIN   | l Pin for |

| Data Left, Right,            | and Top Sides and Clock Left and I                                | Right Sides            |         |         |          |           |          |           |           |

| t <sub>DVACLKGDDR</sub>      | Data Setup Before CLK                                             | All ECP3EA Devices     | _       | 0.225   | _        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub>      | Data Hold After CLK                                               | All ECP3EA Devices     | 0.775   | _       | 0.775    | _         | 0.775    | _         | UI        |

| f <sub>MAX_GDDR</sub>        | DDRX1 Clock Frequency                                             | All ECP3EA Devices     |         | 250     | _        | 250       | _        | 250       | MHz       |

| Generic DDRX1<br>Clock Input | Inputs with Clock and Data (>10 Bit                               | s Wide) Aligned at Pin | (GDDR)  | (1_RX.S | CLK.Alig | ned) Usi  | ng DLL - | CLKIN P   | in for    |

| Data Left, Right             | and Top Sides and Clock Left and F                                | light Sides            |         |         |          |           |          |           |           |

| t <sub>DVACLKGDDR</sub>      | Data Setup Before CLK                                             | All ECP3EA Devices     | _       | 0.225   | _        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub>      | Data Hold After CLK                                               | All ECP3EA Devices     | 0.775   | _       | 0.775    | _         | 0.775    | _         | UI        |

| f <sub>MAX_GDDR</sub>        | DDRX1 Clock Frequency                                             | All ECP3EA Devices     | _       | 250     | _        | 250       | _        | 250       | MHz       |

|                              | Inputs with Clock and Data (<10 Bit                               | s Wide) Centered at P  | n (GDDF | X1_RX.I | OQS.Cen  | tered) U  | sing DQ  | S Pin for | Clock     |

| t <sub>SUGDDR</sub>          | Data Setup After CLK                                              | All ECP3EA Devices     | 535     | _       | 535      |           | 535      | _         | ps        |

| t <sub>HOGDDR</sub>          | Data Hold After CLK                                               | All ECP3EA Devices     | 535     |         | 535      | _         | 535      | <u> </u>  | ps        |

| f <sub>MAX GDDR</sub>        | DDRX1 Clock Frequency                                             | All ECP3EA Devices     | _       | 250     | _        | 250       | _        | 250       | MHz       |

|                              | Inputs with Clock and Data (<10bits                               | wide) Aligned at Pin   | GDDRX   | I_RX.DQ | S.Aligne | d) Using  | DQS Pin  | for Cloc  | k Input   |

| Data and Clock I             | Left and Right Sides                                              |                        |         |         |          |           |          |           |           |

| † <sub>DVACLKGDDR</sub>      | Data Setup Before CLK                                             | All ECP3EA Devices     | _       | 0.225   | _        | 0.225     | _        | 0.225     | UI        |

| DIAGENGEDIT                  | '                                                                 |                        |         |         |          |           |          |           |           |

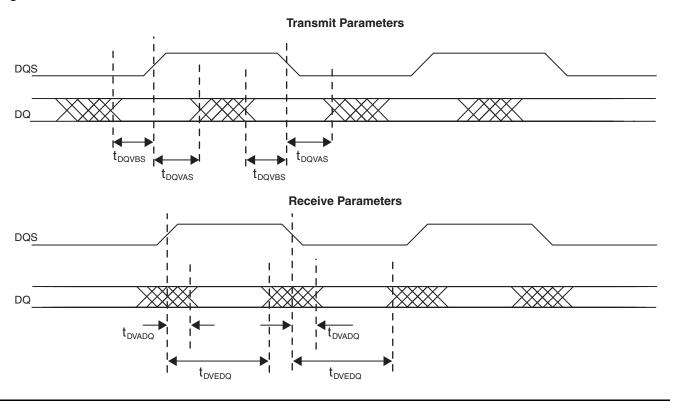

Figure 3-6. Generic DDRX1/DDRX2 (With Clock and Data Edges Aligned)

# CLK Data (TDAT, TCTL) Data (TDAT, TCTL) Tolagodr Tolagodr

**Transmit Parameters**

# RDTCLK Data (RDAT, RCTL) t<sub>DVACLKGDDR</sub> t<sub>DVECLKGDDR</sub>

Figure 3-7. DDR/DDR2/DDR3 Parameters

# **SERDES High-Speed Data Transmitter<sup>1</sup>**

Table 3-6. Serial Output Timing and Levels

| Symbol                                 | Description                                                  | Frequency          | Min.                       | Тур.                       | Max.                       | Units   |

|----------------------------------------|--------------------------------------------------------------|--------------------|----------------------------|----------------------------|----------------------------|---------|

| V <sub>TX-DIFF-P-P-1.44</sub>          | Differential swing (1.44 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1150                       | 1440                       | 1730                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.35</sub>          | Differential swing (1.35 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1080                       | 1350                       | 1620                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.26</sub>          | Differential swing (1.26 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1000                       | 1260                       | 1510                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.13</sub>          | Differential swing (1.13 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 840                        | 1130                       | 1420                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.04</sub>          | Differential swing (1.04 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 780                        | 1040                       | 1300                       | mV, p-p |

| V <sub>TX-DIFF-P-0.92</sub>            | Differential swing (0.92 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 690                        | 920                        | 1150                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.87</sub>          | Differential swing (0.87 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 650                        | 870                        | 1090                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.78</sub>          | Differential swing (0.78 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 585                        | 780                        | 975                        | mV, p-p |

| V <sub>TX-DIFF-P-P-0.64</sub>          | Differential swing (0.64 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 480                        | 640                        | 800                        | mV, p-p |

| V <sub>OCM</sub>                       | Output common mode voltage                                   | _                  | V <sub>CCOB</sub><br>-0.75 | V <sub>CCOB</sub><br>-0.60 | V <sub>CCOB</sub><br>-0.45 | V       |

| T <sub>TX-R</sub>                      | Rise time (20% to 80%)                                       | _                  | 145                        | 185                        | 265                        | ps      |

| T <sub>TX-F</sub>                      | Fall time (80% to 20%)                                       | _                  | 145                        | 185                        | 265                        | ps      |

| Z <sub>TX-OI-SE</sub>                  | Output Impedance 50/75/HiZ Ohms (single ended)               | _                  | -20%                       | 50/75/<br>Hi Z             | +20%                       | Ohms    |

| R <sub>LTX-RL</sub>                    | Return loss (with package)                                   | _                  | 10                         |                            |                            | dB      |

| T <sub>TX-INTRASKEW</sub>              | Lane-to-lane TX skew within a SERDES quad block (intra-quad) | _                  | _                          | _                          | 200                        | ps      |

| T <sub>TX-INTERSKEW</sub> <sup>3</sup> | Lane-to-lane skew between SERDES quad blocks (inter-quad)    | _                  | _                          | _                          | 1UI +200                   | ps      |

<sup>1.</sup> All measurements are with 50 Ohm impedance.

<sup>2.</sup> See TN1176, LatticeECP3 SERDES/PCS Usage Guide for actual binary settings and the min-max range.

<sup>3.</sup> Inter-quad skew is between all SERDES channels on the device and requires the use of a low skew internal reference clock.

# **SERDES High Speed Data Receiver**

Table 3-9. Serial Input Data Specifications

| Symbol                 | Description                                                  |         | Min. | Тур.      | Max.                               | Units   |  |

|------------------------|--------------------------------------------------------------|---------|------|-----------|------------------------------------|---------|--|

|                        |                                                              | 3.125 G | _    | _         | 136                                |         |  |

|                        |                                                              | 2.5 G   | _    | _         | 144                                |         |  |

| RX-CID <sub>S</sub>    | Stream of nontransitions <sup>1</sup>                        | 1.485 G | _    | _         | 160                                | Bits    |  |

| nx-cibs                | (CID = Consecutive Identical Digits) @ 10 <sup>-12</sup> BER | 622 M   | _    | _         | 204                                | Dita    |  |

|                        |                                                              | 270 M   | _    | _         | 228                                |         |  |

|                        |                                                              | 150 M   | _    | _         | 296                                |         |  |

| V <sub>RX-DIFF-S</sub> | Differential input sensitivity                               |         | 150  | _         | 1760                               | mV, p-p |  |

| $V_{RX-IN}$            | Input levels                                                 |         | 0    | _         | V <sub>CCA</sub> +0.5 <sup>4</sup> | V       |  |

| V <sub>RX-CM-DC</sub>  | Input common mode range (DC coupled)                         |         | 0.6  | _         | $V_{CCA}$                          | V       |  |

| V <sub>RX-CM-AC</sub>  | Input common mode range (AC coupled) <sup>3</sup>            |         | 0.1  | _         | V <sub>CCA</sub> +0.2              | V       |  |

| T <sub>RX-RELOCK</sub> | SCDR re-lock time <sup>2</sup>                               |         | _    | 1000      | _                                  | Bits    |  |

| Z <sub>RX-TERM</sub>   | Input termination 50/75 Ohm/High Z                           |         | -20% | 50/75/HiZ | +20%                               | Ohms    |  |

| RL <sub>RX-RL</sub>    | Return loss (without package)                                |         | 10   | _         | _                                  | dB      |  |

<sup>1.</sup> This is the number of bits allowed without a transition on the incoming data stream when using DC coupling.

# **Input Data Jitter Tolerance**

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

Table 3-10. Receiver Total Jitter Tolerance Specification

| Description   | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|---------------|------------|-------------------------|------|------|------|---------|

| Deterministic |            | 600 mV differential eye | _    | _    | 0.47 | UI, p-p |

| Random        | 3.125 Gbps | 600 mV differential eye | _    | _    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | _    | _    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | _    | _    | 0.47 | UI, p-p |

| Random        | 2.5 Gbps   | 600 mV differential eye | _    | _    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | _    | _    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | _    | _    | 0.47 | UI, p-p |

| Random        | 1.25 Gbps  | 600 mV differential eye | _    | _    | 0.18 | UI, p-p |

| Total         | 7          | 600 mV differential eye | _    | _    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | _    | _    | 0.47 | UI, p-p |

| Random        | 622 Mbps   | 600 mV differential eye | _    | _    | 0.18 | UI, p-p |

| Total         | 7          | 600 mV differential eye | _    | _    | 0.65 | UI, p-p |

Note: Values are measured with CJPAT, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

<sup>2.</sup> This is the typical number of bit times to re-lock to a new phase or frequency within +/- 300 ppm, assuming 8b10b encoded data.

<sup>3.</sup> AC coupling is used to interface to LVPECL and LVDS. LVDS interfaces are found in laser drivers and Fibre Channel equipment. LVDS interfaces are generally found in 622 Mbps SERDES devices.

<sup>4.</sup> Up to 1.76 V.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII/CPRI LV E.12 Electrical and Timing Characteristics

### **AC and DC Characteristics**

### Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 | _    | _    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | _    | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5 pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |      |      | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | _    | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100  | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          |      |      | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          | _    | _    | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _    | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | _    | 0.71 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _    | _    | UI    |

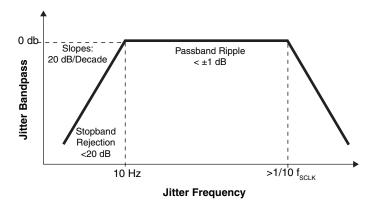

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

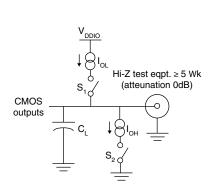

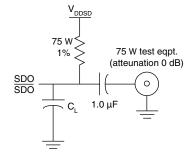

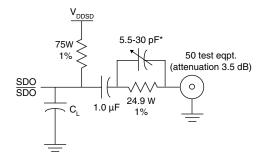

Figure 3-19. Test Loads

### **Test Loads**

$\mathbf{C_L}$  including probe and jig capacitance, 3 pF max.  $\mathbf{S_1}$  - open,  $\mathbf{S_2}$  - closed for  $\mathbf{V}_{\mathrm{OH}}$  measurement.  $\mathbf{S_1}$  - closed,  $\mathbf{S_2}$  - open for  $\mathbf{V}_{\mathrm{OL}}$  measurement.

\*Risetime compensation.

### **Timing Jitter Bandpass**

# **LatticeECP3 sysCONFIG Port Timing Specifications**

# **Over Recommended Operating Conditions**

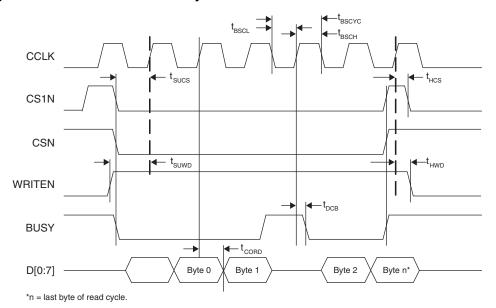

| Parameter            | Description                                                                                                                                    |                                    | Min. | Max.     | Units      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|----------|------------|

| POR, Confi           | guration Initialization, and Wakeup                                                                                                            |                                    |      |          |            |

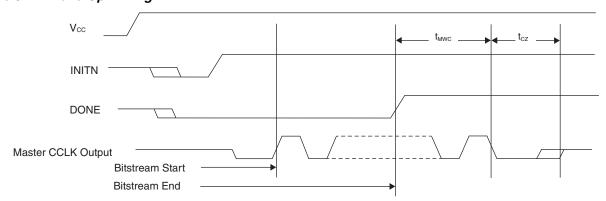

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode                        | _    | 23       | ms         |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode                         | _    | 6        | ms         |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           |                                    | _    | 5        | μs         |

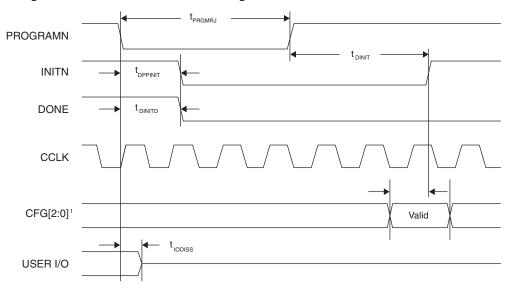

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       |                                    | 25   | _        | ns         |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                                    | _    | 10       | ns         |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                                    | _    | 37       | ns         |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       |                                    | _    | 37       | ns         |

| t <sub>DINIT</sub> 1 | PROGRAMN High to INITN High Delay                                                                                                              |                                    | _    | 1        | ms         |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                                    | 100  | 500      | cycles     |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                                    | _    | 300      | ns         |

| t <sub>IODISS</sub>  | User I/O Disable from PROGRAMN Low                                                                                                             |                                    | _    | 100      | ns         |

| t <sub>IOENSS</sub>  | User I/O Enabled Time from CCLK Edge During Wake-up Sequer                                                                                     | nce                                | _    | 100      | ns         |

| All Configu          | ration Modes                                                                                                                                   |                                    |      |          |            |

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                                    | 5    | _        | ns         |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                                    | 1    | _        | ns         |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          |                                    | -0.2 | 12       | ns         |

| Slave Seria          | I                                                                                                                                              |                                    |      |          |            |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                    | 5    | _        | ns         |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                    | 5    | _        | ns         |

|                      | CCLIV Francisco                                                                                                                                | Without encryption                 | _    | 33       | MHz        |

| TCCLK                | CCLK Frequency                                                                                                                                 | With encryption                    | _    | 20       | MHz        |

| Master and           | Slave Parallel                                                                                                                                 | •                                  |      |          |            |

| t <sub>SUCS</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                                    | 7    | _        | ns         |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                                    | 1    | _        | ns         |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                                    | 7    | _        | ns         |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                                    | 1    | _        | ns         |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                                    | _    | 12       | ns         |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      |                                    | _    | 12       | ns         |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                    | 6    | _        | ns         |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                    | 6    | _        | ns         |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                                    | 30   | _        | ns         |

| f <sub>CCLK</sub>    | CCLK/MCLK Frequency                                                                                                                            | Without encryption With encryption | _    | 33<br>20 | MHz<br>MHz |

| Master and           | Slave SPI                                                                                                                                      | 1                                  |      |          |            |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                                    |      | 80       | ns         |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       |                                    | 0.2  | 2        | μs         |

| t <sub>SOCDO</sub>   | MCLK Low to Output Valid                                                                                                                       |                                    | _    | 15       | ns         |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  |                                    | 0.3  |          | μs         |

| ייסרוט               |                                                                                                                                                | Without encryption                 | _    | 33       | MHz        |

| f <sub>CCLK</sub>    | CCLK Frequency                                                                                                                                 | With encryption                    | _    | 20       | MHz        |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                    | 5    | _        | ns         |

# **LatticeECP3 sysCONFIG Port Timing Specifications (Continued)**

# **Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>SSCL</sub> | CCLK Minimum Low Pulse                   | 5    | _    | ns    |

| t <sub>HLCH</sub> | HOLDN Low Setup Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | _    | 9    | ns    |

| $t_{HHQX}$        | HOLDN to Output Low-Z                    | _    | 9    | ns    |

<sup>1.</sup> Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of the PROGRAMN.

| Parameter              | Min.                 | Max.                 | Units |  |

|------------------------|----------------------|----------------------|-------|--|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |  |

| Duty Cycle             | 40                   | 60                   | %     |  |

Figure 3-20. sysCONFIG Parallel Port Read Cycle

Figure 3-26. Configuration from PROGRAMN Timing

1. The CFG pins are normally static (hard wired)

Figure 3-27. Wake-Up Timing

# **Signal Descriptions (Cont.)**

| Signal Name                           | I/O | Description                                                                       |  |

|---------------------------------------|-----|-----------------------------------------------------------------------------------|--|

| D7/SPID0                              | I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configuration. |  |

| DI/CSSPI0N/CEN                        | I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.               |  |

| Dedicated SERDES Signals <sup>3</sup> |     |                                                                                   |  |

| PCS[Index]_HDINNm                     | Į   | High-speed input, negative channel m                                              |  |

| PCS[Index]_HDOUTNm                    | 0   | High-speed output, negative channel m                                             |  |

| PCS[Index]_REFCLKN                    | Į   | Negative Reference Clock Input                                                    |  |

| PCS[Index]_HDINPm                     | I   | High-speed input, positive channel m                                              |  |

| PCS[Index]_HDOUTPm                    | 0   | High-speed output, positive channel m                                             |  |

| PCS[Index]_REFCLKP                    | I   | Positive Reference Clock Input                                                    |  |

| PCS[Index]_VCCOBm                     | —   | Output buffer power supply, channel m (1.2V/1.5)                                  |  |

| PCS[Index]_VCCIBm                     | _   | Input buffer power supply, channel m (1.2V/1.5V)                                  |  |

<sup>1.</sup> When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

<sup>2.</sup> These pins are dedicated inputs or can be used as general purpose I/O.

<sup>3.</sup> m defines the associated channel in the quad.

| Date                | Version                             | Section                                                                                                                               | Change Summary                                                                                                                                                  |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2009 01.4 | 01.4                                | Architecture                                                                                                                          | Corrected link in sysMEM Memory Block section.                                                                                                                  |

|                     |                                     |                                                                                                                                       | Updated information for On-Chip Programmable Termination and modified corresponding figure.                                                                     |

|                     |                                     | Added footnote 2 to On-Chip Programmable Termination Options for Input Modes table.                                                   |                                                                                                                                                                 |

|                     |                                     | Corrected Per Quadrant Primary Clock Selection figure.                                                                                |                                                                                                                                                                 |

|                     | DC and Switching<br>Characteristics | Modified -8 Timing data for 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers)                                      |                                                                                                                                                                 |

|                     |                                     | Added ESD Performance table.                                                                                                          |                                                                                                                                                                 |

|                     |                                     | LatticeECP3 External Switching Characteristics table - updated data for                                                               |                                                                                                                                                                 |

|                     |                                     | t <sub>DIBGDDR</sub> , t <sub>W_PRI</sub> , t <sub>W_EDGE</sub> and t <sub>SKEW_EDGE_DQS</sub> .                                      |                                                                                                                                                                 |

|                     |                                     | LatticeECP3 Internal Switching Characteristics table - updated data for $t_{\text{COO\_PIO}}$ and added footnote #4.                  |                                                                                                                                                                 |

|                     |                                     | sysCLOCK PLL Timing table - updated data for f <sub>OUT</sub> .                                                                       |                                                                                                                                                                 |

|                     |                                     | External Reference Clock Specification (refclkp/refclkn) table - updated data for $V_{\text{REF-IN-SE}}$ and $V_{\text{REF-IN-DIFF}}$ |                                                                                                                                                                 |

|                     |                                     | LatticeECP3 sysCONFIG Port Timing Specifications table - updated data for t <sub>MWC</sub> .                                          |                                                                                                                                                                 |

|                     |                                     | Added TRLVDS DC Specification table and diagram.                                                                                      |                                                                                                                                                                 |

|                     |                                     | Updated Mini LVDS table.                                                                                                              |                                                                                                                                                                 |

| August 2009         | 01.3                                | DC and Switching<br>Characteristics                                                                                                   | Corrected truncated numbers for $V_{\text{CCIB}}$ and $V_{\text{CCOB}}$ in Recommended Operating Conditions table.                                              |

| July 2009           | 01.2                                | Multiple                                                                                                                              | Changed references of "multi-boot" to "dual-boot" throughout the data sheet.                                                                                    |

|                     |                                     | Architecture                                                                                                                          | Updated On-Chip Programmable Termination bullets.                                                                                                               |

|                     |                                     |                                                                                                                                       | Updated On-Chip Termination Options for Input Modes table.                                                                                                      |

|                     |                                     |                                                                                                                                       | Updated On-Chip Termination figure.                                                                                                                             |

|                     |                                     | DC and Switching<br>Characteristics                                                                                                   | Changed min/max data for FREF_PPM and added footnote 4 in SERDES External Reference Clock Specification table.                                                  |

|                     |                                     |                                                                                                                                       | Updated SERDES minimum frequency.                                                                                                                               |

|                     |                                     | Pinout Information                                                                                                                    | Corrected MCLK to be I/O and CCLK to be I in Signal Descriptions table                                                                                          |

| May 2009            | 01.1                                | All                                                                                                                                   | Removed references to Parallel burst mode Flash.                                                                                                                |

|                     |                                     | Introduction                                                                                                                          | Features - Changed 250 Mbps to 230 Mbps in Embedded SERDES bulleted section and added a footnote to indicate 230 Mbps applies to 8b10b and 10b12b applications. |

|                     |                                     |                                                                                                                                       | Updated data for ECP3-17 in LatticeECP3 Family Selection Guide table.                                                                                           |

|                     |                                     |                                                                                                                                       | Changed embedded memory from 552 to 700 Kbits in LatticeECP3 Family Selection Guide table.                                                                      |

|                     |                                     | Architecture                                                                                                                          | Updated description for CLKFB in General Purpose PLL Diagram.                                                                                                   |

|                     |                                     |                                                                                                                                       | Corrected Primary Clock Sources text section.                                                                                                                   |

|                     |                                     |                                                                                                                                       | Corrected Secondary Clock/Control Sources text section.                                                                                                         |

|                     |                                     |                                                                                                                                       | Corrected Secondary Clock Regions table.                                                                                                                        |

|                     |                                     |                                                                                                                                       | Corrected note below Detailed sysDSP Slice Diagram.                                                                                                             |

|                     |                                     |                                                                                                                                       | Corrected Clock, Clock Enable, and Reset Resources text section.                                                                                                |

|                     |                                     |                                                                                                                                       | Corrected ECP3-17 EBR number in Embedded SRAM in the LatticeECP3 Family table.                                                                                  |

|                     |                                     |                                                                                                                                       | Added On-Chip Termination Options for Input Modes table.                                                                                                        |

|                     | 1                                   |                                                                                                                                       | Updated Available SERDES Quads per LatticeECP3 Devices table.                                                                                                   |