# E. Lattice Semiconductor Corporation - LFE3-150EA-8LFN672I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                         |

|--------------------------------|--------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 18625                                                                          |

| Number of Logic Elements/Cells | 149000                                                                         |

| Total RAM Bits                 | 7014400                                                                        |

| Number of I/O                  | 380                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                             |

| Package / Case                 | 672-BBGA                                                                       |

| Supplier Device Package        | 672-FPBGA (27x27)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-150ea-8lfn672i |

|                                |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

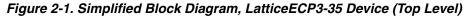

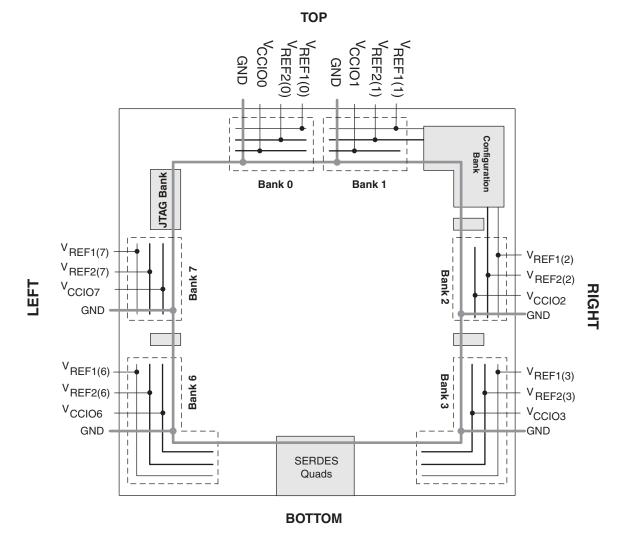

Note: There is no Bank 4 or Bank 5 in LatticeECP3 devices.

# **PFU Blocks**

The core of the LatticeECP3 device consists of PFU blocks, which are provided in two forms, the PFU and PFF. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices numbered 0-3 as shown in Figure 2-2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

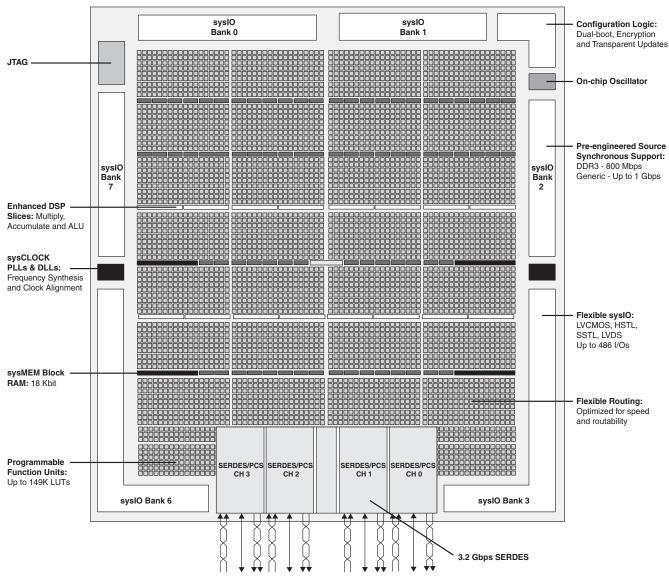

## **Edge Clock Sources**

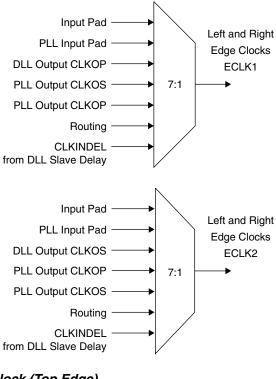

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs, DLLs, Slave Delay and clock dividers as shown in Figure 2-19.

Notes:

1. Clock inputs can be configured in differential or single ended mode.

2. The two DLLs can also drive the two top edge clocks.

3. The top left and top right PLL can also drive the two top edge clocks.

# Edge Clock Routing

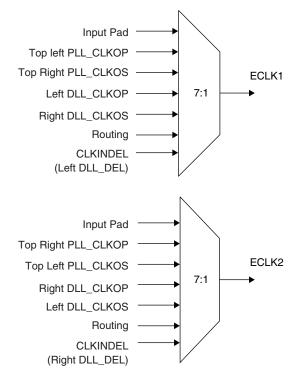

LatticeECP3 devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are six edge clocks per device: two edge clocks on each of the top, left, and right edges. Different PLL and DLL outputs are routed to the two muxes on the left and right sides of the device. In addition, the CLKINDEL signal (generated from the DLL Slave Delay Line block) is routed to all the edge clock muxes on the left and right sides of the device. Figure 2-20 shows the selection muxes for these clocks.

### Figure 2-20. Sources of Edge Clock (Left and Right Edges)

Figure 2-21. Sources of Edge Clock (Top Edge)

The edge clocks have low injection delay and low skew. They are used to clock the I/O registers and thus are ideal for creating I/O interfaces with a single clock signal and a wide data bus. They are also used for DDR Memory or Generic DDR interfaces.

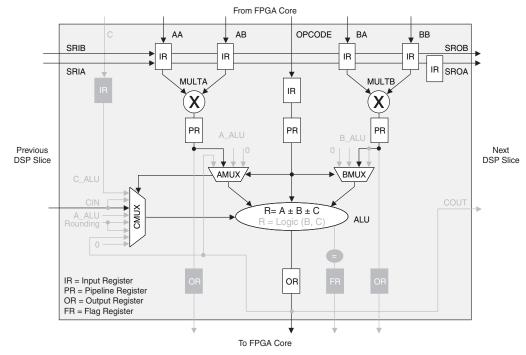

### Figure 2-31. MULTADDSUBSUM Slice 1

# Advanced sysDSP Slice Features

### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

## Addition

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

## Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- Rounding to infinity (RTI)

- Dynamic rounding

- Random rounding

- Convergent rounding

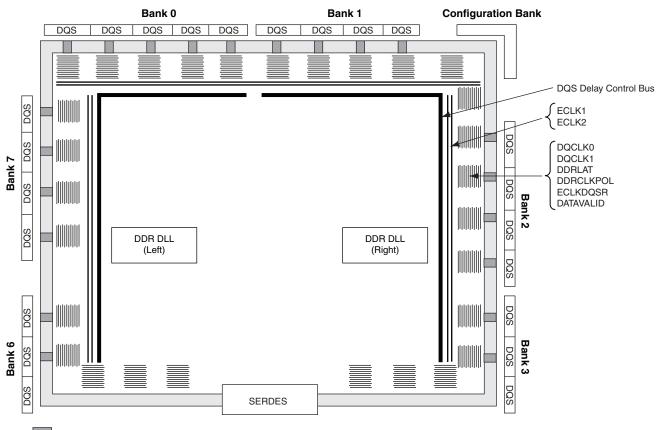

## **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces, a PLL is used for this adjustment. However, in DDR memories the clock (referred to as DQS) is not free-running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The delay required for the DQS signal is generated by two dedicated DLLs (DDR DLL) on opposite side of the device. Each DLL creates DQS delays in its half of the device as shown in Figure 2-36. The DDR DLL on the left side will generate delays for all the DQS Strobe pins on Banks 0, 7 and 6 and DDR DLL on the right will generate delays for all the DQS pins on Banks 1, 2 and 3. The DDR DLL loop compensates for temperature, voltage and process variations by using the system clock and DLL feedback loop. DDR DLL communicates the required delay to the DQS delay block using a 7-bit calibration bus (DCNTL[6:0])

The DQS signal (selected PIOs only, as shown in Figure 2-35) feeds from the PAD through a DQS control logic block to a dedicated DQS routing resource. The DQS control logic block consists of DQS Read Control logic block that generates control signals for the read side and DQS Write Control logic that generates the control signals required for the write side. A more detailed DQS control diagram is shown in Figure 2-37, which shows how the DQS control blocks interact with the data paths.

The DQS Read control logic receives the delay generated by the DDR DLL on its side and delays the incoming DQS signal by 90 degrees. This delayed ECLKDQSR is routed to 10 or 11 DQ pads covered by that DQS signal. This block also contains a polarity control logic that generates a DDRCLKPOL signal, which controls the polarity of the clock to the sync registers in the input register blocks. The DQS Read control logic also generates a DDRLAT signal that is in the input register block to transfer data from the first set of DDR register to the second set of DDR registers when using the DDRX2 gearbox mode for DDR3 memory interface.

The DQS Write control logic block generates the DQCLK0 and DQCLK1 clocks used to control the output gearing in the Output register block which generates the DDR data output and the DQS output. They are also used to control the generation of the DQS output through the DQS output register block. In addition to the DCNTL [6:0] input from the DDR DLL, the DQS Write control block also uses a Dynamic Delay DYN DEL [7:0] attribute which is used to further delay the DQS to accomplish the write leveling found in DDR3 memory. Write leveling is controlled by the DDR memory controller implementation. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock. This will generate the DQSW signal used to generate the DQS output in the DQS output register block.

Figure 2-36 and Figure 2-37 show how the DQS transition signals that are routed to the PIOs.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

#### Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

DQS Strobe and Transition Detect Logic

#### I/O Ring

\*Includes shared configuration I/Os and dedicated configuration I/Os.

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on DDR Memory interface implementation in LatticeECP3.

# sysl/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

### sysl/O Buffer Banks

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , which allow it to be completely independent from the others. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

## Figure 2-38. LatticeECP3 Banks

LatticeECP3 devices contain two types of sysI/O buffer pairs.

#### 1. Top (Bank 0 and Bank 1) and Bottom sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysl/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input. Only the top edge buffers have a programmable PCI clamp.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

The top and bottom sides are ideal for general purpose I/O, PCI, and inputs for LVDS (LVDS outputs are only allowed on the left and right sides). The top side can be used for the DDR3 ADDR/CMD signals.

The I/O pins located on the top and bottom sides of the device (labeled PTxxA/B or PBxxA/B) are fully hot socketable. Note that the pads in Banks 3, 6 and 8 are wrapped around the corner of the device. In these banks, only the pads located on the top or bottom of the device are hot socketable. The top and bottom side pads can be identified by the Lattice Diamond tool.

# 2. Left and Right (Banks 2, 3, 6 and 7) sysl/O Buffer Pairs (50% Differential and 100% Single-Ended Outputs)

The sysl/O buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

In addition, programmable on-chip input termination (parallel or differential, static or dynamic) is supported on these sides, which is required for DDR3 interface. However, there is no support for hot-socketing for the I/O pins located on the left and right side of the device as the PCI clamp is always enabled on these pins.

LVDS, RSDS, PPLVDS and Mini-LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

# 3. Configuration Bank sysl/O Buffer Pairs (Single-Ended Outputs, Only on Shared Pins When Not Used by Configuration)

The sysl/O buffers in the Configuration Bank consist of ratioed single-ended output drivers and single-ended input buffers. This bank does not support PCI clamp like the other banks on the top, left, and right sides.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Programmable PCI clamps are only available on the top banks. PCI clamps are used primarily on inputs and bidirectional pads to reduce ringing on the receiving end.

# Typical sysI/O I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $V_{CCIO8}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. For more information about controlling the output logic state with valid input logic levels during power-up in LatticeECP3 devices, see the list of technical documentation at the end of this data sheet.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

# Supported sysl/O Standards

The LatticeECP3 sysl/O buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, slew rates, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, BLVDS, LVPECL, MLVDS, RSDS, Mini-LVDS, PPLVDS (point-to-point LVDS), TRLVDS (Transition Reduced LVDS), differential SSTL and differential HSTL. For further information on utilizing the sysl/O buffer to support a variety of standards please see TN1177, LatticeECP3 syslO Usage Guide.

# Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol  | Parameter                    | Condition                                 | Min. | Тур. | Max. | Units |

|---------|------------------------------|-------------------------------------------|------|------|------|-------|

| IDK_HS⁴ | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH}$ (Max.)          |      |      | +/-1 | mA    |

| IDK⁵    | Input or I/O Leakage Current | $0 \le V_{IN} < V_{CCIO}$                 |      |      | +/-1 | mA    |

|         |                              | $V_{CCIO} \le V_{IN} \le V_{CCIO} + 0.5V$ | _    | 18   | _    | mA    |

1.  $V_{CC},\,V_{CCAUX}$  and  $V_{CCIO}$  should rise/fall monotonically.

2.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

3. LVCMOS and LVTTL only.

4. Applicable to general purpose I/O pins located on the top and bottom sides of the device.

5. Applicable to general purpose I/O pins located on the left and right sides of the device.

# Hot Socketing Requirements<sup>1, 2</sup>

| Description                                                                     |   | Тур. | Max. | Units |

|---------------------------------------------------------------------------------|---|------|------|-------|

| Input current per SERDES I/O pin when device is powered down and inputs driven. | _ | -    | 8    | mA    |

1. Assumes the device is powered down, all supplies grounded, both P and N inputs driven by CML driver with maximum allowed VCCOB (1.575 V), 8b10b data, internal AC coupling.

2. Each P and N input must have less than the specified maximum input current. For a 16-channel device, the total input current would be 8 mA\*16 channels \*2 input pins per channel = 256 mA

# **ESD** Performance

Please refer to the LatticeECP3 Product Family Qualification Summary for complete qualification data, including ESD performance.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | -8 -7 -6                                                       |                                                                                                             |                                                     |                                                                                                         |                                                                         |                                                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Parameter                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min.                                                                            | Max.                                                           | Min.                                                                                                        | Max.                                                | Min.                                                                                                    | Max.                                                                    | Units                                                                                     |  |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.6                                                                             |                                                                | 1.8                                                                                                         |                                                     | 2.0                                                                                                     |                                                                         | ns                                                                                        |  |

|                                                                                                                                                                                                                                                                                         | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |  |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.2                                                            | _                                                                                                           | 3.4                                                 | _                                                                                                       | 3.6                                                                     | ns                                                                                        |  |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             |                                                                | 1.7                                                                                                         |                                                     | 1.8                                                                                                     |                                                                         | ns                                                                                        |  |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                   | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |  |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.0                                                            | _                                                                                                           | 3.3                                                 | _                                                                                                       | 3.5                                                                     | ns                                                                                        |  |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             | _                                                              | 1.7                                                                                                         | _                                                   | 1.8                                                                                                     | _                                                                       | ns                                                                                        |  |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                   | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             | _                                                              | 0.0                                                                                                         | _                                                   | 0.0                                                                                                     | _                                                                       | ns                                                                                        |  |

| Input                                                                                                                                                                                                                                                                                   | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ns                                                                                        |  |

|                                                                                                                                                                                                                                                                                         | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ps                                                                                        |  |

| tHOGDDR                                                                                                                                                                                                                                                                                 | Data Hald After OLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             |                                                                | 400                                                                                                         |                                                     |                                                                                                         |                                                                         |                                                                                           |  |

|                                                                                                                                                                                                                                                                                         | Data Hold After CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                             |                                                                | 480                                                                                                         | —                                                   | 480                                                                                                     |                                                                         | · ·                                                                                       |  |

| fMAX GDDB                                                                                                                                                                                                                                                                               | Data Hold After CLK<br>DDRX1 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                             | 250                                                            | 480                                                                                                         | <br>250                                             | 480                                                                                                     | —<br>250                                                                | ps<br>MHz                                                                                 |  |

| Clock Input                                                                                                                                                                                                                                                                             | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                               |                                                                | —                                                                                                           |                                                     | —                                                                                                       |                                                                         | ps<br>MHz                                                                                 |  |

| Generic DDRX1  <br>Clock Input                                                                                                                                                                                                                                                          | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                               | (1_RX.S0                                                       | —                                                                                                           | Aligned)                                            | —                                                                                                       | LLCLKIN                                                                 | ps<br>MHz<br>Pin for                                                                      |  |

| Generic DDRX1  <br>Clock Input                                                                                                                                                                                                                                                          | DDRX1 Clock Frequency Inputs with Clock and Data (>10 Bit and Top Sides and Clock Left and Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br>(GDDR)<br>                                                                  |                                                                | —<br>CLK.PLL.                                                                                               | <b>Aligned)</b><br>0.225                            | Using P                                                                                                 |                                                                         | ps<br>MHz<br>Pin for                                                                      |  |

| Generic DDRX1  <br>Clock Input<br>Data Left, Right,                                                                                                                                                                                                                                     | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                               | 0.225                                                          | —                                                                                                           | Aligned) 0.225                                      | —                                                                                                       | 0.225                                                                   | ps<br>MHz<br>Pin for                                                                      |  |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br><sup>t</sup> DVECLKGDDR<br>f <sub>MAX_GDDR</sub>                                                                                                                                                      | DDRX1 Clock Frequency<br>nputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |  |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br><sup>t</sup> DVECLKGDDR<br>f <sub>MAX_GDDR</sub><br>Generic DDRX1 I<br>Clock Input                                                                                                                    | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |  |