Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                               |

|--------------------------------|-------------------------------------------------------------------------------|

| Product Status                 | Active                                                                        |

| Number of LABs/CLBs            | 2125                                                                          |

| Number of Logic Elements/Cells | 17000                                                                         |

| Total RAM Bits                 | 716800                                                                        |

| Number of I/O                  | 133                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 256-BGA                                                                       |

| Supplier Device Package        | 256-FTBGA (17x17)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-17ea-7ftn256c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Introduction

February 2012 Data Sheet DS1021

#### **Features**

#### Higher Logic Density for Increased System Integration

- 17K to 149K LUTs

- 116 to 586 I/Os

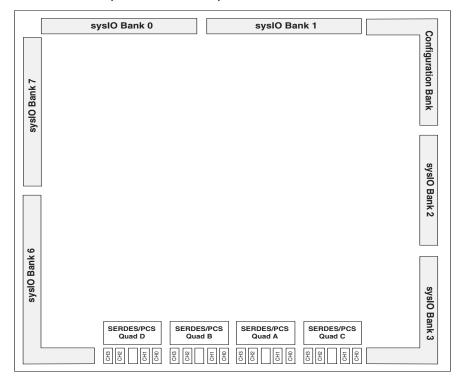

#### **■** Embedded SERDES

- 150 Mbps to 3.2 Gbps for Generic 8b10b, 10-bit SERDES, and 8-bit SERDES modes

- Data Rates 230 Mbps to 3.2 Gbps per channel for all other protocols

- Up to 16 channels per device: PCI Express, SONET/SDH, Ethernet (1GbE, SGMII, XAUI), CPRI, SMPTE 3G and Serial RapidIO

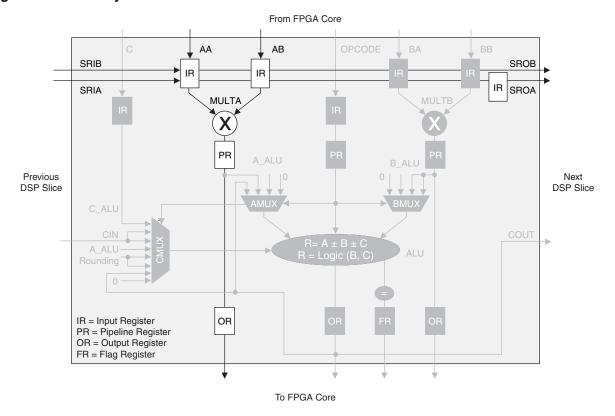

#### ■ sysDSP™

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- · Time Division Multiplexing MAC Sharing

- · Rounding and truncation

- · Each slice supports

- Half 36x36, two 18x18 or four 9x9 multipliers

- Advanced 18x36 MAC and 18x18 Multiply-Multiply-Accumulate (MMAC) operations

#### **■** Flexible Memory Resources

- Up to 6.85Mbits sysMEM™ Embedded Block RAM (EBR)

- 36K to 303K bits distributed RAM

#### sysCLOCK Analog PLLs and DLLs

Two DLLs and up to ten PLLs per device

#### ■ Pre-Engineered Source Synchronous I/O

• DDR registers in I/O cells

#### Table 1-1. LatticeECP3™ Family Selection Guide

- · Dedicated read/write levelling functionality

- Dedicated gearing logic

- Source synchronous standards support

- ADC/DAC, 7:1 LVDS, XGMII

- High Speed ADC/DAC devices

- Dedicated DDR/DDR2/DDR3 memory with DQS support

- Optional Inter-Symbol Interference (ISI) correction on outputs

#### ■ Programmable sysl/O<sup>™</sup> Buffer Supports Wide Range of Interfaces

- On-chip termination

- · Optional equalization filter on inputs

- LVTTL and LVCMOS 33/25/18/15/12

- SSTL 33/25/18/15 I, II

- HSTL15 I and HSTL18 I, II

- · PCI and Differential HSTL, SSTL

- LVDS. Bus-LVDS. LVPECL. RSDS. MLVDS

#### **■** Flexible Device Configuration

- Dedicated bank for configuration I/Os

- · SPI boot flash interface

- · Dual-boot images supported

- Slave SPI

- TransFR™ I/O for simple field updates

- Soft Error Detect embedded macro

#### ■ System Level Support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- ORCAstra FPGA configuration utility

- On-chip oscillator for initialization & general use

- 1.2 V core power supply

| Device                       | ECP3-17            | ECP3-35 | ECP3-70  | ECP3-95  | ECP3-150 |

|------------------------------|--------------------|---------|----------|----------|----------|

| LUTs (K)                     | 17                 | 33      | 67       | 92       | 149      |

| sysMEM Blocks (18 Kbits)     | 38                 | 72      | 240      | 240      | 372      |

| Embedded Memory (Kbits)      | 700                | 1327    | 4420     | 4420     | 6850     |

| Distributed RAM Bits (Kbits) | 36                 | 68      | 145      | 188      | 303      |

| 18 x 18 Multipliers          | 24                 | 64      | 128      | 128      | 320      |

| SERDES (Quad)                | 1                  | 1       | 3        | 3        | 4        |

| PLLs/DLLs                    | 2/2                | 4/2     | 10 / 2   | 10 / 2   | 10 / 2   |

| Packages and SERDES Channels | s/ I/O Combination | าร      |          |          |          |

| 328 csBGA (10 x 10 mm)       | 2/116              |         |          |          |          |

| 256 ftBGA (17 x 17 mm)       | 4 / 133            | 4 / 133 |          |          |          |

| 484 fpBGA (23 x 23 mm)       | 4 / 222            | 4 / 295 | 4 / 295  | 4 / 295  |          |

| 672 fpBGA (27 x 27 mm)       |                    | 4/310   | 8 / 380  | 8 / 380  | 8 / 380  |

| 1156 fpBGA (35 x 35 mm)      |                    |         | 12 / 490 | 12 / 490 | 16 / 586 |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

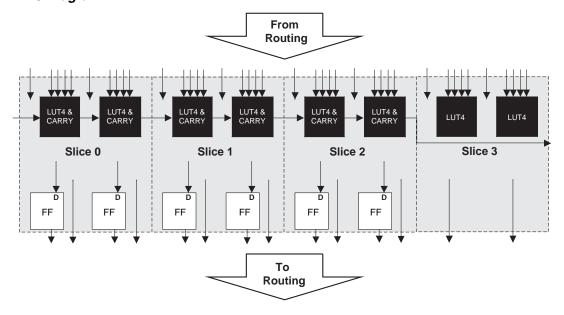

Figure 2-2. PFU Diagram

#### Slice

Slice 0 through Slice 2 contain two LUT4s feeding two registers, whereas Slice 3 contains two LUT4s only. For PFUs, Slice 0 through Slice 2 can be configured as distributed memory, a capability not available in the PFF. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions.

Table 2-1. Resources and Modes Available per Slice

|         | PFU E                   | BLock                   | PFF E                   | Block              |

|---------|-------------------------|-------------------------|-------------------------|--------------------|

| Slice   | Resources               | Modes                   | Resources               | Modes              |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |

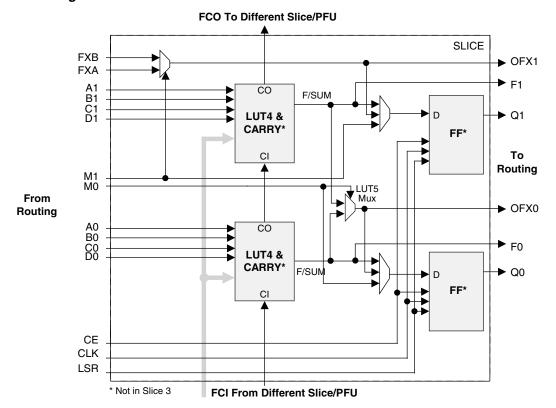

Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Slices 0, 1 and 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 10 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

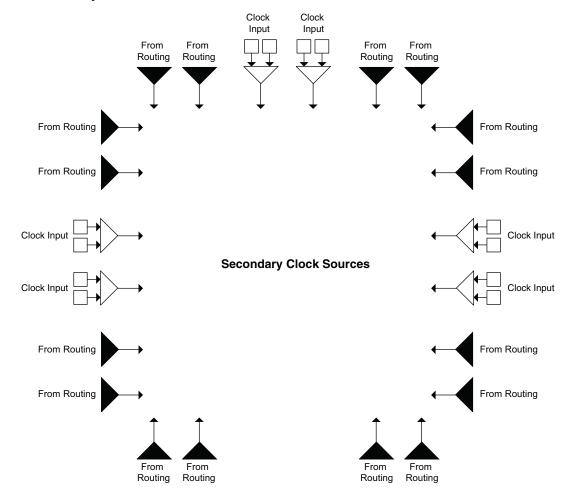

#### **Secondary Clock/Control Sources**

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for the clock.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7.

Figure 2-14. Secondary Clock Sources

Note: Clock inputs can be configured in differential or single-ended mode.

## Secondary Clock/Control Routing

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight secondary clock resources per region (SC0 to SC7). The same secondary clock routing can be used for control signals.

For further information, please refer to TN1182, LatticeECP3 sysDSP Usage Guide.

#### **MULT DSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, AA and AB, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-26 shows the MULT sysDSP element.

Figure 2-26. MULT sysDSP Element

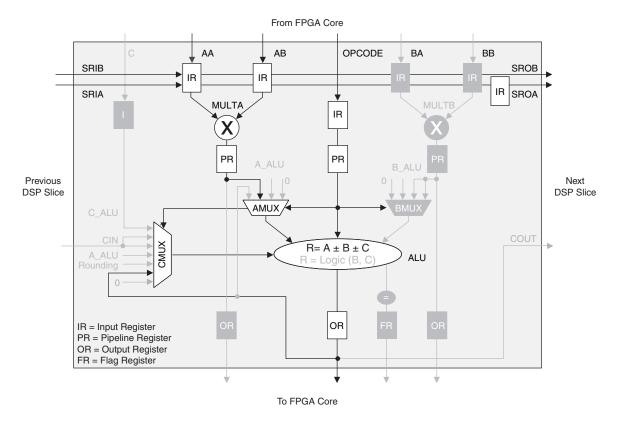

#### **MAC DSP Element**

In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice in the LatticeECP3 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-27 shows the MAC sysDSP element.

Figure 2-27. MAC DSP Element

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-32. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as LVDS inputs.

Table 2-11. PIO Signal List

| Name                                                     | Туре                          | Description                                                                                                                                                                                                                                       |

|----------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDD                                                     | Input Data                    | Register bypassed input. This is not the same port as INCK.                                                                                                                                                                                       |

| IPA, INA, IPB, INB                                       | Input Data                    | Ports to core for input data                                                                                                                                                                                                                      |

| OPOSA, ONEGA <sup>1</sup> ,<br>OPOSB, ONEGB <sup>1</sup> | Output Data                   | Output signals from core. An exception is the ONEGB port, used for tristate logic at the DQS pad.                                                                                                                                                 |

| CE                                                       | PIO Control                   | Clock enables for input and output block flip-flops.                                                                                                                                                                                              |

| SCLK                                                     | PIO Control                   | System Clock (PCLK) for input and output/TS blocks. Connected from clock ISB.                                                                                                                                                                     |

| LSR                                                      | PIO Control                   | Local Set/Reset                                                                                                                                                                                                                                   |

| ECLK1, ECLK2                                             | PIO Control                   | Edge clock sources. Entire PIO selects one of two sources using mux.                                                                                                                                                                              |

| ECLKDQSR <sup>1</sup>                                    | Read Control                  | From DQS_STROBE, shifted strobe for memory interfaces only.                                                                                                                                                                                       |

| DDRCLKPOL <sup>1</sup>                                   | Read Control                  | Ensures transfer from DQS domain to SCLK domain.                                                                                                                                                                                                  |

| DDRLAT <sup>1</sup>                                      | Read Control                  | Used to guarantee INDDRX2 gearing by selectively enabling a D-Flip-Flop in datapath.                                                                                                                                                              |

| DEL[3:0]                                                 | Read Control                  | Dynamic input delay control bits.                                                                                                                                                                                                                 |

| INCK                                                     | To Clock Distribution and PLL | PIO treated as clock PIO, path to distribute to primary clocks and PLL.                                                                                                                                                                           |

| TS                                                       | Tristate Data                 | Tristate signal from core (SDR)                                                                                                                                                                                                                   |

| DQCLK0 <sup>1</sup> , DQCLK1 <sup>1</sup>                | Write Control                 | Two clocks edges, 90 degrees out of phase, used in output gearing.                                                                                                                                                                                |

| DQSW <sup>2</sup>                                        | Write Control                 | Used for output and tristate logic at DQS only.                                                                                                                                                                                                   |

| DYNDEL[7:0]                                              | Write Control                 | Shifting of write clocks for specific DQS group, using 6:0 each step is approximately 25ps, 128 steps. Bit 7 is an invert (timing depends on input frequency). There is also a static control for this 8-bit setting, enabled with a memory cell. |

| DCNTL[6:0]                                               | PIO Control                   | Original delay code from DDR DLL                                                                                                                                                                                                                  |

| DATAVALID <sup>1</sup>                                   | Output Data                   | Status flag from DATAVALID logic, used to indicate when input data is captured in IOLOGIC and valid to core.                                                                                                                                      |

| READ                                                     | For DQS_Strobe                | Read signal for DDR memory interface                                                                                                                                                                                                              |

| DQSI                                                     | For DQS_Strobe                | Unshifted DQS strobe from input pad                                                                                                                                                                                                               |

| PRMBDET                                                  | For DQS_Strobe                | DQSI biased to go high when DQSI is tristate, goes to input logic block as well as core logic.                                                                                                                                                    |

| GSRN                                                     | Control from routing          | Global Set/Reset                                                                                                                                                                                                                                  |

<sup>1.</sup> Signals available on left/right/top edges only.

#### PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

#### **Input Register Block**

The input register blocks for the PIOs, in the left, right and top edges, contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-33 shows the input register block for the left, right and top edges. The input register block for the bottom edge contains one element to register the input signal and no DDR registers. The following description applies to the input register block for PIOs in the left, right and top edges only.

<sup>2.</sup> Selected PIO.

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                     | Data Rate<br>(Mbps)                    | Number of<br>General/Link Width | Encoding Style |  |

|------------------------------------------------------------------------------|----------------------------------------|---------------------------------|----------------|--|

| PCI Express 1.1                                                              | 2500                                   | x1, x2, x4                      | 8b10b          |  |

| Gigabit Ethernet                                                             | 1250, 2500                             | x1                              | 8b10b          |  |

| SGMII                                                                        | 1250                                   | x1                              | 8b10b          |  |

| XAUI                                                                         | 3125                                   | x4                              | 8b10b          |  |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                 | x1, x4                          | 8b10b          |  |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0 | 1228.8,<br>2457.6,              |                |  |

| SD-SDI<br>(259M, 344M)                                                       | - 2/0                                  |                                 | NRZI/Scrambled |  |

| HD-SDI<br>(292M)                                                             | 1483.5,<br>1485                        | x1                              | NRZI/Scrambled |  |

| 3G-SDI<br>(424M)                                                             | 2967,<br>2970                          | x1                              | NRZI/Scrambled |  |

| SONET-STS-3 <sup>2</sup>                                                     | 155.52                                 | x1                              | N/A            |  |

| SONET-STS-12 <sup>2</sup>                                                    | 622.08                                 | x1                              | N/A            |  |

| SONET-STS-48 <sup>2</sup>                                                    | 2488                                   | x1                              | N/A            |  |

<sup>1.</sup> For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

<sup>2.</sup> The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33³             |

| 9.2              |                 |

- 1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

- 2. Maximum MCCLK with encryption enabled.

- 3. Maximum MCCLK without encryption.

## **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

## **DC Electrical Characteristics**

### **Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                | Condition                                                                                                                                                   | Min.           | Тур. | Max.                  | Units |

|---------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2 \text{ V})$                                                                                                               | _              | _    | 10                    | μΑ    |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                | $(V_{CCIO} - 0.2 \text{ V}) < V_{IN} \le 3.6 \text{ V}$                                                                                                     | _              | _    | 150                   | μΑ    |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                                                                                             | -30            | _    | -210                  | μΑ    |

| $I_{PD}$                                          | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{CCIO}$                                                                                                                      | 30             | _    | 210                   | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                     | 30             | _    | _                     | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                                     | -30            | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | _              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | _              | _    | -210                  | μΑ    |

| $V_{BHT}$                                         | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                                                                                             | $V_{IL}$ (MAX) | _    | V <sub>IH</sub> (MIN) | >     |

| C1                                                | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _              | 5    | 8                     | pf    |

| C2                                                | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _              | 5    | 7                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup>  $T_A$  25 °C, f = 1.0 MHz.

Applicable to general purpose I/Os in top and bottom banks.

When used as V<sub>REF</sub> maximum leakage= 25 μA.

# sysI/O Single-Ended DC Electrical Characteristics

| Input/Output  | $V_{IL}$ |                          | V <sub>IḤ</sub>                       |          | V <sub>OL</sub>       | v <sub>oh</sub>          |                        |                                   |

|---------------|----------|--------------------------|---------------------------------------|----------|-----------------------|--------------------------|------------------------|-----------------------------------|

|               | Min. (V) | Max. (V)                 | Min. (V)                              | Max. (V) | Max. (V)              | Min. (V)                 | l <sub>OL</sub> 1 (mA) | I <sub>OH</sub> <sup>1</sup> (mA) |

| LVCMOS33      | -0.3     | 0.8                      | 2.0                                   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|               |          |                          |                                       |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS25      | -0.3     | 0.7                      | 1.7                                   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|               |          |                          |                                       |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS18      | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>                | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16, 12,<br>8, 4        | -16, -12,<br>-8, -4               |

|               |          |                          |                                       |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS15      | -0.3     | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>                | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8, 4                   | -8, -4                            |

| LVOIVIOOTO    | 0.0      | 0.00 4.0010              | 0.03 4 (CCIO                          | 0.0      | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVCMOS12      | -0.3     | 0.35 V <sub>CC</sub>     | 0.65 V <sub>CC</sub>                  | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6, 2                   | -6, -2                            |

| LVOIVIOOTZ    | -0.5     | 0.55 400                 | 0.03 ACC                              | 0.0      | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| LVTTL33       | -0.3     | 0.8                      | 2.0                                   | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |

|               |          |                          |                                       |          | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |

| PCI33         | -0.3     | 0.3 V <sub>CCIO</sub>    | 0.5 V <sub>CCIO</sub>                 | 3.6      | 0.1 V <sub>CCIO</sub> | 0.9 V <sub>CCIO</sub>    | 1.5                    | -0.5                              |

| SSTL18_I      | -0.3     | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125              | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6.7                    | -6.7                              |

| SSTL18_II     | -0.3     | V 0.125                  | V . 0.105                             | 3.6      | 0.28                  | V 0.29                   | 8                      | -8                                |

| (DDR2 Memory) | -0.3     | VREF - 0.123             | V <sub>REF</sub> + 0.125              | 3.0      | 0.20                  | V <sub>CCIO</sub> - 0.28 | 11                     | -11                               |

| SSTL2_I       | -0.3     | V 0.19                   | V .019                                | 3.6      | 0.54                  | V 0.62                   | 7.6                    | -7.6                              |

| 331L2_I       | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18               | 3.0      | 0.54                  | V <sub>CCIO</sub> - 0.62 | 12                     | -12                               |

| SSTL2_II      | -0.3     | V 0.19                   | V .019                                | 3.6      | 0.35                  | V 0.43                   | 15.2                   | -15.2                             |

| (DDR Memory)  | -0.3     | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18               | 3.0      | 0.33                  | V <sub>CCIO</sub> - 0.43 | 20                     | -20                               |

| SSTL3_I       | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2                | 3.6      | 0.7                   | V <sub>CCIO</sub> - 1.1  | 8                      | -8                                |

| SSTL3_II      | -0.3     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2                | 3.6      | 0.5                   | V <sub>CCIO</sub> - 0.9  | 16                     | -16                               |

| SSTL15        | 0.0      | V 0.1                    | V .01                                 | 0.6      | 0.0                   | V <sub>CCIO</sub> - 0.3  | 7.5                    | -7.5                              |

| (DDR3 Memory) | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1                | 3.6      | 0.3                   | V <sub>CCIO</sub> * 0.8  | 9                      | -9                                |

| HOTI 15 I     | 0.0      | V 0.1                    | V .01                                 | 0.6      | 0.4                   | V 0.4                    | 4                      | -4                                |

| HSTL15_I      | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1                | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |

| HCTI 10 I     | 0.0      | V 0.1                    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 0.6      | 0.4                   | V 0.4                    | 8                      | -8                                |

| HSTL18_I      | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1                | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 12                     | -12                               |

| HSTL18_II     | -0.3     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1                | 3.6      | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16                     | -16                               |

<sup>1.</sup> For electromigration, the average DC current drawn by I/O pads between two consecutive V<sub>CCIO</sub> or GND pad connections, or between the last V<sub>CCIO</sub> or GND in an I/O bank and the end of an I/O bank, as shown in the Logic Signal Connections table (also shown as I/O grouping) shall not exceed n \* 8 mA, where n is the number of I/O pads between the two consecutive bank V<sub>CCIO</sub> or GND connections or between the last V<sub>CCIO</sub> and GND in a bank and the end of a bank. IO Grouping can be found in the Data Sheet Pin Tables, which can also be generated from the Lattice Diamond software.

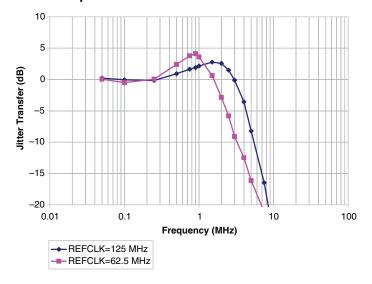

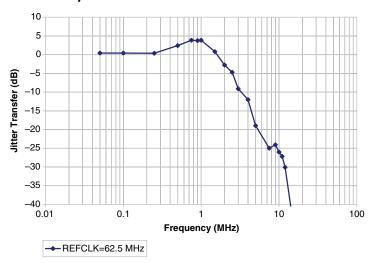

Figure 3-16. Jitter Transfer – 1.25 Gbps

Figure 3-17. Jitter Transfer - 622 Mbps

# **PCI Express Electrical and Timing Characteristics AC and DC Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                   | Description                                                                           | <b>Test Conditions</b>                                 | Min               | Тур  | Max                    | Units |

|------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|------------------------|-------|

| Transmit <sup>1</sup>                    |                                                                                       | l                                                      | <u> </u>          |      | l                      |       |

| UI                                       | Unit interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>TX-DIFF_P-P</sub>                 | Differential peak-to-peak output voltage                                              |                                                        | 0.8               | 1.0  | 1.2                    | V     |

| V <sub>TX-DE-RATIO</sub>                 | De-emphasis differential output voltage ratio                                         |                                                        | -3                | -3.5 | -4                     | dB    |

| V <sub>TX-CM-AC_P</sub>                  | RMS AC peak common-mode output voltage                                                |                                                        | _                 | _    | 20                     | mV    |

| V <sub>TX-RCV-DETECT</sub>               | Amount of voltage change allowed during receiver detection                            |                                                        | _                 | _    | 600                    | mV    |

| V <sub>TX-DC-CM</sub>                    | Tx DC common mode voltage                                                             |                                                        | 0                 | _    | V <sub>CCOB</sub> + 5% | V     |

| I <sub>TX-SHORT</sub>                    | Output short circuit current                                                          | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | _                 | _    | 90                     | mA    |

| Z <sub>TX-DIFF-DC</sub>                  | Differential output impedance                                                         |                                                        | 80                | 100  | 120                    | Ohms  |

| RL <sub>TX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | _    | _                      | dB    |

| RL <sub>TX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | _    | _                      | dB    |

| T <sub>TX-RISE</sub>                     | Tx output rise time                                                                   | 20 to 80%                                              | 0.125             | _    | _                      | UI    |

| T <sub>TX-FALL</sub>                     | Tx output fall time                                                                   | 20 to 80%                                              | 0.125             | _    | _                      | UI    |

| L <sub>TX-SKEW</sub>                     | Lane-to-lane static output skew for all lanes in port/link                            |                                                        | _                 | _    | 1.3                    | ns    |

| T <sub>TX-EYE</sub>                      | Transmitter eye width                                                                 |                                                        | 0.75              | _    | _                      | UI    |

| T <sub>TX-EYE-MEDIAN-TO-MAX-JITTER</sub> | Maximum time between jitter median and maximum deviation from median                  |                                                        | _                 | _    | 0.125                  | UI    |

| Receive <sup>1, 2</sup>                  |                                                                                       | •                                                      |                   |      | •                      |       |

| UI                                       | Unit Interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>RX-DIFF_P-P</sub>                 | Differential peak-to-peak input voltage                                               |                                                        | 0.34 <sup>3</sup> | _    | 1.2                    | V     |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>        | Idle detect threshold voltage                                                         |                                                        | 65                | _    | 340 <sup>3</sup>       | mV    |

| V <sub>RX-CM-AC_P</sub>                  | Receiver common mode voltage for AC coupling                                          |                                                        | _                 | _    | 150                    | mV    |

| Z <sub>RX-DIFF-DC</sub>                  | DC differential input impedance                                                       |                                                        | 80                | 100  | 120                    | Ohms  |

| Z <sub>RX-DC</sub>                       | DC input impedance                                                                    |                                                        | 40                | 50   | 60                     | Ohms  |

| Z <sub>RX-HIGH-IMP-DC</sub>              | Power-down DC input impedance                                                         |                                                        | 200K              | _    | _                      | Ohms  |

| RL <sub>RX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | _    | _                      | dB    |

| RL <sub>RX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | _    | _                      | dB    |

| T <sub>RX-IDLE-DET-DIFF-ENTERTIME</sub>  | Maximum time required for receiver to recognize and signal an unexpected idle on link |                                                        | _                 | _    | _                      | ms    |

<sup>1.</sup> Values are measured at 2.5 Gbps.

<sup>2.</sup> Measured with external AC-coupling on the receiver.

<sup>3.</sup>Not in compliance with PCI Express 1.1 standard.

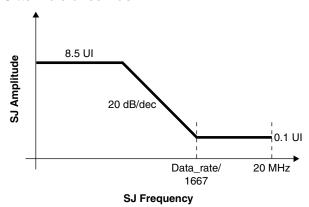

Figure 3-18. XAUI Sinusoidal Jitter Tolerance Mask

Note: The sinusoidal jitter tolerance is measured with at least 0.37 Ulpp of Deterministic jitter (Dj) and the sum of Dj and Rj (random jitter) is at least 0.55 Ulpp. Therefore, the sum of Dj, Rj and Sj (sinusoidal jitter) is at least 0.65 Ulpp (Dj = 0.37, Rj = 0.18, Sj = 0.1).

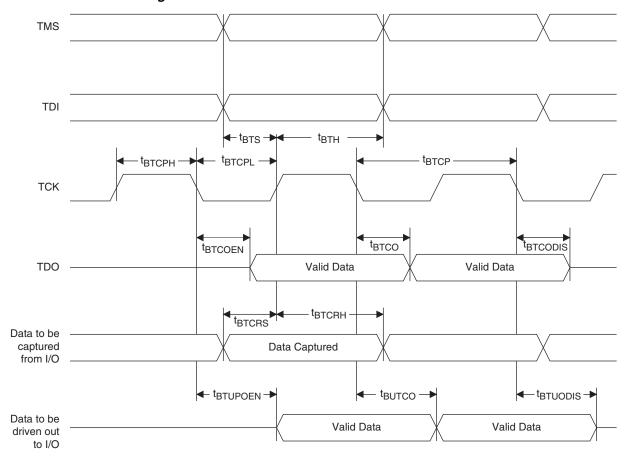

# **JTAG Port Timing Specifications**

### **Over Recommended Operating Conditions**

| Symbol               | Parameter                                                          | Min | Max | Units |

|----------------------|--------------------------------------------------------------------|-----|-----|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                | _   | 25  | MHz   |

| t <sub>BTCP</sub>    | TCK [BSCAN] clock pulse width                                      | 40  | _   | ns    |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20  | _   | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20  | _   | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 10  | _   | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 8   | _   | ns    |

| t <sub>BTRF</sub>    | TCK [BSCAN] rise/fall time                                         | 50  | _   | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               | _   | 10  | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              |     | 10  | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | _   | 10  | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8   | _   | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              |     | _   | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  |     | 25  | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable |     | 25  | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | _   | 25  | ns    |

Figure 3-32. JTAG Port Timing Waveforms

# **Signal Descriptions (Cont.)**

| Signal Name                           | I/O | Description                                                                       |

|---------------------------------------|-----|-----------------------------------------------------------------------------------|

| D7/SPID0                              | I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configuration. |

| DI/CSSPI0N/CEN                        | I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.               |

| Dedicated SERDES Signals <sup>3</sup> | •   |                                                                                   |

| PCS[Index]_HDINNm                     | I   | High-speed input, negative channel m                                              |

| PCS[Index]_HDOUTNm                    | 0   | High-speed output, negative channel m                                             |

| PCS[Index]_REFCLKN                    | I   | Negative Reference Clock Input                                                    |

| PCS[Index]_HDINPm                     | I   | High-speed input, positive channel m                                              |

| PCS[Index]_HDOUTPm                    | 0   | High-speed output, positive channel m                                             |

| PCS[Index]_REFCLKP                    | I   | Positive Reference Clock Input                                                    |

| PCS[Index]_VCCOBm                     | _   | Output buffer power supply, channel m (1.2V/1.5)                                  |

| PCS[Index]_VCCIBm                     | _   | Input buffer power supply, channel m (1.2V/1.5V)                                  |

<sup>1.</sup> When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

<sup>2.</sup> These pins are dedicated inputs or can be used as general purpose I/O.

<sup>3.</sup> m defines the associated channel in the quad.

## **Package Pinout Information**

Package pinout information can be found under "Data Sheets" on the LatticeECP3 product pages on the Lattice website at <a href="http://www.latticesemi.com/Products/FPGAandCPLD/LatticeECP3">http://www.latticesemi.com/Products/FPGAandCPLD/LatticeECP3</a> and in the Diamond or ispLEVER software tools. To create pinout information from within ispLEVER Design Planner, select **Tools > Spreadsheet View**. Then select **File > Export** and choose a type of output file. To create a pin information file from within Diamond select **Tools > Spreadsheet View** or **Tools > Package View**; then, select **File > Export** and choose a type of output file. See Diamond or ispLEVER Help for more information.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

#### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- Power Calculator tool included with the Diamond and ispLEVER design tools, or as a standalone download from www.latticesemi.com/software

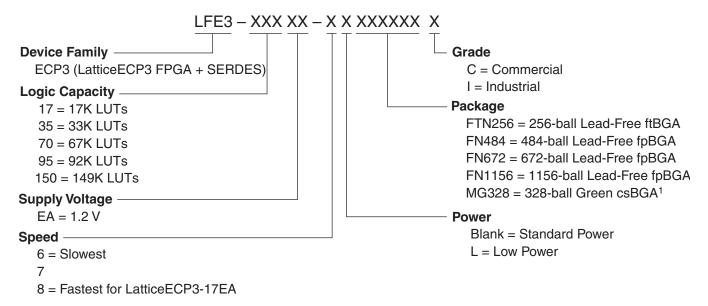

# LatticeECP3 Family Data Sheet Ordering Information

April 2014 Data Sheet DS1021

## **LatticeECP3 Part Number Description**

<sup>1.</sup> Green = Halogen free and lead free.

# **Ordering Information**

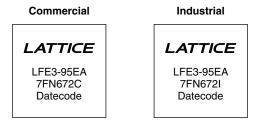

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

# LatticeECP3 Family Data Sheet Supplemental Information

February 2014 Data Sheet DS1021

#### For Further Information

A variety of technical notes for the LatticeECP3 family are available on the Lattice website at www.latticesemi.com.

- TN1169, LatticeECP3 sysCONFIG Usage Guide

- TN1176, LatticeECP3 SERDES/PCS Usage Guide

- TN1177, LatticeECP3 sysIO Usage Guide

- TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide

- TN1179, LatticeECP3 Memory Usage Guide

- TN1180, LatticeECP3 High-Speed I/O Interface

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- TN1182, LatticeECP3 sysDSP Usage Guide

- TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide

- TN1189, LatticeECP3 Hardware Checklist

- TN1215, LatticeECP2MS and LatticeECP2S Devices

- TN1216, LatticeECP2/M and LatticeECP3 Dual Boot Feature Advanced Security Encryption Key Programming Guide for LatticeECP3

- TN1222, LatticeECP3 Slave SPI Port User's Guide

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: www.pcisig.com

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                            |

|---------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                    |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                  |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                     |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                            |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                              |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                   |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                                                                                                                                                                                                     |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                                                                                                                                                                                                      |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                                                                                                                                                                                                      |

|               |         |                                     | Added SERDES/PCS Block Latency Breakdown table.                                                                                                                                                                                                                                                                                           |

|               |         |                                     | External Reference Clock Specifications table, added footnote 4, add symbol name vREF-IN-DIFF.                                                                                                                                                                                                                                            |

|               |         |                                     | Added SERDES External Reference Clock Waveforms.                                                                                                                                                                                                                                                                                          |

|               |         |                                     | Updated Serial Output Timing and Levels table.                                                                                                                                                                                                                                                                                            |

|               |         |                                     | Pin-to-pin performance table, changed "typically 3% slower" to "typically slower".                                                                                                                                                                                                                                                        |

|               |         |                                     | Updated timing information                                                                                                                                                                                                                                                                                                                |

|               |         |                                     | Updated SERDES minimum frequency.                                                                                                                                                                                                                                                                                                         |

|               |         |                                     | Added data to the following tables: External Switching Characteristics, Internal Switching Characteristics, Family Timing Adders, Maximum I/O Buffer Speed, DLL Timing, High Speed Data Transmitter, Channel Output Jitter, Typical Building Block Function Performance, Register-to-Register Performance, and Power Supply Requirements. |

|               |         |                                     | Updated Serial Input Data Specifications table.                                                                                                                                                                                                                                                                                           |

|               |         |                                     | Updated Transmit table, Serial Rapid I/O Type 2 Electrical and Timing Characteristics section.                                                                                                                                                                                                                                            |

|               |         | Pinout Information                  | Updated Signal Description tables.                                                                                                                                                                                                                                                                                                        |

|               |         |                                     | Updated Pin Information Summary tables and added footnote 1.                                                                                                                                                                                                                                                                              |

| February 2009 | 01.0    |                                     | Initial release.                                                                                                                                                                                                                                                                                                                          |