Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                               |

|--------------------------------|-------------------------------------------------------------------------------|

| Product Status                 | Active                                                                        |

| Number of LABs/CLBs            | 2125                                                                          |

| Number of Logic Elements/Cells | 17000                                                                         |

| Total RAM Bits                 | 716800                                                                        |

| Number of I/O                  | 133                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 256-BGA                                                                       |

| Supplier Device Package        | 256-FTBGA (17x17)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-17ea-7ftn256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The LatticeECP3™ (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>TM</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

syslO syslO Configuration Logic: Bank 0 Bank 1 Dual-boot, Encryption and Transparent Updates **JTAG** On-chip Oscillator Pre-engineered Source Synchronous Support: DDR3 - 800 Mbps syslO sysIO Generic - Up to 1 Gbps Bank Bank **Enhanced DSP** Slices: Multiply, Accumulate and ALU svsCLOCK PLLs & DLLs: Frequency Synthesis and Clock Alignment Flexible sysIO: LVCMOS, HSTL, SSTL LVDS Up to 486 I/Os sysMEM Block RAM: 18 Kbit Flexible Routing: Optimized for speed and routability Programmable SERDES/PCS SERDES/PCS SERDES/PCS SERDES/PC **Function Units:** CH 3 CH 2 CH 1 CH 0 Up to 149K LUTs sysIO Bank 6 sysIO Bank 3 3.2 Gbps SERDES

Figure 2-1. Simplified Block Diagram, LatticeECP3-35 Device (Top Level)

Note: There is no Bank 4 or Bank 5 in LatticeECP3 devices.

## **PFU Blocks**

The core of the LatticeECP3 device consists of PFU blocks, which are provided in two forms, the PFU and PFF. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices numbered 0-3 as shown in Figure 2-2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

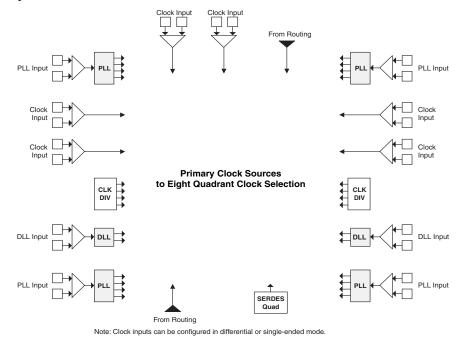

Figure 2-10. Primary Clock Sources for LatticeECP3-35

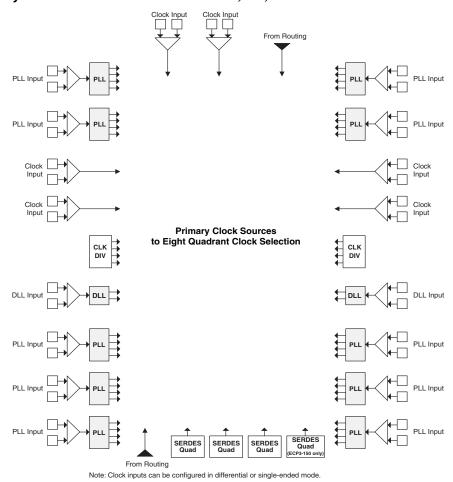

Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

The edge clocks on the top, left, and right sides of the device can drive the secondary clocks or general routing resources of the device. The left and right side edge clocks also can drive the primary clock network through the clock dividers (CLKDIV).

## sysMEM Memory

LatticeECP3 devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18-Kbit RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

## sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-7. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with18-bit and 36-bit data widths. For more information, please see TN1179, LatticeECP3 Memory Usage Guide.

Table 2-7. sysMEM Block Configurations

| Memory Mode      | Configurations                                                              |

|------------------|-----------------------------------------------------------------------------|

| Single Port      | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| True Dual Port   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| Pseudo Dual Port | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

## **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

## **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

## **Memory Cascading**

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

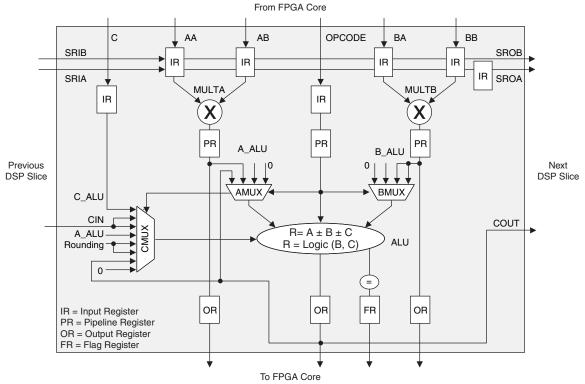

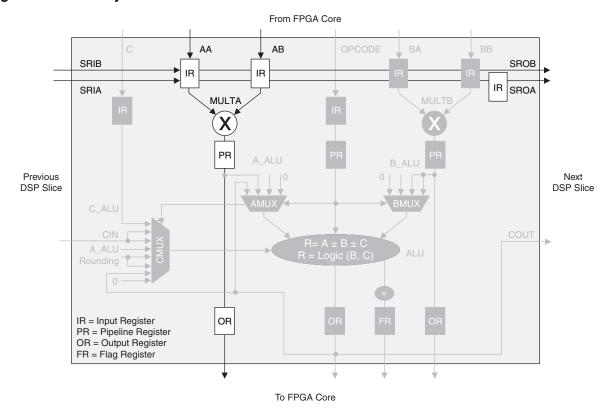

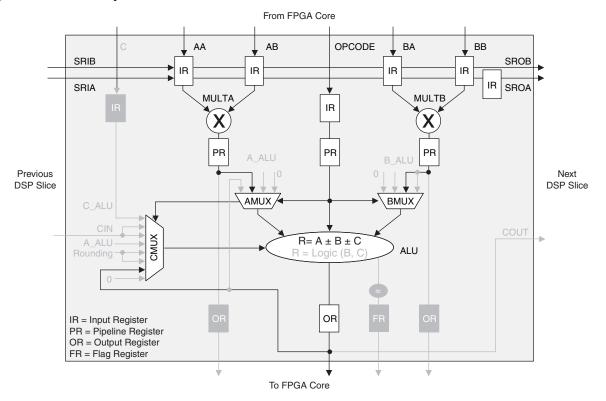

Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | х9             | x18 | x36 |

|-------------------|----------------|-----|-----|

| MULT              | 4              | 2   | 1/2 |

| MAC               | 1              | 1   | _   |

| MULTADDSUB        | 2              | 1   | _   |

| MULTADDSUBSUM     | 1 <sup>1</sup> | 1/2 | _   |

<sup>1.</sup> One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

For further information, please refer to TN1182, LatticeECP3 sysDSP Usage Guide.

#### **MULT DSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, AA and AB, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-26 shows the MULT sysDSP element.

Figure 2-26. MULT sysDSP Element

## **MMAC DSP Element**

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

Figure 2-28. MMAC sysDSP Element

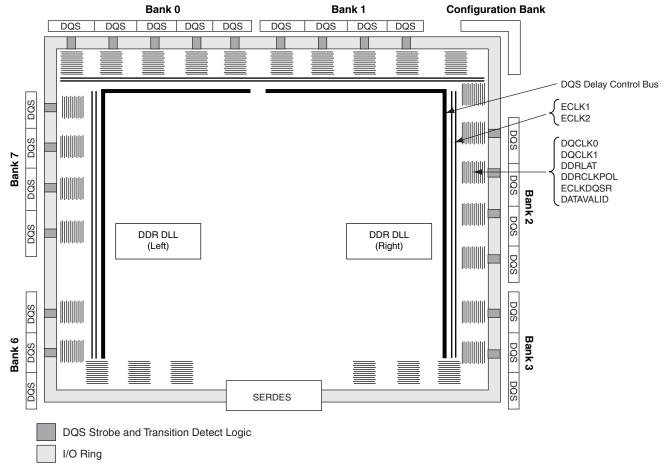

Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

<sup>\*</sup>Includes shared configuration I/Os and dedicated configuration I/Os.

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on DDR Memory interface implementation in LatticeECP3.

## sysI/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

## sysI/O Buffer Banks

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{\rm CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{\rm REF1}$  and  $V_{\rm REF2}$ , which allow it to be completely independent from the others. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

# LatticeECP3 Supply Current (Standby)<sup>1, 2, 3, 4, 5, 6</sup>

## **Over Recommended Operating Conditions**

|                    |                                                                   |             | Турі          | ical       |       |  |

|--------------------|-------------------------------------------------------------------|-------------|---------------|------------|-------|--|

| Symbol             | Parameter                                                         | Device      | -6L, -7L, -8L | -6, -7, -8 | Units |  |

|                    |                                                                   | ECP-17EA    | 29.8          | 49.4       | mA    |  |

|                    |                                                                   | ECP3-35EA   | 53.7          | 89.4       | mA    |  |

| I <sub>CC</sub>    | Core Power Supply Current                                         | ECP3-70EA   | 137.3         | 230.7      | mA    |  |

|                    |                                                                   | ECP3-95EA   | 137.3         | 230.7      | mA    |  |

|                    |                                                                   | ECP3-150EA  | 219.5         | 370.9      | mA    |  |

|                    |                                                                   | ECP-17EA    | 18.3          | 19.4       | mA    |  |

|                    |                                                                   | ECP3-35EA   | 19.6          | 23.1       | mA    |  |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current                                    | ECP3-70EA   | 26.5          | 32.4       | mA    |  |

|                    |                                                                   | ECP3-95EA   | 26.5          | 32.4       | mA    |  |

|                    |                                                                   | ECP3-150EA  | 37.0          | 45.7       | mA    |  |

|                    |                                                                   | ECP-17EA    | 0.0           | 0.0        | mA    |  |

|                    | PLL Power Supply Current (Per PLL)                                | ECP3-35EA   | 0.1           | 0.1        | mA    |  |

| I <sub>CCPLL</sub> |                                                                   | ECP3-70EA   | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP3-95EA   | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP3-150EA  | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP-17EA    | 1.3           | 1.4        | mA    |  |

|                    |                                                                   | ECP3-35EA   | 1.3           | 1.4        | mA    |  |

| I <sub>CCIO</sub>  | Bank Power Supply Current (Per Bank)                              | ECP3-70EA   | 1.4           | 1.5        | mA    |  |

|                    |                                                                   | ECP3-95EA   | 1.4           | 1.5        | mA    |  |

|                    |                                                                   | ECP3-150EA  | 1.4           | 1.5        | mA    |  |

| I <sub>CCJ</sub>   | JTAG Power Supply Current                                         | All Devices | 2.5           | 2.5        | mA    |  |

|                    |                                                                   | ECP-17EA    | 6.1           | 6.1        | mA    |  |

|                    |                                                                   | ECP3-35EA   | 6.1           | 6.1        | mA    |  |

| $I_{CCA}$          | Transmit, Receive, PLL and<br>Reference Clock Buffer Power Supply | ECP3-70EA   | 18.3          | 18.3       | mA    |  |

|                    | Tree crock Bullet I ower ouppry                                   | ECP3-95EA   | 18.3          | 18.3       | mA    |  |

|                    |                                                                   | ECP3-150EA  | 24.4          | 24.4       | mA    |  |

<sup>1.</sup> For further information on supply current, please see the list of technical documentation at the end of this data sheet.

<sup>2.</sup> Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{\scriptsize CCIO}}$  or GND.

<sup>3.</sup> Frequency 0 MHz.

<sup>4.</sup> Pattern represents a "blank" configuration data file.

<sup>5.</sup>  $T_J = 85$  °C, power supplies at nominal voltage.

<sup>6.</sup> To determine the LatticeECP3 peak start-up current data, use the Power Calculator tool.

## sysI/O Recommended Operating Conditions

|                                                |           | V <sub>CCIO</sub> |           |       | V <sub>REF</sub> (V) |       |

|------------------------------------------------|-----------|-------------------|-----------|-------|----------------------|-------|

| Standard                                       | Min.      | Тур.              | Max.      | Min.  | Тур.                 | Max.  |

| LVCMOS33 <sup>2</sup>                          | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| LVCMOS33D                                      | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| LVCMOS25 <sup>2</sup>                          | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| LVCMOS18                                       | 1.71      | 1.8               | 1.89      | _     | _                    | _     |

| LVCMOS15                                       | 1.425     | 1.5               | 1.575     | _     | _                    | _     |

| LVCMOS12 <sup>2</sup>                          | 1.14      | 1.2               | 1.26      | _     | _                    | _     |

| LVTTL33 <sup>2</sup>                           | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| PCI33                                          | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| SSTL15 <sup>3</sup>                            | 1.43      | 1.5               | 1.57      | 0.68  | 0.75                 | 0.9   |

| SSTL18_I, II <sup>2</sup>                      | 1.71      | 1.8               | 1.89      | 0.833 | 0.9                  | 0.969 |

| SSTL25_I, II <sup>2</sup>                      | 2.375     | 2.5               | 2.625     | 1.15  | 1.25                 | 1.35  |

| SSTL33_I, II <sup>2</sup>                      | 3.135     | 3.3               | 3.465     | 1.3   | 1.5                  | 1.7   |

| HSTL15_I <sup>2</sup>                          | 1.425     | 1.5               | 1.575     | 0.68  | 0.75                 | 0.9   |

| HSTL18_I, II <sup>2</sup>                      | 1.71      | 1.8               | 1.89      | 0.816 | 0.9                  | 1.08  |

| LVDS25 <sup>2</sup>                            | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| LVDS25E                                        | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| MLVDS <sup>1</sup>                             | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| LVPECL33 <sup>1, 2</sup>                       | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| Mini LVDS                                      | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| BLVDS25 <sup>1, 2</sup>                        | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| RSDS <sup>2</sup>                              | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| RSDSE <sup>1, 2</sup>                          | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| TRLVDS                                         | 3.14      | 3.3               | 3.47      | _     | _                    | _     |

| PPLVDS                                         | 3.14/2.25 | 3.3/2.5           | 3.47/2.75 | _     | _                    | _     |

| SSTL15D <sup>3</sup>                           | 1.43      | 1.5               | 1.57      | _     | _                    | _     |

| SSTL18D_I <sup>2, 3</sup> , II <sup>2, 3</sup> | 1.71      | 1.8               | 1.89      | _     | _                    | _     |

| SSTL25D_ I <sup>2</sup> , II <sup>2</sup>      | 2.375     | 2.5               | 2.625     | _     | _                    | _     |

| SSTL33D_ I <sup>2</sup> , II <sup>2</sup>      | 3.135     | 3.3               | 3.465     | _     | _                    | _     |

| HSTL15D_ I <sup>2</sup>                        | 1.425     | 1.5               | 1.575     | _     | _                    | _     |

| HSTL18D_ I <sup>2</sup> , II <sup>2</sup>      | 1.71      | 1.8               | 1.89      | _     | _                    | _     |

<sup>1.</sup> Inputs on chip. Outputs are implemented with the addition of external resistors.

<sup>2.</sup> For input voltage compatibility, see TN1177, LatticeECP3 sysIO Usage Guide.

<sup>3.</sup> VREF is required when using Differential SSTL to interface to DDR memory.

## sysI/O Single-Ended DC Electrical Characteristics

| Input/Output  | V <sub>IL</sub> |                          | V <sub>IH</sub>                |                                        | V <sub>OL</sub>       | V <sub>OH</sub>          |                        |                                   |    |     |

|---------------|-----------------|--------------------------|--------------------------------|----------------------------------------|-----------------------|--------------------------|------------------------|-----------------------------------|----|-----|

| Standard      | Min. (V)        | Max. (V)                 | Min. (V)                       | Max. (V)                               | Max. (V)              | Min. (V)                 | I <sub>OL</sub> 1 (mA) | I <sub>OH</sub> <sup>1</sup> (mA) |    |     |

|               |                 |                          |                                |                                        | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,                | -20, -16,                         |    |     |

| LVCMOS33      | -0.3            | 0.8                      | 2.0                            | 3.6                                    |                       |                          | 12, 8, 4               | -12, -8, -4                       |    |     |

|               |                 |                          |                                |                                        | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| LVCMOS25      | -0.3            | 0.7                      | 1.7                            | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |    |     |

|               |                 |                          |                                |                                        | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| LVCMOS18      | -0.3            | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>         | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16, 12,<br>8, 4        | -16, -12,<br>-8, -4               |    |     |

|               |                 |                          |                                |                                        | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| LVCMOS15      | -0.3            | 0.35 V <sub>CCIO</sub>   | 0.65 V <sub>CCIO</sub>         | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8, 4                   | -8, -4                            |    |     |

| LVCIVIOS15    | -0.3            | 0.35 V <sub>CCIO</sub>   | 0.05 VCCIO                     | 3.0                                    | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| LVCMOS12      | -0.3            | 0.35 V <sub>CC</sub>     | 0.65 V <sub>CC</sub>           | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6, 2                   | -6, -2                            |    |     |

| LVCIVIOS12    | -0.3            | 0.33 V <sub>CC</sub>     | 0.05 V <sub>CC</sub>           | 3.0                                    | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| LVTTL33       | -0.3            | 0.8                      | 2.0                            | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4          |    |     |

|               |                 |                          |                                |                                        | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                              |    |     |

| PCI33         | -0.3            | 0.3 V <sub>CCIO</sub>    | 0.5 V <sub>CCIO</sub>          | 3.6                                    | 0.1 V <sub>CCIO</sub> | 0.9 V <sub>CCIO</sub>    | 1.5                    | -0.5                              |    |     |

| SSTL18_I      | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6.7                    | -6.7                              |    |     |

| SSTL18_II     | -0.3            | V <sub>REF</sub> - 0.125 | V . 0.105                      | 3.6                                    | 0.28                  | V 0.29                   | 8                      | -8                                |    |     |

| (DDR2 Memory) | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       | .125 3.6 0.28 V <sub>CCIO</sub> - 0.28 |                       | 11                       | -11                    |                                   |    |     |

| CCTLO         | -0.3            | V 0.19                   | V .019                         | 3.6                                    | 0.54                  | V 0.60                   | 7.6                    | -7.6                              |    |     |

| SSTL2_I       | -0.3            | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18        | 3.0                                    | 0.54                  | V <sub>CCIO</sub> - 0.62 | 12                     | -12                               |    |     |

| SSTL2_II      | -0.3            | V <sub>RFF</sub> - 0.18  | V <sub>REF</sub> + 0.18        | 3.6                                    | 0.35                  | V <sub>CCIO</sub> - 0.43 | 15.2                   | -15.2                             |    |     |

| (DDR Memory)  | -0.3            | V <sub>REF</sub> - 0.16  | V <sub>REF</sub> + 0.16        | 3.0                                    | 0.55                  | V <sub>CCIO</sub> - 0.43 | 20                     | -20                               |    |     |

| SSTL3_I       | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2         | 3.6                                    | 0.7                   | V <sub>CCIO</sub> - 1.1  | 8                      | -8                                |    |     |

| SSTL3_II      | -0.3            | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2         | 3.6                                    | 0.5                   | V <sub>CCIO</sub> - 0.9  | 16                     | -16                               |    |     |

| SSTL15        | 0.0             | V 0.1                    | V . 0.1                        | 2.6                                    | 0.0                   | V <sub>CCIO</sub> - 0.3  | 7.5                    | -7.5                              |    |     |

| (DDR3 Memory) | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         | 3.6                                    | 0.3                   | V <sub>CCIO</sub> * 0.8  | 9                      | -9                                |    |     |

| HSTL15_I      | -0.3            | V 0.1                    | V . 0.1                        | 3.6                                    | 0.4                   | V 0.4                    | 4                      | -4                                |    |     |

| H31L15_1      | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         | 3.0                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |    |     |

| LICTI 10 I    | 0.0             | V 0.1                    | V . 0.1                        | 2.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                                |    |     |

| HSTL18_I      | -0.3            | V <sub>REF</sub> - 0.1   | 0.1 V <sub>REF</sub> + 0.1 3.6 |                                        | 3.6 0.4               |                          | EF + U.1 3.6 U.4       |                                   | 12 | -12 |

| HSTL18_II     | -0.3            | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         | 3.6                                    | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16                     | -16                               |    |     |

<sup>1.</sup> For electromigration, the average DC current drawn by I/O pads between two consecutive V<sub>CCIO</sub> or GND pad connections, or between the last V<sub>CCIO</sub> or GND in an I/O bank and the end of an I/O bank, as shown in the Logic Signal Connections table (also shown as I/O grouping) shall not exceed n \* 8 mA, where n is the number of I/O pads between the two consecutive bank V<sub>CCIO</sub> or GND connections or between the last V<sub>CCIO</sub> and GND in a bank and the end of a bank. IO Grouping can be found in the Data Sheet Pin Tables, which can also be generated from the Lattice Diamond software.

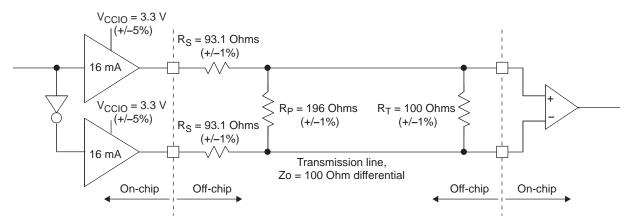

## LVPECL33

The LatticeECP3 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

Figure 3-3. Differential LVPECL33

Table 3-3. LVPECL33 DC Conditions1

## **Over Recommended Operating Conditions**

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.80    | V     |

| $V_{CM}$          | Output Common Mode Voltage       | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 12.11   | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

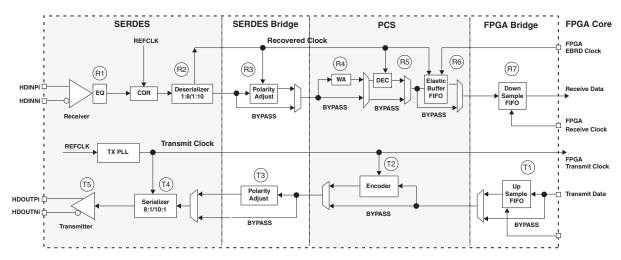

## **SERDES/PCS Block Latency**

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item    | Description                                          | Min. | Avg. | Max. | Fixed                     | Bypass | Units    |

|---------|------------------------------------------------------|------|------|------|---------------------------|--------|----------|

| Transmi | t Data Latency¹                                      |      |      | •    | •                         | •      | •        |

|         | FPGA Bridge - Gearing disabled with different clocks | 1    | 3    | 5    | _                         | 1      | word clk |

| T1      | FPGA Bridge - Gearing disabled with same clocks      | _    | _    | _    | 3                         | 1      | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1    | 3    | 5    | _                         | _      | word clk |

| T2      | 8b10b Encoder                                        | —    | —    | _    | 2                         | 1      | word clk |

| T3      | SERDES Bridge transmit                               | —    |      | _    | 2                         | 1      | word clk |

| T4      | Serializer: 8-bit mode                               | —    |      | _    | 15 + ∆1                   | _      | UI + ps  |

| 14      | Serializer: 10-bit mode                              | —    |      | _    | 18 + ∆1                   | _      | UI + ps  |

| T5      | Pre-emphasis ON                                      |      |      | _    | 1 + ∆2                    | _      | UI + ps  |

| 15      | Pre-emphasis OFF                                     | —    |      | _    | 0 + <u>\( \Delta \) 3</u> | _      | UI + ps  |

| Receive | Data Latency <sup>2</sup>                            |      | •    |      |                           |        |          |

| R1      | Equalization ON                                      | —    |      | _    | Δ1                        |        | UI + ps  |

| n i     | Equalization OFF                                     | —    |      | _    | Δ2                        | _      | UI + ps  |

| R2      | Deserializer: 8-bit mode                             | —    | —    | _    | 10 + ∆3                   | _      | UI + ps  |

| ΠZ      | Deserializer: 10-bit mode                            | —    | —    | _    | 12 + ∆3                   | _      | UI + ps  |

| R3      | SERDES Bridge receive                                | _    | _    | _    | 2                         | _      | word clk |

| R4      | Word alignment                                       | 3.1  | —    | 4    | _                         | _      | word clk |

| R5      | 8b10b decoder                                        | —    | —    | _    | 1                         | _      | word clk |

| R6      | Clock Tolerance Compensation                         | 7    | 15   | 23   | 1                         | 1      | word clk |

|         | FPGA Bridge - Gearing disabled with different clocks | 1    | 3    | 5    | _                         | 1      | word clk |

| R7      | FPGA Bridge - Gearing disabled with same clocks      | _    | _    | _    | 3                         | 1      | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1    | 3    | 5    | _                         | _      | word clk |

<sup>1.</sup>  $\Delta 1 = -245$  ps,  $\Delta 2 = +88$  ps,  $\Delta 3 = +112$  ps.

Figure 3-12. Transmitter and Receiver Latency Block Diagram

<sup>2.</sup>  $\Delta 1 = +118$  ps,  $\Delta 2 = +132$  ps,  $\Delta 3 = +700$  ps.

# **PCI Express Electrical and Timing Characteristics AC and DC Characteristics**

## **Over Recommended Operating Conditions**

| Symbol                                   | Description                                                                           | <b>Test Conditions</b>                                 | Min               | Тур  | Max                    | Units |

|------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|------------------------|-------|

| Transmit <sup>1</sup>                    |                                                                                       | l                                                      | <u> </u>          |      | l                      |       |

| UI                                       | Unit interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>TX-DIFF_P-P</sub>                 | Differential peak-to-peak output voltage                                              |                                                        | 0.8               | 1.0  | 1.2                    | V     |

| V <sub>TX-DE-RATIO</sub>                 | De-emphasis differential output voltage ratio                                         |                                                        | -3                | -3.5 | -4                     | dB    |

| V <sub>TX-CM-AC_P</sub>                  | RMS AC peak common-mode output voltage                                                |                                                        | _                 | _    | 20                     | mV    |

| V <sub>TX-RCV-DETECT</sub>               | Amount of voltage change allowed during receiver detection                            |                                                        | _                 | _    | 600                    | mV    |

| V <sub>TX-DC-CM</sub>                    | Tx DC common mode voltage                                                             |                                                        | 0                 | _    | V <sub>CCOB</sub> + 5% | V     |

| I <sub>TX-SHORT</sub>                    | Output short circuit current                                                          | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | _                 | _    | 90                     | mA    |

| Z <sub>TX-DIFF-DC</sub>                  | Differential output impedance                                                         |                                                        | 80                | 100  | 120                    | Ohms  |

| RL <sub>TX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | _    | _                      | dB    |

| RL <sub>TX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | _    | _                      | dB    |

| T <sub>TX-RISE</sub>                     | Tx output rise time                                                                   | 20 to 80%                                              | 0.125             | _    | _                      | UI    |

| T <sub>TX-FALL</sub>                     | Tx output fall time                                                                   | 20 to 80%                                              | 0.125             | _    | _                      | UI    |

| L <sub>TX-SKEW</sub>                     | Lane-to-lane static output skew for all lanes in port/link                            |                                                        | _                 | _    | 1.3                    | ns    |

| T <sub>TX-EYE</sub>                      | Transmitter eye width                                                                 |                                                        | 0.75              | _    | _                      | UI    |

| T <sub>TX-EYE-MEDIAN-TO-MAX-JITTER</sub> | Maximum time between jitter median and maximum deviation from median                  |                                                        | _                 | _    | 0.125                  | UI    |

| Receive <sup>1, 2</sup>                  |                                                                                       | •                                                      |                   |      | •                      |       |

| UI                                       | Unit Interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>RX-DIFF_P-P</sub>                 | Differential peak-to-peak input voltage                                               |                                                        | 0.34 <sup>3</sup> | _    | 1.2                    | V     |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>        | Idle detect threshold voltage                                                         |                                                        | 65                | _    | 340 <sup>3</sup>       | mV    |

| V <sub>RX-CM-AC_P</sub>                  | Receiver common mode voltage for AC coupling                                          |                                                        | _                 | _    | 150                    | mV    |

| Z <sub>RX-DIFF-DC</sub>                  | DC differential input impedance                                                       |                                                        | 80                | 100  | 120                    | Ohms  |

| Z <sub>RX-DC</sub>                       | DC input impedance                                                                    |                                                        | 40                | 50   | 60                     | Ohms  |

| Z <sub>RX-HIGH-IMP-DC</sub>              | Power-down DC input impedance                                                         |                                                        | 200K              | _    | _                      | Ohms  |

| RL <sub>RX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | _    | _                      | dB    |

| RL <sub>RX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | _    | _                      | dB    |

| T <sub>RX-IDLE-DET-DIFF-ENTERTIME</sub>  | Maximum time required for receiver to recognize and signal an unexpected idle on link |                                                        | _                 | _    | _                      | ms    |

<sup>1.</sup> Values are measured at 2.5 Gbps.

<sup>2.</sup> Measured with external AC-coupling on the receiver.

<sup>3.</sup>Not in compliance with PCI Express 1.1 standard.

# Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII/CPRI LV E.12 Electrical and Timing Characteristics

### **AC and DC Characteristics**

#### Table 3-17. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%         | _    | 80   | _    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 | _    | _    | 0.10 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | _    | _    | 0.24 | UI    |

- 1. Rise and fall times measured with board trace, connector and approximately 2.5 pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 5. Values are measured at 1.25 Gbps.

#### Table 3-18. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions          | Min. | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|--------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   |      |      | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | _    | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                          | 80   | 100  | 120  | Ohms  |

|                                             | Deterministic jitter tolerance (peak-to-peak) |                          |      |      | 0.34 | UI    |

|                                             | Random jitter tolerance (peak-to-peak)        |                          | _    | _    | 0.26 | UI    |

|                                             | Sinusoidal jitter tolerance (peak-to-peak)    |                          | _    | _    | 0.11 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                          | _    | _    | 0.71 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                          | 0.29 | _    | _    | UI    |

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

- 5. Values are measured at 1.25 Gbps.

## **Pin Information Summary**

| Pin Information Summary                    |        | E            | CP3-17E      | Α            | ECP3-35EA    |              |              | ECP3-70EA    |              |               |

|--------------------------------------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Pin Typ                                    | e      | 256<br>ftBGA | 328<br>csBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672<br>fpBGA | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                            | Bank 0 | 26           | 20           | 36           | 26           | 42           | 48           | 42           | 60           | 86            |

|                                            | Bank 1 | 14           | 10           | 24           | 14           | 36           | 36           | 36           | 48           | 78            |

| Canaral Durnaga                            | Bank 2 | 6            | 7            | 12           | 6            | 24           | 24           | 24           | 34           | 36            |

| General Purpose<br>Inputs/Outputs per Bank | Bank 3 | 18           | 12           | 44           | 16           | 54           | 59           | 54           | 59           | 86            |

|                                            | Bank 6 | 20           | 11           | 44           | 18           | 63           | 61           | 63           | 67           | 86            |

|                                            | Bank 7 | 19           | 26           | 32           | 19           | 36           | 42           | 36           | 48           | 54            |

|                                            | Bank 8 | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24            |

|                                            | Bank 0 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2 | 2            | 2            | 2            | 2            | 4            | 4            | 4            | 8            | 8             |

| General Purpose Inputs per Bank            | Bank 3 | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

| per bank                                   | Bank 6 | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

|                                            | Bank 7 | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 8            | 8             |

|                                            | Bank 8 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 0 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| General Purpose Out-                       | Bank 3 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| puts per Bank                              | Bank 6 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 7 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 8 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| Total Single-Ended User                    | I/O    | 133          | 116          | 222          | 133          | 295          | 310          | 295          | 380          | 490           |

| VCC                                        |        | 6            | 16           | 16           | 6            | 16           | 32           | 16           | 32           | 32            |

| VCCAUX                                     |        | 4            | 5            | 8            | 4            | 8            | 12           | 8            | 12           | 16            |

| VTT                                        |        | 4            | 7            | 4            | 4            | 4            | 4            | 4            | 4            | 8             |

| VCCA                                       |        | 4            | 6            | 4            | 4            | 4            | 8            | 4            | 8            | 16            |

| VCCPLL                                     |        | 2            | 2            | 4            | 2            | 4            | 4            | 4            | 4            | 4             |

|                                            | Bank 0 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 1 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 2 | 2            | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

| VCCIO                                      | Bank 3 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 6 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 7 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 8 | 1            | 2            | 2            | 1            | 2            | 2            | 2            | 2            | 2             |

| VCCJ                                       |        | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1             |

| TAP                                        |        | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4             |

| GND, GNDIO                                 |        | 51           | 126          | 98           | 51           | 98           | 139          | 98           | 139          | 233           |

| NC                                         |        | 0            | 0            | 73           | 0            | 0            | 96           | 0            | 0            | 238           |

| Reserved <sup>1</sup>                      |        | 0            | 0            | 2            | 0            | 2            | 2            | 2            | 2            | 2             |

| SERDES                                     |        | 26           | 18           | 26           | 26           | 26           | 26           | 26           | 52           | 78            |

| Miscellaneous Pins                         |        | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8             |

| Total Bonded Pins                          |        | 256          | 328          | 484          | 256          | 484          | 672          | 484          | 672          | 1156          |

## **Pin Information Summary (Cont.)**

| Pin Information Summary Pin Type           |                      | ECP3-70EA |           |            |  |  |

|--------------------------------------------|----------------------|-----------|-----------|------------|--|--|

|                                            |                      | 484 fpBGA | 672 fpBGA | 1156 fpBGA |  |  |

| Emulated Differential<br>I/O per Bank      | Bank 0               | 21        | 30        | 43         |  |  |

|                                            | Bank 1               | 18        | 24        | 39         |  |  |

|                                            | Bank 2               | 8         | 12        | 13         |  |  |

|                                            | Bank 3               | 20        | 23        | 33         |  |  |

|                                            | Bank 6               | 22        | 25        | 33         |  |  |

|                                            | Bank 7               | 11        | 16        | 18         |  |  |

|                                            | Bank 8               | 12        | 12        | 12         |  |  |

|                                            | Bank 0               | 0         | 0         | 0          |  |  |

|                                            | Bank 1               | 0         | 0         | 0          |  |  |

| 11: 1 0 10:4 1: 11/                        | Bank 2               | 6         | 9         | 9          |  |  |

| High-Speed Differential I/<br>O per Bank   | Bank 3               | 9         | 12        | 16         |  |  |

| o por Barne                                | Bank 6               | 11        | 14        | 16         |  |  |

|                                            | Bank 7               | 9         | 12        | 13         |  |  |

|                                            | Bank 8               | 0         | 0         | 0          |  |  |

|                                            | Bank 0               | 42/21     | 60/30     | 86/43      |  |  |

| Total Single-Ended/                        | Bank 1               | 36/18     | 48/24     | 78/39      |  |  |

|                                            | Bank 2               | 28/14     | 42/21     | 44/22      |  |  |

| Total Differential I/O                     | Bank 3               | 58/29     | 71/35     | 98/49      |  |  |

| per Bank                                   | Bank 6               | 67/33     | 78/39     | 98/49      |  |  |

|                                            | Bank 7               | 40/20     | 56/28     | 62/31      |  |  |

|                                            | Bank 8               | 24/12     | 24/12     | 24/12      |  |  |

|                                            | Bank 0               | 3         | 5         | 7          |  |  |

| DDR Groups Bonded<br>per Bank <sup>1</sup> | Bank 1               | 3         | 4         | 7          |  |  |

|                                            | Bank 2               | 2         | 3         | 3          |  |  |

|                                            | Bank 3               | 3         | 4         | 5          |  |  |

|                                            | Bank 6               | 4         | 4         | 5          |  |  |

|                                            | Bank 7               | 3         | 4         | 4          |  |  |

|                                            | Configuration Bank 8 | 0         | 0         | 0          |  |  |

| SERDES Quads                               |                      | 1         | 2         | 3          |  |  |

<sup>1.</sup> Some DQS groups may not support DQS-12. Refer to the device pinout (.csv) file.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7FN484C   | 1.2 V   | <b>-</b> 7         | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

<sup>1.</sup> For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

<sup>1.</sup> For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                            |

|---------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                    |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                  |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                     |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                            |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                              |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                   |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                                                                                                                                                                                                     |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                                                                                                                                                                                                      |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                                                                                                                                                                                                      |

|               |         |                                     | Added SERDES/PCS Block Latency Breakdown table.                                                                                                                                                                                                                                                                                           |

|               |         |                                     | External Reference Clock Specifications table, added footnote 4, add symbol name vREF-IN-DIFF.                                                                                                                                                                                                                                            |

|               |         |                                     | Added SERDES External Reference Clock Waveforms.                                                                                                                                                                                                                                                                                          |

|               |         |                                     | Updated Serial Output Timing and Levels table.                                                                                                                                                                                                                                                                                            |

|               |         |                                     | Pin-to-pin performance table, changed "typically 3% slower" to "typically slower".                                                                                                                                                                                                                                                        |

|               |         |                                     | Updated timing information                                                                                                                                                                                                                                                                                                                |

|               |         |                                     | Updated SERDES minimum frequency.                                                                                                                                                                                                                                                                                                         |

|               |         |                                     | Added data to the following tables: External Switching Characteristics, Internal Switching Characteristics, Family Timing Adders, Maximum I/O Buffer Speed, DLL Timing, High Speed Data Transmitter, Channel Output Jitter, Typical Building Block Function Performance, Register-to-Register Performance, and Power Supply Requirements. |

|               |         |                                     | Updated Serial Input Data Specifications table.                                                                                                                                                                                                                                                                                           |

|               |         |                                     | Updated Transmit table, Serial Rapid I/O Type 2 Electrical and Timing Characteristics section.                                                                                                                                                                                                                                            |

|               |         | Pinout Information                  | Updated Signal Description tables.                                                                                                                                                                                                                                                                                                        |

|               |         |                                     | Updated Pin Information Summary tables and added footnote 1.                                                                                                                                                                                                                                                                              |