# E. Attice Semiconductor Corporation - <u>LFE3-17EA-7LFTN256C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                         |

|--------------------------------|--------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 2125                                                                           |

| Number of Logic Elements/Cells | 17000                                                                          |

| Total RAM Bits                 | 716800                                                                         |

| Number of I/O                  | 133                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 256-BGA                                                                        |

| Supplier Device Package        | 256-FTBGA (17x17)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-17ea-7lftn256c |

|                                |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

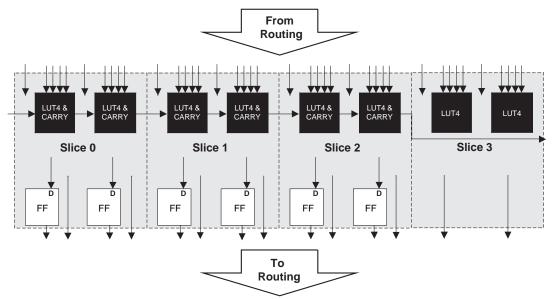

### Figure 2-2. PFU Diagram

### Slice

Slice 0 through Slice 2 contain two LUT4s feeding two registers, whereas Slice 3 contains two LUT4s only. For PFUs, Slice 0 through Slice 2 can be configured as distributed memory, a capability not available in the PFF. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

|         | PFU                     | 3Lock                   | PFF E                   | Block              |

|---------|-------------------------|-------------------------|-------------------------|--------------------|

| Slice   | Resources               | Modes                   | Resources               | Modes              |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |

Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Slices 0, 1 and 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 10 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

### Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### RAM Mode

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals. A 16x2-bit pseudo dual port RAM (PDPR) memory is created by using one Slice as the read-write port and the other companion slice as the read-only port.

LatticeECP3 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in LatticeECP3 devices, please see TN1179, LatticeECP3 Memory Usage Guide.

#### Table 2-3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

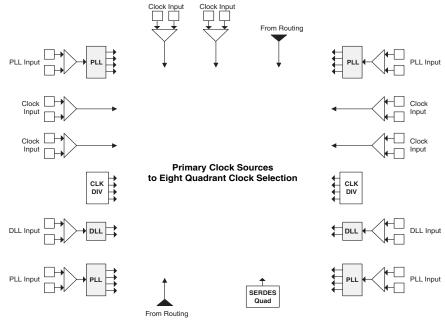

#### Figure 2-10. Primary Clock Sources for LatticeECP3-35

Note: Clock inputs can be configured in differential or single-ended mode.

#### Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

Note: Clock inputs can be configured in differential or single-ended mode.

## ALU Flags

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- Equal to one with mask (EQOM)

- Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

### **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

## **Resources Available in the LatticeECP3 Family**

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

### **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces, a PLL is used for this adjustment. However, in DDR memories the clock (referred to as DQS) is not free-running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The delay required for the DQS signal is generated by two dedicated DLLs (DDR DLL) on opposite side of the device. Each DLL creates DQS delays in its half of the device as shown in Figure 2-36. The DDR DLL on the left side will generate delays for all the DQS Strobe pins on Banks 0, 7 and 6 and DDR DLL on the right will generate delays for all the DQS pins on Banks 1, 2 and 3. The DDR DLL loop compensates for temperature, voltage and process variations by using the system clock and DLL feedback loop. DDR DLL communicates the required delay to the DQS delay block using a 7-bit calibration bus (DCNTL[6:0])

The DQS signal (selected PIOs only, as shown in Figure 2-35) feeds from the PAD through a DQS control logic block to a dedicated DQS routing resource. The DQS control logic block consists of DQS Read Control logic block that generates control signals for the read side and DQS Write Control logic that generates the control signals required for the write side. A more detailed DQS control diagram is shown in Figure 2-37, which shows how the DQS control blocks interact with the data paths.

The DQS Read control logic receives the delay generated by the DDR DLL on its side and delays the incoming DQS signal by 90 degrees. This delayed ECLKDQSR is routed to 10 or 11 DQ pads covered by that DQS signal. This block also contains a polarity control logic that generates a DDRCLKPOL signal, which controls the polarity of the clock to the sync registers in the input register blocks. The DQS Read control logic also generates a DDRLAT signal that is in the input register block to transfer data from the first set of DDR register to the second set of DDR registers when using the DDRX2 gearbox mode for DDR3 memory interface.

The DQS Write control logic block generates the DQCLK0 and DQCLK1 clocks used to control the output gearing in the Output register block which generates the DDR data output and the DQS output. They are also used to control the generation of the DQS output through the DQS output register block. In addition to the DCNTL [6:0] input from the DDR DLL, the DQS Write control block also uses a Dynamic Delay DYN DEL [7:0] attribute which is used to further delay the DQS to accomplish the write leveling found in DDR3 memory. Write leveling is controlled by the DDR memory controller implementation. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock. This will generate the DQSW signal used to generate the DQS output in the DQS output register block.

Figure 2-36 and Figure 2-37 show how the DQS transition signals that are routed to the PIOs.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

## Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol  | Parameter                         | Condition                                 | Min. | Тур. | Max. | Units |

|---------|-----------------------------------|-------------------------------------------|------|------|------|-------|

| IDK_HS⁴ | Input or I/O Leakage Current      | $0 \le V_{IN} \le V_{IH}$ (Max.)          |      |      | +/-1 | mA    |

|         | DK° LINDUT OF I/O Leakage Current | $0 \le V_{IN} < V_{CCIO}$                 |      |      | +/-1 | mA    |

|         |                                   | $V_{CCIO} \le V_{IN} \le V_{CCIO} + 0.5V$ | _    | 18   | _    | mA    |

1.  $V_{CC},\,V_{CCAUX}$  and  $V_{CCIO}$  should rise/fall monotonically.

2.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

3. LVCMOS and LVTTL only.

4. Applicable to general purpose I/O pins located on the top and bottom sides of the device.

5. Applicable to general purpose I/O pins located on the left and right sides of the device.

## Hot Socketing Requirements<sup>1, 2</sup>

| Description                                                                     | Min. | Тур. | Max. | Units |

|---------------------------------------------------------------------------------|------|------|------|-------|

| Input current per SERDES I/O pin when device is powered down and inputs driven. | _    | -    | 8    | mA    |

1. Assumes the device is powered down, all supplies grounded, both P and N inputs driven by CML driver with maximum allowed VCCOB (1.575 V), 8b10b data, internal AC coupling.

2. Each P and N input must have less than the specified maximum input current. For a 16-channel device, the total input current would be 8 mA\*16 channels \*2 input pins per channel = 256 mA

## **ESD** Performance

Please refer to the LatticeECP3 Product Family Qualification Summary for complete qualification data, including ESD performance.

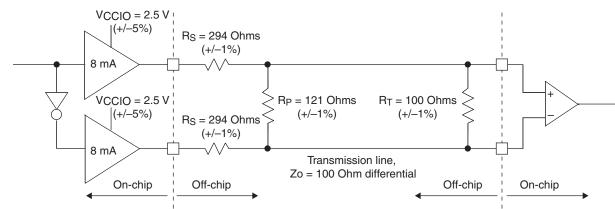

### RSDS25E

The LatticeECP3 devices support differential RSDS and RSDSE standards. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

#### Figure 3-4. RSDS25E (Reduced Swing Differential Signaling)

#### Table 3-4. RSDS25E DC Conditions<sup>1</sup>

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/–5%)     | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 20      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.20    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 3.66    | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

## Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                             | –8 Timing | Units |

|------------------------------------------------------|-----------|-------|

| 18x18 Multiply/Accumulate (Input & Output Registers) | 200       | MHz   |

| 18x18 Multiply-Add/Sub (All Registers)               | 400       | MHz   |

1. These timing numbers were generated using ispLEVER tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

3. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

## **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond and ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond and ispLEVER design tools can provide logic timing numbers at a particular temperature and voltage.

## LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                       |                                 |                          | -        | -8                   | -7      |                       | -6     |          |       |

|-----------------------|---------------------------------|--------------------------|----------|----------------------|---------|-----------------------|--------|----------|-------|

| Parameter             | Description                     | Device                   | Min.     | Max.                 | Min.    | Max.                  | Min.   | Max.     | Units |

| fMAX_GDDR             | DDRX1 Clock Frequency           | ECP3-70EA/95EA           | _        | 250                  |         | 250                   |        | 250      | MHz   |

|                       | Data Valid Before CLK           | ECP3-35EA                | 683      | _                    | 688     | <u> </u>              | 690    | _        | ps    |

|                       | Data Valid After CLK            | ECP3-35EA                | 683      | _                    | 688     | —                     | 690    | —        | ps    |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-35EA                |          | 250                  | —       | 250                   | —      | 250      | MHz   |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-17EA                | 683      | —                    | 688     | —                     | 690    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                | 683      | —                    | 688     | —                     | 690    | —        | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-17EA                | —        | 250                  | —       | 250                   | —      | 250      | MHz   |

| Generic DDRX1 (       | Dutput with Clock and Data Alig | ned at Pin (GDDRX1_TX.   | SCLK.AI  | igned) <sup>10</sup> |         |                       |        |          |       |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | ECP3-150EA               | —        | 335                  | —       | 338                   | —      | 341      | ps    |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-150EA               |          | 335                  | —       | 338                   | —      | 341      | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA               |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Invalid Before Clock       | ECP3-70EA/95EA           | —        | 339                  | —       | 343                   | —      | 347      | ps    |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-70EA/95EA           | —        | 339                  | —       | 343                   | -      | 347      | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA           |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Invalid Before Clock       | ECP3-35EA                | —        | 322                  | —       | 320                   | —      | 321      | ps    |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-35EA                |          | 322                  | —       | 320                   | —      | 321      | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Invalid Before Clock       | ECP3-17EA                | _        | 322                  | —       | 320                   | —      | 321      | ps    |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-17EA                |          | 322                  | —       | 320                   | —      | 321      | ps    |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-17EA                |          | 250                  | —       | 250                   | —      | 250      | MHz   |

| Generic DDRX1 (       | Dutput with Clock and Data (<10 | Bits Wide) Centered at F | Pin (GDD | RX1_TX.              | DQS.Cer | ntered) <sup>10</sup> |        |          |       |

| Left and Right Si     | des                             |                          |          |                      |         |                       |        |          |       |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-150EA               | 670      | _                    | 670     | _                     | 670    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-150EA               | 670      | _                    | 670     | _                     | 670    | —        | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA               |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Valid Before CLK           | ECP3-70EA/95EA           | 657      | _                    | 652     | _                     | 650    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-70EA/95EA           | 657      | _                    | 652     | _                     | 650    | —        | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA           |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Valid Before CLK           | ECP3-35EA                | 670      | _                    | 675     | _                     | 676    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-35EA                | 670      | _                    | 675     | _                     | 676    | —        | ps    |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                |          | 250                  | —       | 250                   | —      | 250      | MHz   |

|                       | Data Valid Before CLK           | ECP3-17EA                | 670      | _                    | 670     | _                     | 670    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                | 670      | _                    | 670     | _                     | 670    | —        | ps    |

| f <sub>MAX GDDR</sub> | DDRX1 Clock Frequency           | ECP3-17EA                |          | 250                  | —       | 250                   | —      | 250      | MHz   |

| Generic DDRX2 (       | Dutput with Clock and Data (>10 | Bits Wide) Aligned at Pi | n (GDDR  | X2_TX.A              | ligned) |                       |        |          |       |

| Left and Right Si     | des                             |                          |          |                      |         |                       |        |          |       |

|                       | Data Invalid Before Clock       | All ECP3EA Devices       |          | 200                  | —       | 210                   | —      | 220      | ps    |

| tDIAGDDR              | Data Invalid After Clock        | All ECP3EA Devices       | _        | 200                  | —       | 210                   | —      | 220      | ps    |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices       | —        | 500                  | —       | 420                   | —      | 375      | MHz   |

| _                     | Output with Clock and Data (>10 | Bits Wide) Centered at F | in Usin  | g DQSDL              | L (GDDF | X2_TX.C               | QSDLL. | Centered | )11   |

| Left and Right Si     | des                             |                          |          |                      |         |                       |        |          |       |

|                       | Data Valid Before CLK           | All ECP3EA Devices       | 400      | _                    | 400     | _                     | 431    | —        | ps    |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | All ECP3EA Devices       | 400      | _                    | 400     | —                     | 432    | —        | ps    |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices       | _        | 400                  | _       | 400                   | _      | 375      | MHz   |

### **Over Recommended Commercial Operating Conditions**

## **DLL** Timing

### **Over Recommended Operating Conditions**

| Parameter                      | Description                                                                                          | Condition               | Min. | Тур. | Max.   | Units  |

|--------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|------|------|--------|--------|

| f <sub>REF</sub>               | Input reference clock frequency (on-chip or off-chip)                                                |                         | 133  | _    | 500    | MHz    |

| f <sub>FB</sub>                | Feedback clock frequency (on-chip or off-chip)                                                       |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOP</sub> 1           | Output clock frequency, CLKOP                                                                        |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOS<sup>2</sup></sub> | Output clock frequency, CLKOS                                                                        |                         | 33.3 |      | 500    | MHz    |

| t <sub>PJIT</sub>              | Output clock period jitter (clean input)                                                             |                         |      |      | 200    | ps p-p |

|                                | Output clock duty cycle (at 50% levels, 50% duty                                                     | Edge Clock              | 40   |      | 60     | %      |

| t <sub>DUTY</sub>              | cycle input clock, 50% duty cycle circuit turned off, time reference delay mode)                     | Primary Clock           | 30   |      | 70     | %      |

|                                | Output clock duty cycle (at 50% levels, arbitrary                                                    | Primary Clock < 250 MHz | 45   |      | 55     | %      |

| t <sub>DUTYTRD</sub>           | duty cycle input clock, 50% duty cycle circuit                                                       | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                | enabled, time reference delay mode)                                                                  | Edge Clock              | 45   |      | 55     | %      |

|                                | duty cycle input clock, 50% duty cycle circuit<br>IR enabled, clock injection removal mode) with DLL | Primary Clock < 250 MHz | 40   |      | 60     | %      |

| t <sub>DUTYCIR</sub>           |                                                                                                      | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                |                                                                                                      | Edge Clock              | 45   |      | 55     | %      |

| t <sub>SKEW</sub> <sup>3</sup> | Output clock to clock skew between two outputs with the same phase setting                           |                         | _    | _    | 100    | ps     |

| t <sub>PHASE</sub>             | Phase error measured at device pads between off-chip reference clock and feedback clocks             |                         | _    | _    | +/-400 | ps     |

| t <sub>PWH</sub>               | Input clock minimum pulse width high (at 80% level)                                                  |                         | 550  | _    | _      | ps     |

| t <sub>PWL</sub>               | Input clock minimum pulse width low (at 20% level)                                                   |                         | 550  | _    | _      | ps     |

| t <sub>INSTB</sub>             | Input clock period jitter                                                                            |                         | _    |      | 500    | ps     |

| t <sub>LOCK</sub>              | DLL lock time                                                                                        |                         | 8    | —    | 8200   | cycles |

| t <sub>RSWD</sub>              | Digital reset minimum pulse width (at 80% level)                                                     |                         | 3    |      |        | ns     |

| t <sub>DEL</sub>               | Delay step size                                                                                      |                         | 27   | 45   | 70     | ps     |

| t <sub>RANGE1</sub>            | Max. delay setting for single delay block (64 taps)                                                  |                         | 1.9  | 3.1  | 4.4    | ns     |

| t <sub>RANGE4</sub>            | Max. delay setting for four chained delay blocks                                                     |                         | 7.6  | 12.4 | 17.6   | ns     |

1. CLKOP runs at the same frequency as the input clock.

2. CLKOS minimum frequency is obtained with divide by 4.

3. This is intended to be a "path-matching" design guideline and is not a measurable specification.

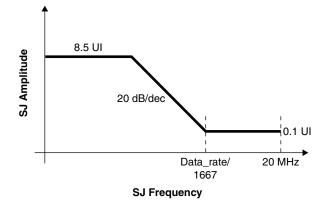

## Figure 3-18. XAUI Sinusoidal Jitter Tolerance Mask

Note: The sinusoidal jitter tolerance is measured with at least 0.37 UIpp of Deterministic jitter (Dj) and the sum of Dj and Rj (random jitter) is at least 0.55 UIpp. Therefore, the sum of Dj, Rj and Sj (sinusoidal jitter) is at least 0.65 UIpp (Dj = 0.37, Rj = 0.18, Sj = 0.1).

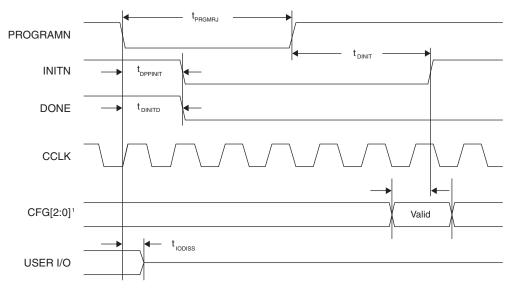

### Figure 3-26. Configuration from PROGRAMN Timing

1. The CFG pins are normally static (hard wired)

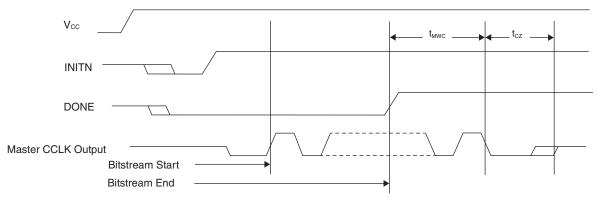

#### Figure 3-27. Wake-Up Timing

## **Switching Test Conditions**

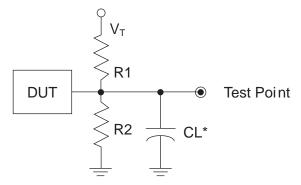

Figure 3-33 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-23.

### Figure 3-33. Output Test Load, LVTTL and LVCMOS Standards

\*CL Includes Test Fixture and Probe Capacitance

| Test Condition                                   | R <sub>1</sub>                         | R <sub>2</sub> | CL   | Timing Ref.                       | V <sub>T</sub>    |

|--------------------------------------------------|----------------------------------------|----------------|------|-----------------------------------|-------------------|

|                                                  |                                        |                |      | LVCMOS 3.3 = 1.5V                 | —                 |

|                                                  |                                        |                |      | LVCMOS 2.5 = $V_{CCIO}/2$         | —                 |

| LVTTL and other LVCMOS settings (L -> H, H -> L) | ∞ 0                                    | $\infty$       | 0 pF | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.5 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | —                 |

| LVCMOS 2.5 I/O (Z -> H)                          | x                                      | 1MΩ            | 0 pF | V <sub>CCIO</sub> /2              | —                 |

| LVCMOS 2.5 I/O (Z -> L)                          | 1 MΩ                                   | $\infty$       | 0 pF | V <sub>CCIO</sub> /2              | V <sub>CCIO</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 100            | 0 pF | V <sub>OH</sub> - 0.10            | —                 |

| LVCMOS 2.5 I/O (L -> Z)                          | 100                                    | $\infty$       | 0 pF | V <sub>OL</sub> + 0.10            | V <sub>CCIO</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

## PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with<br>DQS Strobe     | PIO Within PIC | DDR Strobe (DQS) and<br>Data (DQ) Pins |  |  |  |  |  |

|----------------------------------------|----------------|----------------------------------------|--|--|--|--|--|

| For Left and Right Edges of the Device |                |                                        |  |  |  |  |  |

| P[Edge] [n-3]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n-2]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n-1]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n]                            | А              | [Edge]DQSn                             |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n+1]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n+2]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| For Top Edge of the Devic              | e              | ·                                      |  |  |  |  |  |

| D[Edga] [n 2]                          | А              | DQ                                     |  |  |  |  |  |

| P[Edge] [n-3]                          | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n-2]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n-1]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| D[Edga] [n]                            | А              | [Edge]DQSn                             |  |  |  |  |  |

| P[Edge] [n]                            | В              | DQ                                     |  |  |  |  |  |

| P[Edge] [n+1]                          | А              | DQ                                     |  |  |  |  |  |

|                                        | В              | DQ                                     |  |  |  |  |  |

| D[Edgo] [n   2]                        | А              | DQ                                     |  |  |  |  |  |

| P[Edge] [n+2]                          | В              | DQ                                     |  |  |  |  |  |

Note: "n" is a row PIC number.

## **Pin Information Summary**

| Pin Information Summary                    |        | E            | CP3-17E      | A            | ECP3-35EA    |              |              | ECP3-70EA    |              |               |

|--------------------------------------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Pin Type                                   |        | 256<br>ftBGA | 328<br>csBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672<br>fpBGA | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                            | Bank 0 | 26           | 20           | 36           | 26           | 42           | 48           | 42           | 60           | 86            |

|                                            | Bank 1 | 14           | 10           | 24           | 14           | 36           | 36           | 36           | 48           | 78            |

|                                            | Bank 2 | 6            | 7            | 12           | 6            | 24           | 24           | 24           | 34           | 36            |

| General Purpose<br>Inputs/Outputs per Bank | Bank 3 | 18           | 12           | 44           | 16           | 54           | 59           | 54           | 59           | 86            |

|                                            | Bank 6 | 20           | 11           | 44           | 18           | 63           | 61           | 63           | 67           | 86            |

|                                            | Bank 7 | 19           | 26           | 32           | 19           | 36           | 42           | 36           | 48           | 54            |

|                                            | Bank 8 | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24            |

|                                            | Bank 0 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2 | 2            | 2            | 2            | 2            | 4            | 4            | 4            | 8            | 8             |

| General Purpose Inputs per Bank            | Bank 3 | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

| per Darik                                  | Bank 6 | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

|                                            | Bank 7 | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 8            | 8             |

|                                            | Bank 8 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 0 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| General Purpose Out-                       | Bank 3 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| puts per Bank                              | Bank 6 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 7 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 8 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| Total Single-Ended User I/O                |        | 133          | 116          | 222          | 133          | 295          | 310          | 295          | 380          | 490           |

| VCC                                        |        | 6            | 16           | 16           | 6            | 16           | 32           | 16           | 32           | 32            |

| VCCAUX                                     |        | 4            | 5            | 8            | 4            | 8            | 12           | 8            | 12           | 16            |

| VTT                                        |        | 4            | 7            | 4            | 4            | 4            | 4            | 4            | 4            | 8             |

| VCCA                                       |        | 4            | 6            | 4            | 4            | 4            | 8            | 4            | 8            | 16            |

| VCCPLL                                     |        | 2            | 2            | 4            | 2            | 4            | 4            | 4            | 4            | 4             |

|                                            | Bank 0 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 1 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 2 | 2            | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

| VCCIO                                      | Bank 3 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 6 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 7 | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 8 | 1            | 2            | 2            | 1            | 2            | 2            | 2            | 2            | 2             |

| VCCJ                                       |        | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1             |

| ТАР                                        |        | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4             |

| GND, GNDIO                                 |        | 51           | 126          | 98           | 51           | 98           | 139          | 98           | 139          | 233           |

| NC                                         |        | 0            | 0            | 73           | 0            | 0            | 96           | 0            | 0            | 238           |

| Reserved <sup>1</sup>                      |        | 0            | 0            | 2            | 0            | 2            | 2            | 2            | 2            | 2             |

| SERDES                                     |        | 26           | 18           | 26           | 26           | 26           | 26           | 26           | 52           | 78            |

| Miscellaneous Pins                         |        | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8             |

| Total Bonded Pins                          |        | 256          | 328          | 484          | 256          | 484          | 672          | 484          | 672          | 1156          |

## Pin Information Summary (Cont.)

| Pin Information Summary<br>Pin Type        |                      | ECP3-70EA |           |            |  |  |  |

|--------------------------------------------|----------------------|-----------|-----------|------------|--|--|--|

|                                            |                      | 484 fpBGA | 672 fpBGA | 1156 fpBGA |  |  |  |

|                                            | Bank 0               | 21        | 30        | 43         |  |  |  |

|                                            | Bank 1               | 18        | 24        | 39         |  |  |  |

|                                            | Bank 2               | 8         | 12        | 13         |  |  |  |

| Emulated Differential<br>I/O per Bank      | Bank 3               | 20        | 23        | 33         |  |  |  |

|                                            | Bank 6               | 22        | 25        | 33         |  |  |  |

|                                            | Bank 7               | 11        | 16        | 18         |  |  |  |

|                                            | Bank 8               | 12        | 12        | 12         |  |  |  |

|                                            | Bank 0               | 0         | 0         | 0          |  |  |  |

|                                            | Bank 1               | 0         | 0         | 0          |  |  |  |

|                                            | Bank 2               | 6         | 9         | 9          |  |  |  |

| High-Speed Differential I/<br>O per Bank   | Bank 3               | 9         | 12        | 16         |  |  |  |

| o por Barik                                | Bank 6               | 11        | 14        | 16         |  |  |  |

|                                            | Bank 7               | 9         | 12        | 13         |  |  |  |

|                                            | Bank 8               | 0         | 0         | 0          |  |  |  |

|                                            | Bank 0               | 42/21     | 60/30     | 86/43      |  |  |  |

|                                            | Bank 1               | 36/18     | 48/24     | 78/39      |  |  |  |

| Total Single-Ended/                        | Bank 2               | 28/14     | 42/21     | 44/22      |  |  |  |

| Total Differential I/O                     | Bank 3               | 58/29     | 71/35     | 98/49      |  |  |  |

| per Bank                                   | Bank 6               | 67/33     | 78/39     | 98/49      |  |  |  |

|                                            | Bank 7               | 40/20     | 56/28     | 62/31      |  |  |  |

|                                            | Bank 8               | 24/12     | 24/12     | 24/12      |  |  |  |

|                                            | Bank 0               | 3         | 5         | 7          |  |  |  |

|                                            | Bank 1               | 3         | 4         | 7          |  |  |  |

| DDR Groups Bonded<br>per Bank <sup>1</sup> | Bank 2               | 2         | 3         | 3          |  |  |  |

|                                            | Bank 3               | 3         | 4         | 5          |  |  |  |

|                                            | Bank 6               | 4         | 4         | 5          |  |  |  |

|                                            | Bank 7               | 3         | 4         | 4          |  |  |  |

|                                            | Configuration Bank 8 | 0         | 0         | 0          |  |  |  |

| SERDES Quads                               |                      | 1         | 2         | 3          |  |  |  |

1. Some DQS groups may not support DQS-12. Refer to the device pinout (.csv) file.

## LatticeECP3 Family Data Sheet Supplemental Information

#### February 2014

#### Data Sheet DS1021

## **For Further Information**

A variety of technical notes for the LatticeECP3 family are available on the Lattice website at <u>www.latticesemi.com</u>.

- TN1169, LatticeECP3 sysCONFIG Usage Guide

- TN1176, LatticeECP3 SERDES/PCS Usage Guide

- TN1177, LatticeECP3 sysIO Usage Guide

- TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide

- TN1179, LatticeECP3 Memory Usage Guide

- TN1180, LatticeECP3 High-Speed I/O Interface

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- TN1182, LatticeECP3 sysDSP Usage Guide

- TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide

- TN1189, LatticeECP3 Hardware Checklist

- TN1215, LatticeECP2MS and LatticeECP2S Devices

- TN1216, LatticeECP2/M and LatticeECP3 Dual Boot Feature Advanced Security Encryption Key Programming Guide for LatticeECP3

- TN1222, LatticeECP3 Slave SPI Port User's Guide

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: www.pcisig.com

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## LatticeECP3 Family Data Sheet Revision History

March 2015

Data Sheet DS1021

| Date           | Version | Section                                | Change Summary                                                                                                                                                                                                                                                  |

|----------------|---------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2015     | 2.8EA   | Pinout Information<br>All              | Updated Package Pinout Information section. Changed reference to http://www.latticesemi.com/Products/FPGAandCPLD/LatticeECP3.                                                                                                                                   |

|                |         |                                        | Minor style/formatting changes.                                                                                                                                                                                                                                 |

| April 2014     | 02.7EA  | DC and Switching                       | Updated LatticeECP3 Supply Current (Standby) table power numbers.                                                                                                                                                                                               |

|                |         | Characteristics                        | Removed speed grade -9 timing numbers in the following sections:<br>— Typical Building Block Function Performance<br>— LatticeECP3 External Switching Characteristics<br>— LatticeECP3 Internal Switching Characteristics<br>— LatticeECP3 Family Timing Adders |

|                |         | Ordering Information                   | Removed ordering information for -9 speed grade devices.                                                                                                                                                                                                        |

| March 2014     | 02.6EA  | DC and Switching<br>Characteristics    | Added information to the sysl/O Single-Ended DC Electrical Character-<br>istics section footnote.                                                                                                                                                               |

| February 2014  | 02.5EA  | DC and Switching<br>Characteristics    | Updated Hot Socketing Specifications table. Changed $I_{PW}$ to $I_{PD}$ in footnote 3.                                                                                                                                                                         |

|                |         |                                        | Updated the following figures:<br>— Figure 3-25, sysCONFIG Port Timing<br>— Figure 3-27, Wake-Up Timing                                                                                                                                                         |

|                |         | Supplemental<br>Information            | Added technical note references.                                                                                                                                                                                                                                |

| September 2013 | 02.4EA  | EA DC and Switching<br>Characteristics | Updated the Wake-Up Timing Diagram                                                                                                                                                                                                                              |

|                |         |                                        | Added the following figures:<br>— Master SPI POR Waveforms<br>— SPI Configuration Waveforms<br>— Slave SPI HOLDN Waveforms                                                                                                                                      |

|                |         |                                        | Added tIODISS and tIOENSS parameters in LatticeECP3 sysCONFIG Port Timing Specifications table.                                                                                                                                                                 |

| June 2013      | 02.3EA  | Architecture                           | sysl/O Buffer Banks text section – Updated description of "Top (Bank 0<br>and Bank 1) and Bottom syslO Buffer Pairs (Single-Ended Outputs<br>Only)" for hot socketing information.                                                                              |

|                |         |                                        | sysl/O Buffer Banks text section – Updated description of "Configuration<br>Bank sysl/O Buffer Pairs (Single-Ended Outputs, Only on Shared Pins<br>When Not Used by Configuration)" for PCI clamp information.                                                  |

|                |         |                                        | On-Chip Oscillator section – clarified the speed of the internal CMOS oscillator (130 MHz +/- 15%).                                                                                                                                                             |

|                |         |                                        | Architecture Overview section – Added information on the state of the register on power up and after configuration.                                                                                                                                             |

|                |         | DC and Switching<br>Characteristics    | sysl/O Recommended Operating Conditions table – Removed reference to footnote 1 from RSDS standard.                                                                                                                                                             |

|                |         |                                        | sysl/O Single-Ended DC Electrical Characteristics table – Modified foot-<br>note 1.                                                                                                                                                                             |

|                |         |                                        | Added Oscillator Output Frequency table.                                                                                                                                                                                                                        |

|                |         |                                        | LatticeECP3 sysCONFIG Port Timing Specifications table – Updated min. column for t <sub>CODO</sub> parameter.                                                                                                                                                   |

|                |         |                                        | LatticeECP3 Family Timing Adders table – Description column, references to VCCIO = 3.0V changed to 3.3V. For PPLVDS, description changed from emulated to True LVDS and VCCIO = 2.5V changed to VCCIO = 2.5V or 3.3V.                                           |

© 2015 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                            |

|---------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | LatticeECP3 Maximum I/O Buffer Speed table – Description column, references to VCCIO = 3.0V changed to 3.3V.                                                                                                                                                                              |

|               |         |                                     | Updated SERDES External Reference Clock Waveforms.                                                                                                                                                                                                                                        |

|               |         |                                     | Transmitter and Receiver Latency Block Diagram – Updated sections of the diagram to match descriptions on the SERDES/PCS Latency Break-<br>down table.                                                                                                                                    |

|               |         | Pinout Information                  | "Logic Signal Connections" section heading renamed "Package Pinout<br>Information". Software menu selections within this section have been<br>updated.                                                                                                                                    |

|               |         |                                     | Signal Descriptions table – Updated description for V <sub>CCA</sub> signal.                                                                                                                                                                                                              |

| April 2012    | 02.2EA  | Architecture                        | Updated first paragraph of Output Register Block section.                                                                                                                                                                                                                                 |

|               |         |                                     | Updated the information about sysIO buffer pairs below Figure 2-38.                                                                                                                                                                                                                       |

|               |         |                                     | Updated the information relating to migration between devices in the Density Shifting section.                                                                                                                                                                                            |

|               |         | DC and Switching<br>Characteristics | Corrected the Definitions in the sysCLOCK PLL Timing table for $\ensuremath{t_{RST}}$                                                                                                                                                                                                     |

|               |         | Ordering Information                | Updated topside marks with new logos in the Ordering Information sec-<br>tion.                                                                                                                                                                                                            |

| February 2012 | 02.1EA  | All                                 | Updated document with new corporate logo.                                                                                                                                                                                                                                                 |

| November 2011 | 02.0EA  | Introduction                        | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                                                                                                                                                           |

|               |         | Architecture                        | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                                                                                                                                                           |

|               |         | DC and Switching<br>Characteristics | Updated LatticeECP3 Supply Current table power numbers.                                                                                                                                                                                                                                   |

|               |         |                                     | Typical Building Block Function Performance table, LatticeECP3 Exter-<br>nal Switching Characteristics table, LatticeECP3 Internal Switching<br>Characteristics table and LatticeECP3 Family Timing Adders: Added<br>speed grade -9 and updated speed grade -8, -7 and -6 timing numbers. |

|               |         | Pinout Information                  | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                                                                                                                                                           |

|               |         | Ordering Information                | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                                                                                                                                                           |

|               |         |                                     | Added ordering information for low power devices and -9 speed grade devices.                                                                                                                                                                                                              |

| July 2011     | 01.9EA  | DC and Switching<br>Characteristics | Removed ESD Performance table and added reference to LatticeECP3<br>Product Family Qualification Summary document.                                                                                                                                                                        |

|               |         |                                     | sysCLOCK PLL TIming table, added footnote 4.                                                                                                                                                                                                                                              |

|               |         |                                     | External Reference Clock Specification table – removed reference to<br>VREF-CM-AC and removed footnote for VREF-CM-AC.                                                                                                                                                                    |

|               |         | Pinout Information                  | Pin Information Summary table: Corrected VCCIO Bank8 data for LatticeECP3-17EA 256-ball ftBGA package and LatticeECP-35EA 256-ball ftBGA package.                                                                                                                                         |

| April 2011    | 01.8EA  | Architecture                        | Updated Secondary Clock/Control Sources text section.                                                                                                                                                                                                                                     |

|               |         | DC and Switching<br>Characteristics | Added data for 150 Mbps to SERDES Power Supply Requirements table.                                                                                                                                                                                                                        |

|               |         |                                     | Updated Frequencies in Table 3-6 Serial Output Timing and Levels                                                                                                                                                                                                                          |

|               |         |                                     | Added Data for 150 Mbps to Table 3-7 Channel Output Jitter                                                                                                                                                                                                                                |

|               |         |                                     | Corrected External Switching Characteristics table, Description for DDR3 Clock Timing, $t_{JIT}$ .                                                                                                                                                                                        |

|               |         |                                     | Corrected Internal Switching Characteristics table, Description for EBR Timing, t <sub>SUWREN_EBR</sub> and t <sub>HWREN_EBR</sub> .                                                                                                                                                      |

|               |         |                                     | Added footnote 1 to sysConfig Port Timing Specifications table.                                                                                                                                                                                                                           |

|               |         |                                     | Updated description for RX-CIDs to 150M in Table 3-9 Serial Input Data Specifications                                                                                                                                                                                                     |

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                           |

|---------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                                   |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                                 |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                                           |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                                             |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                                  |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                               |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added SERDES/PCS Block Latency Breakdown table.                                                                                                                                                                                                                                                                                                          |