# E.J. Lattice Semiconductor Corporation - <u>LFE3-35EA-6FN484C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                                         |

| Number of Logic Elements/Cells | 33000                                                                        |

| Total RAM Bits                 | 1358848                                                                      |

| Number of I/O                  | 295                                                                          |

| Number of Gates                |                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-6fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The LatticeECP3<sup>™</sup> (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

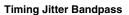

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>™</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

## Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### RAM Mode

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals. A 16x2-bit pseudo dual port RAM (PDPR) memory is created by using one Slice as the read-write port and the other companion slice as the read-only port.

LatticeECP3 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in LatticeECP3 devices, please see TN1179, LatticeECP3 Memory Usage Guide.

#### Table 2-3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

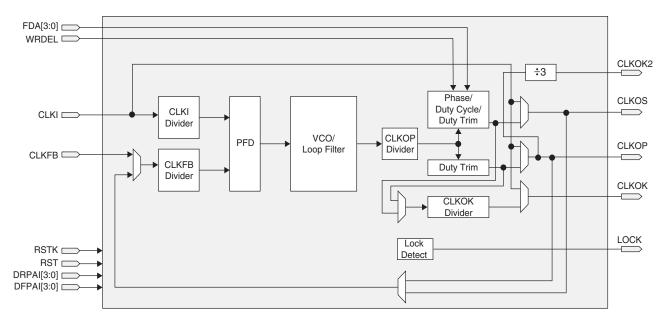

Figure 2-4. General Purpose PLL Diagram

Table 2-4 provides a description of the signals in the PLL blocks.

Table 2-4. PLL Blocks Signal Descriptions

| Signal     | I/O | Description                                                               |  |  |  |

|------------|-----|---------------------------------------------------------------------------|--|--|--|

| CLKI       | I   | Clock input from external pin or routing                                  |  |  |  |

| CLKFB      | I   | PLL feedback input from CLKOP, CLKOS, or from a user clock (pin or logic) |  |  |  |

| RST        | I   | "1" to reset PLL counters, VCO, charge pumps and M-dividers               |  |  |  |

| RSTK       | I   | "1" to reset K-divider                                                    |  |  |  |

| WRDEL      | I   | DPA Fine Delay Adjust input                                               |  |  |  |

| CLKOS      | 0   | output to clock tree (phase shifted/duty cycle changed)                   |  |  |  |

| CLKOP      | 0   | output to clock tree (no phase shift)                                     |  |  |  |

| CLKOK      | 0   | output to clock tree through secondary clock divider                      |  |  |  |

| CLKOK2     | 0   | output to clock tree (CLKOP divided by 3)                                 |  |  |  |

| LOCK       | 0   | "1" indicates PLL LOCK to CLKI                                            |  |  |  |

| FDA [3:0]  | I   | namic fine delay adjustment on CLKOS output                               |  |  |  |

| DRPAI[3:0] | I   | ynamic coarse phase shift, rising edge setting                            |  |  |  |

| DFPAI[3:0] | I   | Dynamic coarse phase shift, falling edge setting                          |  |  |  |

## Delay Locked Loops (DLL)

In addition to PLLs, the LatticeECP3 family of devices has two DLLs per device.

CLKI is the input frequency (generated either from the pin or routing) for the DLL. CLKI feeds into the output muxes block to bypass the DLL, directly to the DELAY CHAIN block and (directly or through divider circuit) to the reference input of the Phase Detector (PD) input mux. The reference signal for the PD can also be generated from the Delay Chain signals. The feedback input to the PD is generated from the CLKFB pin or from a tapped signal from the Delay chain.

The PD produces a binary number proportional to the phase and frequency difference between the reference and feedback signals. Based on these inputs, the ALU determines the correct digital control codes to send to the delay

#### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

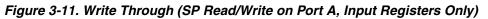

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

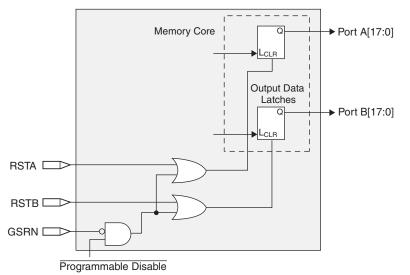

#### Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

#### Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

## sysDSP<sup>™</sup> Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

### sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-32. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as LVDS inputs.

#### Table 2-11. PIO Signal List

| Name                                                     | Туре                             | Description                                                                                                                                                                                                                                               |

|----------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDD                                                     | Input Data                       | Register bypassed input. This is not the same port as INCK.                                                                                                                                                                                               |

| IPA, INA, IPB, INB                                       | Input Data                       | Ports to core for input data                                                                                                                                                                                                                              |

| OPOSA, ONEGA <sup>1</sup> ,<br>OPOSB, ONEGB <sup>1</sup> | Output Data                      | Output signals from core. An exception is the ONEGB port, used for tristate logic at the DQS pad.                                                                                                                                                         |

| CE                                                       | PIO Control                      | Clock enables for input and output block flip-flops.                                                                                                                                                                                                      |

| SCLK                                                     | PIO Control                      | System Clock (PCLK) for input and output/TS blocks. Connected from clock ISB.                                                                                                                                                                             |

| LSR                                                      | PIO Control                      | Local Set/Reset                                                                                                                                                                                                                                           |

| ECLK1, ECLK2                                             | PIO Control                      | Edge clock sources. Entire PIO selects one of two sources using mux.                                                                                                                                                                                      |

| ECLKDQSR <sup>1</sup>                                    | Read Control                     | From DQS_STROBE, shifted strobe for memory interfaces only.                                                                                                                                                                                               |

| DDRCLKPOL <sup>1</sup>                                   | Read Control                     | Ensures transfer from DQS domain to SCLK domain.                                                                                                                                                                                                          |

| DDRLAT <sup>1</sup>                                      | Read Control                     | Used to guarantee INDDRX2 gearing by selectively enabling a D-Flip-Flop in dat-<br>apath.                                                                                                                                                                 |

| DEL[3:0]                                                 | Read Control                     | Dynamic input delay control bits.                                                                                                                                                                                                                         |

| INCK                                                     | To Clock Distribution<br>and PLL | PIO treated as clock PIO, path to distribute to primary clocks and PLL.                                                                                                                                                                                   |

| TS                                                       | Tristate Data                    | Tristate signal from core (SDR)                                                                                                                                                                                                                           |

| DQCLK0 <sup>1</sup> , DQCLK1 <sup>1</sup>                | Write Control                    | Two clocks edges, 90 degrees out of phase, used in output gearing.                                                                                                                                                                                        |

| DQSW <sup>2</sup>                                        | Write Control                    | Used for output and tristate logic at DQS only.                                                                                                                                                                                                           |

| DYNDEL[7:0]                                              | Write Control                    | Shifting of write clocks for specific DQS group, using 6:0 each step is approxi-<br>mately 25ps, 128 steps. Bit 7 is an invert (timing depends on input frequency).<br>There is also a static control for this 8-bit setting, enabled with a memory cell. |

| DCNTL[6:0]                                               | PIO Control                      | Original delay code from DDR DLL                                                                                                                                                                                                                          |

| DATAVALID <sup>1</sup>                                   | Output Data                      | Status flag from DATAVALID logic, used to indicate when input data is captured in IOLOGIC and valid to core.                                                                                                                                              |

| READ                                                     | For DQS_Strobe                   | Read signal for DDR memory interface                                                                                                                                                                                                                      |

| DQSI                                                     | For DQS_Strobe                   | Unshifted DQS strobe from input pad                                                                                                                                                                                                                       |

| PRMBDET                                                  | For DQS_Strobe                   | DQSI biased to go high when DQSI is tristate, goes to input logic block as well as core logic.                                                                                                                                                            |

| GSRN                                                     | Control from routing             | Global Set/Reset                                                                                                                                                                                                                                          |

|                                                          |                                  |                                                                                                                                                                                                                                                           |

1. Signals available on left/right/top edges only.

2. Selected PIO.

# PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

### Input Register Block

The input register blocks for the PIOs, in the left, right and top edges, contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-33 shows the input register block for the left, right and top edges. The input register block for the bottom edge contains one element to register the input signal and no DDR registers. The following description applies to the input register block for PIOs in the left, right and top edges only.

### **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces, a PLL is used for this adjustment. However, in DDR memories the clock (referred to as DQS) is not free-running so this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

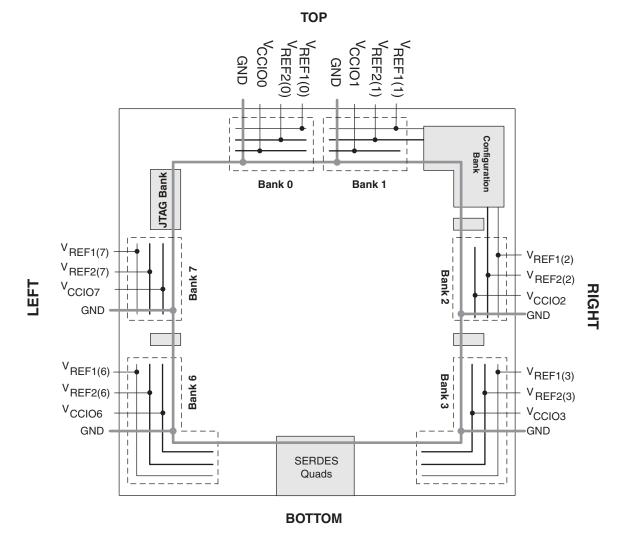

The delay required for the DQS signal is generated by two dedicated DLLs (DDR DLL) on opposite side of the device. Each DLL creates DQS delays in its half of the device as shown in Figure 2-36. The DDR DLL on the left side will generate delays for all the DQS Strobe pins on Banks 0, 7 and 6 and DDR DLL on the right will generate delays for all the DQS pins on Banks 1, 2 and 3. The DDR DLL loop compensates for temperature, voltage and process variations by using the system clock and DLL feedback loop. DDR DLL communicates the required delay to the DQS delay block using a 7-bit calibration bus (DCNTL[6:0])

The DQS signal (selected PIOs only, as shown in Figure 2-35) feeds from the PAD through a DQS control logic block to a dedicated DQS routing resource. The DQS control logic block consists of DQS Read Control logic block that generates control signals for the read side and DQS Write Control logic that generates the control signals required for the write side. A more detailed DQS control diagram is shown in Figure 2-37, which shows how the DQS control blocks interact with the data paths.

The DQS Read control logic receives the delay generated by the DDR DLL on its side and delays the incoming DQS signal by 90 degrees. This delayed ECLKDQSR is routed to 10 or 11 DQ pads covered by that DQS signal. This block also contains a polarity control logic that generates a DDRCLKPOL signal, which controls the polarity of the clock to the sync registers in the input register blocks. The DQS Read control logic also generates a DDRLAT signal that is in the input register block to transfer data from the first set of DDR register to the second set of DDR registers when using the DDRX2 gearbox mode for DDR3 memory interface.

The DQS Write control logic block generates the DQCLK0 and DQCLK1 clocks used to control the output gearing in the Output register block which generates the DDR data output and the DQS output. They are also used to control the generation of the DQS output through the DQS output register block. In addition to the DCNTL [6:0] input from the DDR DLL, the DQS Write control block also uses a Dynamic Delay DYN DEL [7:0] attribute which is used to further delay the DQS to accomplish the write leveling found in DDR3 memory. Write leveling is controlled by the DDR memory controller implementation. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock. This will generate the DQSW signal used to generate the DQS output in the DQS output register block.

Figure 2-36 and Figure 2-37 show how the DQS transition signals that are routed to the PIOs.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

#### Figure 2-38. LatticeECP3 Banks

LatticeECP3 devices contain two types of sysI/O buffer pairs.

#### 1. Top (Bank 0 and Bank 1) and Bottom sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysl/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input. Only the top edge buffers have a programmable PCI clamp.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

The top and bottom sides are ideal for general purpose I/O, PCI, and inputs for LVDS (LVDS outputs are only allowed on the left and right sides). The top side can be used for the DDR3 ADDR/CMD signals.

The I/O pins located on the top and bottom sides of the device (labeled PTxxA/B or PBxxA/B) are fully hot socketable. Note that the pads in Banks 3, 6 and 8 are wrapped around the corner of the device. In these banks, only the pads located on the top or bottom of the device are hot socketable. The top and bottom side pads can be identified by the Lattice Diamond tool.

Please see TN1177, LatticeECP3 sysIO Usage Guide for on-chip termination usage and value ranges.

## **Equalization Filter**

Equalization filtering is available for single-ended inputs on both true and complementary I/Os, and for differential inputs on the true I/Os on the left, right, and top sides. Equalization is required to compensate for the difficulty of sampling alternating logic transitions with a relatively slow slew rate. It is considered the most useful for the Input DDRX2 modes, used in DDR3 memory, LVDS, or TRLVDS signaling. Equalization filter acts as a tunable filter with settings to determine the level of correction. In the LatticeECP3 devices, there are four settings available: 0 (none), 1, 2 and 3. The default setting is 0. The equalization logic resides in the sysI/O buffers, the two bits of setting is set uniquely in each input IOLOGIC block. Therefore, each sysI/O can have a unique equalization setting within a DQS-12 group.

### Hot Socketing

LatticeECP3 devices have been carefully designed to ensure predictable behavior during power-up and powerdown. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. Please refer to the Hot Socketing Specifications in the DC and Switching Characteristics in this data sheet.

# SERDES and PCS (Physical Coding Sublayer)

LatticeECP3 devices feature up to 16 channels of embedded SERDES/PCS arranged in quads at the bottom of the devices supporting up to 3.2Gbps data rate. Figure 2-40 shows the position of the quad blocks for the LatticeECP3-150 devices. Table 2-14 shows the location of available SERDES Quads for all devices.

The LatticeECP3 SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express 1.1

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- Serial RapidIO

- SMPTE SDI (3G, HD, SD)

- CPRI

- SONET/SDH (STS-3, STS-12, STS-48)

Each quad contains four dedicated SERDES for high speed, full duplex serial data transfer. Each quad also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in quads, multiple baud rates can be supported within a quad with the use of dedicated, per channel  $\div$ 1,  $\div$ 2 and  $\div$ 11 rate dividers. Additionally, multiple quads can be arranged together to form larger data pipes.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, please refer to TN1176, LatticeECP3 SERDES/PCS Usage Guide.

## **Enhanced Configuration Options**

LatticeECP3 devices have enhanced configuration features such as: decryption support, TransFR™ I/O and dualboot image support.

#### 1. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. See TN1087, Minimizing System Interruption During Configuration Using TransFR Technology for details.

#### 2. Dual-Boot Image Support

Dual-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeECP3 can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the LatticeECP3 device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

#### Soft Error Detect (SED) Support

LatticeECP3 devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the LatticeECP3 device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

For further information on SED support, please see TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide.

#### **External Resistor**

LatticeECP3 devices require a single external, 10 kOhm  $\pm$ 1% value between the XRES pin and ground. Device configuration will not be completed if this resistor is missing. There is no boundary scan register on the external resistor pad.

#### **On-Chip Oscillator**

Every LatticeECP3 device has an internal CMOS oscillator which is used to derive a Master Clock (MCCLK) for configuration. The oscillator and the MCCLK run continuously and are available to user logic after configuration is completed. The software default value of the MCCLK is nominally 2.5 MHz. Table 2-16 lists all the available MCCLK frequencies. When a different Master Clock is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal Master Clock frequency of 3.1 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The Master Clock frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCCLK frequency of 2.5 MHz.

This internal 130 MHz +/- 15% CMOS oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

## **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

# LatticeECP3 Supply Current (Standby)<sup>1, 2, 3, 4, 5, 6</sup>

|                    |                                                                   | Device      | Турі          | Typical    |       |  |

|--------------------|-------------------------------------------------------------------|-------------|---------------|------------|-------|--|

| Symbol             | Parameter                                                         |             | -6L, -7L, -8L | -6, -7, -8 | Units |  |

|                    |                                                                   | ECP-17EA    | 29.8          | 49.4       | mA    |  |

|                    |                                                                   | ECP3-35EA   | 53.7          | 89.4       | mA    |  |

| I <sub>CC</sub>    | Core Power Supply Current                                         | ECP3-70EA   | 137.3         | 230.7      | mA    |  |

|                    |                                                                   | ECP3-95EA   | 137.3         | 230.7      | mA    |  |

|                    |                                                                   | ECP3-150EA  | 219.5         | 370.9      | mA    |  |

|                    |                                                                   | ECP-17EA    | 18.3          | 19.4       | mA    |  |

|                    |                                                                   | ECP3-35EA   | 19.6          | 23.1       | mA    |  |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current                                    | ECP3-70EA   | 26.5          | 32.4       | mA    |  |

|                    |                                                                   | ECP3-95EA   | 26.5          | 32.4       | mA    |  |

|                    |                                                                   | ECP3-150EA  | 37.0          | 45.7       | mA    |  |

|                    | PLL Power Supply Current (Per PLL)                                | ECP-17EA    | 0.0           | 0.0        | mA    |  |

|                    |                                                                   | ECP3-35EA   | 0.1           | 0.1        | mA    |  |

| I <sub>CCPLL</sub> |                                                                   | ECP3-70EA   | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP3-95EA   | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP3-150EA  | 0.1           | 0.1        | mA    |  |

|                    |                                                                   | ECP-17EA    | 1.3           | 1.4        | mA    |  |

|                    |                                                                   | ECP3-35EA   | 1.3           | 1.4        | mA    |  |

| I <sub>CCIO</sub>  | Bank Power Supply Current (Per Bank)                              | ECP3-70EA   | 1.4           | 1.5        | mA    |  |

|                    |                                                                   | ECP3-95EA   | 1.4           | 1.5        | mA    |  |

|                    |                                                                   | ECP3-150EA  | 1.4           | 1.5        | mA    |  |

| I <sub>CCJ</sub>   | JTAG Power Supply Current                                         | All Devices | 2.5           | 2.5        | mA    |  |

|                    |                                                                   | ECP-17EA    | 6.1           | 6.1        | mA    |  |

|                    |                                                                   | ECP3-35EA   | 6.1           | 6.1        | mA    |  |

| I <sub>CCA</sub>   | Transmit, Receive, PLL and<br>Reference Clock Buffer Power Supply | ECP3-70EA   | 18.3          | 18.3       | mA    |  |

|                    |                                                                   | ECP3-95EA   | 18.3          | 18.3       | mA    |  |

|                    |                                                                   | ECP3-150EA  | 24.4          | 24.4       | mA    |  |

## **Over Recommended Operating Conditions**

1. For further information on supply current, please see the list of technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Frequency 0 MHz.

4. Pattern represents a "blank" configuration data file.

5.  $T_J = 85$  °C, power supplies at nominal voltage.

6. To determine the LatticeECP3 peak start-up current data, use the Power Calculator tool.

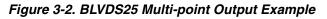

## **BLVDS25**

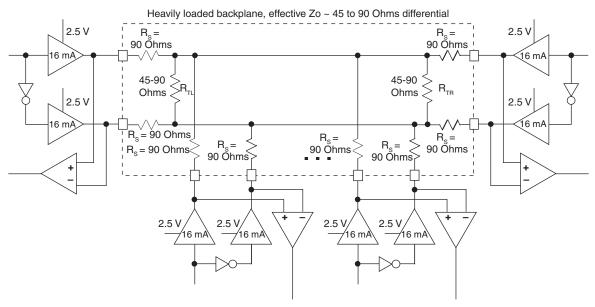

The LatticeECP3 devices support the BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

Table 3-2. BLVDS25 DC Conditions<sup>1</sup>

| Over Recommended Operating Conditions |                                   |                  |                  |       |  |  |  |

|---------------------------------------|-----------------------------------|------------------|------------------|-------|--|--|--|

|                                       |                                   | Тур              | Typical          |       |  |  |  |

| Parameter                             | Description                       | <b>Ζο = 45</b> Ω | <b>Ζο = 90</b> Ω | Units |  |  |  |

| V <sub>CCIO</sub>                     | Output Driver Supply (+/- 5%)     | 2.50             | 2.50             | V     |  |  |  |

| Z <sub>OUT</sub>                      | Driver Impedance                  | 10.00            | 10.00            | Ω     |  |  |  |

| R <sub>S</sub>                        | Driver Series Resistor (+/- 1%)   | 90.00            | 90.00            | Ω     |  |  |  |

| R <sub>TL</sub>                       | Driver Parallel Resistor (+/- 1%) | 45.00            | 90.00            | Ω     |  |  |  |

| R <sub>TR</sub>                       | Receiver Termination (+/- 1%)     | 45.00            | 90.00            | Ω     |  |  |  |

| V <sub>OH</sub>                       | Output High Voltage               | 1.38             | 1.48             | V     |  |  |  |

| V <sub>OL</sub>                       | Output Low Voltage                | 1.12             | 1.02             | V     |  |  |  |

| V <sub>OD</sub>                       | Output Differential Voltage       | 0.25             | 0.46             | V     |  |  |  |

| V <sub>CM</sub>                       | Output Common Mode Voltage        | 1.25             | 1.25             | V     |  |  |  |

| I <sub>DC</sub>                       | DC Output Current                 | 11.24            | 10.20            | mA    |  |  |  |

nmonded Operating Conditions

1. For input buffer, see LVDS table.

# **Typical Building Block Function Performance**

## Pin-to-Pin Performance (LVCMOS25 12 mA Drive)<sup>1, 2, 3</sup>

| Function        | –8 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions | ł         |       |

| 16-bit Decoder  | 4.7       | ns    |

| 32-bit Decoder  | 4.7       | ns    |

| 64-bit Decoder  | 5.7       | ns    |

| 4:1 MUX         | 4.1       | ns    |

| 8:1 MUX         | 4.3       | ns    |

| 16:1 MUX        | 4.7       | ns    |

| 32:1 MUX        | 4.8       | ns    |

1. These functions were generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

## Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                                                   | –8 Timing | Units |

|----------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                            |           |       |

| 16-bit Decoder                                                             | 500       | MHz   |

| 32-bit Decoder                                                             | 500       | MHz   |

| 64-bit Decoder                                                             | 500       | MHz   |

| 4:1 MUX                                                                    | 500       | MHz   |

| 8:1 MUX                                                                    | 500       | MHz   |

| 16:1 MUX                                                                   | 500       | MHz   |

| 32:1 MUX                                                                   | 445       | MHz   |

| 8-bit adder                                                                | 500       | MHz   |

| 16-bit adder                                                               | 500       | MHz   |

| 64-bit adder                                                               | 305       | MHz   |

| 16-bit counter                                                             | 500       | MHz   |

| 32-bit counter                                                             | 460       | MHz   |

| 64-bit counter                                                             | 320       | MHz   |

| 64-bit accumulator                                                         | 315       | MHz   |

| Embedded Memory Functions                                                  | · · ·     |       |

| 512x36 Single Port RAM, EBR Output Registers                               | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, EBR Output Registers) | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers        | 130       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, PLC Output Registers) | 245       | MHz   |

| Distributed Memory Functions                                               | <b>i</b>  |       |

| 16x4 Pseudo-Dual Port RAM (One PFU)                                        | 500       | MHz   |

| 32x4 Pseudo-Dual Port RAM                                                  | 500       | MHz   |

| 64x8 Pseudo-Dual Port RAM                                                  | 400       | MHz   |

| DSP Function                                                               | · · ·     |       |

| 18x18 Multiplier (All Registers)                                           | 400       | MHz   |

| 9x9 Multiplier (All Registers)                                             | 400       | MHz   |

| 36x36 Multiply (All Registers)                                             | 260       | MHz   |

## Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                             | –8 Timing | Units |

|------------------------------------------------------|-----------|-------|

| 18x18 Multiply/Accumulate (Input & Output Registers) | 200       | MHz   |

| 18x18 Multiply-Add/Sub (All Registers)               | 400       | MHz   |

1. These timing numbers were generated using ispLEVER tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

3. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

# **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond and ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond and ispLEVER design tools can provide logic timing numbers at a particular temperature and voltage.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                       |                                 |                             | _        | -8                   | -       | -7                    | _      | -6       |                 |

|-----------------------|---------------------------------|-----------------------------|----------|----------------------|---------|-----------------------|--------|----------|-----------------|

| Parameter             | Description                     | Device                      | Min.     | Max.                 | Min.    | Max.                  | Min.   | Max.     | Units           |

| f <sub>MAX GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              | _        | 250                  | _       | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| tDVAGDDR              | Data Valid After CLK            | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 683      |                      | 688     |                       | 690    |          | ps              |

|                       | Data Valid After CLK            | ECP3-17EA                   | 683      | <u> </u>             | 688     | —                     | 690    | <u> </u> | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Dutput with Clock and Data Alig | ned at Pin (GDDRX1_TX.S     | SCLK.Ali | igned) <sup>10</sup> |         |                       |        |          |                 |

|                       | Data Invalid Before Clock       | ECP3-150EA                  |          | 335                  |         | 338                   |        | 341      | ps              |

|                       | Data Invalid After Clock        | ECP3-150EA                  |          | 335                  |         | 338                   | _      | 341      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-70EA/95EA              |          | 339                  |         | 343                   |        | 347      | ps              |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-70EA/95EA              |          | 339                  | _       | 343                   |        | 347      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-35EA                   |          | 322                  |         | 320                   |        | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-35EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-17EA                   | _        | 322                  | _       | 320                   | _      | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-17EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (<10 | ) Bits Wide) Centered at P  | in (GDD  | RX1_TX.              | DQS.Cer | ntered) <sup>10</sup> |        |          |                 |

| Left and Right Si     |                                 |                             | -        |                      |         | -                     |        |          |                 |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-150EA                  | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-150EA                  | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 670      | —                    | 675     | _                     | 676    | —        | ps              |

|                       | Data Valid After CLK            | ECP3-35EA                   | 670      | _                    | 675     | _                     | 676    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                   | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   |          | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Aligned at Pir | n (GDDR  | X2_TX.A              | ligned) |                       |        |          | 1               |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | All ECP3EA Devices          |          | 200                  |         | 210                   |        | 220      | ps              |

| tDIAGDDR              | Data Invalid After Clock        | All ECP3EA Devices          |          | 200                  |         | 210                   | _      | 220      | ps              |

| f <sub>MAX</sub> GDDR | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 500                  | _       | 420                   |        | 375      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Centered at P  | in Using | g DQSDL              | L (GDDF | X2_TX.D               | QSDLL. | Centered | ) <sup>11</sup> |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

|                       | Data Valid Before CLK           | All ECP3EA Devices          | 400      | —                    | 400     | —                     | 431    | —        | ps              |

| tDVAGDDR              | Data Valid After CLK            | All ECP3EA Devices          | 400      |                      | 400     |                       | 432    | —        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 400                  |         | 400                   | _      | 375      | MHz             |

## **Over Recommended Commercial Operating Conditions**

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

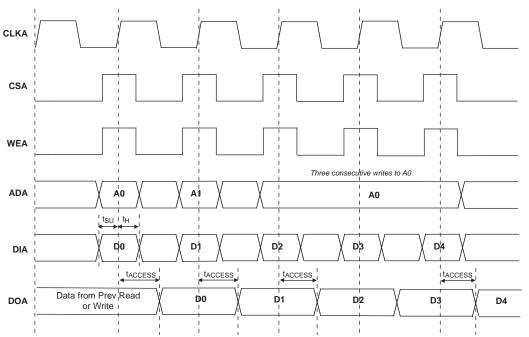

#### Figure 3-19. Test Loads

Test Loads

# LatticeECP3 sysCONFIG Port Timing Specifications

| Parameter            | Description                                                                                                                                    |                                       | Min. | Max.     | Units      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|----------|------------|

|                      | guration Initialization, and Wakeup                                                                                                            |                                       |      | L        |            |

|                      | Time from the Application of $V_{CC}$ , $V_{CCAUX}$ or $V_{CCIO8}^*$ (Whichever is the Last to Cross the POR Trip Point) to the Rising Edge of | Master mode                           |      | 23       | ms         |

| t <sub>ICFG</sub>    | is the Last to Cross the POR Trip Point) to the Rising Edge of INITN                                                                           | Slave mode                            |      | 6        | ms         |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to the Valid Master MCLK                                                                                           | •                                     |      | 5        | μs         |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                                                                                                       | 25                                    | —    | ns       |            |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                                                                                                   |                                       | 10   | ns       |            |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                                                                                                      |                                       |      | 37       | ns         |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                                                                                                       |                                       |      | 37       | ns         |

| t <sub>DINIT</sub> 1 | PROGRAMN High to INITN High Delay                                                                                                              |                                       |      | 1        | ms         |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals After DONE Pin is High                                                                                    |                                       | 100  | 500      | cycles     |

| t <sub>CZ</sub>      | MCLK From Active To Low To High-Z                                                                                                              |                                       |      | 300      | ns         |

| t <sub>IODISS</sub>  | User I/O Disable from PROGRAMN Low                                                                                                             |                                       |      | 100      | ns         |

| t <sub>IOENSS</sub>  | User I/O Enabled Time from CCLK Edge During Wake-up Sequer                                                                                     | nce                                   |      | 100      | ns         |

| All Configu          | iration Modes                                                                                                                                  |                                       |      |          |            |

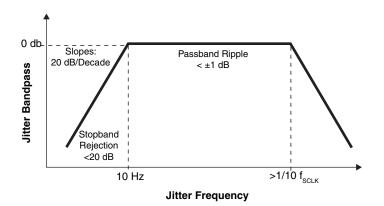

| t <sub>SUCDI</sub>   | Data Setup Time to CCLK/MCLK                                                                                                                   |                                       | 5    | —        | ns         |

| t <sub>HCDI</sub>    | Data Hold Time to CCLK/MCLK                                                                                                                    |                                       | 1    | —        | ns         |

| t <sub>CODO</sub>    | CCLK/MCLK to DOUT in Flowthrough Mode                                                                                                          |                                       | -0.2 | 12       | ns         |

| Slave Seria          | l                                                                                                                                              |                                       |      |          |            |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        | 5                                     | —    | ns       |            |

| t <sub>SSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                       | 5    | —        | ns         |

| _                    | Without encryption                                                                                                                             |                                       |      | 33       | MHz        |

| fcclk                | CCLK Frequency With encryption                                                                                                                 |                                       | _    | 20       | MHz        |

| Master and           | Slave Parallel                                                                                                                                 |                                       |      |          |            |

| t <sub>sucs</sub>    | CSN[1:0] Setup Time to CCLK/MCLK                                                                                                               |                                       | 7    | —        | ns         |

| t <sub>HCS</sub>     | CSN[1:0] Hold Time to CCLK/MCLK                                                                                                                |                                       | 1    | —        | ns         |

| t <sub>SUWD</sub>    | WRITEN Setup Time to CCLK/MCLK                                                                                                                 |                                       | 7    | —        | ns         |

| t <sub>HWD</sub>     | WRITEN Hold Time to CCLK/MCLK                                                                                                                  |                                       | 1    | —        | ns         |

| t <sub>DCB</sub>     | CCLK/MCLK to BUSY Delay Time                                                                                                                   |                                       | _    | 12       | ns         |

| t <sub>CORD</sub>    | CCLK to Out for Read Data                                                                                                                      |                                       | _    | 12       | ns         |

| t <sub>BSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                       | 6    | —        | ns         |

| t <sub>BSCL</sub>    | CCLK Minimum Low Pulse                                                                                                                         |                                       | 6    | —        | ns         |

| t <sub>BSCYC</sub>   | Byte Slave Cycle Time                                                                                                                          |                                       | 30   | —        | ns         |

| fcclk                | CCLK/MCLK Frequency                                                                                                                            | Without encryption<br>With encryption |      | 33<br>20 | MHz<br>MHz |

| Master and           | Slave SPI                                                                                                                                      | ,,                                    |      |          |            |

| t <sub>CFGX</sub>    | INITN High to MCLK Low                                                                                                                         |                                       | _    | 80       | ns         |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                                                                                                       |                                       |      | 2        | μs         |

| tSOCDO               | MCLK Low to Output Valid                                                                                                                       |                                       |      | 15       | ns         |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First MCLK Edge Setup Time                                                                                                  |                                       |      |          | μs         |

|                      |                                                                                                                                                | Without encryption                    | 0.3  | 33       | MHz        |

| fcclk                | CCLK Frequency                                                                                                                                 | With encryption                       | _    | 20       | MHz        |

| t <sub>SSCH</sub>    | CCLK Minimum High Pulse                                                                                                                        |                                       | 5    | —        | ns         |

#### **Over Recommended Operating Conditions**

### Figure 3-30. SPI Configuration Waveforms

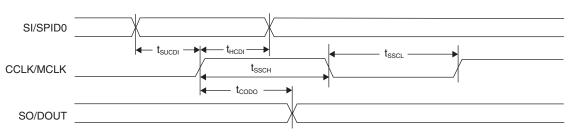

Figure 3-31. Slave SPI HOLDN Waveforms

# **Signal Descriptions (Cont.)**

| I/O | Description                                                                            |

|-----|----------------------------------------------------------------------------------------|

| I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion. |

| I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.                    |

|     |                                                                                        |

| I   | High-speed input, negative channel m                                                   |

| 0   | High-speed output, negative channel m                                                  |

| I   | Negative Reference Clock Input                                                         |

| I   | High-speed input, positive channel m                                                   |

| 0   | High-speed output, positive channel m                                                  |

| I   | Positive Reference Clock Input                                                         |

| —   | Output buffer power supply, channel m (1.2V/1.5)                                       |

|     | Input buffer power supply, channel m (1.2V/1.5V)                                       |

|     | I/O<br>I/O<br>I<br>I<br>I<br>I<br>I<br>I                                               |

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.