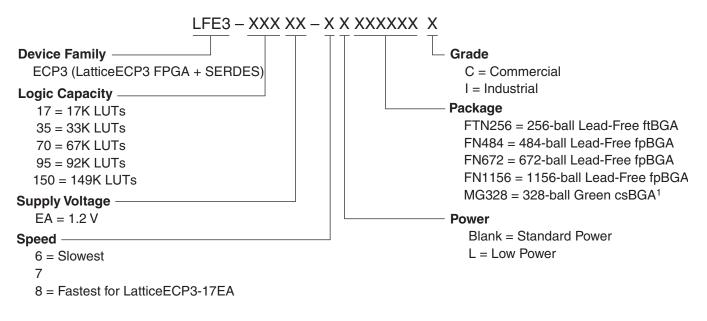

# Lattice Semiconductor Corporation - <u>LFE3-35EA-6FN672I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                                         |

| Number of Logic Elements/Cells | 33000                                                                        |

| Total RAM Bits                 | 1358848                                                                      |

| Number of I/O                  | 310                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 672-BBGA                                                                     |

| Supplier Device Package        | 672-FPBGA (27x27)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-6fn672i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

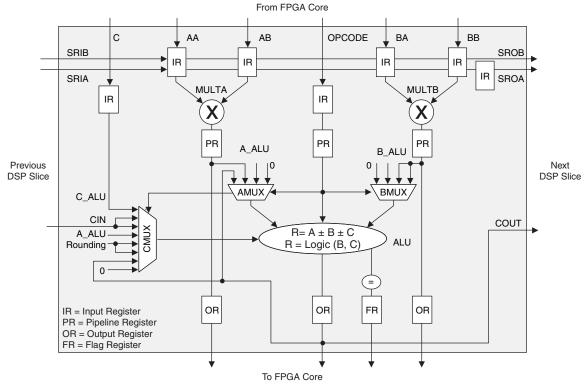

#### Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | x9                    | x18 | x36 |

|-------------------|-----------------------|-----|-----|

| MULT              | 4                     | 2   | 1/2 |

| MAC               | 1                     | 1   | _   |

| MULTADDSUB        | 2                     | 1   | _   |

| MULTADDSUBSUM     | <b>1</b> <sup>1</sup> | 1/2 | _   |

1. One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-32. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as LVDS inputs.

#### Table 2-11. PIO Signal List

| Name                                                     | Туре                             | Description                                                                                                                                                                                                                                               |

|----------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDD                                                     | Input Data                       | Register bypassed input. This is not the same port as INCK.                                                                                                                                                                                               |

| IPA, INA, IPB, INB                                       | Input Data                       | Ports to core for input data                                                                                                                                                                                                                              |

| OPOSA, ONEGA <sup>1</sup> ,<br>OPOSB, ONEGB <sup>1</sup> | Output Data                      | Output signals from core. An exception is the ONEGB port, used for tristate logic at the DQS pad.                                                                                                                                                         |

| CE                                                       | PIO Control                      | Clock enables for input and output block flip-flops.                                                                                                                                                                                                      |

| SCLK                                                     | PIO Control                      | System Clock (PCLK) for input and output/TS blocks. Connected from clock ISB.                                                                                                                                                                             |

| LSR                                                      | PIO Control                      | Local Set/Reset                                                                                                                                                                                                                                           |

| ECLK1, ECLK2                                             | PIO Control                      | Edge clock sources. Entire PIO selects one of two sources using mux.                                                                                                                                                                                      |

| ECLKDQSR <sup>1</sup>                                    | Read Control                     | From DQS_STROBE, shifted strobe for memory interfaces only.                                                                                                                                                                                               |

| DDRCLKPOL <sup>1</sup>                                   | Read Control                     | Ensures transfer from DQS domain to SCLK domain.                                                                                                                                                                                                          |

| DDRLAT <sup>1</sup>                                      | Read Control                     | Used to guarantee INDDRX2 gearing by selectively enabling a D-Flip-Flop in dat-<br>apath.                                                                                                                                                                 |

| DEL[3:0]                                                 | Read Control                     | Dynamic input delay control bits.                                                                                                                                                                                                                         |

| INCK                                                     | To Clock Distribution<br>and PLL | PIO treated as clock PIO, path to distribute to primary clocks and PLL.                                                                                                                                                                                   |

| TS                                                       | Tristate Data                    | Tristate signal from core (SDR)                                                                                                                                                                                                                           |

| DQCLK0 <sup>1</sup> , DQCLK1 <sup>1</sup>                | Write Control                    | Two clocks edges, 90 degrees out of phase, used in output gearing.                                                                                                                                                                                        |

| DQSW <sup>2</sup>                                        | Write Control                    | Used for output and tristate logic at DQS only.                                                                                                                                                                                                           |

| DYNDEL[7:0]                                              | Write Control                    | Shifting of write clocks for specific DQS group, using 6:0 each step is approxi-<br>mately 25ps, 128 steps. Bit 7 is an invert (timing depends on input frequency).<br>There is also a static control for this 8-bit setting, enabled with a memory cell. |

| DCNTL[6:0]                                               | PIO Control                      | Original delay code from DDR DLL                                                                                                                                                                                                                          |

| DATAVALID <sup>1</sup>                                   | Output Data                      | Status flag from DATAVALID logic, used to indicate when input data is captured in IOLOGIC and valid to core.                                                                                                                                              |

| READ                                                     | For DQS_Strobe                   | Read signal for DDR memory interface                                                                                                                                                                                                                      |

| DQSI                                                     | For DQS_Strobe                   | Unshifted DQS strobe from input pad                                                                                                                                                                                                                       |

| PRMBDET                                                  | For DQS_Strobe                   | DQSI biased to go high when DQSI is tristate, goes to input logic block as well as core logic.                                                                                                                                                            |

| GSRN                                                     | Control from routing             | Global Set/Reset                                                                                                                                                                                                                                          |

|                                                          |                                  |                                                                                                                                                                                                                                                           |

1. Signals available on left/right/top edges only.

2. Selected PIO.

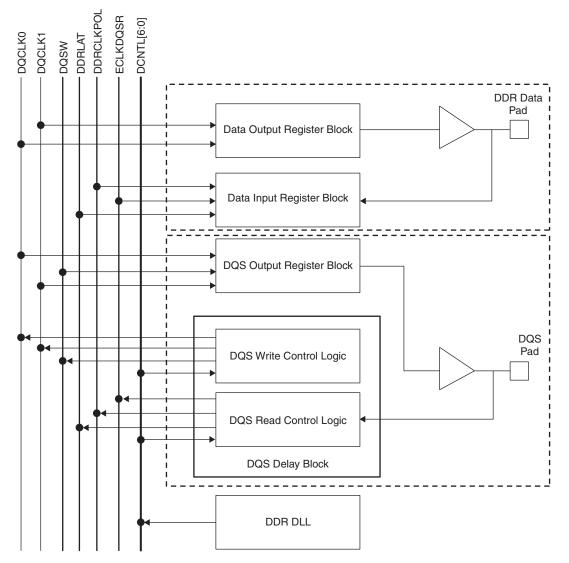

# PIO

The PIO contains four blocks: an input register block, output register block, tristate register block and a control logic block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

## Input Register Block

The input register blocks for the PIOs, in the left, right and top edges, contain delay elements and registers that can be used to condition high-speed interface signals, such as DDR memory interfaces and source synchronous interfaces, before they are passed to the device core. Figure 2-33 shows the input register block for the left, right and top edges. The input register block for the bottom edge contains one element to register the input signal and no DDR registers. The following description applies to the input register block for PIOs in the left, right and top edges only.

Input signals are fed from the sysl/O buffer to the input register block (as signal DI). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), a clock (INCK) and, in selected blocks, the input to the DQS delay block. If an input delay is desired, designers can select either a fixed delay or a dynamic delay DEL[3:0]. The delay, if selected, reduces input register hold time requirements when using a global clock.

The input block allows three modes of operation. In single data rate (SDR) the data is registered with the system clock by one of the registers in the single data rate sync register block.

In DDR mode, two registers are used to sample the data on the positive and negative edges of the modified DQS (ECLKDQSR) in the DDR Memory mode or ECLK signal when using DDR Generic mode, creating two data streams. Before entering the core, these two data streams are synchronized to the system clock to generate two data streams.

A gearbox function can be implemented in each of the input registers on the left and right sides. The gearbox function takes a double data rate signal applied to PIOA and converts it as four data streams, INA, IPA, INB and IPB. The two data streams from the first set of DDR registers are synchronized to the edge clock and then to the system clock before entering the core. Figure 2-30 provides further information on the use of the gearbox function.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred to the system clock domain from the ECLKDQSR (DDR Memory Interface mode) or ECLK (DDR Generic mode). The DDRLAT signal is used to ensure the data transfer from the synchronization registers to the clock transfer and gearbox registers.

The ECLKDQSR, DDRCLKPOL and DDRLAT signals are generated in the DQS Read Control Logic Block. See Figure 2-37 for an overview of the DQS read control logic.

Further discussion about using the DQS strobe in this module is discussed in the DDR Memory section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

#### Figure 2-37. DQS Local Bus

## **Polarity Control Logic**

In a typical DDR Memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeECP3 family contains dedicated circuits to transfer data between these domains. A clock polarity selector is used to prevent set-up and hold violations at the domain transfer between DQS (delayed) and the system clock. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects the first DQS rising edge after the preamble state. This signal is used to control the polarity of the clock to the synchronizing registers.

## DDR3 Memory Support

LatticeECP3 supports the read and write leveling required for DDR3 memory interfaces.

Read leveling is supported by the use of the DDRCLKPOL and the DDRLAT signals generated in the DQS Read Control logic block. These signals dynamically control the capture of the data with respect to the DQS at the input register block.

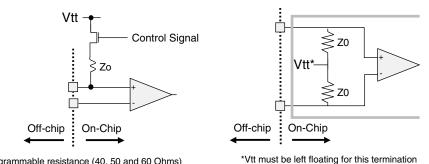

## **On-Chip Programmable Termination**

The LatticeECP3 supports a variety of programmable on-chip terminations options, including:

- Dynamically switchable Single-Ended Termination with programmable resistor values of 40, 50, or 60 Ohms. External termination to Vtt should be used for DDR2 and DDR3 memory controller implementation.

- Common mode termination of 80, 100, 120 Ohms for differential inputs

#### Figure 2-39. On-Chip Termination

Programmable resistance (40, 50 and 60 Ohms)

Parallel Single-Ended Input

Differential Input

See Table 2-12 for termination options for input modes.

#### Table 2-12. On-Chip Termination Options for Input Modes

| IO_TYPE    | TERMINATE to VTT <sup>1, 2</sup> | DIFFERENTIAL TERMINATION RESISTOR <sup>1</sup> |

|------------|----------------------------------|------------------------------------------------|

| LVDS25     | þ                                | 80, 100, 120                                   |

| BLVDS25    | þ                                | 80, 100, 120                                   |

| MLVDS      | þ                                | 80, 100, 120                                   |

| HSTL18_I   | 40, 50, 60                       | þ                                              |

| HSTL18_II  | 40, 50, 60                       | þ                                              |

| HSTL18D_I  | 40, 50, 60                       | þ                                              |

| HSTL18D_II | 40, 50, 60                       | þ                                              |

| HSTL15_I   | 40, 50, 60                       | þ                                              |

| HSTL15D_I  | 40, 50, 60                       | þ                                              |

| SSTL25_I   | 40, 50, 60                       | þ                                              |

| SSTL25_II  | 40, 50, 60                       | þ                                              |

| SSTL25D_I  | 40, 50, 60                       | þ                                              |

| SSTL25D_II | 40, 50, 60                       | þ                                              |

| SSTL18_I   | 40, 50, 60                       | þ                                              |

| SSTL18_II  | 40, 50, 60                       | þ                                              |

| SSTL18D_I  | 40, 50, 60                       | þ                                              |

| SSTL18D_II | 40, 50, 60                       | þ                                              |

| SSTL15     | 40, 50, 60                       | þ                                              |

| SSTL15D    | 40, 50, 60                       |                                                |

1. TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR when turned on can only have one setting per bank. Only left and right banks have this feature. Use of TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR are mutually exclusive in

an I/O bank.

On-chip termination tolerance +/- 20%

2. External termination to VTT should be used when implementing DDR2 and DDR3 memory controller.

# LatticeECP3 Family Data Sheet DC and Switching Characteristics

#### April 2014

Data Sheet DS1021

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V_{CC}                                                         |

|-------------------------------------------------------------------------------|

| Supply Voltage V_{CCAUX} $\ldots \ldots \ldots \ldots -0.5$ V to 3.75 V       |

| Supply Voltage V_{CCJ} $\ldots \ldots \ldots \ldots \ldots -0.5$ V to 3.75 V  |

| Output Supply Voltage V_{CCIO} –0.5 V to 3.75 V                               |

| Input or I/O Tristate Voltage Applied $^4.$ –0.5 V to 3.75 V                  |

| Storage Temperature (Ambient) $\ldots \ldots -65$ V to 150 $^{\circ}\text{C}$ |

| Junction Temperature $(T_J)$                                                  |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

# **Recommended Operating Conditions**<sup>1</sup>

| Symbol                             | Parameter                                                                      | Min.  | Max.   | Units |

|------------------------------------|--------------------------------------------------------------------------------|-------|--------|-------|

| V <sub>CC<sup>2</sup></sub>        | Core Supply Voltage                                                            | 1.14  | 1.26   | V     |

| V <sub>CCAUX</sub> <sup>2, 4</sup> | Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES) | 3.135 | 3.465  | V     |

| V <sub>CCPLL</sub>                 | PLL Supply Voltage                                                             | 3.135 | 3.465  | V     |

| V <sub>CCIO<sup>2, 3</sup></sub>   | I/O Driver Supply Voltage                                                      | 1.14  | 3.465  | V     |

| V <sub>CCJ<sup>2</sup></sub>       | Supply Voltage for IEEE 1149.1 Test Access Port                                | 1.14  | 3.465  | V     |

| $V_{REF1}$ and $V_{REF2}$          | Input Reference Voltage                                                        | 0.5   | 1.7    | V     |

| V <sub>TT</sub> ⁵                  | Termination Voltage                                                            | 0.5   | 1.3125 | V     |

| t <sub>јсом</sub>                  | Junction Temperature, Commercial Operation                                     | 0     | 85     | °C    |

| t <sub>JIND</sub>                  | Junction Temperature, Industrial Operation                                     | -40   | 100    | °C    |

| SERDES External P                  | ower Supply <sup>6</sup>                                                       | •     | •      |       |

|                                    | Input Buffer Power Supply (1.2 V)                                              | 1.14  | 1.26   | V     |

| V <sub>CCIB</sub>                  | Input Buffer Power Supply (1.5 V)                                              | 1.425 | 1.575  | V     |

|                                    | Output Buffer Power Supply (1.2 V)                                             | 1.14  | 1.26   | V     |

| V <sub>CCOB</sub>                  | Output Buffer Power Supply (1.5 V)                                             | 1.425 | 1.575  | V     |

| V <sub>CCA</sub>                   | Transmit, Receive, PLL and Reference Clock Buffer Power Supply                 | 1.14  | 1.26   | V     |

1. For correct operation, all supplies except V<sub>REF</sub> and V<sub>TT</sub> must be held in their valid operation range. This is true independent of feature usage.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC.</sub> If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3 V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. V<sub>CCAUX</sub> ramp rate must not exceed 30 mV/µs during power-up when transitioning between 0 V and 3.3 V.

5. If not used, V<sub>TT</sub> should be left floating.

6. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for information on board considerations for SERDES power supplies.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeECP3 External Switching Characteristics <sup>1, 2, 3, 13</sup>

|                            |                                                                   |                     | -         | -8              | •    | -7         | 1    | -6         |       |

|----------------------------|-------------------------------------------------------------------|---------------------|-----------|-----------------|------|------------|------|------------|-------|

| Parameter                  | Description                                                       | Device              | Min.      | -8<br>Max.      | Min. | -7<br>Max. | Min. | -о<br>Max. | Units |

| Clocks                     | Description                                                       | Device              | Min.      | wax.            | win. | wax.       | MIN. | wax.       | Units |

| Primary Clock <sup>6</sup> |                                                                   |                     |           |                 |      |            |      |            |       |

|                            | Frequency for Primary Clock Tree                                  | ECP3-150EA          | _         | 500             |      | 420        | _    | 375        | MHz   |

| t <sub>MAX_PRI</sub>       | Clock Pulse Width for Primary                                     |                     |           | 000             |      | 420        |      | 0/0        |       |

| t <sub>W_PRI</sub>         | Clock                                                             | ECP3-150EA          | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-150EA          | -         | 300             | —    | 330        | —    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-150EA          | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-70EA/95EA      | -         | 500             | —    | 420        | -    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-70EA/95EA      | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-70EA/95EA      | _         | 360             | _    | 370        | _    | 380        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-70EA/95EA      | —         | 310             | —    | 320        | —    | 330        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-35EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-35EA           | 0.8       | —               | 0.9  |            | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-35EA           | -         | 300             | —    | 330        | _    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-35EA           | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-17EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-17EA           | 0.8       | _               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-17EA           | _         | 310             | —    | 340        | —    | 370        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-17EA           | _         | 220             | —    | 230        | —    | 240        | ps    |

| Edge Clock <sup>6</sup>    | •                                                                 |                     | •         |                 |      | •          | •    | •          |       |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-150EA          | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-150EA          | 0.9       | —               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-150EA          | -         | 200             | —    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-70EA/95EA      | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-70EA/95EA      | 0.9       | _               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-70EA/95EA      | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-35EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-35EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| <sup>t</sup> skew_edge_dqs | Edge Clock Skew Within an Edge of the Device                      | ECP3-35EA           | _         | 200             | —    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-17EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-17EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| tskew_edge_dqs             | Edge Clock Skew Within an Edge of the Device                      | ECP3-17EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| Generic SDR                | •                                                                 |                     | •         | •               |      | •          | •    | •          | ·     |

| General I/O Pin Pa         | arameters Using Dedicated Clock In                                | put Primary Clock V | Vithout P | LL <sup>2</sup> |      |            |      |            |       |

| t <sub>CO</sub>            | Clock to Output - PIO Output<br>Register                          | ECP3-150EA          | _         | 3.9             | —    | 4.3        | —    | 4.7        | ns    |

| t <sub>SU</sub>            | Clock to Data Setup - PIO Input<br>Register                       | ECP3-150EA          | 0.0       | _               | 0.0  |            | 0.0  | _          | ns    |

| t <sub>H</sub>             | Clock to Data Hold - PIO Input<br>Register                        | ECP3-150EA          | 1.5       | _               | 1.7  |            | 2.0  |            | ns    |

| t <sub>SU_DEL</sub>        | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-150EA          | 1.3       | —               | 1.5  | _          | 1.7  |            | ns    |

## **Over Recommended Commercial Operating Conditions**

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                               | ·8                                                             | _                                                                                                           | -7                                                  | _                                                                                                       | -6                                                                      |                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min.                                                                            | Max.                                                           | Min.                                                                                                        | Max.                                                | Min.                                                                                                    | Max.                                                                    | Units                                                                                     |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.6                                                                             |                                                                | 1.8                                                                                                         |                                                     | 2.0                                                                                                     |                                                                         | ns                                                                                        |

|                                                                                                                                                                                                                                                                                         | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.2                                                            | _                                                                                                           | 3.4                                                 | _                                                                                                       | 3.6                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             |                                                                | 1.7                                                                                                         |                                                     | 1.8                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                   | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.0                                                            | _                                                                                                           | 3.3                                                 | _                                                                                                       | 3.5                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                       | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                  | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             | _                                                              | 1.7                                                                                                         | _                                                   | 1.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                   | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             | _                                                              | 0.0                                                                                                         | _                                                   | 0.0                                                                                                     | _                                                                       | ns                                                                                        |

| Input                                                                                                                                                                                                                                                                                   | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ns                                                                                        |

|                                                                                                                                                                                                                                                                                         | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ps                                                                                        |

| tHOGDDR                                                                                                                                                                                                                                                                                 | Data Hald After OLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             |                                                                | 400                                                                                                         |                                                     |                                                                                                         |                                                                         |                                                                                           |

|                                                                                                                                                                                                                                                                                         | Data Hold After CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                             |                                                                | 480                                                                                                         | —                                                   | 480                                                                                                     |                                                                         | · ·                                                                                       |